Изобретение относится к вычислительной технике и может быть использовано при контроле и диагностике цифровых устройств.

Целью изобретения является увеличение быстродействия и гювышение достоверности контроля.

В анализаторе за счет включения мультиплексоров в цепь записи блоков памяти (а не подключение к одноканальному входу данных, как это осуществляется в известных устройствах), проявляется новое техническое свойство, заключающееся в том, что контроль m выходов объекта контроля осуществляется за один цикл. Это позволяет значительно сократить время (в m раз) операции контроля. При этом для каждого канала формируется отдельная т-разрядная сигнатура, что дает возможность сразу по окончании цикла контроля указать выходы ОК, на которых проявилась неисправность.

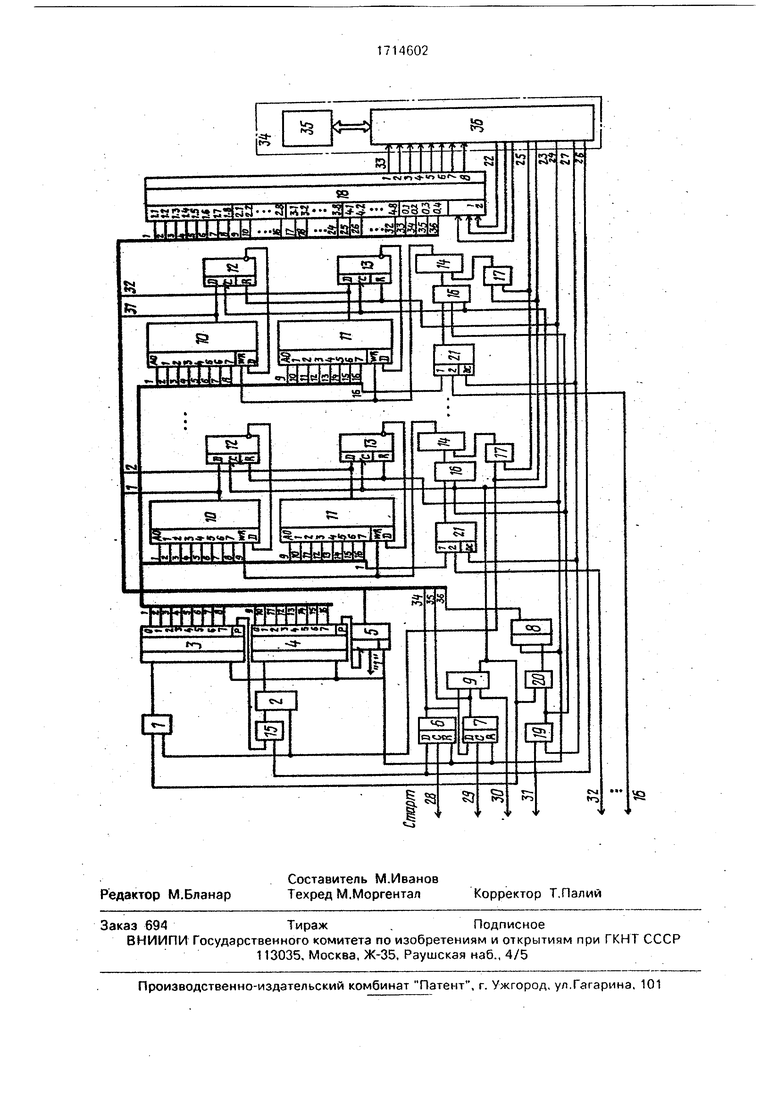

На чертеже представлена функциональная схема анализатора.

- Для определенности принято m 16.

Анализатор выполнен в виде модуля микропроцессорной системы контроля диагностики и содержит первый 1 и второй 2 элементы. ИЛ И, первый 3 и второй 4 счетчики, первый 5, второй 6, третий 1 D-триггеры, четвертый 8 Т-триггер, второй элемент И9, первую группу 10 блоков памяти, вторую группу 11 блоков памяти, первую 12 и вторую 13 группы триггеров, группу элементов ИЛИ 14, первый элемент И 15. первую 16 и вторую 17 группы элементов И, мультиплексор 18, третий элемент ИЛИ 19, третий элемент И 20, группу 21 мультиплексоров, группу 22 входов задания режима, вход 23 записи/считывания, вход24.сброса, первый вход 25 задания режима, вход 26 разрешения, второй вход 27 задания режима, вход 28 Старт,- вход 29 Стоп, тактовый 30 и информационный 31 входы, группу 32 информационных входов и группу 33 информационных выходов анализатора. На чертеже также показаны контроллер 34, ЭВМ 35, интерфейсный 36 блок. Анализатор реализован по перестраиваемой структуре. В одноканальном режиме (О на втором входе 27 задания режима) он формирует одну сигнатуру первого порядка и m сигнатур второго порядка одновременно. В многоканальном режиме (1 на втором входе 27 задания режима) он по m каналам формирует параллельно и независимо m сигнатур первого порядка. Процесс получения сигнатур поясняют на примере формирования сигнатуры первого порядка для одного из m каналов. Как известно, сигнатура первого порядка представляет собой сумму по модулю два номеров тактов, на которых символы контролируемой последовательности равны единице: N - 1. S« 2 Dk Ak.(1) где S - m-разрядный двоичный вектор искомой сигнатуры; N-длина контролируемой последовательности в тактах; Dk-значение k-ro символа контролируемой последовательности. Dk {0,1); k-номер такта; Ak - значение k в двоичном коде (двоичный вектор-разрядности tQg2ND. . Здесь и далее конъюнкция Dk&Ak обознамается Dk Ak. Полагая-т четным и N-2, записывают выражение (1) в следующем виде:

5w-t

SVn-a

.. 1

OmtT. . A

Z. ----Z,PKAK),

Owi2-« TOfu--4 5ml4-4 Y-й компонент (разряд) сигнатуры SY 5) Dh a Yk определяется только Y-м компонентов aY вектора номера такта А. Выделяют и далее рассматривают формирование младших компонентов вектора сигнатуры, отделенных в (2) пунктирной линией:о«,-. о„И.. И- f Si.i..,,.e-So.V.«.-4.«-S°« fi .

««

(t-)

Младшие m/2 разрядов вектора (младший вектор) номера такта при О k N могут принимать значения от 000...00 до 111... 11, причем на последовательности длиной N 2 каждый из этих векторов появляется ровно () раз с периодом в 2 тактов. Разложим сумму (3) на такие слагаемые-суммы, в которые в качестве сомножителя входит младший вектор номера такта только одного фиксированного вида. И4-),о ynttV иI tSD4(t-.a«i О 2Г2)е+( + : «V г : а Ott-ga (а «w i t-i iMt ne .. ( . :.S (t4l2 2 tmW-«),0 ) f 4) где z - вес вектора - двоичное число, представляющее собой младшие т/2 разрядов номера такта. Рассмотрим z-e слагаемое-сумму в выражении (4), Это слагаемое равно нулю, если ) О АЛ всех t или событие Di-(M|2 1 появляется четное число раз на рассматриваемых 2 тактах. Если данное событие появляется нечетное число раз, то значение соответствующего слагаемогосуммы совпадает со значением веса вектора младших п/2 разрядов номера такта. Тогда очевидно, что младшие m/2 разрядов сигнатуры «)жно получить, просуммировав по

модулю два такие вектора младших т/2 разрядов векторов номера такта, при которых символ контролируемой последовательности равен единице нечетное число раз.

Аналогично старшие т/2 разрядов вектора сигнатуры могут быть получены суммированием по модулю два векторов старших т/2 разрядов номеров тактов, если на этих тактах символ контролируемой последовательности равен единице нечетное число раз.

Таким образом, процесс формирования сигнатур первого порядка описывается выражениями

r/ -j-Vi

S(m/2-1),0 S Е Dz+{t-1)2 A(m/2-1).0

f r N -1

2 Dk A(ni/2-i).o:(5)

JM/ QM/l

S{m-1).m/2 X E ) X

tit

IN-1

xA(m-1),m/2 E Pk A(m-1).m/2. k 1

Рассмотрим принцип действия анализатора, выделив два режима работы - одноканальный и многоканальный. Для каждого режима в процедуре получения сигнатур можно выделить три этапа:

подготовка к работе (очистка памяти). На этом этапе анализатор функционирует одинаково как в одноканальном. так и в многоканальном режиме;

определение четности числа вектйров фиксированного вида, на которые попадают единичные символы контролируемой последовательности;

суммирование вектрров.

Первый и третий этапы реализуются программно, второй - аппаратно.

В одноканальном режиме анализатор функционирует точно так же. как и известное устройство, так как в этом режиме контроллер 34 выставляет О на втором входе 27 задания режима, восстанавливая тем самым связи, существующие в известном устройстве.

Рассмотрим работу анализатора в многоканальном режиме.

На этапе подготовки к работе контроллер 34 подает на вход элемента И 15 и на D-вход триггера 6 сигнал О, запрещая тем самым восприятие внешних сигналов Старт, Стоп. Синхр., а на вход всех элементов И 17 подается сигнал разрешения очистки блоков 10 и 11 памяти (по первому входу 25 задания режима).

Кроме того, контроллер 34 по группе 22 входов задания режима устанавливает на 5 управляющих входах мультиплексора 18 код 000 для считывания в контроллер через нулевой канал мультиплексора слова состояния анализатора - выходных сигналов триггеров 5-8. Одновременно контроллер

10 34 подает на входы сброса R счетчиков 3 и 4, а также всех триггеров (58, 12, 13) сигнал Сброс, после чего формирует импульсы очистки элементов памяти, которые поступают на вход 23 записи/считывания

5 анализатора. Эти импульсы с.выхода контроллера 34 проходят через элементы 1 и 2 на входы синхронизации счетчиков 3 и 4 соответственно, а через элементы 17 и 14 на входы записи WR соответствующих блоков

0 10 и 11 памяти.

При этом во все ячейки всех блоков 10 и 11 памяти с выходов триггеров 12 и 13 записывается 1. По окончании записи в последнюю 2 -ую ячейку блоков памяти

5 импульс переполнения счетчика 4 поступает на С-вход триггера 5 и устанавливает его в 1. Сигналом с выхода триггера 5 контроллер 34 через нулевой канал мультиплексора 18 информирует об окончании первого этапа. При этом контроллер прекращает формирование импульсов очистки памяти, восстанавливает сигнал О на входе элементов 17 (по первому входу 25 задания режима анализатора) и подает сигнал

5 Сброс для установки триггеров и счетчи ков в исходное состояние.

В начале второго этапа в многоканальном режиме контроллер 34 подает 1 на вход элемента ИЛИ 19 и нч вход управления

0 всех мультиплексоров 21, блокируя тем самым одноканальный информационный вход 31 и подключая информационные входы 32 анализатора через мультиплексоры 21. элементы И 16 и элементы ИЛИ 14 к входам

5 записи WR соответствующих блоков 10 и 11 памяти. Одновременно контроллер 34 подает 1 на D-вход триггера 6 и на вход элемента И 15. При этом вход счетчика 4 через элемент И Л И-2 и элемент И 15 соездиняется

0 с выходом переполнения счетчика 3, вход которого через элемент ИЛИ 1 и элемент И 9 соединяется с тактовым входом 30 анализатора. Анализатор переходит в режим ожидания внешних управляющих сигналов, а

5 контроллер следит за состоянием триггеров 5-8через нулевой канал мультиплексора 18, Формирование сигнатуры начинается с приходом сигнала Сгярт, по которому триггер б устанавливается в 1. открывается элемент И 9. импульсы с тактового входа

30 анализатора через элемент 1/19 и элемент ИЛИ 1 проходят на вход счетчика .3, кроме того,,импульсы с выхода элемента И 9 поступают на тактовые входы всех триггеров 12 и 13 и на входы всех элементов И 16. На другие входы элементов И 16 приходят 1 с выхода элемента ИЛИ 19 и сигналы с соответствующих информационных входов 32 анализатора,

В процессе счета тактовых импульсов контролируемой последовательности опрашиваются соответствующие ячейки всех блоков 10 и 11.

При этом в начале каждого k-ro такта импульсов синхронизации в триггеры 12 и 13 обеих групп триггеров записываются коды, хранящиеся в соответствующих ячейках памяти блоков 10 и 11.

Если на этом k-м такте символ контролируемой последовательности на некотором J-M входе данных равен Dk 1, в конце такта коды с инверсных выходов 1-х триггеров 12 и 13 переписываются в соответствующие ячейки 1-х блоков 10 и 11.

Таким образом, если Dil О, то код в соответствующих ячейках сохраняется без

изменения, если же Dil 1, то код в этих ячейках инвертируется. Если при oripoce некоторой ячейки памяти блока 10 (11) символ контролируемой последовательности равен единице четное число раз, то в этой ячейке сохраняется код, записанный на первом этапе работы (т,е. 1), если нечетное число раз - TQ код инвертируется (О), т.е. происходит определение четности числа векторов фиксированного вида (младших и старших байтов кода номера такта), на которые попадают единичные символы контролируемой последовательности.

С приходом, импульса Стоп от объекта контроля триггер 7 устанавливается в 1 при этом закрывается элемент И 9, а сигналом от триггера 7 через нулевой канал мультиплексора 18 контроллер 34 информируется о завершении второго этапа работы. Кроме того, в контроллер через нулевой канал мультиплексора 18 поступают сигналы от триггера 5, который устанавливается в 1, если длина контролируемой последовательности N 2, от триггера 6 - для информации контроллера о зависании (если на анализатор не пришел сигнал Старт).

Перед началом третьего этапа контроллер 34 подает сигнал О на вход всех элементов И 17, на D-вход триггера б и на вход элемента И15. При этом блокируется запуск анализатора сигналом Старт и запись в блоки 10 и 11 памяти, а также разрывается связь между счетчиками 3 и 4.

Затем контроллер 34 устанавливает на управляющих кодах мультиплексора 18 код 001, подготавливая к чтению через первый канал мультиплексора 18 из блоков 10 и 11

памяти соответствующих векторов младших четырех сигнатур (с первого канала по четвертый), подает сигнал установки в О всех счетчиков и триггеров анализатора и формирует импульсы опроса ячеек блоков 10 и 11

памяти.

Далее на каждое состояние счетчиков 3 и 4 (которые работают синхронно) производится считывание содержимого опрашиваемых блоков памяти и, если считываемые

биты равны О, то соответствующие вектора младших (старших) байтов соответствующей сигнатуры суммируются по модулю два с ранее полученной суммой векторов младших (старших) байтов. После опроса последних 2 -X ячеек блоков памяти первых четырех сигнатур, контроллер устанавливает на управляющих входах мультиплексора 18 код 010 для чтения из блоков 10 и 11 памяти через второй канал мультиплексора

18 соответствующих векторов для формирования сигнатур с пятого по восьмой канал и т.д.

Таким образом, программным путем по алгоритму, описываемому формулами (5),

получают все m сигнатур первого порядка. Предлагаемый сигнатурный анализатор позволяет для каждого из m каналов параллельно и независимо формировать т-разрядную сигнатуру первого порядка за один

цикл контроля обьекта. Программная обработка не требует многократного повторения запуска объекта испытаний, что повышает достоверность контроля.

Выполнение счетчика номеров тактов в

виде двух m/2-разрядных счетчиков позволяет в 2 раз уменьшить продолжительность этапа очистки и каждого цикла опроса -блоков памяти, что дополнительно повышает быстродействие анализатора. Очевидно,

что счетчик может быть выполнен и как четыре ni/4-разрядных счетчика, при этом целесообразно использовать деление вектора номера такта соответственно на четыре части и блоки памяти с произвольной выборкой одного из 2 слов и т.п.

Рассмотрим пример формирования сигнатуры первого порядка для одного произвольного канала для двоичной последовательности, символы которой Dk равным

единице на тактах с номерами 0007f1, ОООСН, 001Н, 010СН (здесь и далее номера даны в шестнад1;атиричном - Н или двоичном - В кодах), на остальных тактах Dk 0: m 16,

На нулевом такте (по окончании этапа подготовки) содержимое всех ячеек блоков 10 и 11 памяти равно единице. Пока Dk О, т.е. по такт с номером 0006Н включительно состояние ячеек не изменяется. На такте номер 0007Н проинвертируется содержимое ячейки с адресом 07Н блока 10. Аналогично на тактах ОООСН и 0017Н проинвертируется содержимое ячеек с адресом ОСИ и 17Н соответственно блока 10. На такте 01 ОС проинвертируется содержимое ячеек с адресом ОСН блока 10 и с адресом 01Н блока 11.

При считывании опрашиваются все ячейки блоков 10 и 11 и суммируются по модулю два коды адресов тех ячеек соответствующих микросхем, в которых записан О. Так а блоке 10 О записан в ячейки 07Н, 17Н (в ячейке этого блока с адресом ОС записана 1, так как информация в ней инвертировалась дважды - на тактах ОООС и 010С). поэтому младший байт сигнатуры равен

(0000 0111) В + (0001 0111)В

(0001 0000)В ЮН.

Так как в блоке 11 О записан только в ячейку с адресом 01Н. то старший байт сигнатуры равен 01 Н. Полная сигнатура для этого канала равна соответственно OIIOH,Эта сигнатура совпадает с сигнатурой, полученной по выражению (1);

(0000 0000 0000 0111)8 +

+ (0000 0000 0000 1100)В + + (000000000001 0111)В + + (0000 0001 0000 1100)8

(0000 0001 0001 оооо)в 01 юн.

Полученные в процессе контроля испытуемого устройства сигнатуры сравнивают с ранее полученными для заведомо исправного аналогичного устройства (или рассчитанными аналитический). Если сигнатуры совпадают, то делается вывод об отсутствии ошибок в контролируемых двричных последовательностях и, следовательно, об исправности контролируемого объекта.

Однако ввиду сжатия информации сигнатурным анализатором возможен пропуск ошибок. В многоканальном режиме данный сигнатурный анализатор обеспечивает с вероятностью Р 1 в каждом канале обнаружение одиночных ошибок в независимости от длины последовательности. При длине последовательности - 1 обнаруживаются все ошибки кратности 2 и локализуются все одиночные ошибки. При предположении о равновероятности ошибок произвольной кратности усредненная вероятность пропуска ошибок равна отношению мощности множества всех необнаруживаемых ошибочных последовательностей к мощности множества всех возможных ошибочных последовательностей:

oN -m

1

РОШ -

о

1

где m - разрядность сигнатуры первого порядка.. Устройство реализовано в виде модуля

4Q программно-управляемого сигнатурного анализатора и входит в состав автоматизированной системы контроля и диагностики. Модуль выполнен в интерфейсе микроЭВМ Электроника 60 и содержит около ЮОмик 5 росхем серий К531, К555.

. Объем программ формирования сигнатур, включая управление анализатором на всех этапах и во всех режимах работы, составляет около 350 команд на языке ассемQ блера микроэвм Электроника 60, время отработки программы около 15 мс, собственно цикл сбора информации об объекте контроля равен N/f, где N - длина контролируемой последовательности, f- тактовая

5 частота работы объекта (f 10 МГц). Формула изобретения Сигнатурный анализатор, содержащий два счетчика, первый, второй, третий и четвертый триггеры, первую и вторую группы

Q триггеров, первую и вторую группы элементов 1Д, мультиплексор, группу элементов ИЛИ, два элемента ИЛИ, три элемента И, две группы блоков памяти, причем входы сброса счетчиков, входы сброса первого,

с второго, третьего и четвертого триггеров,

, входы сброса триггеров первой и второй

групп объединены i/f образуют вход сброса

анализатора, первые входы элементов И

первой группы объединены с первым вхоQ дом третьего элемента И, группа управляющих входов мультиплексора образует группу входов задания режима анализатора,-тактовые входы триггеров первой и второй групп, третьи входы элементов И

g первой группы, первый вход первого элемента ИЛ И и второй вход третьего элемента И объединены и подключены к выходу второго элемента И, первый вход которого соединен с D-входом третьего триггера и

Q подключен к выходу второго триггера, второй вход второго элемента И соединен с инверсным выходом третьего триггера, выход третьего элемента И подключен к тактовому входу четвертого триггера, третий вход

е второго элемента И является тактовым входом анализатора, второй вход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ, с первыми входами элементов И второй группы и образует вход записи-считывания анализатора, вторые

входы элементов И второй группы объединены и образуют первый вход задания режима анализатора, выходы i-x элементов И первой и второй групп соединены с входами i-x элементов ИЛИ группы, выходы которых соединены с входами записи 1-х блоков памяти первой и второй групп, где I ТТгп, m 2п, п-разрядность первого и второго счетчиков, информационные входы с первого по четвертый первой группы мультиплексора соединены с выходами первого, второго, третьего и четвертого триггеров, выход переполнения первого счетчика соединен с первым входом первого элемента И, второй вход которого соединен с D-входом второго триггера и образует вход разрешения анализатора, выход первого элемента И соединен с вторым входом второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены с тактовыми входами соответственно первого и второго счетчиков, выход переполнения второгосчетчика соединен с тактовым входом первого триггера, разрядные выходы первого и второго счетчиков соединены с адресными входами блоков памйти соответственно первой и второй групп, информационные выходы и входы 1-х блоков памяти первой и второй групп соединены с D-входами и инверсными выходами 1-х триггеров соответственно первой и второй групп, информационные

входы второй группы мультиплексора соединены с выходами соответствующих блоков памяти первой и второй групп, группа выходов мультиплексора является группой

информационных выходов анализатора, тактовые входы второго и третьего триггеров образуют соответственно входы Старт и Стоп анализатора, отличающийся тем, что, с целью увеличения быстродейстВИЯ и повышения достоверности контроля. в него введены третий элемент ИЛИ и группа мультиплексоров, причем первые информационные входы J-X мyльtиплeкcopoв группы подключены к выходам j-x разрядов

первого счетчика, где J - Гп, первые информационные входы мультиплексоров группы подключены к выходам j-x разрядов второго счетчика, вторые информационные входы мультиплексоров группы образуют

группу информационных входов анализатора, управляющие входы мультиплексоров группы объединены с первым входом третьего элемента ИЛИ и образуют второй вход задания режима, выходы 1-х мультиплексорое группы соединены с вторыми входами 1-х элементов И первой группы, выход третьего элемента ИЛИ подключен к первым входам элементов И первой группы, второй вход третьего элемента ИЛИ образует информационный вход анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1988 |

|

SU1580366A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для функционального контроля логических элементов | 1984 |

|

SU1226468A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования. Цель изобретения - увеличение быстродействия и повышение достоверности контроля. Устройство осуществляет контроль m выходов объекта за один цикл. При этом для каждого канала формируется отдельная т-разряд- ная сигнатура, что дает возможность сразу по окончании цикла контроля указать выходы объекта контроля, на которых проявилась неисправность. 1 ил.

| Сигнатурный анализатор | 1988 |

|

SU1580366A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1992-02-23—Публикация

1989-12-22—Подача