(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СХЕМ СРАВНЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Устройство для подключения источника информации к общей магистрали ЭВМ | 1990 |

|

SU1835547A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

| Устройство для ввода информации | 1983 |

|

SU1119000A1 |

| Устройство для имитации сбоев и неисправностей цифровой вычислительной машины | 1985 |

|

SU1265779A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1234841A1 |

| Устройство для контроля электромагнита | 1986 |

|

SU1348776A1 |

| Формирователь сигналов специальной формы | 1988 |

|

SU1550604A1 |

| Устройство для подсчета числа импульсов | 1987 |

|

SU1497742A2 |

| Пересчетное устройство с контролем | 1982 |

|

SU1019452A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств контроля электронных блоков дискретной автоматики и вычислительных машин.

Известно устройство для контроля схем, сравнения, содержащее два двоичных счетчика, выходы разрядов которых подключены к входам проверяемой схемы сравнения, триггер, элемент неравнозначности и индикатор, выходы переполнения триггера, один из выходов которого и выход проверяемой схемы сравнения соединены с входами элемента неравнозначности, выход . которого подключен к входу индикатора, причем входы обоих счетчиков соединены с шиной тактовых сигналов, а вход одного из них - с входной шиной предварительной установки 1.

Недостаток такого устройства заключается в том, что схема сравнения не контролируется на равность двух чисел, участвующих в сравнении.

Наиболее близким к изобретению является устройство для контроля схем сравнения, содержащее триггеры, логический блок, два счетчика, входы которых через соответствующие схеМэ1 И соединены с шиной тактовых сигналов , а выходы подключены к входам проверяемой схемы сравнения. Логический &ЛОК оценивает выходную информацию, выдаваемую схемой сравнения, и информацию о численных значениях двоичных чисел, записанных в счетчики, накопленную в триггерах, В зависимости от правильности работы схе10мы сравнения логический блок выдает сигнал Исправно или Неисправно Г2.

Однако в известном устройстве даже в случае неисправности схемы сравнения тактовые сигналы продолжают

15 поступать на счетчики импульсов, что затрудняет анализ и поиск места возникновения неисправности. Кроме того, неодновременность поступления сигналов триггеров и схемы сравнения

20 на логический блок может вызывать ложные срабатывания устройства.

Целью изобретения является построение устройства для проверки схем сравнения двоичных чисел, позволяющего

25 оперативно осуществлять диагностику схем сравнения, т,е, повышение диагностических возможностей устройства,

Поставленная цель достигается тем, что в устройство для контроля схем

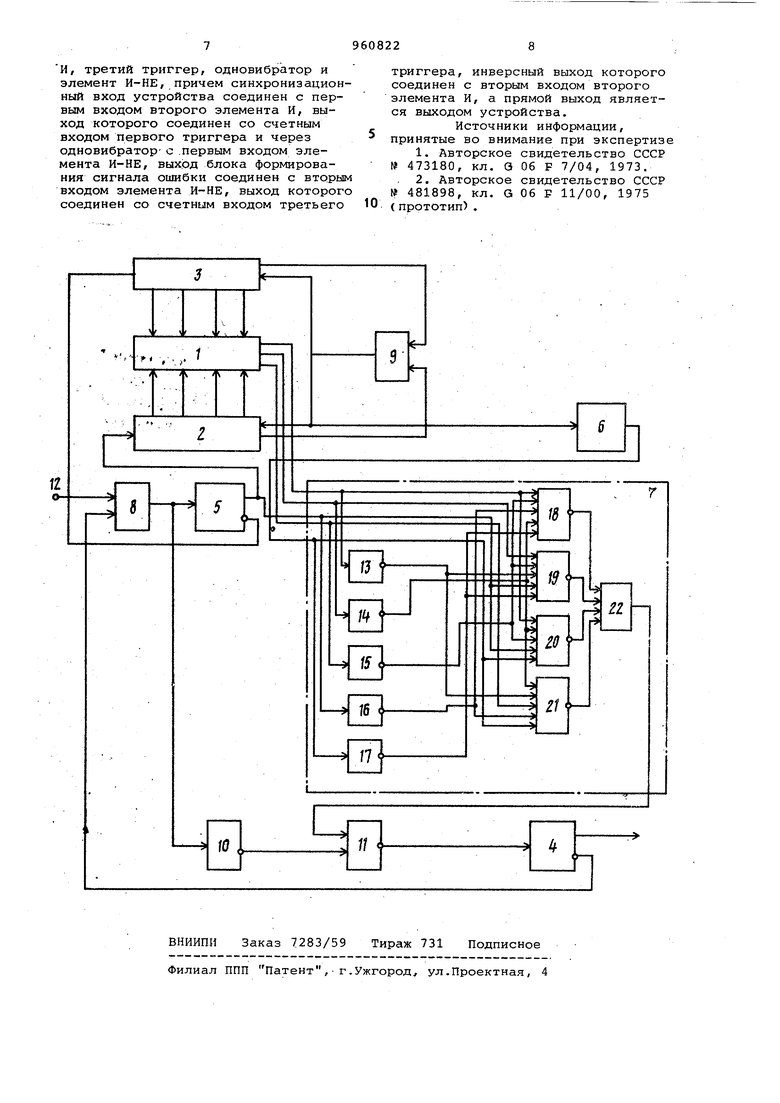

30 сравнения, содержащее первый и второй счетчики, первый элемент И, пер вый и второй триггеры и блок формир вания ошибок, причем прямой и инверсный выходы первого триггера сое динены соответственно со счетными входами первого и второго счетчиков выходы которых образуют первую и вт рую группу выходов устройства, выхо сигнала переполнения первого и второго счетчиков соединены соответственно с первым и вторым входами пер вого элемента И, выход которого сое динен с установочными входами перво го и второго счетчиков и со счетным входом второго триггера, выход которого соединен с первым входом блока формирования ошибки, второй, третий и четвертый входы которого соединены соответственно с единичным выходом первого триггера, с первым, вторым и третьим входами устройства, введегел второй элемент И, третий триггер, одновибратор и элемент И-НЕ, причем синхронизационный вход устройства соединен с первым входом второго элемента И, выход которого соединен со счетным входом первого триггера и через одновибратор с перввлм входом элемента И-НЕ, выход блока формирования сигнала ошибки соединен с вторым входом элемента И-НЕ,;; выход которого соединен со счетным входом третьего триггера, инверсный выход которого соединен с вторым входом второго элемента И, а прямой выход является вьрсодом устройства. На чертеже показана схема устройства для контроля схем сравнения Устройство содержит проверяемую схему 1 сравнения, первый и второй счетчики 2 и 3, первый, .второй и третий триггеры 4,5 и б, блок 7 фор мирования ошибок, второй и первый элементы И 8 и 9, одновибратор 10, элемент И-НЕ 11. Прямой и инверсный выходы триггера 5 подключены соответственно к входам счетчиков 2 и 3. Счетный вход триггера 5 соединен с выходом элемента ИЗ, первый вход которого подключен к шине тактовых сигналов 12, а второй вход - к инвареному выходу триггера 4. Выходы сигналов переполнения счетчиков 2 и 3 соединены с входами первого эле MeHTta И 9, выход которого подключен к в:||рдам обнуления, счетчиков 2 и 3 и к счетному входу триггера 6. Вы.хода счетчиков 2 и 3 соединены с входами проверяемой схемы 1 сравнения. Вход одновибратора 10 подключен к выходу второго элемента ИВ. Прямые выходы триггеров 5 и 6 и выходы проверяемой схемы 1 сравнения подключены к входам блока 7, выход которого подключен к входам элемент И-НЕ 11, второй вход. которого соединен с инверсным выходом одновибра тора 10, а выход подключен к входу установки в единичное состояние триггера 4, прямой выход которого является выходом устройства. БЛОК 7 формирования ошибок содержит пять элементов НЕ 13-17, четыре элемента И-НЕ 18-21 и элемент ИЛИ 22. Устройство работает следующим образом. Перед началом проверки счетчики 2и 3 и триггеры 4,5 и б устанавливаются в нулевое состояние сигналом Сброс (цепи сброса на схеме не показаны) . При этом второй элемент И 8 открыт и на выходе первого элемента И 9 существует сигнал логической единицы а схема 1 сравнения выдает на блок 7 сигнал Х1 (, где А и В числа в счетчиках 3 и 2 соответственно) . Логический блок 7 сравнивает сигнал XI с состоянием триггеров 5 и б (состояние СО - оба триггера в нулевом состоянии) и затем вьщает на вход элемента И-НЕ 11 сигнал Исправно (логический Нуль) при наличии сигнала XI или сигнал Неисправно логическая единица) при отсутствии сигнала XI. В,случае исправности схемы сравнения триггер .4 остается в нулевом состоянии (все триггеры устройства переключаются при подаче на их информационные входы перепада логическая единица - логический нуль) и с его инверсного выхода на вход второго элемента И 8 поступает сигнал логической единицы, т.е. элемент И 8 открыт для прохождения импульсов тактовой последовательности. Первый .тактовый импульс переключает триггер 5 в единичное состояние, в результате чего на входе счетчика 3возникает перепад логическая единица - логический нуль и в счетчик 3 записывается 1 (А 1, В 0). При этом состояние триггеров 5 и 6 10, а схема сравнения должна вьщать сигт нал Х2 (). Второй тактовый импульс переключает триггер 5 в нулевое состояние и перепад логическая единица - логический нуль возникает на входе счетчика 2, в который записывается 1 (, ). При этом состояние триггеров 5 и 6 00, а схема 1 сравнения должна выдать сигнал XI () . Третий тактовый импульс записывает 1 в счетчик 3 (, ) и переводит триггеры 5 и 6 в состояние 10. При этом схема 1 сравнения должна выдать сигнал Х2 () . Четвертый тактовый импульс записывает 1 в счетчик 2 (, ), что должно соответствовать сигналу схемы 1 сравнения XI и соответствует состоянию триггеров 5 и б 00. При этом заканчивается проверка младшего разряда схемы 1 сравнения, Проверка последующих разрядов производится аналогично, за исключением последнего разряда. При и полностью заполненных счетчиках 2 и 3 следующий тактовый импульс переводит триггер 5 в единичное состояние и записывает 1 в счетчик 3, в этом счетчике возникает переполнение и сигнал переполнения логическим нулем через элемент И 9 поступает на шины обнуления обоих счетчиков и на счетный вход триггера 6. Триггер .6 переключается в единичное состояние Возникает ситуация , при состоянии триггеров 5 и 6 11. При этом схема 1 сравнения должна выдать сигнал XI. Следующий тактовый импульс переводит триггеры 5 и 6 в состояние 01 и записьавает 1 в счетчик 2 (, ). При этом схема 1 сравнения дол на выдать сигнал ХЗ (). С приходом последующих импульсов Ьоследовательно возникают ситуации , ) , (, ) , (,) ит.д. с соответственным изменением состояний триггеров 5 и 6, а также выходного сигнала схемы 1 сравнения Для обеспечения правильной работы устройства при повторной проверке схемы 1 сравнения, при новом заполнении счетчиков 2 и 3 и при сле дую11ций икпупьс переводит триггер 5 в нулевое состояние и записывает 1 в счетчик 2. В этом счетчике возникает переполнение и сигнал переполн ния логическим нулем -через элемент И 9 поступает на шнны обнуления обо счетчиков и на счетный вход триггер и. Триггер переключается в нулевое состояние. Возникает ситуация , , при состоянии триггеров 5 и 6 00. При этом схема 1 сравнения должна выдать сигнал XI (А В), т.е. схема возвращается в исходное состо ние . 3 случае неисправности схемы сра нения триггер 4 перепадом логическ ехиница - логический нуль на входе У;тановки в единичное состояние переключается в. единичное состояние. При этом с инверсного выхода тригге 4 ыа-;вход элемента И 8 поступает си нал логического нуля, который блоки рует поступление на устройство такт Bbtx импульсов, чем зафиксируется во никающее состояние неисправности. Блок 7 строится в соответствии со с дующей таблицей состояний: При реализации одного -из приведенных четырех состояний на выходе логического блока возникает сигнал логического нуля. При отсутствии импульса одновибратора сигнал логического блока инвертируется элементом И-НЕ и поступает на вход установ ки в единичное состояние триггера 4 при наличии импульса одновибратора на выходы элемента И-НЕ всегда отсутствует сигнал логической единицы Таким образом, инфо млация об исправности или неисправности проверяемой схемы сравнения проходит на вход установки в единичное состояние триггера 4 лишь в отсутствие импульса одновибратора, а при наличии импульса одновибратора на выходе элемента И-НЕ всегда существует .сигнал логической единицы, что позволяет избежать ложных срабатываний устройства изза разнесения во времени сигйалов схемы 1 сравнения и триггеров 5 и 6. Длительность импульса одновибратора рекомендуется делать равной половине длительности тактаимпульсов тактовой последовательности, поступающих на вход устройства. . Таким образом, по .сравнению с известными техническими ранениями данное устройство при минимальных схемных затратах обеспечивает оперативную диагностику схем сравнения с момент тальной фиксацией возникшего состоя ния неисправности. Технический эффект выражается в повышении стабильности и упрощении работы устройства. Формула изобретения Устройство для контроля схем сравнения, содержащее первый и второй счетчики, первый элемент И, первый и второй триггеры и блок формирования ошибок, причем прямой и инверсный выходы первого триггера соединены соответственно со счетными входами первого и второго счетчиков, выходы которых образуют первую и вторую группу выходов устройства, выходы сигнала переполнения первого и второго счетчика соединены соответственно с nepBEJM и вторым входами первого элемента И, выход которого соединен с установочными входами первого и второго счетчиков и со счетаам вводсж второго триггера, выход которого соединен с первым входом блока формирования ошибки, второй, третий и четвертый входы которого соединены соответственно с единичным выходом первого триггера, с первым, вторым и третьим входами устройства, отлич ающее ся тем, что, с целью повышения диагностических свойств, оно содержит второй элемент

И, третий триггер, одновибратор и элемент И-НЕ, причем синхронизационный вход устройства соединен с первым входом второго элемента И, выход которого соединен со счетным входом первого триггера и через одновибратор с .первым входом элемента И-НЕ, выхрд блока формирования сигнала ошибки соединен с вторым входом элемента И-НЕ, выход которого соединен со счетным входом третьего

триггера, инверсный выход которого соединен с вторым входом второго элемента И, а прямой выход является выходом устройства.

Источники информации, принятые во внимание при экспертиз

(прототип).

Авторы

Даты

1982-09-23—Публикация

1979-11-12—Подача