Изобретение относится к вычислительной технике и может быть использовано при отработке оборудования и программ, выполняющих контроль и диагностирование неисправностей в реальном масштабе -времени.

Целью изобретения является расширение функциональных возможностей устройства за счет возможности имитации серии сбоев.

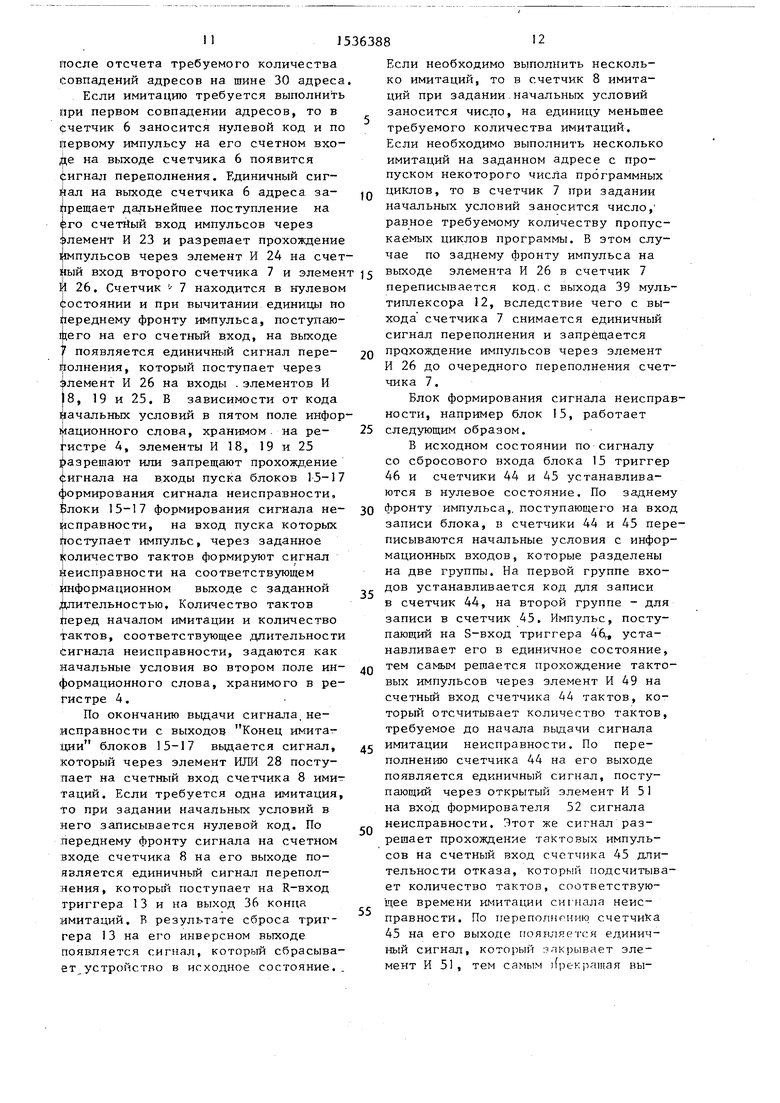

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока формирования сигнала неисправности; на фиг.З - функциональная схема примера реализа ции блока автоматического задания неисправностей; на фиг.4 и 5 - временные диаграммы, поясняющие работу устройства.

Устройство для имитации неисправностей (фиг.1) содержит первый 1, второй 2 и третий 3 регистры адреса, первый 4 и второй 5 регистры кода, первый 6 иг второй 7 счетчики адреса, счетчик 8 имитаций, первый 9 и рой 30 блоки сравнения, мультиплексоры адреса 11 и кода 12, триггер 13, одновибратор 14, первый - третий блоки 15-17 формирования сигнала неисправности, первый - десятый элементы И 18-26, первый 27 и второй 28 элементы ИЛИ и переключатель 29. На схеме устройства также обозначены первая шина 30 адреса и вход 31 синхронизации первой шины адреса, вторая шина 32 адреса и вход 33 синхронизации второй шины адреса, шины 34 данных, вход 35 пуска устройства и выход 36 конца имитаций устройства Кроме того, обозначены первая 37, вторая 38, третья 39, четвертая 40 и пятая 41-43 группы выходов мультиплексора 12 кода.

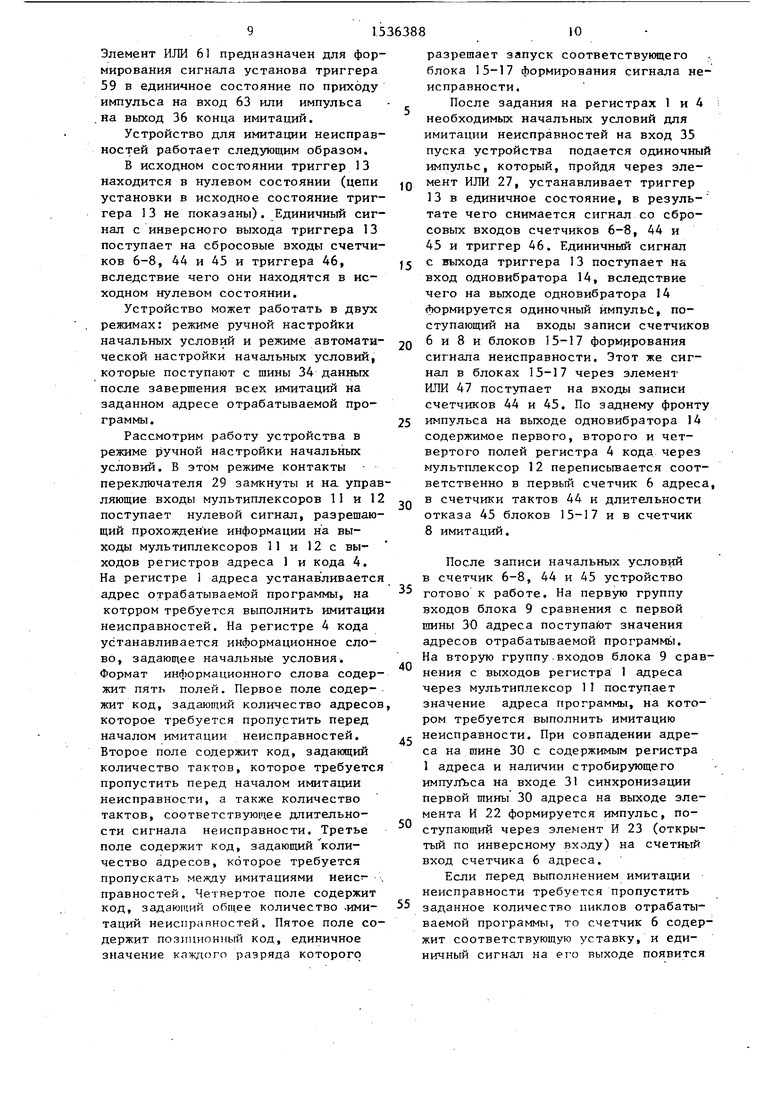

Каждый из трех блоков 15-17 формирования сигнала неисправности, например блок 15 (фиг.2), содержит счетчик 44 тактов, счетчик 45 длительности отказа, триггер 46, первый 47 и второй 48 элементы ИЛИ, первый третий элементы И 49-51 и формирователь 52 импульсов, вход 53 тактовых импульсов.

Блок 54 автоматического задания неисправностей (фиг.З) содержит блок 55 памяти (ПЗУ), регистр 56 годреса, счетчик 57 адреса, счетчик 58 двух импульсов, триггер 59. элемент И 60,

10

15

20

25

363884

элемент ИЛИ 61, вход 62 тактовых импульсов и вход 63 пуска блока 54.

Регистры адреса 1 и кода 4 предназначены для задания начальных условий в режиме ручной настройки. Б этом режиме начальные условия -задаются тумблерами вручную перед началом работы. Регистры адреса 2 и кода 5 предназначены для приема и хранения начальных условий в режиме автоматической настройки, которые поступают с шины 34 данных. Регистр 3 адреса предназначен для хранения эталонного кода, соответствующего адресу рассматриваемого устройства на шине 32 адреса (на шине адреса может находиться несколько устройств например, инструментальная мини-ЭВМ, блоки памяти, устройства ввода-вывода и т.п.).

Счетчик 6 адреса предназначен для подсчета количества адресов, которое требуется пропустить перед началом имитации неисправности. Счетчик 7 . адреса предназначен для подсчета количества адресов, которое требуется пропустить между имитациями неисправностей. Счетчик 8 имитаций предназначен для подсчета общего количества неисправностей на заданном адресе в регистре 1 или регистре 2. Счетчики 6-8 могут быть реализованы, например, на стандартных микросхемах 155ИЕ7.

Блок 9 сравнения предназначен для сравнения информации на шине 30 адреса с информацией, поступающей с выходов мультиплексора 11 адреса. Блок 10 сравнения предназначен для сравнения информации на шине 32 адреса с эталонным кодом, заданном на регистре 3 адреса.

Мультиплексор 11 адреса предназначен для подключения к второй группе входов блока 9 сравнения выходов регистра 1 или регистра 2 в зависимости от положения переключателя 29 (при подключении к общей шине на выходы мультиплексора 11 поступает информация с выходов регистра 1, при разомкнутом положении переключателя - с выходов регистра 2, разомкнутое состояние переключателя воспринимается мультиплексором как в ТТЛ-логике - логической 1).

Мультиплексор 12 кода предназначен для подключения к его выходам выходов регистра 4 или регистра 5 в

30

35

40

45

50

55

зависимости от положения переключа- теля 29 (при подключении к общей шине на выходы мультиплексора 12 поступает информация с выходов регистра 4; при разомкнутом положении переключателя - с выходов регистра 5

Выходы мультиплексора 12 кода делятся на пять групп. На первой группе выходов 37 устанавливается код для задания количества адресов, которое требуется пропустить перед началом имитации неисправностей. На второй группе выходов 38 устанавливается код для задания количества тактов, которое требуется пропустить перед началом имитации неисправности и количество тактов, соответствующее длительности сигнала неисправности. На третьей группе выходов 39 устанавливается код для задания количества адресов, которое требуется пропустить между имитациями неисправностей, На четвертой группе выходов 40 устанавливается код, задающий общее количество неисправностей. На пятой группе выходов 41-43 устанавливается позиционный код, единичное значение каждого разряда которого разрешает запуск соответствующего блока 15-17 формирования сигнала не- исправности.

Мультиплексоры 11 и 12 могут быть реализованы, например, на стандартных интегральных микросхемах 55КП11 Триггер 13 предназначен для запуска устройства и его сброса после завершения работы на заданных начальных условиях. Одновибратор 14 предназначен для формирования единичного импульса, стробирующего запись начальных условий в счетчики 6-8, 44 и 45 Одновибратор 14 может быть реализован, например, на стандартной интегральной микросхеме 155АГ1. Блоки 15-17 предназначены для формирования сигнала неисправности через заданное количество тактов с заданной длительностью. Элементы И 18, 19 и 25 предназначены для формирования импульса пуска, запускающего блоки 15-17 формирования сигналов неисправности. Элемент И 20 предназначен для формирования импульса записи в регистр 2 адреса информации, поступающей с шины 34 данных при четном адресе на шине 32 адреса и совпадении старших разрядов с эталонным кодом регистра 3. Элемент И 21 предназначен для

0

5

0

формирования импульса записи в регистр 5 кода информации, поступающей с шины 34 данных при нечетном адресе на шине 32 адреса и совпадении старших разрядов с эталонным кодом регистра 3. Элемент И 22 предназначен для формирования импульса соответствующего наличия на шине 30 адреса, на котором требуется выполнить имитацию неисправности. Элемент И 32 предназначен для блокировки поступления импульсов на счетный i вход счетчика 6 после отсчета заданного количества адресов, которое требуется пропустить перед началом имитации неисправностей. Элемент И 24 предназначен для блокировки поступления импульсов на счетный вход счетчика 7 и первый вход элемента И 26 до момента отсчета заданного-количества адресов, которое требуется пропустить перед началом имитации неисправности. Элемент И 26 предназначен 5 для формирования импульса при первой имитации, а также при отсчете количества адресов, которое требуется пропустить между имитациями неисправностей. Элемент ИЛИ 27 предназначен для формирования сигнала пуска устройства, устанавливающего триггер 13 в единичное состояние. Элемент ИЛИ 28 предназначен для формирования сигнала, передний фронт которого соответствует концу очередной имитации неисправности.

Переключатель 29 предназначен для задания режима работы устройства. При замыкании контактов переключателя задается режим ручной настройки начальных условий. Разомкнутое состояние переключателя задает режим автоматической настройки начальных условий, которые поступают с шины 34 данных после завершения всех имитаций на заданном адресе программы. Разомкнутое состояние переключателя воспринимается мультиплексорами 11 и 12 как- в ТТЛ-логике - логической 1П.

Счетчик 44 (фиг.2) предназначен для подсчета количества тактов, которое тре буется пропустить перед началом имитации неисправности. Счетчик 45 предназначен для подсчета количества тактов, которое соответствует длительности сигнала имитации неисправности. Счетчики 44 и 45 могут быть реализованы, на0

5

0

5

0

5

пример, на стандартных микросхемах 155ИЕ7. Триггер 46 предназначен для Формирования сигнала пуска блока 15 формирования сигнала неисправности после прихода импульса на вход триггера; Элемент ИЛИ А7 предназначен для формирования сигнала аписи в счетчики 44 и 45 информации, поступакяцей с второй группы выходов 38 мультиплексора 12. Элемент ИЛИ 48 предназначен для формирования сигнала сброса триггера 46 |при наличии сигнала на входе сброса лока 15 или по наличию сигнала на выходе элемента И 49. Элемент И 49 предназначен для блокировки поступ- ения импульсов на счетный вход счетчика 44 до прихода сигнала на вход пуска блока 15 и после отсчета количества тактов до момента начала имитации неисправности Элемент И 50 предназначен для блокировки по- |Ступления импульсов на счетный вхо счетчика 45 до появления единичного сигнала на выходе счетчика 44 и пбс ле появления единичного сигнала на выходе счетчика 45. Элемент И 51 предназначен для формирования сигнала, управляющего формирователем 52 сигнала неисправности. Формировател 52 предназначен для формирования сигнала неисправности,, согласующегося с параметрами, соответствующими требованиям отрабатываемого оборудования. Формирователь 52 при выдаче сигнала неисправности на магистрали отрабатываемой ЭВМ может быть реализован,, например, на стандартных микросхемах с открытым коллектором (155ЛА7), или микросхемах с тремя состояниями на выходе (589АП16).

Блок 54 автоматического задания | неисправностей предназначен для организации в реальном масштабе времени имитаций сбоев или отказов на разных участках отрабатываемой программы и (или) в разных каналах отрабатываемого оборудования путем автоматического задания новых начальных условий после завершения очередной имитации по приходу импулса с выхода 36 конца имитаций устройства.

В качестве блока 54 может быть использована инструментальная или технологическая ЭВМ (любая стандартная мини- или микроЭВМ); , может быт

5

0

5

0

5

0

5

0

5

использована непосредственно отрабатываемая ЭВМ (в этом случае адресные шины 32, 33 и 30, 31 объединяются в одну шину, а автоматическое задание начальных условий осуществляется по отладочной программе, управление которой передается по прерыванию после выдачи сигнала с выхода 36 конца имитаций). Использование инструментальной ЭВМ или отладочной программы позволяет легко осуществлять всевозможный набор неисправностей при работе в реальном масштабе времени. Кроме того, блок 54 автоматического задания неисправностей может быть реализован в виде специального устройства, представленного на фиг.З.

.Блок 55 памяти предназначен для хранения значений начальных условий. В четных адресах блока 55 хранятся адреса, на которых имитируется неисправность, в нечетных - коды, задающие количество пропусков адресов до начала имитации, количество тактов до начала имитации, количество, тактов, соответствующее длительности имитации, количество пропусков адресов между имитациями, общее количество имитаций и каналы, в которых требуется имитация.

Блок 55 памяти может быть реализован, например, на стандартных микросхемах 155РЕЗ. Регистр 56 адреса предназначен для хранения старших разрядов адреса, на который настроено предлагаемое устройство (фиг.1). Счетчик 57 адреса предназначен для перебора адресов блока 55 памяти, с выхода которого на шину 34 данных выдаются начальные условия, задающие имитации неисправностей. Счетчик 58 предназначен для подсчета двух импульсов на выходе элемента И 60, которые стробируют выдачу из блока 54 по шине 34 двух информационных слов, содержащих начальные условия. Счетчики 57 и 58 могут быть реализованы на 1К-триггерах, например, на стандартных микросхемах 155TBJ. Триггер 59 предназначен для запуска блока 54 и его останова после выдачи двух информационных слов на шину 34 данных. Элемент И 60 предназначен для блокировки поступления тактовых импульсов во время ожидания импульса пуска на входе 63 или импульса на выходе 36 конца имитаций устройства.

915

Элемент ИЛИ 61 предназначен для формирования сигнала установа триггера 59 в единичное состояние по приходу импульса на вход 63 или импульса на выход 36 конца имитаций.

Устройство для имитации неисправностей работает следующим образом.

В исходном состоянии триггер 13 находится в нулевом состоянии (цепи установки в исходное состояние триггера 13 не показаны). Единичный сигнал с инверсного выхода триггера 13 поступает на сбросовые входы счетчиков 6-8, 44 и 45 и триггера 46, вследствие чего они находятся в исходном нулевом состоянии.

Устройство может работать в двух режимах: режиме ручной настройки начальных условий и режиме автоматической настройки начальных условий, которые поступают с шины 34 данных после завершения всех имитаций на заданном адресе отрабатываемой программы.

Рассмотрим работу устройства в режиме ручной настройки начальных условий. В этом режиме контакты переключателя 29 замкнуты и на управляющие входы мультиплексоров 11 и 12 поступает нулевой сигнал, разрешающий прохождение информации на выходы мультиплексоров 11 и 12 с выходов регистров адреса 1 и кода 4. На регистре 1 адреса устанавливается

адрес отрабатываемой программы, на котрром требуется выполнить имитации неисправностей. На регистре 4 кода устанавливается информационное слово, задающее начальные условия. Формат информационного слова содержит пять полей. Первое поле содержит код, задающий количество адресов которое требуется пропустить перед началом имитации неисправностей. Второе поле содержит код, задающий количество тактов, которое требуется пропустить перед началом имитации неисправности, а также количество тактов, соответствующее длительности сигнала неисправности. Третье поле содержит код, задающий количество адресов, которое требуется пропускать между имитациями неисправностей. Четвертое поле содержит код, задающий общее количество -имитаций неисправностей. Пятое поле содержит позиционный код, единичное значение каждого разряда которого

0

5

388

0

5

0

10

разрешает запуск соответствующего блока 15-17 формирования сигнала неисправности.

После задания на регистрах 1 и 4 необходимых начальных условий для имитации неисправностей на вход 35 пуска устройства подается одиночный импульс, который, пройдя через элемент ИЛИ 27, устанавливает триггер 13 в единичное состояние, в результате чего снимается сигнал со сбросовых входов счетчиков 6-8, 44 и 45 и триггер 46. Единичный сигнал с выхода триггера 13 поступает на вход одновибратора 14, вследствие чего на выходе одновибратора 14 Лормируется одиночный импульс, поступающий на входы записи счетчиков 6 и 8 и блоков 15-17 формирования сигнала неисправности. Этот же сигнал в блоках 15-17 через элемент ИЛИ 47 поступает на входы записи счетчиков 44 и 45. По заднему фронту импульса на выходе одновибратора 14 содержимое первого, второго и четвертого полей регистра 4 кода через мультплексор 12 переписывается соответственно в первый счетчик 6 адреса, в счетчики тактов 44 и длительности отказа 45 блоков 15-17 и в счетчик 8 имитаций.

После записи начальных условий в счетчик 6-8, 44 и 45 устройство

готово к работе. На первую группу входов блока 9 сравнения с первой шины 30 адреса поступают значения адресов отрабатываемой программы. На вторую группу входов блока 9 сравнения с выходов регистра 1 адреса через мультиплексор 11 поступает значение адреса программы, на котором требуется выполнить имитацию неисправности. При совпадении адреса на шине 30 с содержимым регистра 1 адреса и наличии стробирующего импухГЬса на входе 31 синхронизации первой шины 30 адреса на выходе элемента И 22 формируется импульс, поступающий через элемент И 23 (открытый по инверсному входу) на счетный вход счетчика 6 адреса.

Если перед выполнением имитации неисправности требуется пропустить

заданное количество циклов отрабатываемой программы, то счетчик 6 содержит соответствующую уставку, и единичный сигнал на его выходе появится

После отсчета требуемого количества (овладений адресов на шине 30 адреса

Если имитацию требуется выполнить при первом совпадении адресов, то в Счетчик 6 заносится нулевой код и по Первому импульсу на его счетном вхо- е на выходе счетчика 6 появится |:игнал переполнения. Единичный сигнал на выходе счетчика 6 адреса запрещает дальнейшее поступление на го счетный вход импульсов через элемент И 23 и разрешает прохождение импульсов через элемент И 24 на счетный вход второго счетчика 7 и элемен И 26. Счетчик 7 находится в нулевом состоянии и при вычитании единицы по переднему фронту импульса, поступаю- цего на его счетный вход, на выходе 7 появляется единичный сигнал переполнения, который поступает через элемент И 26 на входы элементов И

8, 19 и 25. В зависимости от кода начальных условий в пятом поле информационного слова, хранимом на регистре 4, элементы И 18, 19 и 25 разрешают или запрещают прохождение сигнала на входы пуска блоков 15-17 нормирования сигнала неисправности, рлоки 15-17 формирования сигнала не- справности, на вход пуска которых поступает импульс, через заданное Количество тактов формируют сигнал Неисправности на соответствующем информационном выходе с заданной Длительностью, Количество тактов Јгеред началом имитации и количество Тактов, соответствующее длительности Сигнала неисправности, задаются как начальные условия во втором поле информационного слова, хранимого в регистре 4.

По окончанию выдачи сигнала.неисправности с выходов Конец имитации блоков 15-17 выдается сигнал, Который через элемент ИЛИ 28 поступает на счетный вход счетчика 8 имитаций. Если требуется одна имитация, То при задании начальных условий в него записывается нулевой код. По Переднему фронту сигнала на счетном аходе счетчика 8 на его выходе появляется единичный сигнал переполнения, который поступает на R-вход триггера 13 и на выход 36 конца имитаций. В результате сброса триггера 13 на его инверсном выходе появляется сигнал, который сбрасывает устройство в исходное состояние. .

0

5

0

5

0

5

0

5

0

5

Если необходимо выполнить несколько имитаций, то в счетчик 8 имитаций при задании начальных условий заносится число, на единицу меньшее требуемого количества имитаций. Если необходимо выполнить несколько имитаций на заданном адресе с пропуском некоторого числа программных циклов, то в счетчик 7 при задании начальных условий заносится число, равное требуемому количеству пропускаемых циклов программы. В этом случае по заднему фронту импульса на выходе элемента И 26 в счетчик 7 переписывается код с выхода 39 мультиплексора 12, вследствие чего с выхода счетчика 7 снимается единичный сигнал переполнения и запрещается прохождение импульсов через элемент И 26 до очередного переполнения счетчика 7.

Блок формирования сигнала неисправности, например блок 15, работает следующим образом.

В исходном состоянии по сигналу со сбросового входа блока 15 триггер 46 и счетчики 44 и 45 устанавливаются в нулевое состояние. По заднему фронту импульса, поступающего на вход записи блока, в счетчики 44 и 45 переписываются начальные условия с информационных входов, которые разделены на две группы. На первой группе входов устанавливается код для записи в счетчик 44, на второй группе - для записи в счетчик 45. Импульс, поступающий на S-вход триггера 46,, устанавливает его в единичное состояние, тем самым решается прохождение тактовых импульсов через элемент И 49 на счетный вход счетчика 44 тактов, который отсчитывает количество тактов, требуемое до начала выдачи сигнала имитации неисправности. По переполнению счетчика 44 на его выходе появляется единичный сигнал, поступающий через открытый элемент И 51 на вход формирователя 52 сигнала неисправности. Ттот же сигнал разрешает прохождение тактовых импульсов на счетный вход счетчика 45 длительности отказа, который подсчитывает количество тактов, соответствующее времени имитации сигнала неисправности. По переполнению счетчика 45 на его выходе появляется единичный сигнал, который закрывает элемент И 51, тем самым ifpei- рашая вы

дачу сигнала имитации неисправности Этот же сигнал закрывает элемент И 50, прекращая поступление тактовых импульсов на счетный вход счетчика 45, и выдается на вход блока 15 сигнал Конец имитации. По заднему фронту сигнала на выходе элемента И 51 в счетчики 44 и 45 переписываютс начальные условия, после чего блок 15 готов к формированию очередного сигнала неисправности.В режиме автоматического задания начальных условий устройство работает аналогично, е той разницей, что задание и начальных условий происходит путем записи начальных условий с шины 34 данных в регистр 2 адреса и регистр 5 кода, причем в этом режиме контакты переключателя 29 разомкнуты, что соответствует единичному сигналу на управляющих входах мультиплексоров, вследствие чего информация с выходов регистров 2 и 5 поступает на выходы,мультипле соров 11 и 12. Запись начальных, условий в регистры 2 и 5 происходит следующим образом. Устройство на второй шине 32 адреса имеет два смежных адреса, четный и нечетный. Регистру 2 адреса соответствует четный адрес, регистру 5 кода - нечетный адрес. Запись начальных условий начинается с адресации устройства по четному адресу. При наличии четного адреса на шине 32 и сравнении блоком 10 старших разрядов адреса с эталонным кодом регистра 3 адреса по сигналу на входе 33 синхронизаци адреса на выходе элемента И 20 появляется импульс, по переднему фронту которого происходит запись в регистр 2 значения адреса, на котором требуется имитация неисправности.

Далее на шине 32 задается нечетный адрес устройства, при распознавании которого на выходе элемента И 21 появляется импульс, попереднему фронту которого в регистр 5 записывается информационное слово, содержащее начальные условия. Этот же импульс через элемент ИЛИ 27 поступает на S-вход триггера 13, вследствие чего устройство начинает работу аналогично описанному режиму рунной настройки. По завершению заданного количества имитаций на выходе 36 конца имитаций формируется импульс, означающий готовность

0

5

0

5

0

5

0

устройства для приема очередных значений начальных условий.

Блок 54 автоматического задания неисправностей работает- следующим образом.

В исходном состоянии счетчик 57 адреса, счетчик 58 и триггер 59 установлены в нулевое состояние (цепи сброса не показаны). Запуск блока 54 происходит при поступлении на вход 63 одиночного импульса, по которому триггер 59 устанавливается в единичное состояние, разрешая тем самым поступление тактовых импульсов на счетные входы счетчиков 57 и 58 и выход 33 синхронизации адреса. По переднему фронту первого тактового импульса происходит выдача из блока 55 памяти содержимого, хранимого .по нулевому адресу, на шину 34 данных. По заднему фронту тактового импульса наращивается содержимое счетчика 57 адреса и счетчика 58;

По переднему фронту второго тактового импульса из блока 55 памяти на шину 34 данных выдается содержимое, хранимое по первому адресу. По заднему фронту второго тактового импульса наращивается содержимое счетчика 57 адреса, а на выходе счетчика 58 появляется единичный сигнал,, который сбрасывает триггер 59, вслед-. ствие чего закрывается элемент И 60, сбрасывается счетчик. 58.и блок 54 переходит в ожидание поступления импульса на вход 36, который запускает блок 59 для выдачи очередных двух информационных слов на шину данных.

Формула изобретения

Устройство для имитации неисправностей, содержащее первый и второй регистры адреса, первый и второй регистры кода, счетчик адреса, первый и второй блоки формирования сигнала неисправности, триггер, первый и второй блоки сравнения, первый и второй элементы И, причем первая шина адре- са устройства соединена с первой группой входов первого блока сравнения, выходы первого и второго элементов И соответственно соединены с входами пуска первого и второго блоков формирования сигнала неисправности, . выходы которых являются первым н вторым информационными выходамиустройства, отличающееся тем,

что, с целью расширения функциональ- ных возможностей устройства за счет возможности имттации серии сбоев, в устройство введены третий регистр адреса, мультиплексор адреса, мультиплексор кода, второй счетчик адреса, счетчик имитаций, третий блок формирования.сигнала неисправности, одновибратор, два элемента ИЛИ, семь элементов И и переключатель, причем группа выходов третьего регистра адреса соединена с первой группой входов второго блока сравнения, вторая группа входов которого соединена с второй шиной адреса устройства, а выход - с вторыми входами третьего - и четвертого элементов И, первые входы которых соединены с входом синхронизации второй шины адреса устройства, младший разряд шины адреса устройства соединен-с инверсным входом третьего элемента И и с третьим входом четвертого элемента И, выходы третьего и четвертого элементов И соединены соответственно с входами записи второго регистра адреса и второго регистра кода, группы информационных входов которых соединены с шиной данных устройства, выходы первого и второго регистров адреса соответственно соединечы с первой и второй группами информационных входов мультиплексора адреса, выходы которого соединены с второй группой входов первого блока сравнения, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с входом синхронизации первом шины адреса устройства, а выход пятого элемента И соединен с первыми входами шестого и седьмого элементов И, тактовые входы блоков формирования сигнала неисправности подключены к тактовому входу устройства, БХОД пуска устройства и выход четвертого элемента И через первый элемент ИЛИ соединен с S-входом триггера, прямой выход которого соединен с входом одновибратора, а инверсный выход - со сбросовыми входами первого и второго счетчиков адреса, счетчика имитаций и сбросовыми входами трех блоков формирования .сигнала неисправности, выход одновибратора соединен с входами записи первого счетчика адреса, счетчика имитаций и блоков формирования сигнала неисправности,

0

5

0

5

0

5

О

5

0

5

управляющие входы мультиплексоров адреса и кода соединены с подвижным контактом переключателя, неподвижный контакт которого соединен с шиной нулевого потенциапа устройства, выходы первого и второго регистров кода соединены соответственно с первой и второй группами информационных входов мультиплексора кода, первая - четвертая группы выходов которого соединены соответственно с группой информационных входов первого счетчика адреса, группами информационных входов блоков формирования сигнала неисправности, группой информационных входов второго счетчика адреса и группой информационных входов счетчика имитаций, пятая группа выходов мультиплексора кода соединена с первыми входами первого, второго и восьмого элементов И, выход шестого элемента И соединен со счетным входом первого счетчика адреса, выход которого соединен с инверсным входом шестого элемента И и вторым входом седьмого элемента И, выход которого соединен с первым входом девятого элемента И и со счетным входом второго счетчика адреса, выход которого соединен с вторым входом девятого элемента И, выход которого соединен с входом записи второго счетчика адреса и с вторыми входами первого, второго и восьмого элементов И, выход восьмого элемента И соединен с входом пуска третьего блока формирования сигнала .неисправности, выход которого является третьим информационным выходом устройства, выходы Конец имитации трех блоков формирования сигнала неисправности через второй элемент ИЛИ соединены со счетным входом счетчика имитаций, выход которого является выходом конца имитаций устройства и соединен с R-входом триггера, причем каждый блок формирования сигнала неисправности содержит первый, второй и третий элементы И, первый и второй элементы ИЛИ, счетчик тактов, счетчик длительности отказа, триггер и формирователь импульсов, причем вход пуска блока формирования сигнала неисправности соединен с S- входов триггера, R-вход которого соединен с выходом первого элемента ИЛИ, а выход - с первым входом первого элемента И, вход записи блока

1715

Лорнирования сигнала неисправности соединен с первым входом второго элемента ИЛИ, выход которого соедине с входами записи счетчика тактов и счетчика длительности отказа, группы информационных входов которого соединены с группами информационных входов блока формирования сигнала неисправности, сбросовый вход которого соединен с первым входом первого элемента ИЛИ, со сбросовыми входами счетчика длительности отказа и счетчика тактов, выход которого соединен с первым входом второго элемента И, с инверсным входом первого элемента И и с первым входом третьего элемента И, вход тактовых импульсов блока

18

формирования сигнала неисправности соединен с вторыми входами первого и второго элементов И, выходы которых соответственно соединены со счетными входами счетчика такта и счетчика длительности отказа, выход счетчика длительности отказа является выходом Конец имитации блока формирования сигнала неисправности и соединен с инверсными входами второго и третьего элементов И, выход третьего элемента И соединен с вторыми входами первого и второго элементов ИЛИ и с входом формирователя импульсов, выход которого является информационным выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1520499A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для программного управления | 1988 |

|

SU1520480A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

Изобретение относится к вычислительной технике и может быть использовано при отработке оборудования и программ. Цель изобретения состоит в расширении функциональных возможностей устройства за счет возможности имитации серии сбоев. Устройство содержит первый 1, второй 2 и третий 3 регистры адреса, первый 4 и второй 5 регистры кода, первый 6 и второй 7 счетчики адреса, счетчик 8 имитаций, первый 9 и второй 10 блоки сравнения, мультиплексор 11 адреса и мультиплексор 12 кода, триггер 13, одновибратор 14, первый, второй, третий блоки 15-17 формирования сигнала неисправности, первый - девятый элементы И 18-26, первый 27 и второй 28 элементы ИЛИ и переключатель 29. Устройство позволяет автоматически задавать начальные условия для имитации отказов в разных каналах и на разных участках отрабатываемой программы в реальном масштабе времени. 5 ил.

С6Р

фиг. 2

32

33 J4

JL

TL

П

1Ш1АШ11Ш1ЛШҐ1Шт

n

TL

П

Л.

П

П

JL.

JL

JL

П

JUL

JTJL

JUL

JUL

JUL

ЛЛ

n

51

П

TL

П

П

П

Шт

JL.

JL

JL

П

JTJL

JUL

JUL

JUL

ЛЛ

n

| Устройство для имитации неисправностей | 1985 |

|

SU1273933A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1283775A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-26—Подача