Изобретение относится к вычислительной технике и может быть использовано для проверки и отладки программно-аппаратных средств контроля, диагностики и восстановления работоспособности цифровых вычислительных устройств для имитации различных видов сбоев и неисправностей в заданные моменты времени в процессе их работы .

Цель изобретения - расширение функциональных возможностей устройства за счет формирования сигнала ошибки любой длительности.

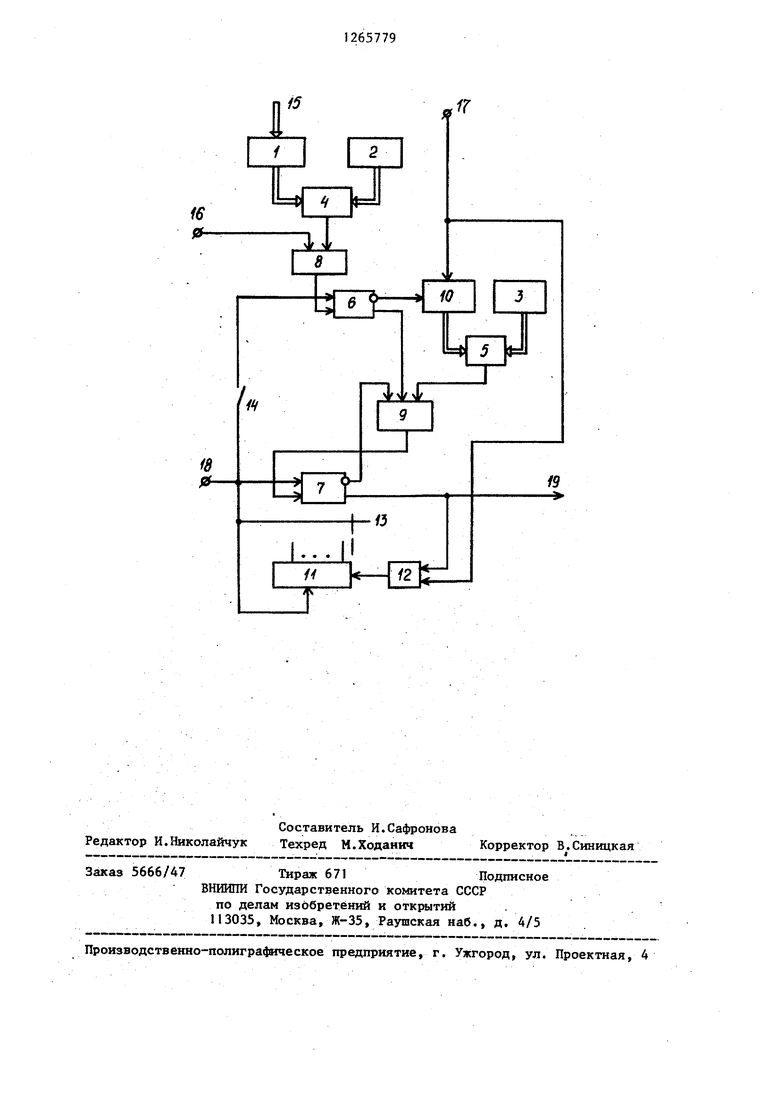

На чертеже представлена структурная схема устройства.

Устройство содержит первый 1 и второй 2 регистры адреса, регистр 3 тактов, схему 4 сравнения адреса, схему 5 сравнения тактов, триггеры 6 и 7, элемент ИЛИ 8, первый элемент И 9, счетчик 10 тактов, счетчик 11, второй элемент И 12, второй 13 и первый 14 переключатели, адресный выход 15 ЦВМ, стробирующий вход 16 устройства, тактовый вход 17 устройства, вход 18 начальной установки и информационный выход 19.

Устройство работает следующим образом.

Переключатель 14 замкнут. На вход 18 устройства подается сигнал обнуления, устанавливающий в нулевое состояние первый 6 и второй 7 триггеры и счетчик 11. При этом единичный сигнал с инверсного выхода триггера 6 устанавливает в нулевое состояние счётчик 10 тактов, а нулевой сигнал с прямого выхода триггера 6 поступает на второй вход элемента И 9, на третий вход которого поступает единичный сигнал с инверсного выхода второго триггера 7.

На первом регистре 1 адреса фиксируются текущие адреса команд и программ, вьшолняемых ЦВМ, при совпадении одного из которых с адресом, заданным во втором регистре 2 адреса, срабатьшает схема 4 сравнения, выходной сигнал которой через элемент ИЛИ В устанавливает первый триггер 6 в единичное состояние, при котором на его прямом выходе и, следовательно, на втором входе элемента И 9 появляется логическая 1. Сигнал обнуления, поступающий на первый счетчик 10 с инверсного выхода триггера 6, снимается и первый счетчик 10 начйнает считать импульсы, поступающие на тактовый вход 17 устройства. При совпадении кода, посчитанного на первом счетчике 10, с кодом задержки, заданным на регистре 3, срабатывает схема 5 сравнения, выходной сигнал с которой, проходя через элемент И 9, устанавливает второй триггер 7 в единичное состояние. При этом на его инверсном выходе устанавливается логический О, который поступает на третий вход элемента И 9 и запрещает дальнейшее прохождение сигналов через него. Единичный сигнал с прямого

5 выхода триггера 7 поступает на выход 19 устройства, что соответствует началу появления сигнала ошибки. Одновременно этот же сигнал поступает на первый вход элемента И 12 и разрешает прохождение импульсов с тактового входа 17 устройства через элемент И

12на счетный вход счетчика 11. Счетчик 11 и второй переключатель

13определяют вид вырабатьтаемого сигнала ошибки, соответствующего имитации неисправности или сбоя, а также длительность сбоя. При работе устройства в режиме формирования сигналов ошибки для имитации сбоев малой

0 длительности подвижный контакт переключателя 13 замкнут на выход младшего разряда счетчика 11. После начала счета на выходе младшего разряда счетчика 11 появляется единичный сиг5 нал, который поступает на вход обнуления счетчика 11 и второго триггера 7. При этом на прямом выходе второго триггер 7 и, соответственно, на выходе 19 устройства устанавливается

0 нулевой сигнал, который определяет момент окончания имитируемого сбоя. Этот же сигнал запрещает дальнейшее прохождение счетных импульсов через элемент И 12 на счетчик 11. В случае

5 имитации однократного сбоя переключатель 14 остается в замкнутом положении. При этом единичный сигнал с выхода счетчика 11 также поступает на вход обнуления первого триггера 6,

0 нулевой сигнал с прямого выхода которого запрещает прохождение сигналов через трехвходовьй элемент И 9, а .сигнал с инверсного выхода первого триггера 6 обнуляет первый счетчик

5 50. Система возвращается в исходное состояние и следующий сбой может имитироваться только при повторном появления сигналов на входе устройства.

В случае формирования сигналов ошибки для имитации повторяющихся сбоев второй переключатель 14 разомкнут. В этом случае сигнал обнуления с выхода счетчика 11 на первый триггер 6 не поступает. Счетчик 10 тактов продолжает работу до переполнения, обнуляется и при повторном совпадении подсчитанного кода с заданным в третьем регистре 3 на выходе схемы 5 сравнения снова появляется единичный сигнал, который, проходя через элемент И 9, вновь устанавливает в единичное состояние второй .триггер 7, с прямого выхода которого на выход 19 устройства снова поступает сигнал ошибки. Период следования сигналов ошибки повторяющихся сбоев определяется разрядностью счетчика 10 и равен , где Т- период следования импульсов на входе 17 устройства; h число разрядов.

Для имитации сбоев увеличенной длительности подвижньш контакт переключателя 1 3 замыкается, например, на выход старших разрядов счетчика 11. Увеличенная длительность сбоя обеспечивается более поздним появлением 1 на выходе старшего разряда по сравнению с выходом младшего разряда счетчика 11. Для имитации постоянной неисправности подвижный контакт первого переключателя 13 устанавливается в нейтральное положение. В этом случае сигнал обнуления на второй. триггер 7 не поступает и на выходе 19 устройства сохраняется постоянный сигнал ошибки неограниченной длительности.

в случае, когда необходимо привязать момент формирования сигнала ошибки к появлению единичного сигнала в любой из доступных для подключения цепей ЦВМ, используется вход 16 устройства. При этом первый I и второй 2 регистры и схема 4 сравнения не работают. В остальном работа устройства аналогична описанному.

Формула изобретения

Устройство для имитации сбоев и неисправностей цифровой вычислительной машины, содержащее первый и второй регистры адреса, схему сравнения

адреса, счетчик тактов, регистр тактов, схему сравнения тактов, первый триггер, первый элемент И, причем вход первого регистра адреса подключен к адресному выходу цифровой вычислительной машины, выходы первого и второго регистров адреса подключены соответственно к первому и втором входам схемы сравнения адреса, счетный вход счетчика тактов подключен к тактовому входу устройства, выходы счетчика тактов и регистра тактов соединены соответственно с первым и вторым входами схемы сравнения тактов, выход равенства которой соединен с первым входом первого элемента И, второй вход которого подключен к прямому выходу первого триггера, инверсный выход которого соединен с входом сброса счетчика тактов, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования сигнала ошибки любой длительности, в устройство введены второй триггер, элемент ИЛИ, счетчик, второй элемент И и два переключателя, причем выход равенства схемы сравнения адреса, соединен с первым входом элемента ИЛИ, второй вход которого подключен к стррбиругощему входу устройства, выход элемента ИЛИ соединен с е:диничным входом первого триггера, нулевой вход которого соединен с неподвижным контактом первого переключателя, подвижный контакт которого соединен с входом сброса счетчика и нулевым входом второго триггера и подключен к входу начальной установки устройства единичньгй вход второго триггера подключей к выходу первого элемента И, третий вход которого соедгшен с инверсным выходом второго триггера, прямой выход которого подключен к

«

первому входу второго элемента И и является информационным выходом устройства, второй вход и выход второго элемента И соединены соответственно с тактовым входом устройства и счетным входом счетчика, выходы разрядов которого подключены к группе неподвижных контактов второго переключателя, подвижный контакт которого соединен с входом начал ьной установки устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1988 |

|

SU1536387A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1273933A1 |

| Устройство для контроля передачи информации | 1984 |

|

SU1251083A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1283775A1 |

| Устройство для имитации неисправностей цифровой вычислительной машины | 1982 |

|

SU1016787A1 |

| Устройство для контроля @ -разрядных схем сравнения | 1984 |

|

SU1187171A1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| Логический пробник | 1986 |

|

SU1352420A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1987 |

|

SU1451702A1 |

Изобретение может быть использовано в вычислительной технике для проверки и отладки программно-аппаратных средств контроля, диагностики и восстановления работоспособности хщфровых вычислительных устройств путем имитации различных видов сбоев .и неисправностей в заданные моменты времени в процессе их работы Цель изобретения - расширение функциональных возможностей за счет возможности формирования сигналов ошибки любой длительности. Устройство содержит две схемы сравнения, одна из которых за счет связи входов с информационгными выходами первого и второго регистров обеспечивает привязку момента формирования сигнала ошибки к многоразрядному входному сигналу. Вторая схема сравнения за счет связи входов с выходом первого счетчика и информационным выходом третьего регистра обеспечивает заданную задержку от указанного выше момента времени, а также требуемый период повторения сигнала ошибки в режиме многократных сбоев. Элемент ИЛИ за счет связи первого и второго входов с вторым информационным входом устройства и выходом первой схемы сравнения соответственно обеспечивает управление первым триггером по одноразряднсму и (Л многоразрядному входному сигналу, соответственно. Требуемая длительность сигнала ошибки обеспечивается вторым счетчиком, выходы которого соединены с неподвижньв4и контактами первого переключателя, который коммутирует вход N9 обнуления второго триггера. Второй О переключатель коммутирует вход обну01 ления первого триггера, чем обеспечи вает режим однократныхи многократных сбоев. 1 ил. (;о

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации неисправностей цифровой вычислительной машины | 1982 |

|

SU1016787A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1985-04-01—Подача