Изобретение относится к вычислительной технике и предназначено для обнаружения ошибок, возникающих в арифметическом устройстве ЭВМ в процессе вычислений.

Известно устройство для обнаружения ошибок в системе остаточных классов, содержащее два блока памяти, три сумматора, три преобразователя в дополнительный код, сумматор по модулю Р„ первого уровня, два сумматора по модулям Р. и РК первого уровня, два сумматора по модулям Р и Рц2. второго уровня и блок формирования сигнала ошибки, причем п-1 входов устройства соединены с входами первого блока памяти, выходы которого связаны соответственно с входами сумматоров, выход первого сумматора подключен к первому входу сумматора по модулю Р„ первого уровня, второй вход которого через первый преобразователь в дополнительный код соединен с п-м входом устройства, а выход - с входом второго блока памяти 11 .

в этом устройстве с помощью сумматоров и преобразователей, блоков |Памяти и сумматоров по контрольным модулям первого и второго-уровней

обеспечивается получение разностей между кодом контрольных частей слова и свертками кода информационной части слова по контрольным модулям Рц.., и P,t2.. Анализ полученных разностей позволяет сформировать . сигналы о знаке числа, наличии ошибки в его представлении и выполнить исправление ошибок определенного

10 класса. Но имеющаяся большая избыточность используется лишь для формирования указанных двух сигналов. Исправление ошибок при этом не производится.

15

Наиболее близким к изобретению техническим решением является устройство для обнаружения ошибок в системе остаточных классов, содержащее регистры информационной и конт20рольной частей слова, входы которых являются входами устройства, преобразователь кода из системы остаточных классов в позиционную систему счисления, блок свертки слова

25 по контрольным основаниям, схему сравнения, первый вход которой подключен к выходу регистра контрольной части слова, а второй - к выходу блока свертки слова по контрольным

30 основаниям, входом подключенного к

выходу преобразователя кода из системы остаточных классов в позиционную систему счисления, первый вход которого подключен к выходу регистра информационной части слова, а второй - к выходу регистра контрольной части слова, выход схемы сравнения является выходом устройства 2 .

Недостатком устройства является отсутствие возможности исправления ошибок.

Цель изобретения - расширение функциональных возможностей устройства за счет обнаружения всех одиночных ошибок и исправления одиночных ошибок, не выводящих величину контролируемого числа за предела

ИИ

диапазона П PJ

Поставленная цель достигается

т.ем, что устройство содержит блок выделения ошибочного основания, элемент И, блок хранения поправок, сумматор, элемент ИЛИ-НЕ, причем выход схемы сравнения подключен к первомувходу элемента И и управляющему входу блока хранения поправок, группа адресных входов которого объединена с соответствующими входами элемента ИЛИ-НЕ и подключена к группе выходов блока выделения ошибочного основания, входы которого объединены с соответствующими входами первой группы входов сумматора и годключены к соответствующим выходам регистров информационной и контрольной частей слова, вторая группа входов сумматора подключена к соответстВ5ТОЩИМ выходам блока хранения поправок, второй вход элемента И подключен к выходу элемента ИЛИ-НЕ, выход сумматора является информационным выходом устройства, выход эле1у1ента И является выходом Ошибка устройства .

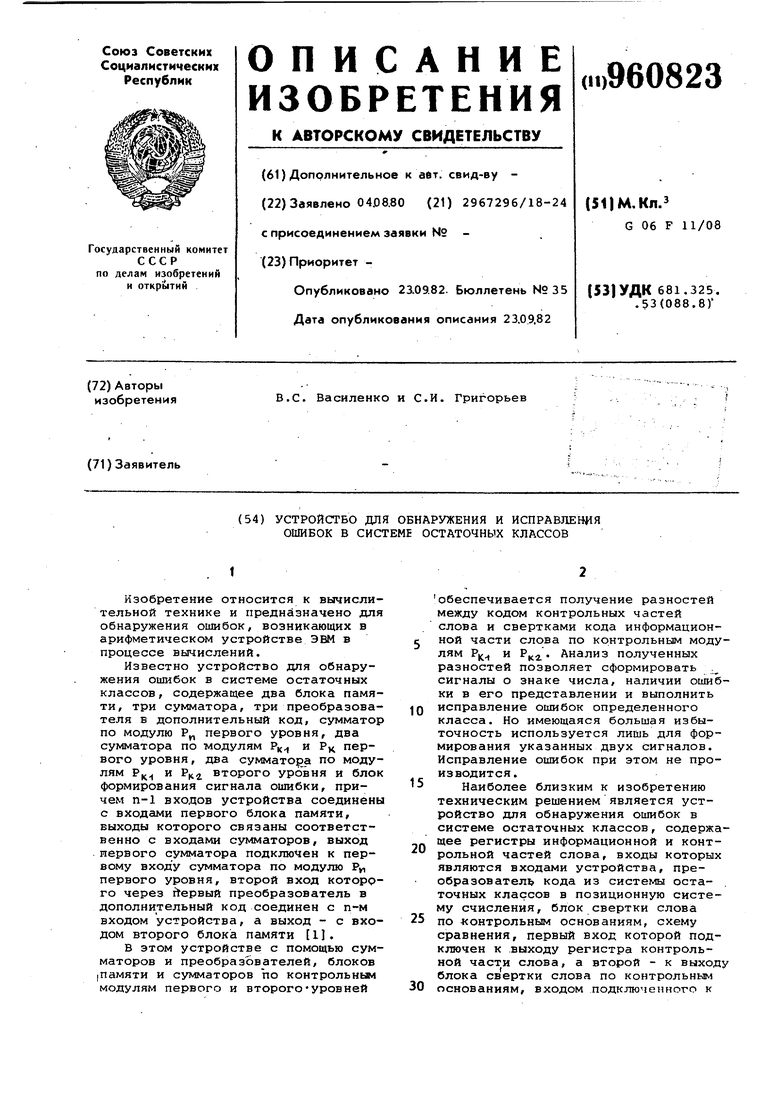

При этом блок выделения о11Шбочного основания содержит группу из (п+1) дешифраторов, группу из (n+l) элементов ИЛИ, группу из (п+1) схем сравнения, выходы которых являются группой выхода блока, выходы i-ro дешифратора группы подключены к соответствующим входам 1-го элемента ИЛИ (1 1,2,,..,п+1), выход которого подключен к входу i-й схемы сравнения с константой, входы дешифрат Ьров являются входом блока.

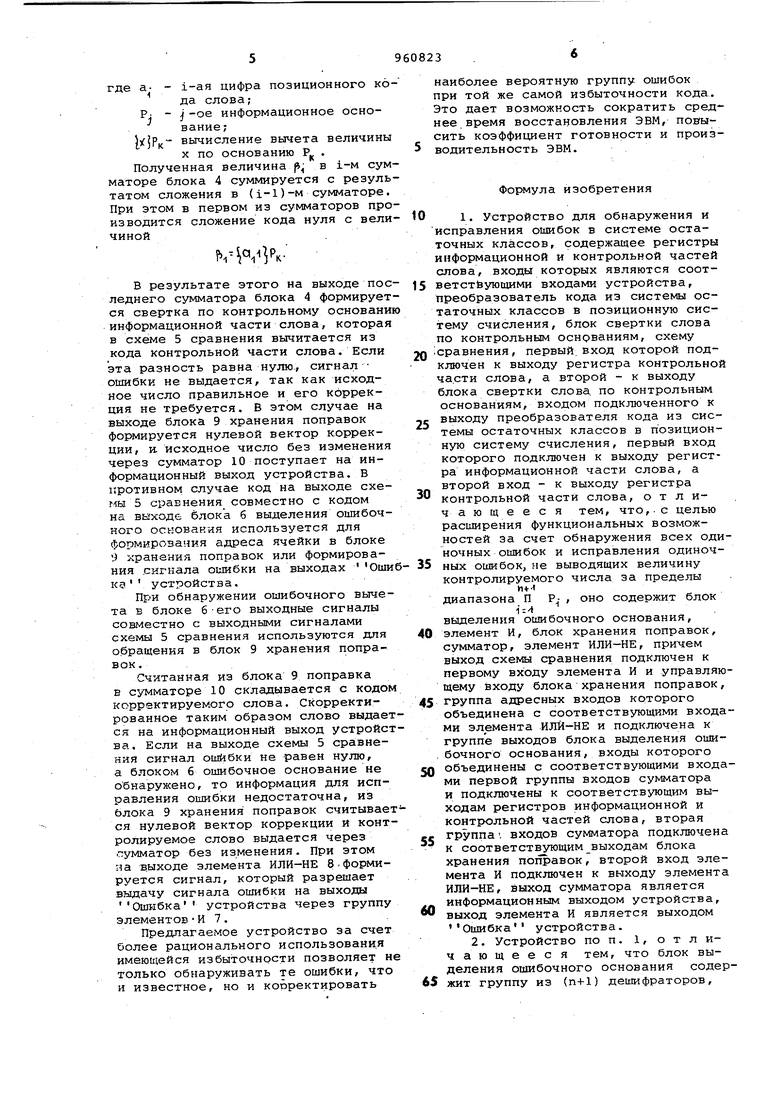

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема блока выделения ошибочного основания.

Устройство содержит регистры 1 и 2 информационной и контрольной частей слова, преобразователь 3 кода из системы остаточных классов в позиционную систему счисления, блок 4 свертки слова по контрольным основаниям, схему 5 сравнения, блок

6 выделения ошибочного основания, элемент И 7, элемент ИЛИ-НЕ 8, блок 9 хранения поправок, сумматор 10, группу дешифраторов 11, группу элементов ИЛИ 12, группу схем 13 сравнения .

Блок 4 свертки слова по контрольным основаниям представляет собой многоярусную схему, в каждом ярусе которой установлены сумматор и умножитель (не показаны). К первым входам сумматора каждого последующего яруса подключены выходы сумматор предыдущего яруса. На вторые входы сумматоров через умножители подключены разряды позиционного представления информационной части слова с выхода преобразователя 3.

Блок 6 выделения ошибочного основания преобразует вычеты по основаниям системы в унитарный код, который через элементы ИЛИ 12 поступает на входы схем сравнения 13, гд происходит его сравнение с константой -1. Если вычет по некоторому модулю не имеет ошибки, на выходе схемы 5 сравнения по данному модулю сигнал равен нулю. Если вычет по некоторому модулю ошибочен или неправильно дешифриройан, на выходе схемы 5 сравнения по данному модулю сигнал равен единице.

Блок хранения поправок 9 представляет собой, например, одностороннее запоминающее устройство, в котором хранятся величины поправок. Адрес ячейки этого запоминающего устройства задается кодами с выходов блока 6 выделения ошибочного основания и схемы 5 сравнения.

Сумматор 10 представляет собой набор сумматоров, каждый из которых обеспечивает сложение по соответствующему основанию вьпетов, поступающих на его входы.

Устройство работает следуюгдам образом.

На регистры 1 и 2 из арифметического устройства ЭВМ поступает контролируемый код слова, состояший из совокупности вычетов числа по контрольным и информационным основаниям. Информационная часть слова преобразуется в преобразователе 3 в позиционный код. Цифры позиционного кода слова по мере, их формирования подаются на блок 4, где в y нoжитeляx вычисляется произведение по контрольному основанию данной цифры позиционного кода слова на величину произведений оснований по которым формирование цифр позиционного кода закончено, т.е. формирование величины

1-1

,. где а- - i-ая цифра позиционного к да слова; Р: - j -ое информационное основание;j ifjPi - вычисление вычета величин X по основанию Р . Полученная величина р в i-м су маторе блока 4 суммируется с резул татом сложения в (i-l)-M сумматоре При этом в первом из сумматоров пр изводится сложение кода нуля с вел чиной результате этого на выходе по леднего сумматора блока 4 формируе ся свертка по контрольному основан информационной части слова, котора в схеме 5 сравнения вычитается из кода контрольной части слова. Если эта разность равна нулю., сигнал ошибки не выдается, так как исходное число правильное и его коррекция не требуется. В этом случае на выходе блока 9 хранения поправок фО1 1ируется нулевой вектор коррекции, и. исходное число без изменения через сумматор 10 поступает на информационный выход устройства. В противном случае код на выходе схемы 5 сравнения совместно с кодом на выходе блока б выделения ошибочного основания используется для формирования адреса ячейки в блоке У хранения поправок или формирования .сигнала ошибки на выходах Оши устройства. При обнаружении ошибочного выче та в блоке 6-его выходные сигналы совместно с выходными сигналами схемы 5 сравнения используются для обращения в блок 9 хранения поправок . Считанная из блока 9 поправка в сумматоре 10 складывается с кодом корректируемого слова. Скорректированное таким образом слово выдает ся на информационный выход устройс ва. Если на выходе схемы 5 сравнения сигнал ошибки не -равен нулю, а блоком 6 ошибочное основание не обнаружено, то информация для исправления ошибки недостаточна, из блока 9 хранения поправок считывае ся нулевой вектор коррекции и конт ролируемое слово выдается через сумматор без изменения. При этом на выходе элемента ИЛИ-НЕ 8.формируется сигнал, который разрешает выдачу сигнала ошибки на выходы Ошибка устройства через группу элементовИ 7. Предлагаемое устройство за счет более рационального использовани.я имеющейся избыточности позволяет н только обнаруживать те ошибки, что и известное, но и корректировать наиболее вероятную группу ошибок при той же самой избыточности кода. Это дает возможность сократить среднее, время восстановления ЭВМ, повысить коэффициент готовности и производительность ЭВМ. Формула изобретения 1.Устройство для обнаружения и исправления ошибок в системе остаточных классов, содержащее регистры нформационной и контрольной частей слова, входы которых являются соответстЬующими входами устройства, преобразователь кода из системы остаточных классов в позиционную систему счисления, блок свертки слова по контрольным основаниям, схему сравнения, первый, вход которой подключен к выходу регистра контрольной ча.сти слова, а второй - к выходу блока свертки слова, по контрольным основаниям, входом подключенного к выходу преобразователя кода из системы остаточных классов в позиционную систему счисления, первый вход которого подключен к выходу регистра информационной части слова, а второй вход - к выходу регистра контрольной части слова, отличающееся тем, что,, с целью расширения функциональных возможностей за счет обнаружения всех одиночных ошибок и исправления одиночных ошибок, не выводящих величину контролируемого числа за пределы диапазона П Р-, оно содержит блок внщеления ошибочного основания, элемент И, блок хранения поправок, сумматор, элемент ИЛИ-НЕ, причем выход схемы сравнения подключен к первому входу элемента И и управляющему входу блока хранения поправок, группа адресных входов которого объединена с соответствующими входами элемента ИЛЙ-НЕ и подключена к группе выходов блока выделения ошибочного основания, входы которого объединены с соответствующими входами первой группы входов сумматора и подключены к соответствующим выходам регистров информационной и контрольной частей слова, вторая группа . входов сумматора подключена к соответствующим выходам блока хранения поправок, второй вход элемента И подключен к выходу элемента ИЛИ-НЕ, выход сумматора является информационным выходом устройства, выход элемента И является выходом Ошибка устройства. 2.Устройство по п. 1, отличающееся тем, что блок выделения ошибочного основания содержит группу из (п+1) дешифраторов.

группу из (п+1) элементов ИЛИ, группу из (п+1) схем сравнения, выходы которых являются группой выходов блока, выходы 1-го дешифратора группы подключены к соответствующим входам 1-го элемента ИЛИ (i 1,2,.. ,..,п+1), выход которого подключен к входу i-й схемы сравнения с константой, входы дешифраторов являются входом блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

519714, кл. G 06 F 11/08,1976.

2.Журавлев Ю.П. и др. Надежность и контроль ЭВМ. М., Советское радио, 1978, с. 136 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибокВ СиСТЕМЕ ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU842820A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯРНОМ КОДЕ | 1991 |

|

RU2015620C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯТОРНОМ КОДЕ | 1991 |

|

RU2022472C1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ОБНАРУЖЕНИЯ, ЛОКАЛИЗАЦИИ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2301442C2 |

| Устройство для обнаружения и исправления ошибок арифметических операций | 1977 |

|

SU744583A1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО | 2004 |

|

RU2297036C2 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 2004 |

|

RU2297029C2 |

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

т

tQUJudha

Фиг

5

fJ f

W

Вхрд (fflOHQ 6

дшод лома f (pt/г. 2

Авторы

Даты

1982-09-23—Публикация

1980-08-04—Подача