Изобретение относится к вычислительной технике и может быть использовано в цифровых ЭВМ повышенной информационной надежности, их устройствах обмена информацией и для повышения верности в системах передачи данных, в системах шумопонижения цифровой зву- ко-, видеозаписи и воспроизведения при представлении информации в последовательном коде.

Известно устройство для исправления ошибок в системе остаточных классов, содержащее операционный и запоминающий регистры с л выходами, блоки памяти констант нулевизации, дешифраторы, блоки памяти констант нулевизации и ошибок, сумматор, переключатели и логические элементы.

Недостатком устройства является низкое быстродействие, большие затраты оборудования и невозможность использования в системах счисления, отличающихся от остаточных классов.

Известно устройство для исправления ошибок, содержащее регистры информационной и контрольной части кода числа, узел свертки по контрольным основаниям, узел перевода СОК-ПСС, вычислитель таблиц поправок и сумматор.

Недостатком устройства являются значительные затраты оборудования, использованного для хранения и обработки контрольной части кода числа.

Наиболее близким к изобретению техническим решением является устройство для обнаружения и исправления ошибок, содержащее первый регистр, выходы всех разрядов которого соединены с адресными входами первого блока памяти и с информационными входами первого коммутатора, первый сумматор, выходы которого соединены с информационными входами второго регистра, выходы которого соединены с первыми входами первого сумматора и информационными входами третьего регистра, выходы которого соединены с информационными входами второго коммутатора, первый счетчик импульсов, выходы которого соединены с адресными входами второго, третьего блоков памяти и входами второго дешифратора, первый выход которого соединен с первым входом первого элемента ИЛИ, выходы третьего блока памяти соединены с первыми входами блока сравнения, второй счетчик импульсов, выходы которого соединены с входами второго дешифратора, первый и второй выходы которого соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом сброса второго счетчика

импульсов, первый элемент НЕ, вход которого объединен с вторым входом второго элемента И, выход подключен к второму входу первого элемента И и первому входу третьего элемента И, третий счетчик им0 пульсов, выходы которого соединены с входами третьего дешифратора, четвертый элемент ИЛИ, второй элемент НЕ, четвертый элемент И, четвертый регистр, триггер, выход которого соединен с первым входом

5 пятого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, четвертый блок памяти, третий коммутатор, первый и второй элементы задержки.

Такое устройство требует значительных

0 аппаратурных затрат.

Целью изобретения является упрощение устройства.

Для этого в устройство введен второй сумматор, информационный вход первого

5 регистра является информационным входом устройства, вход сдвига информации первого регистра объединен со счетным входом второго счетчика импульсов и является входом синхронизации устройства, вы0 ходы первого блока памяти соединены с информационными входами третьего коммутатора, выходы которого объединены с выходами первого коммутатора и соединены с вторыми входами первого сумматора,

5 выходы второго коммутатора соединены с первыми входами второго сумматора, выходы которого соединены с входами параллельного приема информации первого регистра, информационные входы второго и

0 четвертого блоков памяти объединены и подсоединены к выходам всех разрядов первого регистра, вторые входы блока сравнения подключены к выходам младших разрядов первого регистра, выход старшего

5 разряда которого является информационным, выходом устройства, выходы четвертого блока памяти подключены к информационным входам третьего блока памяти, выход блока сравнения подключен

0 к первому входу четвертого элемента И, выход которого соединен с входом последовательного приема информации четвертого регистра и счетным входом третьего счетчика импульсов, выходы третьего дешифрато5 ра подключены к соответствующим входам четвертого элемента ИЛИ, выход которого является выходом контроля устройства, третий выход второго дешифратора соединен с вторым входом третьего элемента И, выход которого непосредственно соединен с входом Чтение второго блока памяти и через первый элемент задержки ;- с входом Запись первого регистра, входы Чтение первого, четвертого блоков памяти, вход Запись второго блока памяти и вход пер- вого элемента задержки объединены и подключены к выходу первого элемента И, выход первого элемента задержки соединен с входами Запись второго регистра и третьего блока памяти, вход Чтение треть- его блока памяти подключен к выходу второго элемента И, вход Запись третьего регистра, первый вход триггера и второй вход пятого элемента И объединены и подключены к первому выходу первого дешиф- ратора, второй выход которого непосредственно соединен с управляющим входом третьего коммутатора и через второй элемент НЕ - с управляющим входом первого коммутатора, вторые входы перво- го, третьего, пятого элементов ИЛИ и триггера объединены и являются входом начальной установки устройства, выход пятого элемента ИЛИ подключен к входу сброса второго регистра, выходы второго блока памяти соединены с вторыми входами второго сумматора, выход первого элемента ИЛИ соединен с входами сброса первого и третьего счетчиков импульсов, счетный вход первого счетчика импульсов, вход сдвига информации четвертого регистра и второй вход четвертого элемента И объединены и подключены к выходу второго элемента ИЛИ, третий вход четвертого элемента И соединен с входом первого элемента НЕ и подключен к выходу триггера, выход четвертого регистра подключен к управляющему входу второго коммутатора.

Устройство для исправления ошибок реализует каскадируемый вырожденный ВГ-код, суть которого заключается в следующем.

Информационная часть кода числа сопровождается, как и при известных способах контроля, контрольным признаком. Но в отличие от известных способов контрольный признак сострит из двух частей, каждая из которых вычисляется следующим образом. Информационная часть кода числа разбивается на фиксированные группы оп- ределенной разрядности, например на п групп по S разрядов в каждой. Разрядность групп S определяет максимальную кратность обнаруживаемых и исправляемых ошибок. Для расчета первой части конт- рольного признака используется вырожденный ВГ-код, который отличается от ВГ-кода величинами используемых весовых коэффициентов и контрольного модуля и

получается из последнего, если в формуле для расчета контрольного признака

г(А) { 2 (A Ci}q, I 1

0)

где О| - код 1-й группы, рассматриваемый как некоторое число;

Ci - весовой коэффициент 1-й группы;

q - контрольный модуль;

п - число S-разрядных групп, на которое разбит код исходного числа;

знак {х}у означает вычисление остатка отделения числа на х число у,° J

в качестве весовых коэффициентов использовать Ci 1 для всех значений I, а в качестве контрольного модуля

q 2S.

В этом случае будет получен контрольный признак той же разрядности S, что и разрядность групп, на которые разбито исходное число. Естественно, что при этом код теряет корректирующие свойства, так как он позволяет только определить факт наличия ошибки, но не позволяет определить ее место и величину.

Однако, если место ошибки определено каким-либо другим способом, то вырожденный ВГ-код позволяет величину этой ошибки определить. Действительно, при наличии ошибки в j-й группе величиной Ао| величина контрольного признака в соответствии с выражением (1) при Ci 1 будет равна

КА} { 2 СЦ+(Ц+АЩ) § «l}q.

+ 1

а разность контрольных признаков исходного и искаженного чисел, вычисленная по контрольному модулю,Ar(A ) {r(A )-r(A)}q

-Л 2 ot+(o5+Ao|)4 1

& -&«№«} - «

(2)

+

Поэтому, если место ошибки известно, то ее исправление осуществляется легко, так как

откуда

aj |aj+AoiJq

Щ Щ

|5j-Aq|q

Для определения места ошибки используется вторая часть контрольного признака, которая получается как совокупность из п частных контрольных признаков. Каждый из частных контрольных признаков f относится к соответствующей i-й фиксированной группе разрядов выше разбиения и получается относительно величины оз применением любого обнаруживающего кода, например, контроля по модулю q, где qi q, т.е.

НЕсли теперь применить к исходному коду процедуры (1, 3), то контрольный признак числа будет представлен совокупностью

R(A) r(A), f( ai), f2(«2)fn( «л). (4)

которая сопровождает исходное число при его хранении, передаче и т.п.

Совокупность исходного числа и его контрольного признака (4) образует информационную и контрольную части разрядов каскадируемого вырожденного ВГ-кода (КВВГ-кода), используемого в предлагаемом устройстве. При декодировании числа применение процедуры (3) и сравнение величин fi с ранее вычисленными позволяет определить наличие ошибки и ее место, а применение процедур (1,2)- наличие ошибки и ее величину. Совместная обработка информации о наличии ошибки позволяет обеспечить высокую вероятность ее обнаружения, а знание величины ошибки - ее безусловную коррекцию.

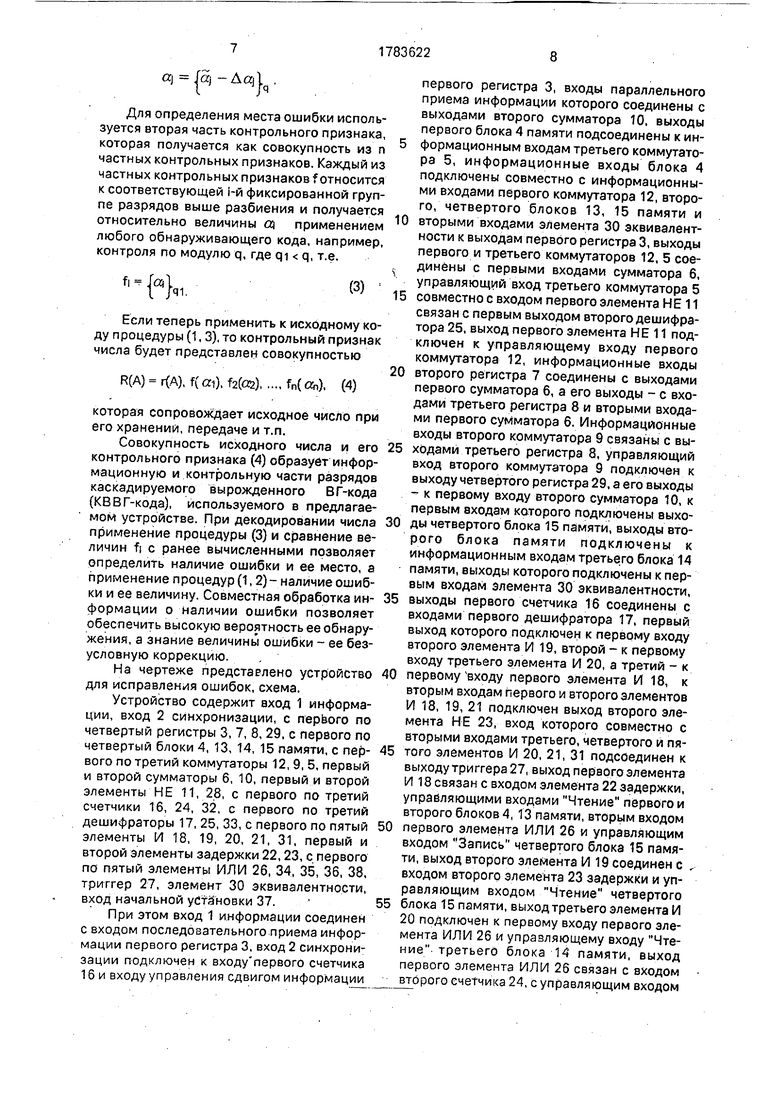

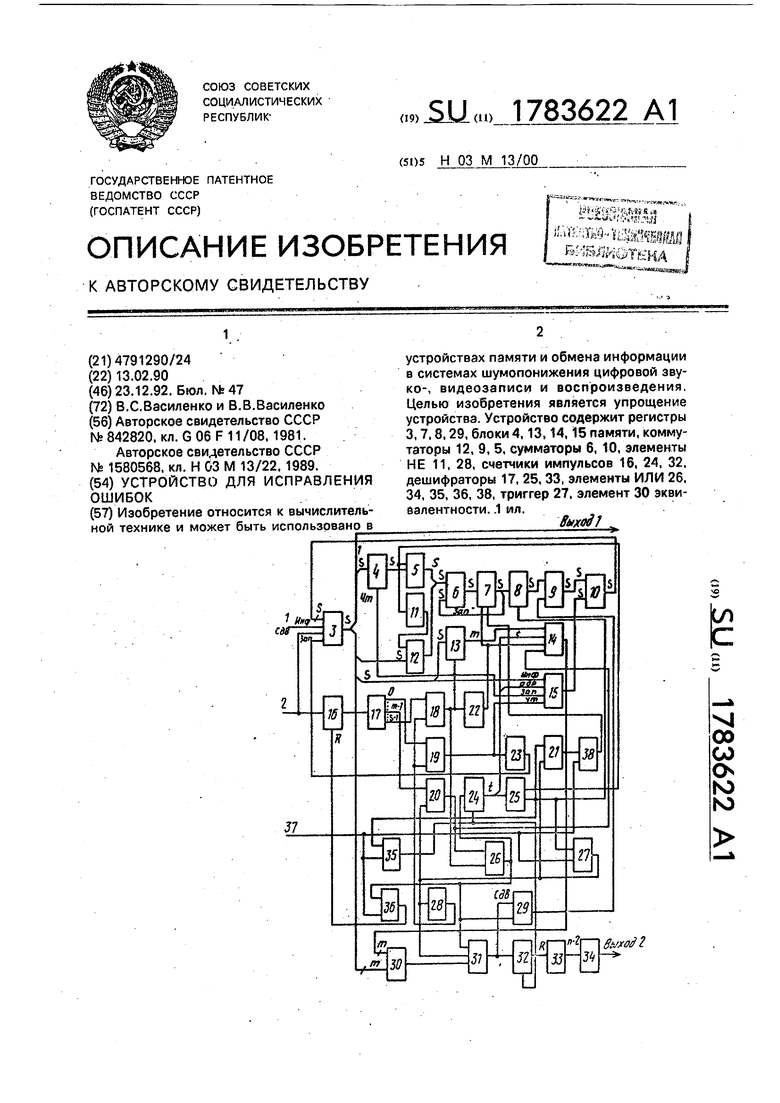

На чертеже представлено устройство для исправления ошибок, схема.

Устройство содержит вход 1 информации, вход 2 синхронизации, с первого по четвертый регистры 3, 7, 8, 29, с первого по четвертый блоки 4, 13, 14, 15 памяти, с первого по третий коммутаторы 12, 9, 5, первый и второй сумматоры б, 10, первый и второй элементы НЕ 11, 28, с первого по третий счетчики 16, 24, 32, с первого по третий дешифраторы 17, 25, 33, с первого по пятый элементы И 18, 19, 20, 21, 31, первый и второй элементы задержки 22,23, с первого по пятый элементы ИЛИ 26, 34, 35, 36, 38, триггер 27, элемент 30 эквивалентности, вход начальной установки 37.

При этом вход 1 информации соединен с входом последовательного приема информации первого регистра 3, вход 2 синхронизации подключен к входу первого счетчика 16 и входу управления сдвигом информации

первого регистра 3, входы параллельного приема информации которого соединены с выходами второго сумматора 10, выходы первого блока 4 памяти подсоединены к ин5 формационным входам третьего коммутатора 5, информационные входы блока 4 подключены совместно с информационными входами первого коммутатора 12, второго, четвертого блоков 13, 15 памяти и

10 вторыми входами элемента 30 эквивалентности к выходам первого регистра 3, выходы первого и третьего коммутаторов 12, 5 соединены с первыми входами сумматора 6, управляющий вход третьего коммутатора 5

15 совместно с входом первого элемента НЕ 11 связан с первым выходом второго дешифратора 25, выход первого элемента НЕ 11 подключен к управляющему входу первого коммутатора 12, информационные входы

20 второго регистра 7 соединены с выходами первого сумматора 6, а его выходы - с входами третьего регистра 8 и вторыми входами первого сумматора 6. Информационные входы второго коммутатора 9 связаны с вы25 ходами третьего регистра 8, управляющий вход второго коммутатора 9 подключен к выходу четвертого регистра 29, а его выходы - к первому входу второго сумматора 10, к первым входам которого подключены выхо30 ды четвертого блока 15 памяти, выходы второго блока памяти подключены к информационным входам третьего блока 14 памяти, выходы которого подключены к первым входам элемента 30 эквивалентности,

35 выходы первого счетчика 16 соединены с входами первого дешифратора 17, первый выход которого подключен к первому входу второго элемента И 19, второй - к первому входу третьего элемента И 20, а третий - к

40 первому входу первого элемента И 18, к вторым входам первого и второго элементов И 18, 19, 21 подключен выход второго элемента НЕ 23, вход которого совместно с вторыми входами третьего, четвертого и пя45 того элементов И 20, 21, 31 подсоединен к выходу триггера 27, выход первого элемента И 18 связан с входом элемента 22 задержки, упраёляющими входами Чтение первого и второго блоков 4, 13 памяти, вторым входом

50 первого элемента ИЛИ 26 и управляющим входом Запись четвертого блока 15 памяти, выход второго элемента И 19 соединен с . входом второго элемента 23 задержки и управляющим входом Чтение четвертого

55 блока 15 памяти, выход третьего элемента И 20 подключен к первому входу первого элемента ИЛИ 26 и управляющему входу Чтение третьего блока 14 памяти, выход первого элемента ИЛИ 26 связан с входом второго счетчика 24, с управляющим входом

Сдвиг четвертого регистра 29 и первыми входами четвертых элементов ИЛИ 36 и И 31, к третьему входу которого подключен выход элемента 30 эквивалентности, выход второго элемента 22 задержки подключен к управляющим входам Запись второго регистра 7 и третьего блока 14 памяти, выход третьего элемента 23 задержки связан с управляющим входом параллельного приема информации Запись первого регистра 3, выходы второго счетчика 24 подключены к адресным входам Адрес третьего и четвертого блоков 14, 15 памяти и входам второго дешифратора 25, второй выход которого связан с первым входом третьего элемента ИЛИ 35, управляющим входом Запись третьего регистра 8, первым входом четвертого элемента И 21 и первым входом триггера 27, выход пятого элемента И 31 подключен к входу последовательного приема информации четвертого регистра 29 и входу третьего счетчика 32, выходы третьего счетчика 32 соединены с входами третьего дешифратора 33, все выходы которого, кроме нулевого и первого, соединены с вхо- дами второго элемента ИЛИ 34, выход четвертого элемента И 21 связан с входом установки в нуль второю регистра 7, вход начальной установки 37 подключен к вторым входам триггера 27, третьего, четверто- го и пятого элементов.ИЛИ 35, 36,38, выход третьего элемента ИЛИ 35 связан с входами установки в нуль второго и третьего счетчиков 24, 32, выход четвертого элемента ИЛИ 36 подсоединен к входу установки в нуль первого счетчика 16, выход старшего разряда первого регистра 3 является информационным, а выход второго элемента ИЛИ - контрольным выходом устройства.

Регистр 3 предназначен для приема, хранения и сдвигов S-разрядных двоичных чисел. Прием осуществляется по S-разряд- ным входам параллельного приема информации при наличии разрешающего сигнала на управляющем входе Запись 1 или по од- поразрядному входу последовательного приема Инф. при наличии разрешающего сигнала на управляющем входе Сдвиг. В последнем случае осуществляется сдвиг содержимого регистра на один разряд и за- пись в его младший разряд информации по входу последовательного приема. Выходная информация снимается со всех разрядов регистра по S-разрядной шине и, кроме того, с последнего, S-ro разряда, являюще- гося выходом устройства.

Второй и третий регистры 7, 8 предназначены для приема и хранения S-разрядных двоичных чисел. Прием осуществляется при наличии разрешающего сигнала на управляющем входу Запись, Съем информации в регистре 8 осуществляется с прямых, а в регистре 9 - с инверсных выходов.

Четвертый регистр 29 предназначен для приема, хранения и сдвигов одноразрядных двоичных сигналов, поступающих на вход последовательного приема информации. Прием и сдвиг этих сигналов осуществляется при наличии разрешающего сигнала на управляющем входе Сдвиг, Емкость регистра должна быть рассчитана на (п+1) разрядов, где п - ЧИС710 групп разбиения исходного контролируемого числа. Съем информации осуществляется с последи С, го разряда. После записи всей информации на регистре окажутся записанными в позиционном коде номера групп, где обнаружены искажения. Под позиционным понимается код, в котором единица на некоторой j-й позиции свидетельствует о наличии ошибок в j-й группе, а нуль - об ее отсутствии в этой же группе.

Первый и второй блоки 4, 13 памяти предназначены для табличного расчета выходных кодов по входным (перекодировки). В качестве этих блоков памяти могут использоваться, например, постоянные (долговременные) запоминающие устройства на 2s ячеек памяти, где S - разрядность групп разбиения исходного контролируемого числа. В каждой ячейке первого блока 4 памяти при этом хранится заранее рассчитанное по модулю q отрицательное S-разрядное значение кода адреса этой ячейки

L q-r(A),

где q - величина контрольного модуля вырожденного ВГ-кода;

г(А) - код адреса ячейки, соответствующий контрольному признаку числа, представленного в вырожденном ВГ-коде.

В ячейках второго блока 13 памяти хранятся m-разрядные, заранее рассчитанные частные контрольные признаки

{«Кгде сц - адрес ячейки, соответствующий коду 1-й фиксированной группы разбиения исходного контролируемого числа.

Считывание информации осуществляется по разрешающим сигналам на управляющих входах Чтение.

Третий и четвертый блоки 14, 15 памяти предназначены для записи, хранения и последующего считывания информации, поступающей на соответствующие входы. В качестве этих блоков памяти могут использеваться, например, оперативные запоминающие устройства (ОЗУ) на (п+1) ячеек памяти. В ячейки третьего блока 14 памяти записываются m-разрядные частные контрольные признаки групп разбиения исходного кода, рассчитанные во втором блоке 13 памяти, а в ячейки четвертого блока 15 памяти - S-разрядные группы разбиения исходного кода с выхода первого регистра 3 при наличии разрешающего сигнала на управляющем входе Запись. Считывание информации осуществляется по разрешающему сигналу на управляющем входе Чтение. Адрес ячейки для записи или считывания информации определяется кодом, подаваемым на адресные входы Адр. ОЗУ с выходов второго счетчика 24.

Коммутаторы 5, 9, 12 предназначены для передачи на свои выходы S-разрядных кодов, поступающих на их информационные входы, при наличии разрешающих сигналов на управляющих входах. В качестве коммутаторов могут использоваться, например, группы из двухвходовых элементов И, управляющие входы которых объединены в один общий управляющий вход.

Сумматоры 6, 10 предназначены для сложения по модулю q S-разрядных чисел, поступающих на их первые и вторые входы. Первый сумматор 6 вместе с вторым регистром 7 образуют при этом накапливающий сумматор, реализующий функцию расчета величины ошибки в некоторой, j-й, группе

A« {r(A)-r{A)}q

- { I а + L}q, I 1

где г(А) 2) а - контрольный признак обI 1

рабатываемого числа, вновь рассчитанный в данном устройстве;

г(А) - сопровождающий контролируемое число контрольный признак.

Во втором сумматоре 10 производится сложение кода j-й группы со считываемым с третьего регистра 8 инверсным кодом ошибки в этой группе, что эквивалентно операции вычитания и образованию исправленного кода j-й группы

а,

|5j-AajJq

где dj - код j-й искаженной группы, считываемой из четвертого блока 15 памяти;

А О) - код ошибки в j-й группе, рассчитанный в накапливающем сумматоре (первый сумматор 6 и второй регистр 7).

Операции сложения по модулю в сумма- торах 6,10 реализуются естественным образом, если эти сумматоры S-разрядные, а величина модуля выбрана равной

10

2s.

Первые счетчик 16 и дешифратор 17 обеспечивают подсчет числа синхроимпульсов, соответствующих информационным разрядам в каждой группе разбиения контролируемого числа или в их частных контрольных признаках, которые принимаются в первый регистр 3, и управление этим приемом. При приеме групп разбиения и контрольного признака вырожденного ВГ-кода

необходимо обеспечить счет от нуля до (S- 1)-S состояний счетчика, а при приеме частных контрольных признаков - от нуля до (m-1)-m состояний счетчика, т.е. необходимо изменять модуль счета. Это обеспечивается принудительной установкой первого счетчика 16 в нулевое состояние сигналами с (S-1)-ro или (т-1)-го выходов первого дешифратора 17 через первый или третий элементы И 18, 20, выходные сигналы которых

объединяются первым элементом ИЛИ 26 и

через четвертый элемент ИЛИ 36 поступают

на вход установки в нуль первого счетчика 16.

Триггер 27 - триггер со счетным входом,

обеспечивающий управление третьим элементом И 20 непосредственно и четвертым элементом И 21 через элемент НЕ 28, изменяя тем самым модуль счета первого счетчика 16, Его начальная установка в нулевое состояние обеспечивается по второму входу

R сигналом с входа 37 начальной установки устройства.

Вторые счетчик 24 и дешифратор 26 обеспечивает подсчет числа принимаемых групп разбиения и их частных контрольных

признаков. С этой целью на вход счетчика поступают сиг.налы окончания приема группы разбиения или частного контрольного признака с выхода первого элемента ИЛИ 26. Для приема всех групп разбиения, включая контрольный признак вырожденного ВГ-кода, или их частных контрольных признаков необходимо обеспечить счет от нуля до п, т.е. (п+1) состояний счетчика. Поэтому принудительная установка в нуль второго

счетчика 24 осуществляется сигналом с второго выхода второго дешифратора 25, соответствующего (п + 2)-му, включая нулевое, состоянию второго счетчика 24, через третий элемент ИЛИ 35. Через этот же элемент

ИЛИ 35 производится и начальная установка в нулевое состояние второго и третьего счетчиков 24, 32. Сигналом с первого, п-го, выхода второго дешифратора 25, соответствующего (п+1)-му состоянию второго счетчи- ка 24, управляются первый коммутатор 5 непосредственно и третий коммутатор 12 через элемент НЕ 11. Этим обеспечивается непосредственная передача содержимого первого регистра 3 (п групп разбиения) в накапливающий сумматор (первый сумматор 6, второй регистр 7) или через блок 4 памяти - отрицательного значения контрольного признака вырожденного ВГ-кода -(п+1)-я группа.

Первый элемент 21 задержки обеспечивает формирование выходного сигнала для установки второго регистра 7 в нулевое состояние, задержанного относительно входного на время, равное времени записи информации в третий регистр 8.

Второй элемент 22 задержки обеспечивает формирование выходного сигнала, задержанного относительно входного на время, равное сумме времен выборки ин- формации из первого или второго блоков 4, 13 памяти, передачи через первый коммутатор 5 и сложения в первом сумматоре 6.

Третий элемент 23 задержки обеспечивает формирование выходного сигнала, за- держанного относительно входного на время, равное сумме времен выборки информации из четвертого блока 15 памяти и сложения во втором сумматоре 10.

Элемент. 30 эквивалентности предназ- начен для сравнения кодов двух т-разряд- ных чисел, подаваемых на его выходы, и выработки сигнала, соответствующего единичному уровню, при их несравнении.

Третий счетчик 32, третий дешифратор 33 и второй элемент ИЛИ 34 обеспечивают выработку сигнала на контрольном выходе устройства и возможности или невозможности исправления ошибки той кратности, ко- торая обнаружена устройством. Так как в устройстве обнаруженными могут быть ошибки любой кратности, а исправленными - ошибки в пределах одной из групп разбиения, то счетчик 32 должен обеспечить счет от нуля до (п-1). При любом состоянии счетчика, отличном от нуля и единицы, что свидетельствует о том, что обнаружены ошибки в более чем одной группе разбиения, необходимо вырабатывать сигнал невозможно- сти исправления. С этой целью с третьего дешифратора 33 на второй элемент ИЛИ на (п-2) входов подаются сигналы со всех выходов, кроме нулевого и первого, т.е. с ( выходов.

, Устройство работает следующим образом. В исходном состоянии первый, второй и третий счетчики 16, 24, 32, второй регистр 7 и триггер 27 находятся в нулевом состоянии, установка в которое производится в предыдущем такте или по входу 37 начальной установки. В четвертом блоке памяти 15 хранится поступившее в предыдущем такте на контроль слово, записанное в ячейки по S разрядов в каждой в соответствии с принятым в коде разбиением на группы, а в третьем блоке 14 памяти - его частные контрольные признаки. В третьем регистре 8 хранится рассчитанная в предыдущем такте величина ошибки в J-й группе. В четвертом регистре 29 хранится позиционный код номера искаженной группы j таким образом, что в старшем (выходном) разряде записан признак наличия или отсутствия ошибок в первой (нулевой) группе разбиения. В установившемся режиме, т.е. при приеме второго и последующих контрольных слов, в момент перевода счетчиков 16, 24, 32 в нулевое состояние сигналом установки в нуль второго счетчика 24 с выхода второго дешифратора 25 устанавливается в нуль триггер 27. При этом на выходе второго элемента НЕ 28 появляется сигнал, разрешающий прохождение сигналов через элементы И 18, 19, 21, в результате чего на выходе второго элемента И 19 появится сигнал единичного уровня, так как и на первый вход этого элемента с нулевого выхода первого дешифратора 17 будет подан разрешающий сигнал. Сигнал с выхода второго элемента И 19 разрешит чтение из четвертого блока 15 памяти информации первой (нулевой) группы разбиения предыдущего слова, в результате того, что на адресные входы этого блока памяти с выхода второго счетчика 24 подан код, соответствующий номеру первой (нулевой) группы, так как этот счетчик установлен в нулевое состояние. Код сосчитанной первой (нулевой) группы подается на второй вход второго сумматора 10, на первый вход которого при наличии единичного сигнала на выходе четвертого регистра 29 поступит код ошибки с третьего регистра 8 через второй коммутатор 9. Если в коде первой (нулевой) группы ошибка не обнаружена, то на выходе четвертого регистра 29 сигнал будет иметь нулевой уровень и код ошибки через второй коммутатор 9 на первый вход второго сумматора 10 передан не будет. Таким образом, на выходе второго сумматора и, следовательно, на входах параллельного приема информации первого регистра 3 будет сформирован код скорректированной первой (нулевой) группы, если ошибка в этой группе была обнаружена, или

код этой же неискаженной группы в противном случае. Этот код записывается в первый регистр 3 разрешающим сигналом на управляющем входе Запись, который формируется на выходе второго элемента 23 задержки по сигналу чтения из четвертого блока 15 памяти и имеет относительно данного сигнала соответствующую задержку. Таким образом, к моменту поступления первого информационного символа нового слова в первый регистр 3 записана скорректированная первая группа предыдущего слова.

При поступлении первого информационного символа очередного слова и связанного с ним синхросигнала осуществляется сдвиг информации первого регистра 3 на один разряд и запись в него первого информационного символа. При этом из старшего разряда первого регистра на информационный выход устройства поступает первый символ предыдущего скорректированного слова, а первый счетчик 16 переводится в очередное состояние.

Эти процессы повторяются S раз, при этом на выход устройства выдается первая группа предыдущего слова, в первый регистр 3 записывается первая группа нового слова, а первый счетчик 16 переводится в S-e состояние, считая нулевое первым, При этом на (5-1)-м выходе дешифратора 17 появится сигнал, который, проходя через открытый первый элемент И 18, первый и четвертый элементы ИЛИ 26, 36, установит первый счетчик 16 в нулевое состояние, обеспечит сдвиг содержимого четвертого регистра 29 на один разряд и как разрешающий сигнал поступит на управляющие входы Чтение первого и второго блоков 4,

13памяти и на управляющий вход Запись четвертого блока 15 памяти. Кроме того, этот же сигнал после задержки во втором элементе 22 задержки поступит как разрешающий сигнал на управляющие входы Запись второго регистра 7 и третьего блока

14памяти. По этим разрешающим сигналам по входной S-разрядной группе сигналов, снимаемой с выхода первого регистра 3, будет сосчитана и передана на информационные входы третьего коммутатора 5 величина L из первого блока 4 памяти, будет сосчитана из второго блока 13 памяти и записана в третий блок 14 памяти величина частного контрольного признака fj и записана во второй регистр 7 сумма содержимого этого же регистра 7, подаваемого на второй вход первого сумматора 6, и подаваемого на первый вход этого же сумматора кода первой, а затем последующей группы разбиения контролируемого слова, передаваемой через первый коммутатор 12, или величины L, передаваемой через третий коммутатор 5 после приема всех групп информационной

части контролируемого слова. Кроме того, этим же разрешающим сигналом, поступающим на управляющий вход Запись четвертого блока 15 памяти, осуществляется прием кода обрабатываемой группы разбиения с выхода первого регистра 3. Одно- временно с этим разрешающим сигналом с выхода первого элемента ИЛИ 26 переводится в очередное состояние второй счетчик 24,

Описанные процедуры повторяются для каждой последующей группы разбиения данного слова, пока второй счетчик 24 и вместе с ним второй дешифратор 25 не будут переведены в (п+1)-е состояние. За это время из четвертого блока 15 памяти будет считана вся информационная часть предыдущего слова, которая после исправления во втором сумматоре 10 будет передана на

первый регистр 3 и с его выходного S-ro разряда - на выход устройства. Кроме того, в четвертый блок 15 памяти будут записаны все п группы а проверяемого слова, а в третий блок 14 памяти - их частные контрольные признаки fi, во втором регистре 7 - сформирован контрольный признак проверяемого слова для вырожденного ВГ-кода г(А), При этом на первом выходе второго дешифратора 25, соответствующего (п+1)му состоянию второго счетчика 24. появляется сигнал, разрешающий передачу информации с первого блока 4 памяти через первый коммутатор 5 и запирающий через первый элемент НЕ 11 третий коммутатор

12, в результате этого после приема (п+1)-й группы контролируемого слова, т.е. после приема его контрольного признака для вырожденного ВГ-кода г(А), на выходе первого блока 4 памяти формируется величина L q

- г(А), которая передается через коммутатор 5 на сумматор 6. После сложения во второй регистр 7 записывается величина ошибки ACHJ и второй счетчик 24 переводится в (п+2)-е состояние, что приводит к появлению на втором выходе второго дешифратора 25 сигнала, которым устанавливается в нулевое состояние второй и треий счетчики 24,32, переводится в единичное состояние триггер 27 и осуществляется

перепись ошибки A2j из второго регистра 7 в третий регистр 8. При переводе в единичное состояние триггера 27 закрываются первый и второй элементы И 18,19 и открываются третий и четвертый элементы

И 20, 21. Этим блокируются цепи формирования управляющих сигналов для получения с использованием вырожденного ВГ-кода и обеспечиваются условия для определения мест возникновения и количест- ва ошибок. При этом прием информации в первый регистр 3 продолжается, но первым счетчиком 16 и дешифратором 17 обеспечивается подсчет символов в группе от нуля до (т-1). Это достигается тем, что при перехо- де первого счетчика 16 в состояние (т-1) на соответствующем выходе первого дешифратора 17 появляется сигнал, который поступает через открытый третий элемент И 20 и первый элемент ИЛИ на вход установки в нуль первого счетчика 16, обеспечивая его принудительный сброс, Этот же сигнал поступает на управляющий вход Чтение третьего блока 14, обеспечивая считывание частных контрольных признаков текущего контролируемого слова, рассчитанных на этапе приема информационной части этого слова. Это считывание осуществляется по адресам, формируемым вторым счетчиком 24, изменяющим свое состояние под воз- действием сигналов с выхода первого элемента ИЛИ 26. Частные контрольные признаки с выхода третьего блока 14 памяти подаются на первые входы элемента 30 эквивалентности, на вторые входы которого поступают частные контрольные признаки с выхода первых m разрядов первого регистра 3. При их несовпадении на выходе элемента 30 эквивалентности формируется единичный сигнал, поступающий на третий вход пятого элемента И 31. Так как-в этот момент на первом входе этого элемента И 31 имеется разрешающий сигнал с выхода первого элемента ИЛИ 26, а на втором - разрешающий сигнал с выхода триггера 27, то элемент И 31 открывается и сигнал с выхода элемента 30 эквивалентности поступает на вход последовательного приема информации четвертого регистра 29 и на вход третьего счетчика 32. Поскольку одновре- менно с этим на управляющий вход Сдвиг четвертого регистра 29 поступает разрешающий сигнал, то в этот регистр последовательно записываются сигналы обнаружения или необнаружения ошибок в каждой из групп контролируемого слова, а третий счетчик 32 обеспечивает подсчет числа обнаруженных ошибок. Если число ошибок превышает одну, то сигналы со всех выходов третьего дешифратора через второй эл - мент ИЛИ на (п-2) входов 34 как сигнал невозможности правильной коррекции поступают на контрольный выход устройства. Описанная процедура выполняется (п+1) раз до тех пор, пока второй счетчик 24

и второй дешифратор 25 не окажутся в состоянии (п+2), при этом сигналом с второго выхода второго дешифратора 25 через открытый четвертый элемент И 21 и пятый элемент ИЛИ 38 устанавливается в нулевое состояние второй регистр 7 и через третий элемент ИЛИ 35 обнуляются второй и третий счетчики 24, 32, переводится в нулевое состояние триггер 27. Устройство готово к приему очередного слова. При этом за время приема и обработки контрольных признаков в четвертый регистр 29 будет записан позиционный код места ошибки в принятом на коррекцию слове, в третий регистр 8 - величина этой ошибки и с контрольного выхода 2 - выдан сигнал невозможности правильной коррекции, если число ошибок превысит функциональные возможности устройства.

При включении устройства сигналом начальной установки по входу 37 устанавливаются в нулевое состояние счетчики 16, 24, 32, триггер 27, регистр 7, Состояние регистров 3, 8, 29 безразлично, так как предыдущего такта работы устройства не было и с его выхода 1 в течение приема первого слова может сниматься любая информация, которая потребителем использована не будет.

В результате работы устройства с выхода S-ro разряда первого регистра 3 будет снят последовательный код скорректированного слова, поступившего на информационный выход 1 устройства в предыдущем такте, а на контрольном выходе 2 устройства будет сформирован признак возможности или невозможности коррекции вновь принятого слова. Это позволяет потребителю принять решение о возможности или невозможности использования информации по выходу 1 устройства. Причем сигнал неправильной коррекции на контрольном выходе 2 формируется только тогда, когда характер искажения исходного слова превышает возможности кода. Прототип таким свойством не обладает, и поскольку правильная или неправильная коррекция в нем производится всегда, а информация о ее правильности или неправильности не выдается, то потребитель вынужден всегда использовать скорректированное или дополнительное искаженное слово, что может привести к нежелательным для него последствиям.

Формула изобретения Устройство для исправления ошибок, содержащее первый регистр, выходы всех разрядов которого соединены с адресными входами первого блока памяти и с информационными входами первого коммутатора, первый сумматор, выходы которого соединены с информационными входами второго регистра, выходы которого соединены с первыми входами первого сумматора и информационными входами третьего регистра, выходы которого соединены с информационными входами второго коммутатора, первый счетчик импульсов, выходы которого соединены с адресными входами второго, третьего блоков памяти и входами первого дешифратора, первый выход которого соединен с первым входом первого элемента ИЛИ, выходы третьего блока памяти соединены с первыми входами блока сравнения, второй счетчик импульсов, выходы которого соединены с входами второго дешифратора, первый и второй выходы которого соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом сброса второго счетчика импульсов, первый элемент НЕ, вход которого объединен с вторым входом второго элемента И, выход подключен к второму входу первого элемента И и первому входу третьего элемента И, третий счетчик импульсов, выходы которого соединен с входами третьего дешифратора, выходы которого соединены с входами третьего дешифратора, четвертый элемент ИЛИ, второй элемент НЕ, четвертый элемент И, четвертый регистр, триггер, выход которого соединен с первым входом пятого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, четвертый блок памяти, третий коммутатор, первый и второй элементы задержки, отличающееся тем, что, с целью упрощения устройства, в него введен втброй сумматор, информационный вход первого регистра является информационным входом устройства, вход сдвига информации первого регистра объединен со счетным входом второго счетчика импульсов и является входом синхронизации устройства, выходы первого блока памяти соединены с информационными входами третьего коммутатора, входы которого объединены с выходами первого коммутатора и соединены с вторыми входами первого сумматора, выходы второго коммутатора соединены с входами пэрал- лельного приема информации первого регистра, информационные входы второго и четвертого блоков памяти объединены и подсоединены к выходам всех разрядов первого регистра, вторые входы блока сравнения подключены к выходам младших разрядов первого регистра, выход старшего разряда является информационным выходом устройства, выходы четвертого блока памяти подключены к информационным входам третьего блока памяти, выход блока сравнения подключен к первому входу четвертого элемента И, выход которого соединен с входом последовательного приема информации четвертого регистра и со счетным входом третьего счетчика импульсов, выходы третьего дешифратора подключены к соответствующим входам четвертого элемента ИЛИ, выход которого является выходом контроля устройства, третий выход второго дешифратора соединен с вторым входом третьего элемента И, выход которого непосредственно соединен с входом Чтение второго блока памяти и через первый элемент задержки с входом Запись первого регистра, входы Чтение первого, четвертого блоков пгамяти, вход Запись второго блока памяти и вход первого элемента задержки объединены и подключены к выходу первого элемента И, выход первого элемента задержки соединен с входами Запись второго регистра и третьего блока памяти, вход Чтение третьего блока памяти подключен к выходу второго элемента И, вход Запись третьего регистра, первый вход триггера и второй вход пятого элемента И объединены и подключены к первому выходу первого дешифратора, второй выход которого непосредственно соединен с управляющим входом третьего коммутатора и через второй элемент НЕ с управляющим входом первого коммутатора, вторые входы первого, третьего, пятого элементов ИЛИ и триггера объединены и являются входом начальной установки устройства, выход пятого элемента ИЛИ подключен к входу сброса второго регистра, выходы второго блока памяти соединены с вторыми входами второго сумматора, выход первого элемента ИЛИ соединен с входами сброса первого и третьего счетчиков импульсов, счетный вход первого счетчика импульсов, вход сдвига информации четвертого регистра и второй вход четвертого элемента И объединены и подключены к выходу второго элемента ИЛИ, третий вход четвертого элемента И соединен с входом первого элемента НЕ и подключен к выходу триггера, выход четвертого регистра подключен к управляющему входу второго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1569996A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1989 |

|

SU1633497A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для исправления ошибок | 1989 |

|

SU1654825A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах памяти и обмена информации в системах шумопонижения цифровой зву- ко-, видеозаписи и воспроизведения. Целью изобретения является упрощение устройства. Устройство содержит регистры 3,7,8,29, блоки 4,13,14,15 памяти, коммутаторы 12, 9, 5, сумматоры 6, 10, элементы НЕ 11, 28, счетчики импульсов 16, 24, 32. дешифраторы 17, 25,33, элементы ИЛИ 26. 34, 35, 36, 38, триггер 27, элемент 30 эквивалентности. .1 ил. Выход Х| 00 со сх ю ю -| | ff6/jretf2

| Устройство для исправления ошибокВ СиСТЕМЕ ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU842820A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-12-23—Публикация

1990-02-13—Подача