(54) ДИСКРЕТНАЯ ЛИНИЯ ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Многоканальный фазометр | 1989 |

|

SU1720028A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

Изобретение относится к измерительной техник и технике радиосвязи и может быть использовано при приеме сиглапов с фазоразностной модуляцией и при измерении их параметров.

Известны устройства задержки, содержащие генератор тактовых импульсов, подключенный к регистру сдвига, каждый разряд которого состоит из триггера и двух элементов И, входной триггер в ,Q старшем разряде регистра, выходной формирователь, (W-l) регистров сдвига, аналогичных указанному, Vvi переключателей, причем в каждом регистре сдвига входная шина подключена к первым вхо- 15 дам всех элементов И данного регистра, вход каждого входного триггера подключен к выходу первых элементов И младшего и старшего разрядов своего регистра сдвига, нулевой выход входного триг- 20 гера подсоединен к разрешающему входу второго элемента И старшего разряда каждого регистра подключен к счетному входу триггера младшего разряда данного регистра, нулевой выход триггера каждого разряда регистра, кроме старшего соединен с вторым входом второго элемента И данного разряда, единичный выход триггера каждого разряда регистра сдвига подключен к второму входу первого элемента Инк соответствующему для каждого регистра сдвига переключателю установки вьщержки времени, нулевые контакты каждого из которых подсоединены к выходу генератора тактовых импульсов. Выходы всех переключателей подключены к соответствующим входам выходного формирователя, при этом выход первого элемента И старшего разря- Да каждого предыдущего регистра сдвига соединен с входной шиной последующего регистра сдвига Г.

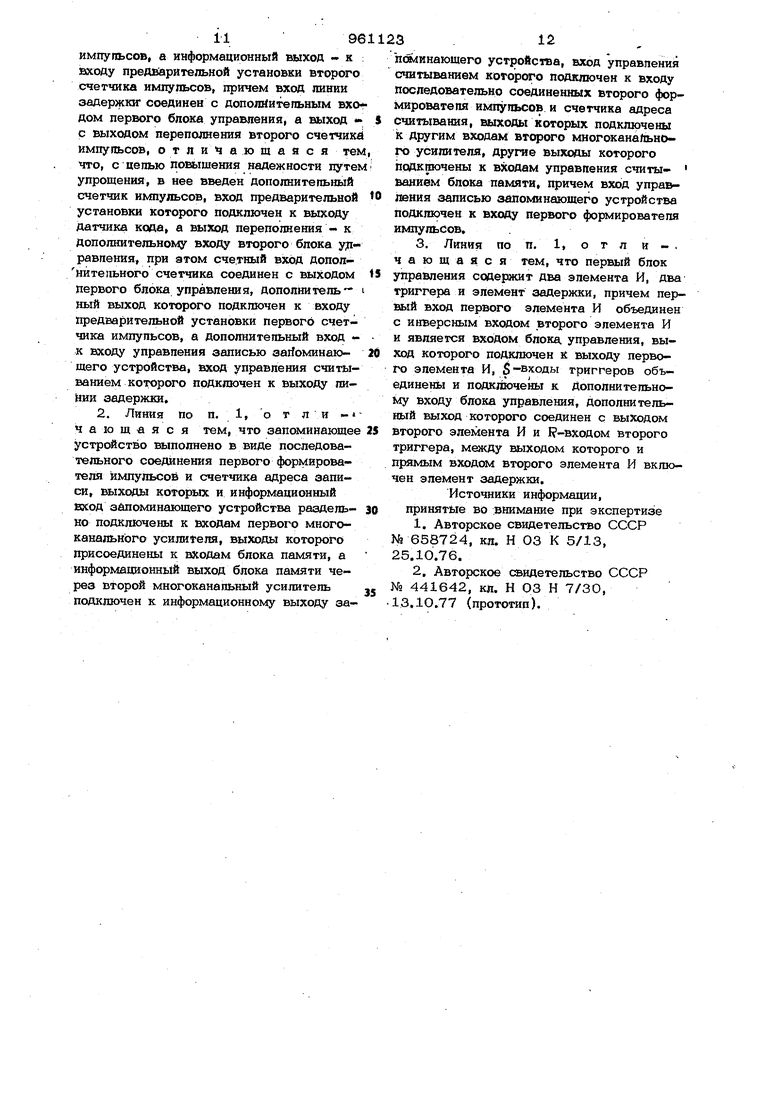

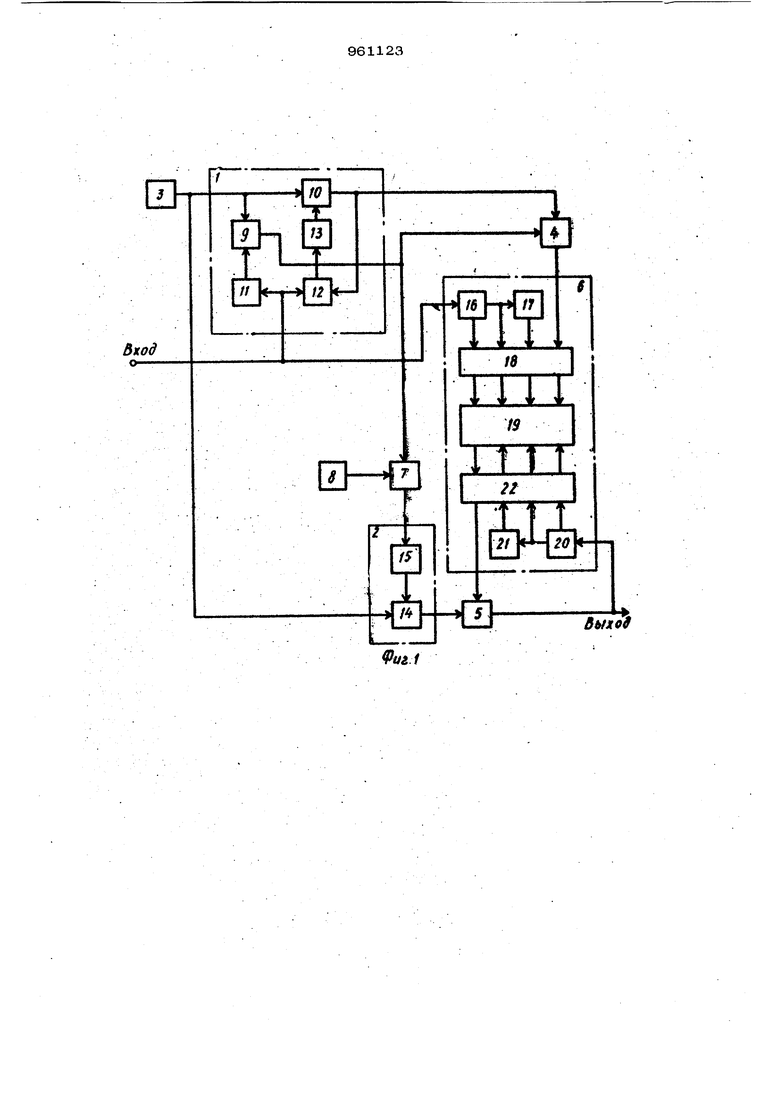

Недостатком этих устройств задержки является большой объем оборудования в тех случаях, когда максимальное время задержки во много раз превышает период следования входных импульсов. 396 Неиболее близким по технической сущности к предлагаемой является пиния за держки, содержащая датчик кода, генератор, первый и второй блоки управления, входы которых объединен л и подключены к выходу генератора, а выходы соединены со счетными входами соответственно первого и второго счетчиков импульсов, запоминающее устройство, информационный вход которого подключен к выходу первого счетчика импульсов, а информационный выход - к входу предварительной установки второго счетчика импупьсов, причем вход пинии задержки соединен с дополнительным входом первого блока управления, а выход -с выходом переполнения второго счетчика импульсов Регулировка времени задержки, превышающего период следования входных импуль сов, в указанном устройстве ос ществля- ется путем коммутации разрядов регист ра сдвига, вход которого подключен к вы ходу первого счетчика импульсов, а выход каждого разряда связан с выходом соответствующего разряда датчика кода 2}. Число разрядов регистра сдвига, а также число разрядов и число выводов датчика вода, которое необходимо для регулировки времени задержки ti, можно определить по формуле Эгмакс Т -величины максимального - Mctitc времени задержки; -минимальный период следования входных импульсов Так, если иммн ° ЮООО. Очевидно, что датчик кода и регистр сдвига, содержащие ЮООО раз рядов, отличаются повыщенной сложное тью, что приводит к усложнению конструк ции всей линии задержки и, соответствен но, уменыиению надежности. Цель изобретения - повышение надежности путем упрощения линии задержки. Указанная цель достигается тем, что в дискретную линию задержки, содержащую . датчик кода, генератор, первый и второй блоки управления, входы которых объединены и подключены к выходу генератора, а выходы соединены со счетными входами соответственно первого и второго счетчиков импульсов, запоминающее устройство, информационный вход которого подключен к выходу первого счетчика импульсов, а информационный выход к входу предварительной установки второ гчз счетчика импульсов, причем вход ли3нии задержки соединен с дополнительным входом первого блока управления, а выход - с выходом переполнения второго счетчика импульсов, введен дополнительный счетчик импульсов, вход предварительной установки которого подключен к выходу датчика кода, а выход переполненияк дополнительному входу второго блока управления, при этом счетный вход дополнительного счетчика соединен с выходом первого блока управления, дополнительнЬхй выход которого подключен к входу предварительной установки первого счетчика импульсов, а дополнительный вход к входу управления записью запоминающего устро йства, вход управления считыванием, которого подключен к выходу линии задержки. , Запоминающее устройство выполнено в виде поспеДовательного соединения первого формирователя импульсов и счетчика адреса записи, входы которых и информационный вход запоминающего устройства раздельно подключены к входам первого многоканального усилителя, выходы которого присоединень к входам блока памяти, а информационный выход блока памяти через второй многоканальный усилитель подключен к информационному выходу запоминающего устройства, подкп1оченного входом управления считыванием к входу последовательно соединенных второго формирователя импульсов и счетчика адреса считывания, выходы которых подключены к другим входам второго многоканального усилителя, другие выходы которого подключены к входам управления считыванием блока памяти, причем вход управления записью запоминающего устройства подключен к входу первого формирователя импульсов. Первый блок управления содержит два элемента И, Два триггера и элемент задержки, причем первый вход первого элемента И объединен с инверсным входом второго элемента И и является входом блока управления, выход которого подключен к выходу первого элемента И, S -входы триггеров объединены и подклкьчены к дополнительному входу блока управления, дополнительный выход которого соединен с выходом второго элемента И и R-входом второго триггера, между выходом которого и прямым входом второго элемента И подключен элемент задержки. На фиг. 1 представлена структурная схема дискретной линии задержки; на фиг. 2 - временные диаграммы, поясняющие ее работу. Дискретная линия задержки содержит первый блок 1 управления, второй блок 2 управления, генератор 4, первый счетчик 4 импульсов, второй счетчик 5 импупьсов, запоминающее устройство 6, дополнительный счетчик 7 импульсов и датчик 8 кода. Блок 1 управления содержит два элемента И 9 и 10, два триггер)а 11 к 12 элемент 13 задержки. Блок 2 управления содержит элемент И 14 и триггер 15, В состав запоминающего устройства 6 входят первый формирователь 16 импульсов, счетчик 17 адреса записи, первый многоканальный усилитель 18, блок 19 памяти, второй формирователь 20 импульсов, счетчик 21 адреса считывания и второй многоканальный усилитель 22. Входы первого блока 1 управления и второго блока 2 управления объединены и подключены к выходу генератора 3. Вы ход первого блока 1 управления соединен со счетным входом счетчика 4, а выход второго блока 2 управления - со счетным входом счетчика 5. Дополнительный выход первого блока 1 управления подкяючен к входу установки счетчика 4. Вы ход первого счетчика 4 импульсов, подключен к информационному входу запоминающего устройства 6, информационный выход которого связан с входом предварительной установки счетчика 5 импуль- сов. Вход управления записью запоминающего устройства 6 объединен с дополнительным входом первого блока 1 управле ния и подключен к входу дискретной ли НИИ задержки. Вход управления считыванием запоминающего устройства 6 объеди нен с выходом переполнения второго счет чика 5 импульсов и подключен к выходу дискретной линии задержки. Дополнительный вход второго блока 2 управления соединен с выходом переполнения До- полнительного счетчика 7 импульсов, сче ный вход которого связан с выходом первого блока 1 управления, а вход предварительной установки - с выходом датчика 8 кода. Первый вход элемента И 9 объ-, единен с инверсным входом элемента И 1О и является входом первого блока 1 управления. Второй вход элемента И 9 связан с выходом триггера 11, 5 -вход которого объединен с S-входом триггера 12 и подключен к допопнительному входу блока 1 управления, R-вход триггера 12 объединен с выходом элемента И 10 и является дополнительным выходом блока 1 управления, выход которого соединен с выходом элемента И 9. Вход элемента 13 задержки соединен с выходом триггера 12, а выход - с прямым входом элемента. И 10. Вход блока 2 управления подключен к первому входу элемента И 14, выход которого является выходом блока 2 управления. Второй вход / элемента И 14 соешнен с выходом триггера 15, 5-вход которого является дополнительным входом второго блока 2 уп равления. Вход управления записью запоминающего устройства 6 подключен к вхо ДУ первого формирователя 16 импульсов, выход которого, а также выходы счетчика 17 адрэса записи, вход которого соединен с первым выходом формирователя 16, и информационный вход запоминающего устройства 6 раздельно подключены к входам первого многоканального усилителя 18, выходы которого соединены с входами блока 19 памяти. При этом первый выход формирователя 16 через первый многоканальный усилитель 18 связан с входом разрешения выборки аДреса записи, второй выход формирователя 16с входом разрешения записи, выходы счетчика 17 адреса записи - с входами адреса записи, информационный вход запоминающего устройства 6 - с информационным входомблока 19 памяти. Вход управления считыванием запоминающего устройства 6 подключен к входу формирователя 2О импульсов, первый выход которого подключен к входу счетчика 21 адреса. Информационный выход блока 19 памяти через второй многоканальный усилитель 22 соединен с информационным выходом запоминающего устройства 6, Другие входы второго многоканального усилителя 22 соединены с выходами второго формирователя 2О и счетчика 21 адреса считывания, другие выходы - с входами управления считыванием блока 19 памяти. При этом первый выход формирователя 20 через многоканальный усилитель 22 связан с входом разрешения выборки адреса считывания, второй выход формирователя 20 - с входом разрешения считывания, выходы счетчика 21 с входами адреса считывания блока 19 памяти. Запоминающее устройство 6 предназначено для временного хранения кодов, поступающих на его информационный вход и последующей их вьщачи на информационный выход в том же порядке, в каком они поступили. Идбнтичные формироватет 16 и 20 I импульсов, являющиеся двухфаэшлми заторможенными мулыивибрагорами.формируют на своих первых выходах импульсы, длительность которых дбпжна быть не меньше времени выборки адресов записи 1л чтения в блоке 19 памяти. На выходах формирователей 16 и 20 формируется короткий импульс, разрешающий соответственно запись или считывание ин формации из блока 19. Блок 19 памяти представляет из себя оперативное запоминающее устройство с раздельными цепями записи и считывания информации. Блок реализует принципы- построения магнитных запоминающи устройств. Он может быть та1сже построен на базе микросхем запоминающих устройств серий 133, 155, 565 и других, имеющих выход информации в инверсном виде.Число разрядов в слове блока 19 равно числу разрядов счетчиков 4 и 5. Число слов соответствует емкости счетчиков 17 -к 21, Датчик 8 кода является регистром, предназначенным для хранения числа представленного в двоичном дополнитель-ном .коде, адёсь число К соответствует .требуемому времени задержки и определя ,ется из формулы ,,/Tr, время задержки; f - период следования импульсов - - 3. генератора Датчик 8 кода может быть построен . на статических R 5 -триггерах. В исходном состоянии первый счетчик 4 импульсов, счетчики 17 и 21, а также триггеры 11, 12 и 15 находятся в нулевом состоянии. При этом на выходах элементов И 9 и 14 отсутствуют импупь сы. Все разряды второго счетчика 5 импульсов находятся в единичном состоянии в дополнительном счетчике 7 импульсов установлен хранящийся в датчике 8 кода код числа К . Дискретная линия -задержки работает следующим образом. Первь1й импульс, поступивший на вход Дискретной линии задерл ки в момент Й (фиг. 2а), поступает также на .дополнительный вход первого блока 1 управле ния и устанавливает триггер 11 в единичное состояние. Тем самым разрешает- ся прохождение импульсов генератора 3 через элемент И 9 на выход блока 1 :удоавлення (фиг. 26). Эти импульсы на чинают поступать на счетные входы счетчиков 4 и 7, Далее первый блок 1 управления, первый счетчик 4 импульсов и запоминающее устройство 6 работают повторяющимися циклами в следующей поспедоватепь ности. Каждый входной импульс поступает в момент времени (фиг, 2а, i « 1, 2, 3, .,.) на дополнительный вход блока 1 управления и устанавливает триг-; 12 ъ единичное состояние. На выходе элемента 13 задержки эта логическая единица появляется через время задержки, которое должйо быть больше длительности цикла записи запоминающего устройства 6 ..но меньше периода следования импульсов генератора 3. Если в этот момент на инверсном.входе элемента И 1О действует импульс генератора 3, то на выходе элемента И 10 устанавливает1ся уровень логи гескрй единицы только после окончания действия импульса генератора 3. В противном случае уровень логической единицы устанавливается на выходе элемента И 1О сразу же после его установления на выходе элемента 13 задерлжи. После его появления триггер 12 возвращается в исходное нулевое состояние. Таким образом, на дополнительном выходе первого блока 1 управления формируется короткий импульс, задержанный относительно входного импульса и не совпадающий с импульсами генератора 3. Этот импульс воздействует на вход предварительной установки счетчика 4 и вызывает установку всех его разрядов в единичное состояние. Так как на счетный вход счетчика 4 продоягкают поступать импульсы с йыхода первого блока 1 управления, то к моментуt- прихода следующего входного импульса в счетчике 4 фиксируется число ( где N.-число импульсов, поступивщих с выхода блока 1 управления за интервал времени от i. до (фиг. 26, 1 1, 2, 3, ...). Выходной импульс в момент времени .посчупает н& вход управления записью за-поминающего устройства 6 и:вход первого формироззателя 16 импульсов. При этом на его первом выходе формируется импульс, который проходит через многоканальный усилитель 18 и разрещает выборку в блоке 19 памяти слоВа, адрес которого определяется кодом, .присутствующим на выходах разрядов счетчика 17. На втором выходе формирователя 16 формируется короткий импульс, который разрещает запись в выбранное слово блока 996 19памяти кода, присутствующего на инфррмационком входе запоминающего устройства 6, т.е. числа ..f. После окончания 1шкла записи отрицательным фронтом импульса на первом выходе формирователя 16 содержимое счетчика 17 увеличивается на 1, тем самым запоминающее уст ройство 6 подготавливается к приему нового кода. На этом цикл работы первого блока 1 управления, счетчика 4 и запо- минаюшего устройства 6 заканчивается. Так как первоначально в дополнительном счетчике 7 импульсов устанавпивает-ся число Kij., то после поступления на его счетный вход К импульсов с выхода первого блока 1 управления на выходе пе реполнения счетчика 7 появляется импуль который, поступив на дополнительный вход второго блока 2 управления устанавливает триггер 15 в единичное состояние и разрешает прохождение импульсов генератора 3 через элемент И 14. на его выход (фиг. 2в). Поскольку предварительно все разряды второго счетчика 5 установлены в единичное состояние,то первый же импульс, поступивший на его счетный вхо вызывает переполнение счетчика 5. Далее второй счетчик 5 и запоминающее устройство 6 работают повторяющимися импульсами следующим образом. Каждый импульс переполнения счетчика 5 в момент времени (фиг. 2г, i - 1, 2, 3, ...) проходит на вход управления считыванием запоминающего устройства 6 и вход второго формирователя 2О импульсов. При этом на его первом выходе формируется импульс, который проходит через многоканальный усилитель 22 и разрешает выборку в блоке 19 памяти слова, адрес которого определяется кодом, присутствующим на выходах разрядов счетчика 21. На втором выходе формирователя 2О формируется короткий импульс, который разрешает считывание информации из выбранного спова блока 19 памяти, т.е. инверсного кода числа Этот код, проходя через многоканалЬ ный усилитель 22, воздействует на вход предварительной установки счетчика 5 и записывается в него. Поступившие после этого Ni импульсов с выхода второго блока 2 управления вызывают переполнение счетчика 5 в момент времени (фиг. 2г, i 1, 2, 3, ...). На этом очередной цикл работы второго счетчика 5 импульсов и запоминающего устройства 6 заканчивается. Сформированный в конце 1шкла импульс в момент времени i по3ступаетна выход дискретнЬй пинии задержки. Как видно из временных диаграмм, представленных на фиг. 2, каждому входному импульсу соответствует импупьс на выходе дискретной линии задержки, отстоящий на время задержки, где Ati - случайная величина, не превышающая Т|(фиг. 2а, л 1, 2, 3, ....). При использовании двоичнЫ) системы счисления число разрядов дополнительного счетчика 7, а также число разрядов и число выводов датчика 8 кода может быть определено из формулы 0.- I г J Ц мн где Е обозначает функцию целая часть числа , . 1т г Так как.обычно VTt 1О-15, а при значениях времени задержки, во много раз превышающих период следования входныk импульсов, выполняется соогнощение рпл- g f waitc 1 ТТ и,н то На «И,Так, если |дад,( Иа 4О96, то h 26« мин «1000О. Очевидно, что за счет существенного уменьшения аппаратурных затрат и числа выводов датчика кода существенно упрощается конструкция всей дискрет-. ной линии задержки. Введение дополнительного счетчика импульсов позволяет упростить конструкцию дискретной линии задержки, повысить надежность, а также расширить рабочий диапазон времени задержки до 10О 2ОО с, что значительно расширяет возможные области применения ее в современной науке и технике. Формула изобретения 1. Дискретная линия задержки, содержащая датчик кода, генератор, первый и второй блоки управления, входы которых объединены и подключены к выходу генератора, а выходы соединены со счетными ходами соответственно первого и второго счетчиков импульсов, запоминающее устройство, информационный вход которого подключен к выходу первого счетчика

импупьсов, а информационный выход - к : входу преД ;арительной установки второго счетчика импульсов, причем вход линии задержки- соединен с дополните пьным вхог дом первого блока управления, а выход с выходом переполнения второго счетчик импупьсов, отличающаяся тем что, с цепью повышения надежности путем упрощения, в нее введен дополнительный счетчик импульсов, вход предварительной установки которого подключен к выходу датчика кода, а выход переполнения - к дополнительному входу второго блока урравления, при этом счетный вход дополнйтецьного счетчика соединен с выходом Первого блока управления, дополнитель яый выход которого подключен к входу предварительной установки первого счетчика импульсов, а дополнительный вход к входу управления записью эайоминающего устройства, вход управления считыванием которого подключен к выходу лийии задержки,

Источник;и информации, принятые во .внимание при экспертизе

сз

ч

«Ч

«)

NJ

Авторы

Даты

1982-09-23—Публикация

1980-11-28—Подача