Изобретение относится к контрольно-измерительной технике, может быть использовано для проверки функционирования и диагностики цифровых узлов и является дополнительным к основному авт. св. №1166120.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения автоматического контроля блоков оперативной памяти. .

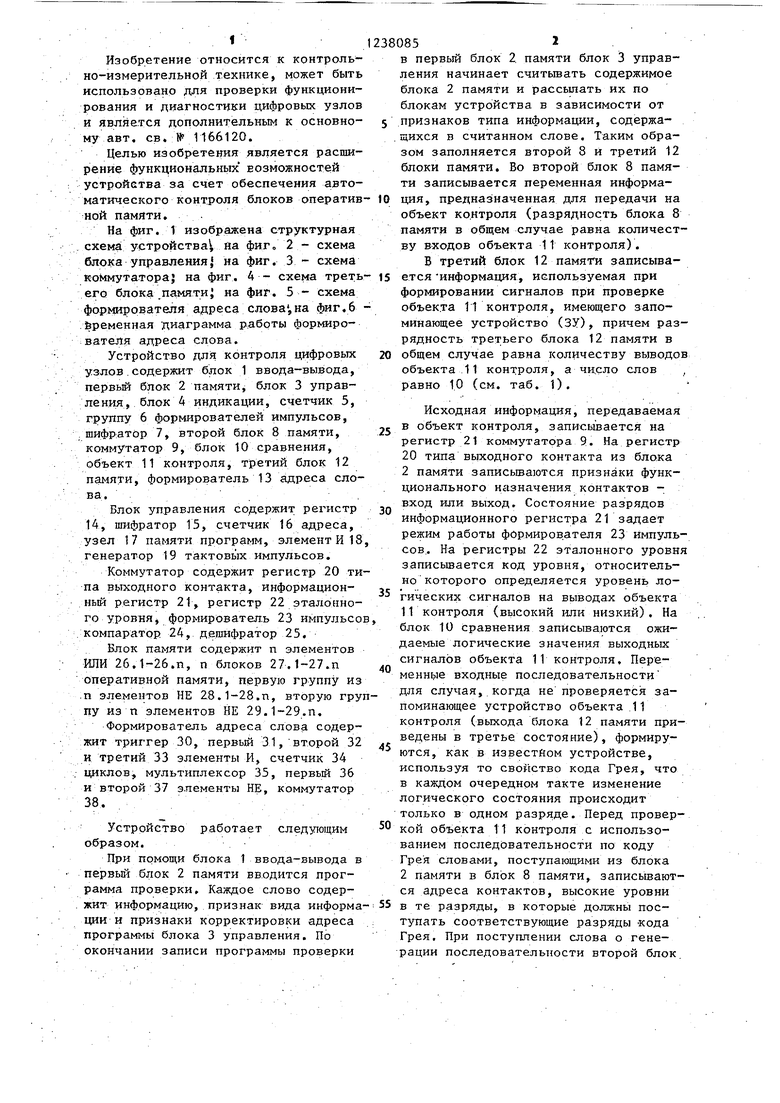

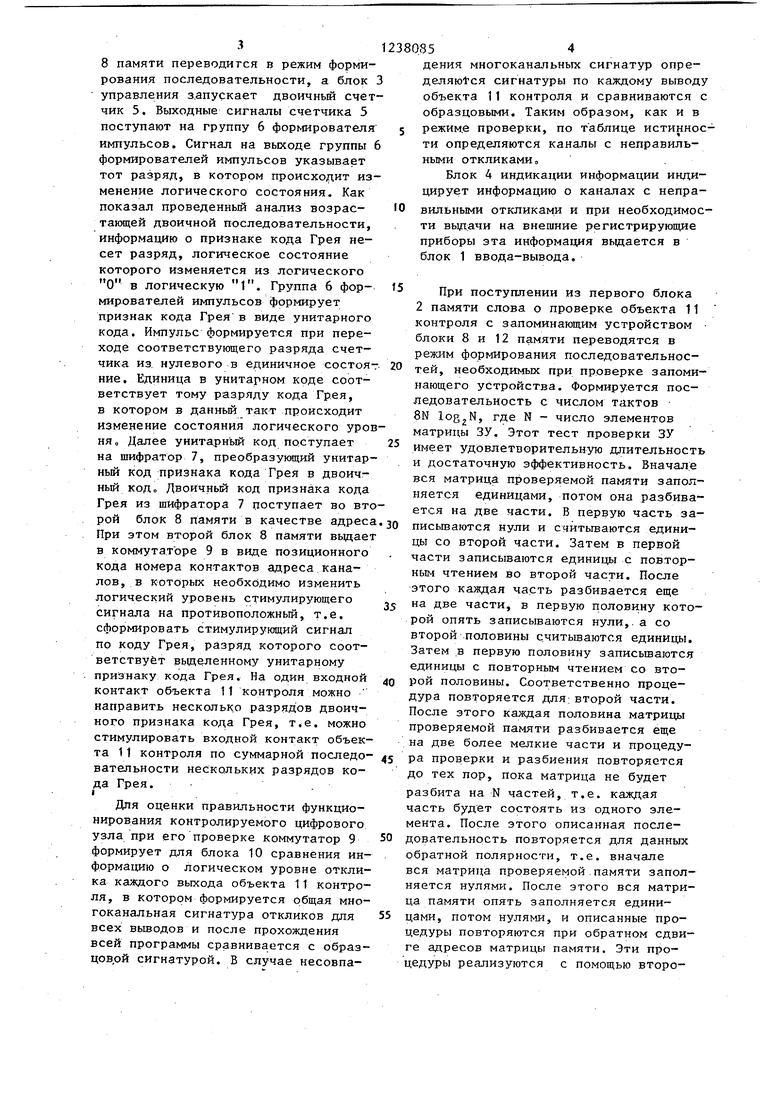

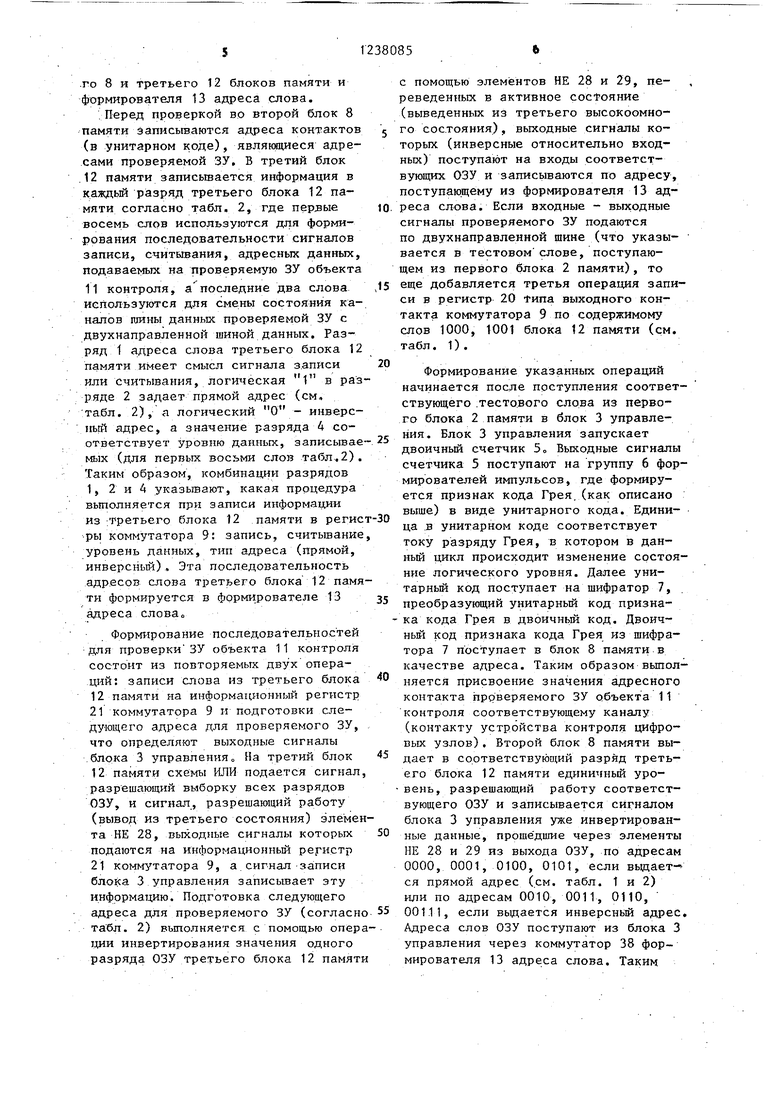

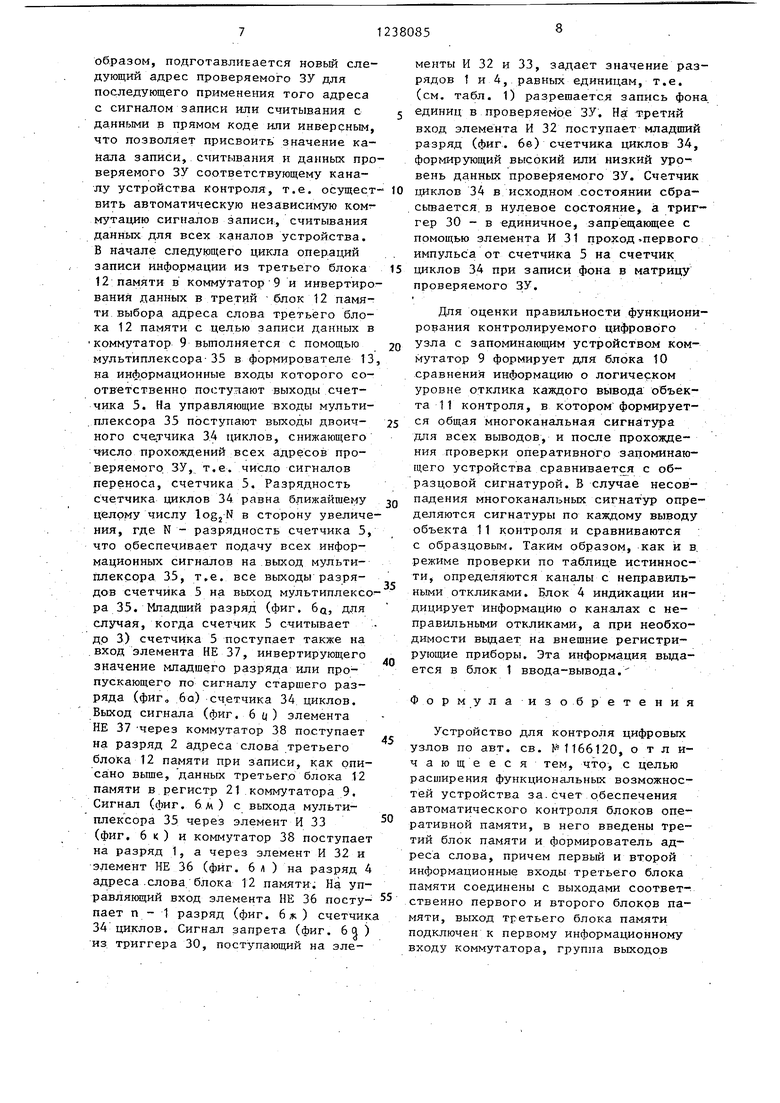

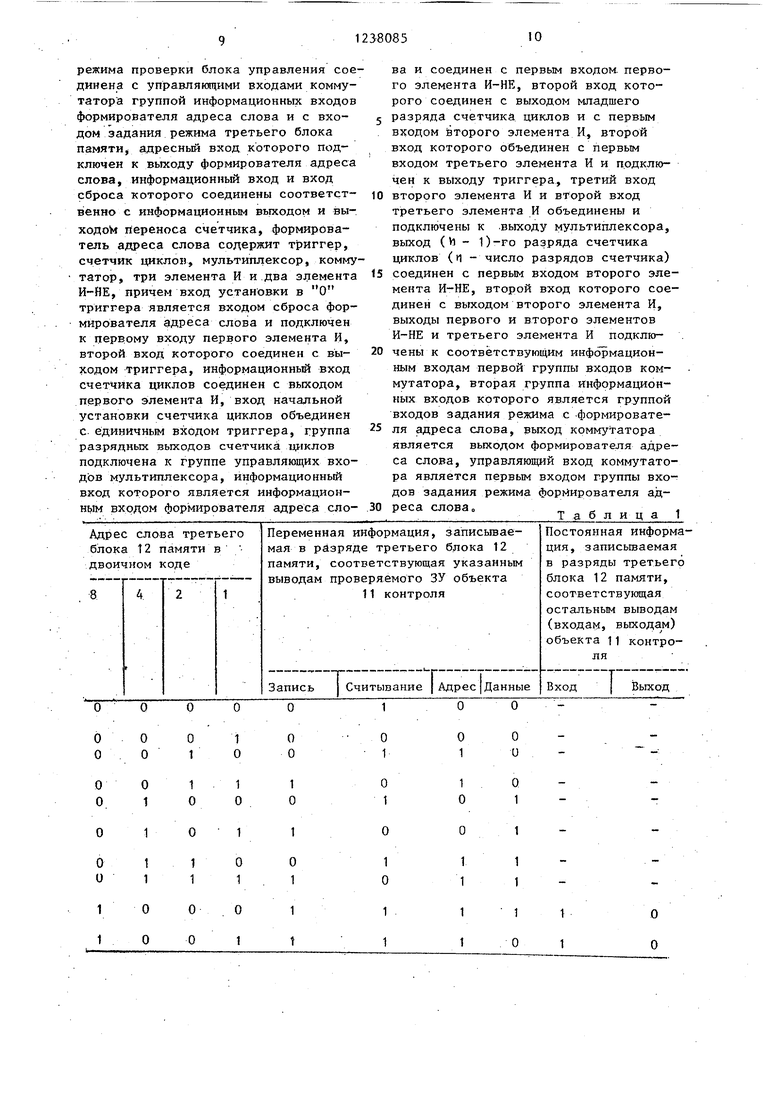

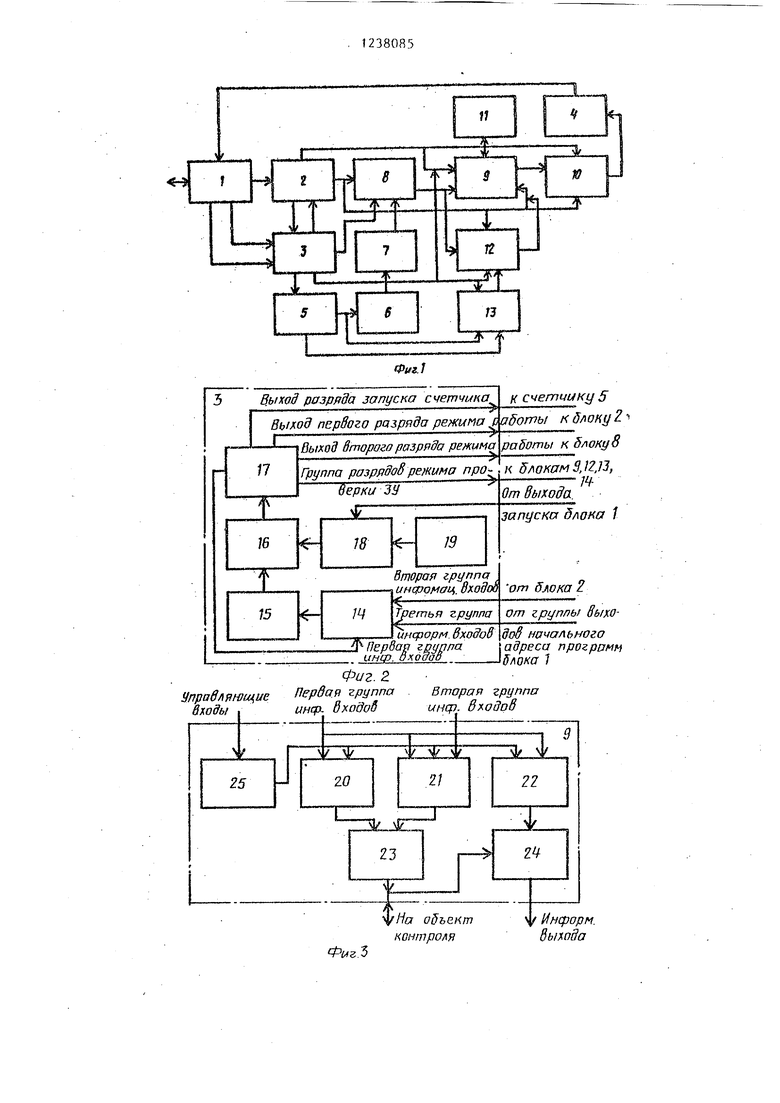

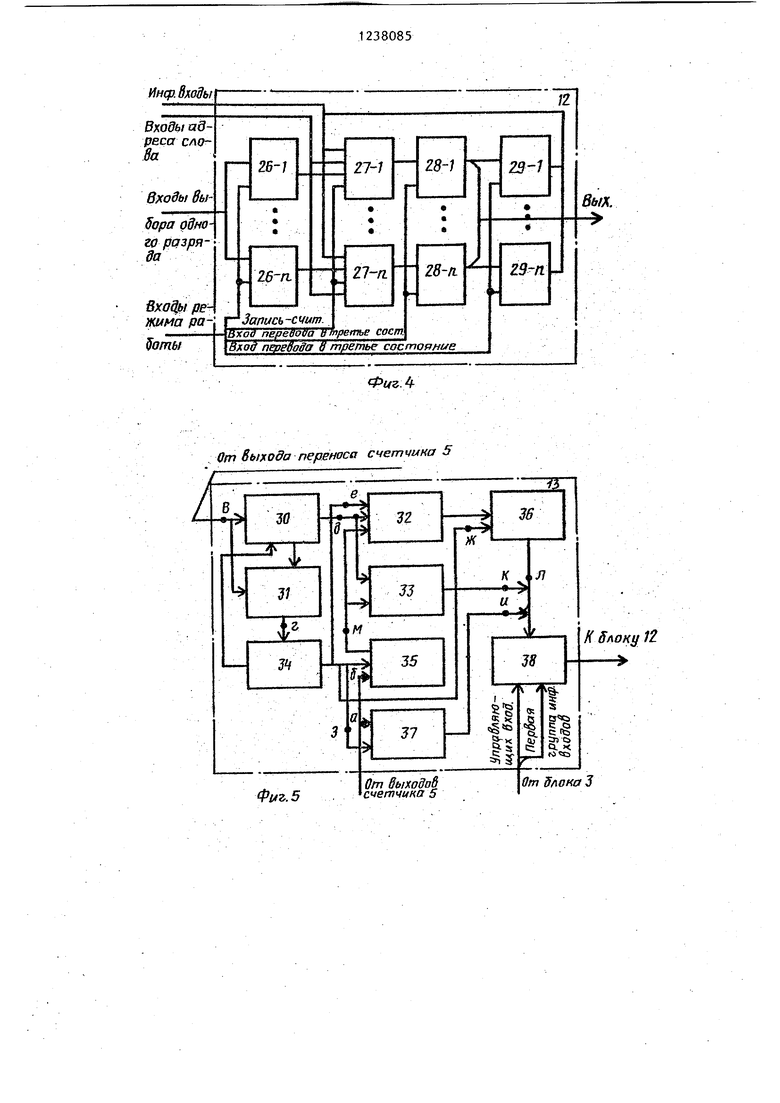

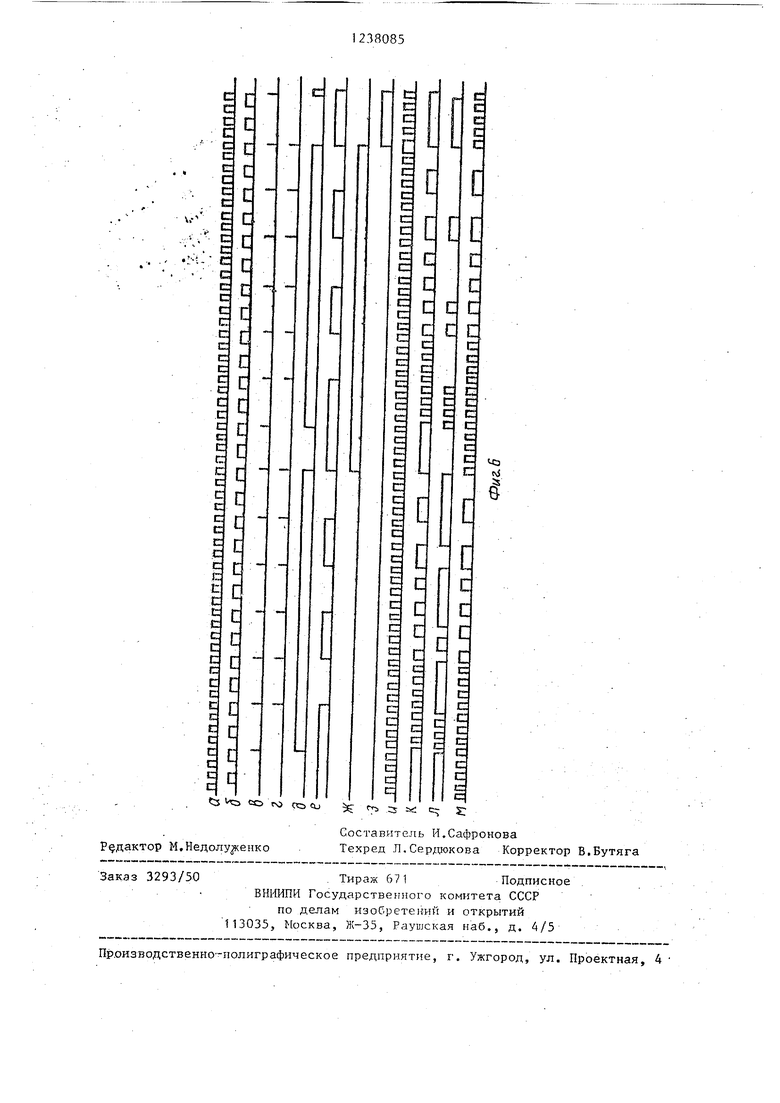

На фиг. 1 изображена структурная схема ycтpoйcтвaV йа фиг, 2 - схема блока управления) на фиг. 3 - схема коммутатора; на фиг. 4 - схема третьего блока .памятиJ на фиг. 5 - схема фор 1Ирователя адреса слова ,на фиг.6 .бременная диаграмма работы формирователя адреса слова.

Устройство для контроля цифровых узлов.содержит блок 1 ввода-вывода, первьй блок 2 памяти, блок 3 управления, блок 4 индикации, счетчик 5, группу 6 формирователей импульсов, шифр:атор 7, второй блок 8 памяти, коммутатор 9, блок 10 сравнения, объект 11 контроля, третий блок 12 памяти, формирователь 13 адреса слова.

Блок управления содержит регистр 14, шифратор 15, счетчик 16 адреса, узел 17 памяти программ, элемент И 18 генератор 19 тактовых импульсов.

Коммутатор содержит регистр 20 типа выходного контакта, информацион- ньй регистр 21, регистр 22 эталонного уровня, формирователь 23 импульсо компаратор 24, дешифратор 25.

Блок памяти содержит п элементов ИЛИ 26.1-26.п, п блоков 27.1-27.П оперативной памяти, первую группу из .п элементов НЕ 28.1-28.п, вторую гру пу из п элементов НЕ 29.1-29.П.

Формирователь адреса еловд содержит триггер 30, первый 31, второй 32 и третий 33 элементы И, счетчик 34 циклов, мультиплексор 35, первый 36 и второй 37 элементы НЕ, коммутатор 38. .

Устройство работает следующим образом.

При помощи блока 1 ввода-вывода в первьй блок 2 памяти вводится программа проверки. Каждое слово содержит информацию, признак вида информации и признаки корректировки адреса программы блока 3 управления. По окончании записи программы проверки

380852

в первьй блок 2 памяти блок 3 управления начинает считьгоать содержимое блока 2 памяти и рассылать их по блокам устройства в зависимости от

5 признаков типа информации, содержа- .щихся в считанном слове. Таким образом заполняется второй 8 и третий 12 блоки памяти. Во второй блок 8 памяти записывается переменная информа0 ция, предназначенная для передачи на объект контроля (разрядность блока 8 памяти в общем случае равна количеству входов объекта 11 контроля).

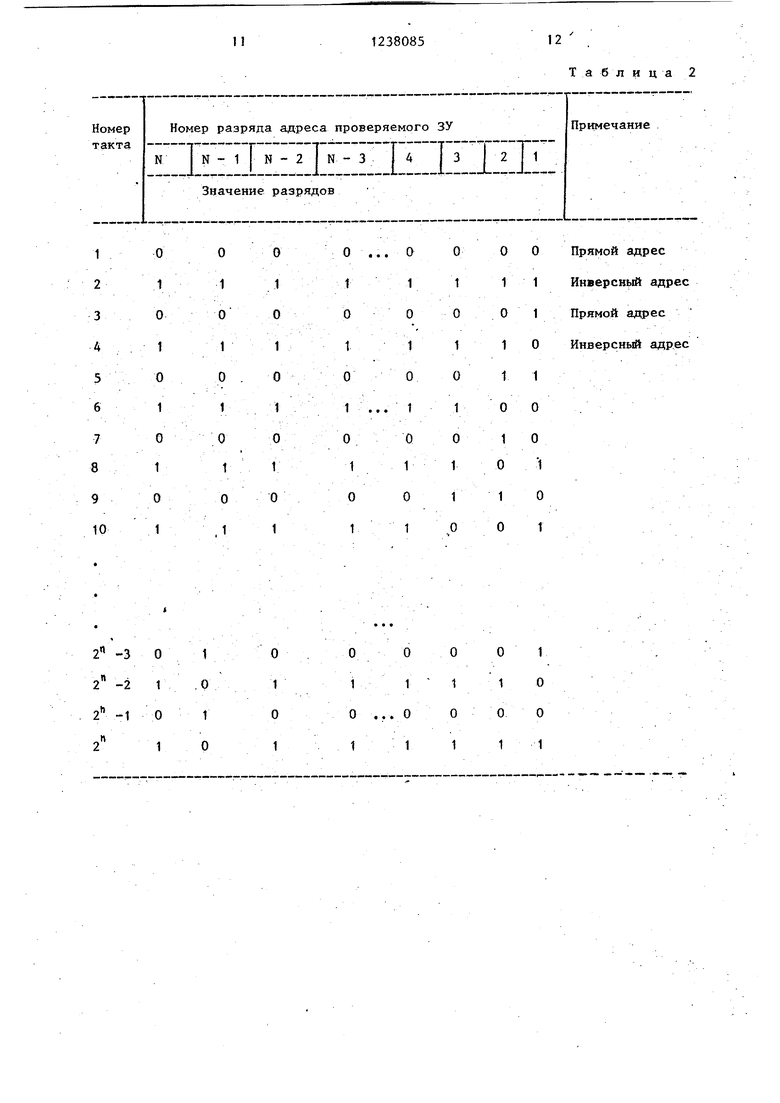

В третий блок 12 памяти записыва5 ется информация, используемая при формировании сигналов при проверке объекта 11 контроля, имеющего запоминающее устройство (ЗУ), причем разрядность третьего блока 12 памяти в

20 общем случае равна количеству выводов объекта 11 контроля, а чи.сло слов равно 10 (см. таб. 1).

5

0

5

0

5

0

5

Исходная информация, передаваемая в объект контроля, записывается на регистр 21 коммутатора 9. На регистр 20 типа выходного контакта из блока 2 памяти записьтаются признаки функционального назначения контактов - вход или выход. Состояние разрядов информационного регистра 21 задает режим работы формирователя 23 импульсов.. На регистры 22 эталонного уровня записьшается код уровня, относительно которого определяется уровень логических сигналов на выводах объекта 11 контроля (высокий или низкий). На блок 10 Сравнения записываются ожидаемые логические значения выходных сигналов объекта 11 контроля. Переменные входные последовательности для случая, когда не проверяется запоминающее устройство объекта 11 контроля (выхода блока 12 памяти приведены в третье состояние), формируются, как в известйом устройстве, используя то свойство кода Грея, что в каждом очередном такте изменение логического состояния происходит только в одном разряде. Перед проверкой объекта 11 контроля с использованием последовательности по коду Грея словами, поступающими из блока 2 памяти в блок 8 памяти, записьшают- ся адреса контактов, высокие уровни в те разряды, в которые должны поступать соответствующие разряды кода Грея. При поступлении слова о генерации последовательности второй блок.

8 памяти переводится в режим формирования последовательности, а блок управления з.апускает двоичный счетчик 5, Выходные сигналы счетчика 5 поступают на группу 6 формирователя импульсов. Сигнал на выходе группы формирователей импульсов указывает тот разряд, в котором происходит изменение логического состояния. Как показал проведенный анализ возрас- тающей двоичной последовательности, информацию о признаке кода Грея несет разряд, логическое состояние которого изменяется из логического О в логическую 1. Группа 6 фор- мировате.лей импульсов формирует признак кода Грея в виде унитарного кода. Импульс формируется при переходе соответствующего разряда счетчика из. нулевого в единичное состоя ние. Единица в унитарном коде соответствует ТОМУ разряду кода Грея, в котором в данньй такт происходит изменение состояния логического уроня. Далее унитарный код поступает на шифратор 7, преобразующий унитарный код признака кода Грея в двоичный код. Двоичный код признака кода Грея из шифратора 7 поступает во втрой блок 8 памяти в качестве адрес При этом второй блок 8 памяти вьщае в коммутаторе 9 в виде позиционного кода номера контактов адреса каналов, в которых необходимо изменить логический уровень стимулирующего сигнала на противоположный, т.е. сформировать стимулирующий сигнал по коду Грея, разряд которого соответствует вьщеленному унитарному признаку кода Грея. На один входной контакт объекта 11 контроля можно направить несколько разрядов двоичного признака кода Грея, т.е. можно стимулировать входной контакт объекта 11 контроля по суммарной поеледо- вательности нескольких разрядов кода Грея. . I

Для оценки правильности функционирования контролируемого цифрового узла при его проверке коммутатор 9 формирует для блока 10 сравнения ин- формагщю о логическом уровне отклика каждого выхода объекта 11 контроля, в котором формируется общая многоканальная сигнатура откликов для всех выводов и после прохождения всей программы сравнивается с образ- цоврй сигнатурой. В случае несовпа

5 Ю f5 20 25 зо 0 5

0 . 5

5

дения многоканальных сигнатур определяются сигнатуры по каждому выводу объекта 11 контроля и сравниваются с образцовыми. Таким образом, как и в режиме проверки, по таблице истинности определяются каналы с неправильными откликами

Блок 4 индикации информации индицирует информацию о каналах с неправильными откликами и при необходимости выдачи на внешние регистрирующие приборы эта информация выдается в блок 1 ввода-вывода.

При поступлении из первого блока 2 памяти слова о проверке объекта 11 контроля с запоминающим устройством блоки 8 и 12 памяти переводятся в режим формирования последовательностей, необходимых при проверке запоминающего устройства. Формируется последовательность с числом тактов 8N , где N - число элементов матрицы ЗУ. Этот тест проверки ЗУ имеет удовлетворительную длительность и достаточную эффективность. Вначал;е вся матрица проверяемой памяти заполняется единицами, потом она разбивается на две части. В первую часть за- письгоаются нули и считьгеаются единицы со второй части. Затем в первой части записываются единицы с повторным чтением во второй части. После этого каждая часть разбивается еще на две части, в первую половину которой опять записываются нули,, а со второй -ПОЛОВИНЫ считываются единицы. Затем в первую половину записьшаются единицы с повторным чтением со второй половины. Соответственно процедура повторяется ДЛЯ:второй части. После этого каждая половина матрицы проверяемой памяти разбивается еще на две более мелкие части и процедура проверки и разбиения повторяется до тех пор, пока матрица не будет разбита на N частей, т.е. каждая часть будет состоять из одного элемента. После этого описанная последовательность повторяется для данных обратной полярности, т.е. вначале вся матрица проверяемой памяти заполняется нулями. После этого вся матрица памяти опять заполняется единицами, потом нулями, и описанные процедуры повторяются при обратном сдвиге адресов матрицы памяти. Эти процедуры реализуются с помощью второо 8 и третьего 12 блоков памяти и ормирователя 13 адреса слова.

.Перед проверкой во второй блок 8 амяти записываются адреса контактов j (в унитарном коде), являнлдиеся адресами проверяемой ЗУ, В третий блок 12 памяти записьшается информация в каждьй разряд третьего блока 12 памяти согласно табл. 2, где пер:вые ю. восемь слов используются для формиования последовательности сигналов записи, считывания, адресных данных, одаваемых на проверяемую ЗУ объекта

11 контроля, а последние два слова ,15 используются для смены состояния каналов гаины данных проверяемой ЗУ с двухнаправленной шиной данных. Разряд 1 адреса слова третьего блока 12 памяти имеет смысл сигнала з.аписи 20 или считывания, логическая 1 в разряде 2 задает прямой адрес (см, табл. 2), а логический О - инверс- ьгй адрес, а значение разряда 4 соответствует уровню данных, записывае-. 25 мых (для первьгх восьми слов табл.2) . Таким образом, комбинации разрядов 1, 2 и 4 указьгоают, какая процедура вьтолняется при записи информации из третьего блока 12 памяти в регист-30 ры коммутатора 9: запись, считывание, уровень данных, тип адреса (прямой, инверсньй). Эта последовательность адресов слова третьего блока 12 памяти формируется в формирователе 13 35 адреса слова,,

Формирование последовательностей для проверки ЗУ объекта 11 контроля состоит из повторяемых двУх операций: записи слова из третьего блока 0 12 памяти на информационный регистр 21 коммутатора 9 и подготовки следующего адреса для проверяемого ЗУ, что определяют выходные сигналы блока 3 управления На третий блок 5 12 памяти схемы ИЛИ подается сигнал, разрешающий выборку всех разрядов ОЗУ, и сигнал, разрешающий работу (вывод из третьего состояния) элемента НЕ 28, выходные сигналы которых 50 подаются на информационньй регистр 21 коммутатора 9, а сигнал записи блока 3 управления записывает эту информацию. Подготовка следующего адреса для проверяемого ЗУ (согласно 55 табл. 2) вьтолняется с помощью опера- 1.1ии инвертирования значения одного разряда ОЗУ третьего блока 12 памяти

с помощью элементов НЕ 28 и 29, переведенных в активное состояние (выведенных из третьего высокоомно- го сос.тояния), выходные сигналы которых (инверсные относительно входных) поступают на входы соответствующих ОЗУ и записываются по адресу, поступающему из формирователя 13 ад реса слова. Если входные - выходные сигналы проверяемого ЗУ подаются по двухнаправленной шине (что указывается в тестовом слове, поступающем из первого блока 2 памяти), то еще добавляется третья операция записи в регистр 20 Типа выходного контакта коммутатора 9 по содержимому слов 1000, 1001 блока 12 памяти (см. табл. 1) .

Формирование указанных операций начинается после поступления соответствующего .тесто.вого слова из первого блока 2 памяти в блок 3 управления. Блок 3 управления запускает двоичный счетчик 5 Выходные сигналы счетчика 5 поступают на группу 6 формирователей импульсов, где формируется признак кода Грея.(как описано выше) в виде унитарного кода. Единица .в унитарном коде соответствует току разряду Грея, в котором в данный цикл происходит изменение состояние логического уровня. Далее уни- тарньй код поступает на шифратор 7, преобразующий унитарньй код признака кода Грея в двоичньй код. Двоич- ньй код признака кода Грея из шифратора 7 поступает в блок 8 памяти в качестве адреса. Таким образом выполняется присвоение значения адресного контакта проверяемого ЗУ объекта 11 контроля соответствующему каналу (контакту устройства контроля цифровых узлов). Второй блок 8 памяти выдает в сортветствуюпщй разряд третьего блока 12 памяти единш(ный уровень, разрешающий работу соответствующего ОЗУ и записывается сигналом блока 3 управления уже инвертированные данные, прошедшие через элементы ИЕ 28 и 29 из выхода ОЗУ, по адресам 0000, 0001, 0100, 0101, если вьиается прямой адрес (см. табл. 1 и 2) или по адресам 0010, 0011, 0110, 00111, если вьодается инверсньй адрес Адреса слов ОЗУ поступают из блока 3 управления через коммутатор 38 формирователя 13 адреса слова. Таким

образом, подготавлиЕзется новый следующий адрес проверяемого ЗУ для последующего применения того адреса с сигналом записи шти считывания с данными в прямом коде или инверсным, что позволяет присвоить значение ка- йала записи, считывания и данных про веряеиого ЗУ соответствующему каналу устройства Контроля, т.е. осущест вить автоматическую независимую коммутацию сигналов записи, считывания данных для всех каналов устройства. В начале следующего цикла операций записи информации из третьего блока 12; памяти в коммутатор 9 и инвертирования данных в третий -блок 12 памяти выбора адреса слова третьего блока 12 памяти с целью записи данных в

коммутатор 9 выполняется с помощью мультиплексора-35 в формирователе 13 на информационные входы которого соответственно поступают выходы счетчика 5. На управляющие входы мульти.плексора 35 поступают выходы двоич- ного счетчика 34 циклов, снижающего число прохождений всех адресов проверяемого. ЗУ, т.е. число сигналов переноса, счетчика 5. Разрядность счетчика циклов 34 равна ближайшему целому числу в сторону увеличения, где N - разрядность счетчика 5, что обеспечивает подачу всех информационных сигналов на выход мультиплексора 35, т.е. все вькоды разря- дов счетчика 5 на выход мультиплексора 35. Мпадший разряд (фиг. 6а, для случая, когда счетчик 5 считывает до 3) счетчика 5 поступает также на

.вход элемента НЕ 37, инвертирующего значение младшего разряда или пропускающего по сигналу старшего разряда (фиг, 6а) счетчика 34 циклов. Выход сигнала (фиг. 6 ц) элемента НЕ 37 через коммутатор 38 поступает на разряд 2 адреса слова третьего блока 12 памяти при записи, как опи- вьше, данных третьего блока 12 памяти в регистр 21 коммутатора 9. Сигнал (фиг. 6м) с выхода мультиплексора 35 через элемент И 33 (фиг, 6 к ) и KOMi-iyTaTop 38 поступает на разряд 1, а через элемент И 32 н элемент НЕ 36 (фиг. 6л ) на разряд 4 адреса .слова блока 12 памяти. На уп- равлянщий вход элемента НЕ 36 посту- пает п - 1 разряд (фиг. 6) счетчик 34 циклов. Сигнал запрета (фиг. 6а ) из триггера 30, поступающий на эле

j 10 15

20

25 о

0

5

менты И 32 и 33, задает значение разрядов 1 и 4, равных единицам, т.е. (см. табл. 1) разрешается запись фона, единиц в проверяемое ЗУ. На третий вход элемента И 32 поступает младший разряд (фиг. бе) счетчика циклов 34, формирующий высокий или низкий уро- вень данных проверяемого ЗУ. Счетчик циклов 34 в исходном .состоянии сбра- сьгоается. в нулевое состояние, а триггер 30 - в единичное, запрещающее с помощью элемента И 31 проход«первого импульса от счетчика 5 на счетчик циклов 34 при записи фона в матрицу проверяемого ЗУ.

Для оценки правильности функционирования контролируемого цифрового узла с запоминающим устройством коммутатор 9 формирует дпя блока 10 сравнения информацию о логическом уровне отклика каждого вывода объекта 1 1 контроля, в котором формируется общая многоканальная сигна;тура для всех выводов, и после прохождения проверки оперативного запоминающего устройства сравнивается с образцовой сигнатурой. В случае несовпадения многоканальных сигнатур определяются сигнатуры по каждому выводу объекта 11 контроля и сравниваются ; с образцовым. Таким образом, как и в, режиме проверки по таблице истинности, определяются каналы с неправипь- ными откликами. Блок 4 индикации индицирует информацию о каналах с неправильными откликами, а при необходимости вьщает на внешние регистрирующие приборы. Эта информация вьща- ется в блок 1 ввода-выво;а;а,

Формула из обре те ния

Устройство для контроля цифровых узлов по авт. св. N 1166120, отличающееся тем, что, с целью расширения функциональных возможностей устройства за.счет обеспечения автоматического контроля блоков оперативной памяти, в него введены третий блок памяти и формирователь адреса слова, причем первый и второй информационные входы третьего блока памяти соединены с выходами соответственно первого и второго блоков памяти, выход третьего блока памяти подключен к первому информационному входу коммута.тора, группа выходов

режима проверки блока управления соединена с управляющими входами коммутатора группой информационньк входов формирователя адреса слова и с входом задания режима третьего блока памятиJ адресный вход которого подключен к выходу формирователя адреса слова, информационный вход и вход сброса которого соединены соответственно с информационным выходом и выходов переноса счетчика, формирователь адреса слова содержит триггер, счетчик циклоп, мультиплексор, коммутатор, три элемента И и .два элемента И-НЕ, причем вход установки в О триггера является входом сброса формирователя адреса слова и подключен к ггерв.ому входу первого элемента И, второй вход которого соединен с выходом триггера, информационньй вход счетчика циклов соединен с выходом первого элемента И, вход начальной установки счетчика циклов объединен с. единичным входом триггера, группа разрядных выходов счетчика циклов подключена к группе управляющих входов мультиплексора, информационный вход которого является информационным входом формирователя адреса слова и соединен с первьп входом, первого элемента И-НЕ, второй вход которого соединен с выходом младшего разряда счетчика циклов и с первым входом йторого элемента И, второй вход которого объединен с первым входом третьего элемента И и п.одклю- чен к выходу триггера, третий вход

второго элемента И и второй вход третьего элемента И объединены и подключены к .выходу мультиплексора, выход (И - 1)-го разряда счетчика циклов (и - число разрядов счетчика)

соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом второго элемента И, выходы первого и второго элементов И-НЕ и третьего элемента И подклю-

чены к соответствующим информационным входам первой группы входов коммутатора, вторая группа информационных входов которого является группой входов задания режима с формирователя адреса слова, выход коммутатора является выходом формирователя адреса слова, управляющий вход коммутатора является первым входом группы входов задания режима формирователя ад30 реса слова.

Таблица 1

о 1

1 о

о и

о 1

о о

Таблица 2

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1166120A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для контроля радиотехническихОб'ЕКТОВ | 1979 |

|

SU796859A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано для проверки функционирования и диагностики цифровых узлов. Изобретение является усовершенствованием устройства по основному авт. св. № 1166120. Изобретение позволяет расширить функциональные возможности за счет обеспечения автоматического контроля блоков оперативной памяти. В устройство содержащее блок ввода-вывода, первый блок памяти, блок-управления, блок индикации, счетчик, группу формирователей импульсов, шифратор, второй блок памя ти, коммутатор, блок сравнения, введены третий блок памяти и формирователь адреса слова, 6 ил. , с & (Л С

Фиг. 2

Управляющие Первая группа вхо ыинср. Вуодоб

4l3lLj

Вторая группа uHqj.

23

24

.Ъ

На объект контроля

ф Инсрорм. выхода

Инср. дходы

Входь адреса слова

2В-1

в)(овы выSopa odfiow разряда

16-п

Запчсь-счит

BxaS перевода оп ретье сост.

{Bixoff nepeooffoWmpsmbe состояние

От Выхода переноса счетчина 5

/2

27-1

Вь/Х. -

Zl-fi

28-п

Z9-n

Ф(zЛ

1

30

Ф{4г.5

От быходаб счетчика 5

От длока J

СЗ Irs O tNj со Си 5

Редактор М.Недолу еико

Составитель И.Сафронова

Техред Л.Сердгокова Корректор В.Бутяга

Заказ 3293/50

. Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, ocквa, , Рауи;ская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

f ,3 crj S;

| Устройство для контроля цифровых узлов | 1983 |

|

SU1166120A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1985-01-07—Подача