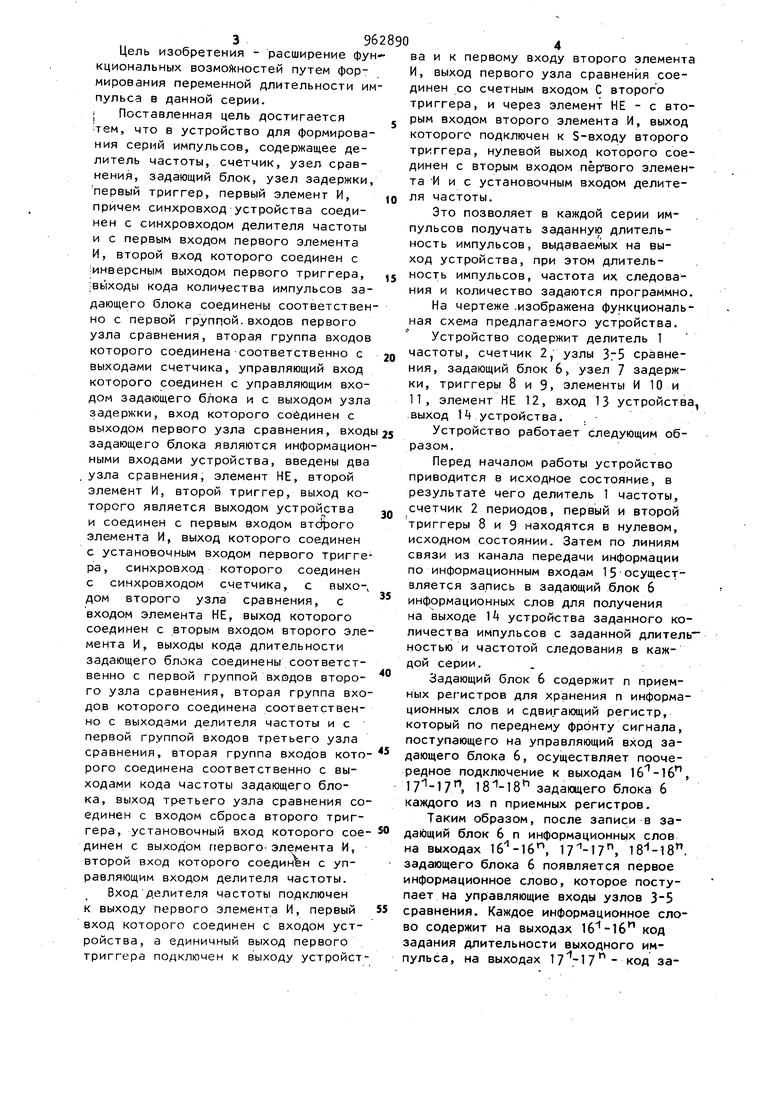

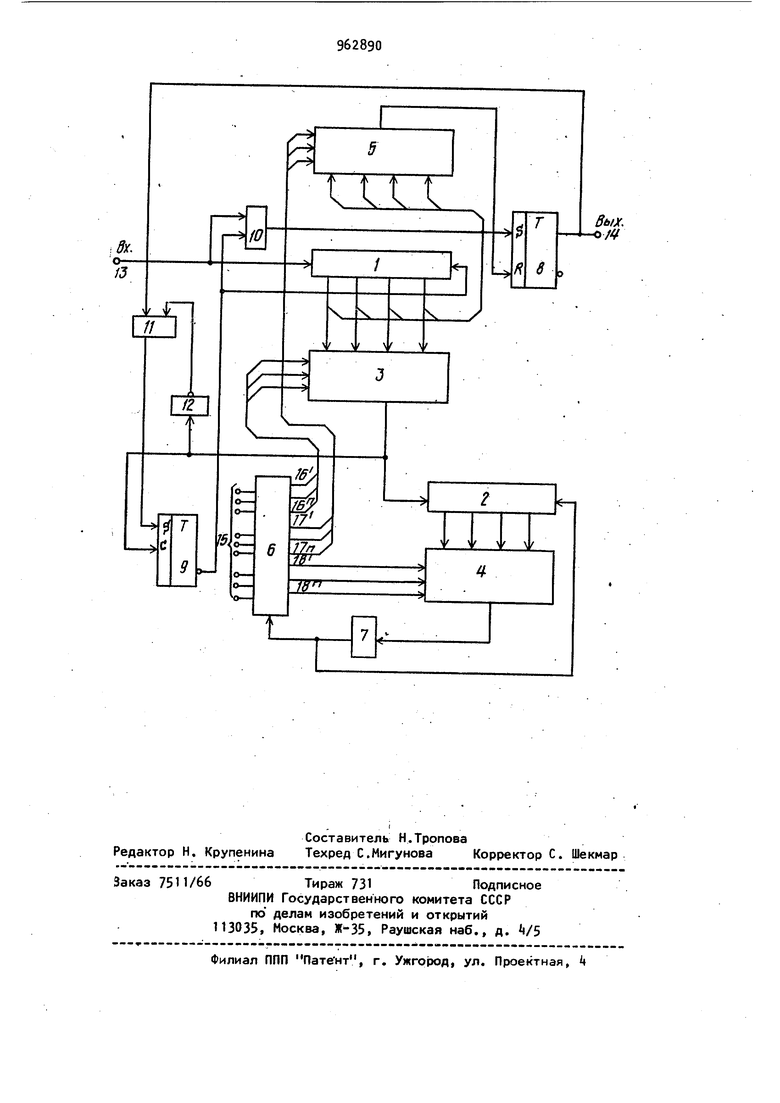

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления, а также в устройствах вычислительной техники. Известен формирователь серий импульсов, содержащий программное устройство, регистр сдвига, счетчик цик лов, генератор тактовых импульсов, л нию задержки, блок записи единиц, элементы И 1. . Однако указанное устройство не обеспечивает выдачу переменного коли чества импульсов в данной серии изза отсутствия возможности менять емкость счетчика циклов. Это не позволяет использовать устройство для построения делителей частоты с перемен ным коэффициентом деления, что часто требуется в системах автоматики и вычислительной техники. Наиболее близким к предлагаемому является формирователь серий импульсов, содержащий делитель частоты, вход которого соединен с входом устройства, а выходы соединены с установочным входом первого узла сравнения, управляющие входы которого соединены с выходами кода частоты следования импульсов задающего блока, выход первого узла сравнения соединен с входом счетчика периодов, которого соединены с установочными входами второго узла сравнения, управляющие входы которого соединены с выходами кода количества импульсов задающего блока, выход второго узла сравнения через узел задержки соединен с установочным входом счетчика периодов и с управляющим входом задающего блока, триггер, элементы И С2, Однако известное устройство не обеспечивает выдачу переменной длительности импульсов в данной серии, ,что часто требуется в системах за- . томатического управления. Это сужает функциональные возможности устройства. 396 Цель изобретения - расширение фун кциональных возмоя ностей путем формирования переменной длительности им пульса в данной серии. I Поставленная цель достигается ;тем, что в устройство для формирования серий импульсов, содержащее делитель частоты, счетчик, узел сравнения, задающий блок, узел задержки первый триггер, первь1Й элемент И, причем синхровход устройства соединен с синхровходом делителя частоты и с первым входом первого элемента И, второй вход которого соединен с ;инверсным выходом первого триггера, ;вь|ходы кода количества импульсов задающего блока соединены соответствен но с первой группой.входов первого узла сравнения, вторая группа входов которого соединена соответственно с выходами счетчика, управляющий вход которого соединен с управляющим входом задающего блока и с выходом узла задержки, вход которого соединен с выходом первого узла сравнения, вход задающего блока являются информацион ными входами устройства, введены два узла сравнения, элемент НЕ, второй элемент И, второй триггер, выход которого является выходом устрой ;тва и соединен с первым входом STCfporo элемента И, выход которого соединен с установочным входом первого тригге ра, синхровход которого соединен с синхровходом счетчика, с выходом второго узла сравнения, с входом элемента НЕ, выход которого соединен с вторым входом второго эле мента И, выходы кода длительности задающего блока соединены соответственно с первой группой входов второго узла сравнения, вторая группа вхо дов которого соединена соответственно с выходами делителя частоты и с первой группой входов третьего узла сравнения, вторая группа входов кото рого соединена соответственно с выходами кода частоты задающего блока, выход третьего узла сравнения со единен с входом сброса второго три1- гера, установочный вход которого сое динен с выходом первого-элемента И, второй вход которого соединен с управляющим входом делителя частоты. Вход делителя частоты подключен к выходу первого элемента И, первый вход которого соединен с входом устройства, а единичный выход первого триггера подключен к выходу устройст ва И К первому входу второго элемента И, выход первого узла сравнения соединен со счетным входом С второго триггера, и через элемент НЕ - с вторым входом второго элемента И, выход которого подключен к S-входу второго триггера, нулевой выход которого соединен с вторым входом пёрвого элемента И и с установочным входом делителя частоты. Это позволяет в каждой серии импульсов получать заданную длительность импульсов, выдаваемых на выход устройства, при этом длительность импульсов, частота их следования и количество задаются программно. На чертеже .изображена функциональная схема предлагаемого устройства. Устройство содержит делитель 1 частоты, счетчик 2, узлы сравнения, задающий блок 6, узел 7 задержки, триггеры 8 и 9, элементы И 10 и 11, элемент НЕ 12, вход 13 устройства, .выход tit устройства. Устройство работает следующим образом. Перед началом работы устройство приводится в исходное состояние, в результате чего делитель 1 частоты, счетчик 2 периодов, первый и второй триггеры 8 и 9 находятся в нулевом, исходном состоянии. Затем по линиям связи из канала передачи информации по информационным входам 15осуществляется запись в задающий блок 6 информационных слов для получения на выходе 14 устройства заданного количества импульсов с заданной длитель ностью и частотой следования в каждой серии. Задающий блок 6 содержит п приемных регистров для хранения п информационных слов и сдвигающий регистр, который по переднему фронту сигнала, поступающего на управляющий вход задающего блока 6, осуществляет поочередное подключение к выходам 16 -1б, 17-17, задающего блока 6 каждого из п приемных регистров. Таким образом, после записи в задающий блок 6 п информационных слов на выходах 1б-1б, , 18-18. задающего блока 6 появляется первое информационное слово, которое поступает на управляющие входы узлов 3-5 сравнения. Каждое информационное слово содержит на выходах 1б-1б код задания длительности выходного импульса, на выходах код заДания частоты следования выходных импульсов, а на выходах - код задания количества выходных импульсов в данной серии импульсов. ; После этого на вход 13 устройства поступают входные импульсы..По переднему фронту первого входного импульса, поступающего с выхода первого элемента И 10 на S-вход первого три|- ;гера 8, первый триггер 8 переключает :Ся в единичное состояние, формируя на выходе 1 устройства передний фронт положительного импульса, так .как первый элемент И 10 был подготов лен к работе Сигналом, поступающим с инверсного выхода второго триггера 9, который находится в нулевом, исходном состоянии. . Сигнал с прямого выхода первого триггера 8 поступает также на первый вход второго элемента И 11, кото рый подготовлен к работе сигналом, поступающим на его второй вход с выхода первого узла 3 сравнения через элементы НЕ 12. По переднему фронту сигнала, поступающего с выхо,да второго элемента И 11 на С-вход второго триггера 9, второй триггер 9.переключается в единичное состояние запрещая работу первого элемента И lO и снимая сигнал с установочного входа делителя 1 частоты, который удерживает делитель 1 частоты в нулевом, исходном состоянии. Затем делитель 1 частоты начинает заполняться первым и последующими входными импульсами, поступающими по входу 13 устройства. В момент достижения делителем 1 частоты запрограммированного количества импульсов в третьем узле 5 сравнения, который определяет длительность выходного импульса, третий узел 5 сравнения срабатывает и выдает сигнал на R-вхрд первого триггера 8. По переднему фрон ту этого сигнала первый триггер 8 переключается в нулевое состояние, формируя на выходе 1 устройства задний фронт положительного выходного импульса и запрещая {заботу второго элемента И 11 . Делитель 1 частоты продолжает заполняться входными импульсами, поступающими по входу 13 устройства. В момент достижения делителем 1 частоты запрограммированного количества импульсов -В первом узле 3 сравнения, который определяет частоту следования выходных импульсов, первый узел 3 ; 96 06 сравнения срабатывает и выдает сигнал на вход счетчика 2 периодов, где он регистрируется. Сигнал с выхода первого узла 3 сравнения поступает также на счетный вход С второго триггера 9, который по заднему фронту этого сигнала переключается в нулевое состояние, подготавливая к работе первый элемент И 10 и устанавливая в нулевое состояние делитель 1 частоты. Очередной импульс, поступающий на вход 13, аналогично вь(шеописанному циклу устанавливает в единимкэе состояние первый и второй триггеры 8 и 9 формируя на выходе 1k положительный фронт выходного импульса и снимая сигнал с установочного входа делителя 1 частоты. Затем делитель 1 .частоты начинает заново заполняться этим и последующими импульсами, поступающими по входу 13- В момент достижения делителем 1 частоты запрограммированного количества импульсов в третьем узле 5 сравнения, третий узел 5 сравнения срабатывает и аналогично вышеописанному циклу формируется задний фронт положительного выходного импульса. Делитель 1 частоты продолжает заполняться входными импульсами, поступающими по входу 13- В момент достижения делителем 1 частоты запрограммированного количества импульсов в первом узле .сравнения первый узел 3 сравнения срабатывает и по вышеописанному циклу выдается сигнал на вход счетчика 2 периодов и устанавливает в нулевое состояние делитель 1 частоты. Этот процесс продолжается до выдачи определенного количества импульсов, запрограммированных во втором узле сравнения. В момент достижения счетчиком 2 периодов заданного количества импульсов, второй узел сравнения срабатывает и через узел 7 задержки,i который задерживает сигнал на длительность, равную длительности импульса,j поступающего по входу 13, оотцествля}ет установку счетчика 2 периодов в нулевое состояние и подключает следующий приемный регистр к выходам 1б-1б, , 18-18 задающего блока 6 для получения на выходе 1А , устройства второй серии импульсов с заданной длительностью и частотой следования. Далее по вышеописанному циклу осу ществляется выдача второй серии импульсов. Процесс выдачи п заданных серий импульсов продолжается до выдачи п-й серии импульсов. Использование предлагаемого устройства обеспечивает по сравнению с известным следующие преимущества: расширяются функциональные возможности устройства, а именно обеспечивается возможность в каждой серии имзаданную длительпульсов получать выдаваемых устройность импульсов, при этом длительством на выходе, частота их следованость импульсов, ния и количество задаются программно Формула изобретения Устройство формирования серий импульсов, содержащее делитель частоты счетчик, узел сравнения, задающий блок, узел задержки, первый триггер, первый элемент И, причем синхровход устройства соединен с синхровходом делителя частоты и с первым входом первого элемента И, второй вход которого соединен с инверсным выходом первого триггера, выходы кода количе ства импульсов задающего блоки соеди нены соответственно с первой группой входов первого узла сравнения, вторая группа входов которого соединена соответственно с выходами счетчика, управляющий вход которого соединен с управляющим входом задающего блока и с выходом узла задержки, вход которо го соединен с выходом первого узла сравнения, входы задающего блока являются информационными входами устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем формирорания переменной длительности импульса в данной серии,в него введены два узла сравнения,элемент НЕ, второй элемент И, второй триггер, выход которого является выходом устройства и соединен с первым входом второго элемента И, выход которого соединен с установочным входом первого триггера, синхровход которого соединен с синхровходом счетчика, с выходом второго узла сравнения, с входом элемента НЕ, выход которого соединен с вторым входом второго элемента И, выходы кода длительности задающего блока соединены соответственно с первой группой входов второго узла сравнения,, вторая группа входов которого соединена соответственно с выходами делителя частоты и с первой группой входов третьего узла сравнения, вторая группа входов которого соединена соответственно с выходами кода частоты задающего блока, выход третьего узла сравнения соединен с входом сброса второго триггера, установочный вход которого соединен с выходом первого элемента И, второй вход которого соединен с управляющим входом делителя частоты. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № , кл. G Об F l/Qi, 1971. 2.Авторское свидетельство СССР N 798772, кл. Н Об F 1/0, 197В (прототип).

/ -

I UI

/

дх.

/J

5t,/. o/tf

8

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с каналами связи | 1989 |

|

SU1679496A1 |

| Формирователь серий и импульсов | 1978 |

|

SU798772A1 |

| Устройство для формирования входных воздействий в системе программного контроля | 1980 |

|

SU920729A1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

| ИЗМЕРИТЕЛЬ СПЕКТРАЛЬНЫХ ПАРАМЕТРОВ РАДИОСИГНАЛОВ | 2005 |

|

RU2279098C1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Многоканальный формирователь одиночных импульсов | 1985 |

|

SU1243115A1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Устройство для сопряжения абонента с каналом связи | 1986 |

|

SU1388878A1 |

W.

.

f

Авторы

Даты

1982-09-30—Публикация

1981-02-13—Подача