Изобретение относится к области радиотехники и вычислительной техники и предназначено для использования в локаторах дистанционного действия.

Целью изобретения является расширение области применения устройства за счет реализации возможности изменения параметров выходных сигналов.

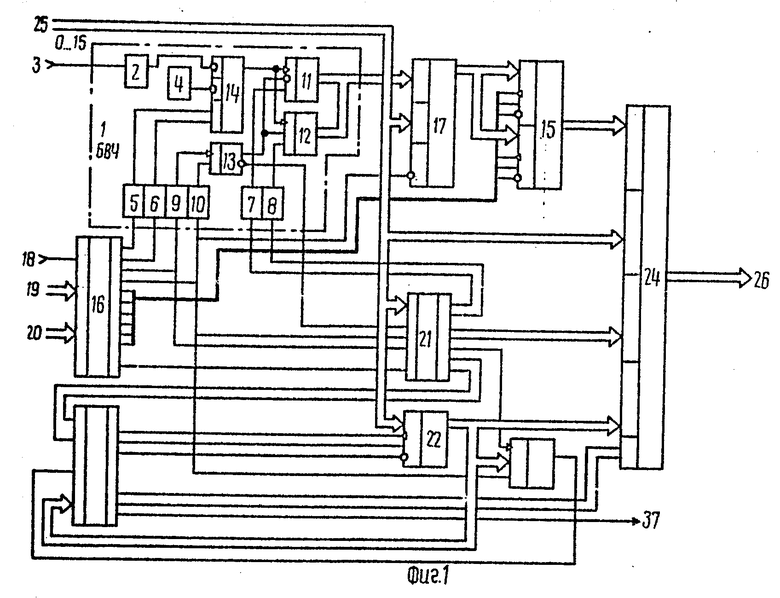

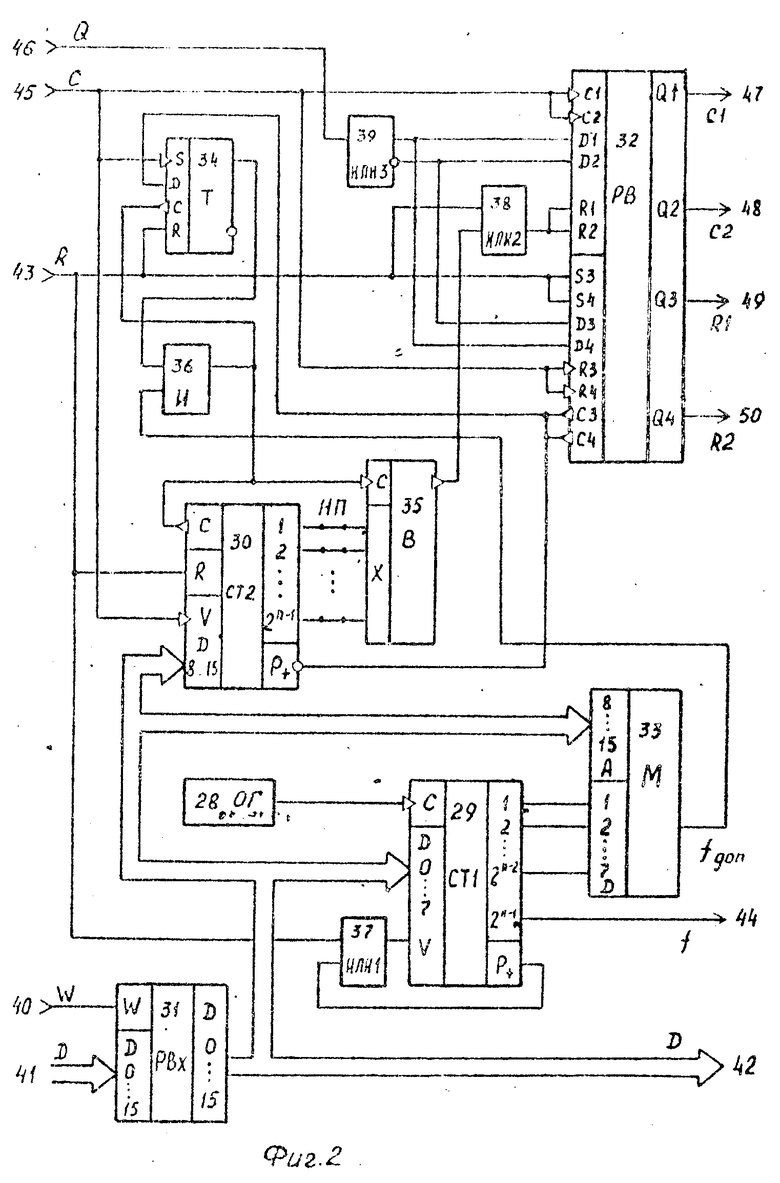

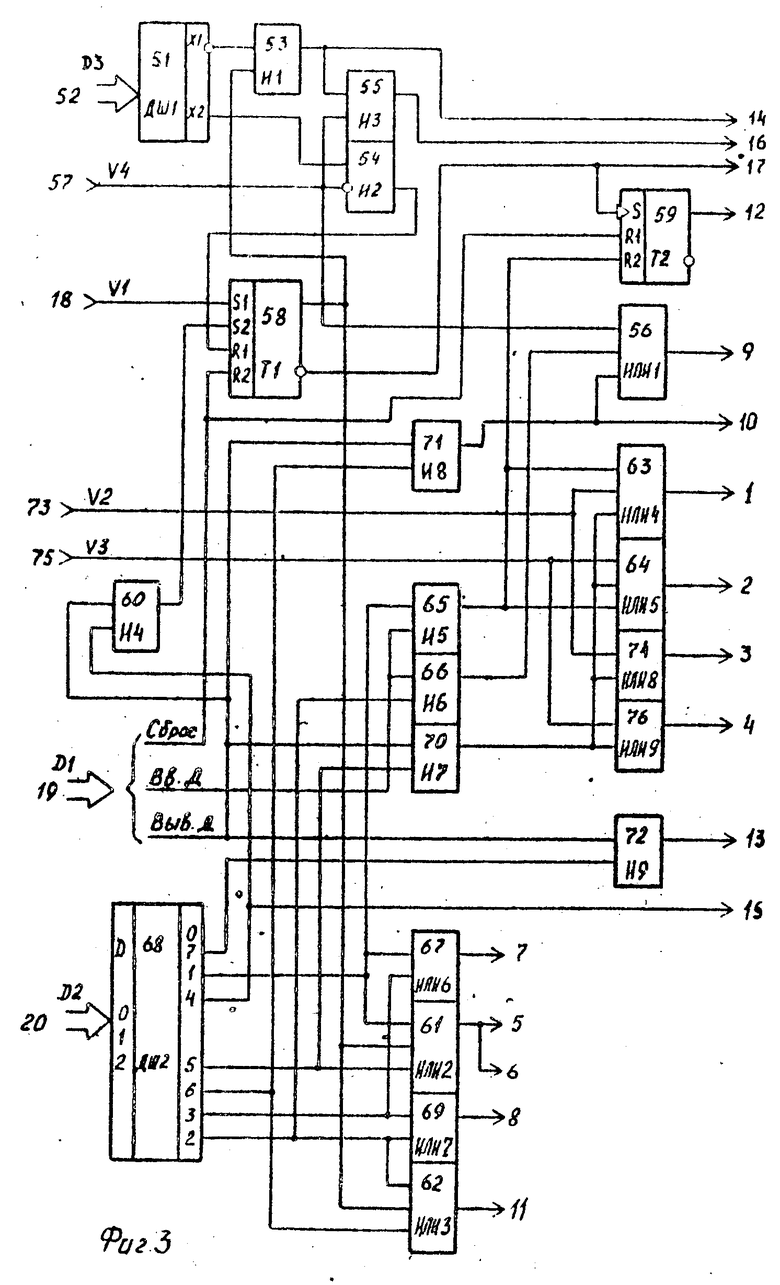

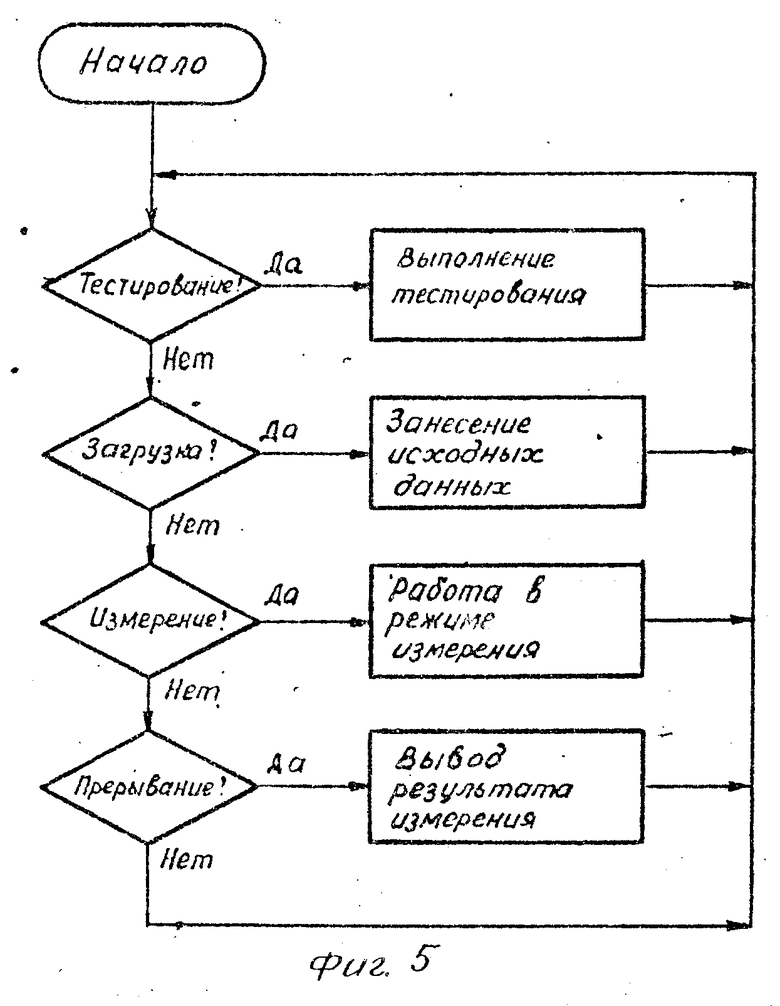

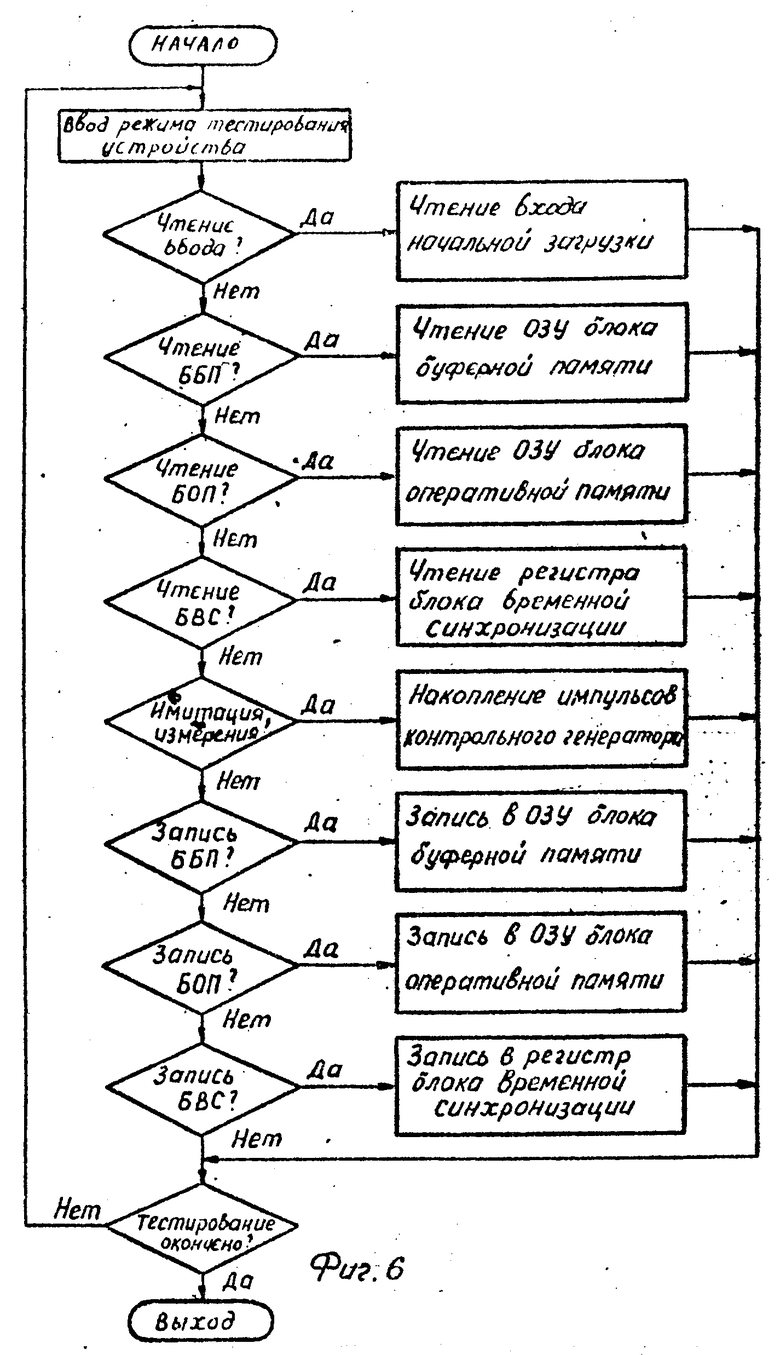

На фиг. 1 представлена функциональная схема устройства буферизации и синхронизации для обработки непрерывного сигнала; на фиг.2 функциональная схема временного синхронизатора; на фиг.3 функциональная схема блока коммутации; на фиг. 4 эпюры напряжений; на фиг.5 общий алгоритм работы устройства; на фиг.6 алгоритм тестирования.

Устройство буферизации и синхронизации для обработки непрерывного сигнала (фиг. 1) содержит блок высокочастотный (БВЧ) 1, включающий в себя формирователь импульсов (Ф) 2. вход которого подключен к информационному входу 3 устройства, контрольный генератор (КГ) 4, группу из шести формирователей импульсов (Ф1,Ф6) 5 10, первый (СТ1) 11 и второй (СТ2) 12 счетчики, триггер (Т) 13 и первый мультиплексор (М1) 14, первый (D1) информационный вход которого подключен к выходу формирователя 2, второй (2) информационный вход первого мультиплексора 14 подключен к выходу контрольного генератора 4, первый (V1) и второй (V2) управляющие входы первого мультиплексора 14 подключены соответственно к выходам третьего 5 и четвертого 6 формирователей импульсов группы, а выход первого мультиплексора 14 подключен к счетным входам (С) первого 1 1 и второго 12 счетчиков, установочные входы (Р) первого 11 и второго 12 счетчиков подключены соответственно к выходам первого 7 и второго 8 формирователей импульсов группы, а парафазные входы управления  и V) этих счетчиков 11,12 подключены к прямому выходу триггера 13, счетный (С) и установочный (Р) входы которого соответственно к выходам пятого 9 и шестого 10 формирователей импульсов группы.

и V) этих счетчиков 11,12 подключены к прямому выходу триггера 13, счетный (С) и установочный (Р) входы которого соответственно к выходам пятого 9 и шестого 10 формирователей импульсов группы.

Кроме того, устройство содержит два узла памяти блока буферной памяти (ББП) 15, блок коммутации (БК) 16 и второй мультиплексор (М2) 17, первый информационный вход (D1) которого соединен с выходами первого 11 и второго 12 счетчиков, а выход второго мультиплексора 17 соединен с информационными входами первого (D1- разряды 0 7) и второго (D2-разряды 8 15) узлов памяти блока буферной памяти 15, синхровходы (С1, С2), входы записи (W1, W2) и установочные входы (Р1, Р2) которых соединены соответственно с первого по шестой выходами блока коммутации 16, первый управляющий вход (V1) которого подключен к входу запуска 18 устройства, первый информационный вход (Д1) блока коммутации 16 подключен к входу признаков состояния 19 устройства, а второй информационный вход (D2) блока коммутации 16 подключен к входу задания режима работы 20 устройства.

Устройство содержит также временной синхронизатор (ВС) 21, блок оперативной памяти (БОП) 23, управляемый делитель частоты (УДЧ) 23 и третий мультиплексор (МЗ) 24, первый информационный вход (D1) которого соединен с выходом блока буферной памяти 15, второй информационный вход (D2) третьего мультиплексора 24, информационный вход (D) управляемого делителя частоты и третий информационный вход (D3) блока коммутации 16 соединены с выходом блока оперативной памяти 22, третий информационный вход (D3) третьего мультиплексора 24, второй информационный вход (D2) второго мультиплексора 17, информационные входы (D) временного синхронизатора 21 и блока оперативной памяти 22 подключены к входу начальной загрузки 25 устройства, четвертый информационный вход (D4) третьего мультиплексора 24 подключена к информационному выходу (D) временного синхронизатора 21, первый (V1) и второй (V2) управляющие входы третьего мультиплексора 24 соединены соответственно с седьмым и восьмым выходами блока коммутации 16, выход третьего мультиплексора 24 является информационным выходом 26 устройства. Переключающий вход (Q) временного синхронизатора 21 подключен к инверсному выходу триггера 13, вход записи (W) временного синхронизатора 21 подключен к тринадцатому выходу блока коммутации 16, первый (R1) второй (R2) установочные выходы временного синхронизатора 21 подключен к входам соответственно первого 7 и второго 8 формирователей импульсов группы, первый (С1) и второй (С2) синхровходы временного синхронизатора 21 подключены соответственно к второму (V2) и третьему (V3) управляющим входам блока коммутации 16, частотный выход (f) временного синхронизатора 21 подключен к синхровходу (С) управляемого делителя частоты 23, выход которого соединен с четвертым управляющим входом (V4) блока коммутации 16, двенадцатый выход блока коммутации 16 является выходом требования прерывания 27 устройства, четырнадцатый и пятнадцатый выходы блока коммутации 16 подключены к входам соответственно третьего 5 и четвертого 6 формирователей импульсов группы. шестнадцатый выход блока коммутации 16 подключен к входу пятого формирователя импульсов 9 группы и синхровходу (С) временного синхронизатора 21, семнадцатый выход блока коммутации 16 подключен к входу шестого формирователя импульсов 10 группы, инверсному управляющему входу (V) второго мультиплексора 17 и установочным входам (R) временного синхронизатора 21 и управляемого делителя частоты 23.

По функциональному назначению формирователь импульсов 2, контрольный генератор 4, счетчики 11, 12, мультиплексоры 14, 17, 24, блок буферной памяти 15, блок оперативной памяти 22 совместно с управляемым делителем частоты 23, блок коммутации 16 и временной синхронизатор 21 с триггером 13 аналогичны следующим узлам прототипа: формирователю, контрольному генератору, счетчикам, мультиплексорам, блоку буферной памяти, блоку задания интервалов, блоку коммутации и блоку временной синхронизации с опорным генератором.

Временной синхронизатор устройства буферизации и синхронизации для обработки непрерывного сигнала (фиг.2) содержит опорный генератор (ОГ) 28, первый счетчик (СТ1) 29 и второй счетчик (СТ2) 30, регистры входной (РВх) и выходной (РВ) 32, мультиплексор (М) 33, триггер (Т) 34, импульсно-потенциальный вентиль (В) 35 с набором перемычек (НП) для механического задания управляющего кода X, элемент И 36 и элементы ИЛИ 37, 38, 39. Вход записи (W) и информационный вход (Д с разрядами 0 15 входного регистра 3 1 являются соответственно входом записи 40 и информационным входом 41 временного синхронизатора, выход входного регистра (разряды 0 15) является информационным выходом 42 блока и подключен к информационному входу (D-разряды 8 15) второго счетчика 30, адресному входу (А-разряды 8 15) мультиплексора 33 и к информационному входу (D-разряды 0 7) первого счетчика 29, управляющий вход (V) которого соединен c выходом первого элемента ИЛИ 37, первый вход которого и входы установки в "ноль" (R) второго счетчика 30 и триггера 34, входы установки в "единицу" третьего (S3) и четвертого (S4) разрядов выходного регистра 32, первый вход второго элемента ИЛИ 38 подключены к установочному входу (R) 43 временного синхронизатора, а второй вход первого элемента ИЛИ подключен к выходу переполнения (P+) первого счетчика 29, выход (2n-1) старшего разряда первого счетчика 29 является частотным выходом (f) 44 временного синхронизатора, выходы (1, 2,2n-2) остальных разрядов первого счетчика 29 подключены к информационному входу (D-разряды 1 7) мультиплексора 33, выход которого соединен с первым входом элемента И 36. Второй вход элемента И 36 соединен с прямым выходом триггера 34, выход элемента И 36 соединен с динамическим прямым входом (С) импульсно-потенциального вентиля 35 и с динамическими инверсными синхровходами (С) второго счетчика 30 и триггера 34, динамический вход установки в "единицу" (S) которого и динамические синхровходы первого (С1) и второго (С2), установочные входы в "ноль" третьего (R3) и четвертого (R4) разрядов выходного регистра 32, динамический управляющий вход (V) второго счетчика 30 соединены с синхровходом (С) 45 временного синхронизатора, а информационный вход (Д) триггера и инверсные динамические синхровходы третьего (СЗ) и четвертого (С4) разрядов выходного регистра 32 соединены с инверсным выходом переполнения  второго счетчика 30, выходы разрядов (1, 2, 2n) второго счетчика 30 через набор перемычек (НП) для механического задания кода управления X подключены к потенциальным входам управления импульсно-потенциального вентиля 35, динамический выход которого соединен с вторым входом второго элемента ИЛИ 38, выход которого подключен к входам установки в "ноль" первого (R1) и второго (R2) разрядов выходного регистра 32. Первый (D1) и четвертый (D4) информационные входы выходного регистра 32 соединены с прямым выходом третьего элемента ИЛИ 39, второй (D2) и третий (D3) информационные входы выходного регистра 32 соединены с инверсным выходом третьего элемента ИЛИ 39, вход которого является переключающим входом (Q) 46 временного синхронизатора. Первый (С1) 47 и второй (С2) 48 синхровходы и первый (R1) 49 и второй (R2) 50 установочные выходы временного синхронизатора являются выходами соответственно с первого по четвертый разрядов выхода выходного регистра 32.

второго счетчика 30, выходы разрядов (1, 2, 2n) второго счетчика 30 через набор перемычек (НП) для механического задания кода управления X подключены к потенциальным входам управления импульсно-потенциального вентиля 35, динамический выход которого соединен с вторым входом второго элемента ИЛИ 38, выход которого подключен к входам установки в "ноль" первого (R1) и второго (R2) разрядов выходного регистра 32. Первый (D1) и четвертый (D4) информационные входы выходного регистра 32 соединены с прямым выходом третьего элемента ИЛИ 39, второй (D2) и третий (D3) информационные входы выходного регистра 32 соединены с инверсным выходом третьего элемента ИЛИ 39, вход которого является переключающим входом (Q) 46 временного синхронизатора. Первый (С1) 47 и второй (С2) 48 синхровходы и первый (R1) 49 и второй (R2) 50 установочные выходы временного синхронизатора являются выходами соответственно с первого по четвертый разрядов выхода выходного регистра 32.

Блок коммутации устройства буферизации и синхронизации для обработки непрерывного сигнала (фиг. 3) содержит первый 'дешифратор (ДШ1) 51, вход которого является третьим информационным входом (D3) 52 блока, первый инверсный выход первого дешифратора 51 (кодовая комбинация X1) подключен к первому входу первого элемента И 53, второй выход первого дешифратора 51 (кодовая комбинация Х2) подключен к прямому входу второго элемента И 54, инверсный вход которого и первые входы третьего элемента И 55 и первого элемента ИЛИ 56 соединены с четвертым управляющим входом (V4) 57 блока, а выход второго элемента И 54 соединен с первым входом установки в "ноль" (R1) первого триггера (Т1) 58, второй вход установки в "ноль" (R2) первого триггера 58 и первый вход установки в "ноль" (R1) второго триггера (Т2) 59 подключены к разряду "Сброс" первого информационного входа (D1) 19 блока, первый вход установки а "единицу" (S1) первого триггера 58 подключен к первому управляющему входу (V1) 18 блока, второй вход установки в "единицу" (2) первого триггера 58 подключен к выходу четвертого элемента И 60, прямой выход первого триггера 58 подключен к первым входам второго 61 и третьего 62 элементов ИЛИ и второму входу первого элемента И 53, а инверсный выход первого триггера 58 подключен к семнадцатому выходу блока и динамическому входу установки в "единицу" (S) второго триггера 59. Второй вход установки в "ноль" (R2) второго триггера 59 и первые входы четвертого 63 и пятого 64 элементов ИЛИ соединены с выходом пятого И 65, первый вход которого и первый вход шестого элемента И 66 подключены к разряду "Ввод данных" первого информационного входа (1) 19 блока, а второй вход пятого элемента И 65 и второй вход второго 61 и первый вход шестого 67 элементов ИЛИ подключены к первому выходу второго дешифратора (ДШ2) 68. Вход второго дешифратора (D-разряды 0 2) является вторым информационным входом (D2) 20 блока, второй выход второго дешифратора 68 подключен к второму входу шестого элемента И 66 и к первому и второму входам седьмого 69 и третьего 62 элементов ИЛИ, третий выход второго дешифратора 68 подключен к вторым входам шестого 67 и седьмого 69 элементов ИЛИ, четвертый выход второго дешифратора 68 подключен к первому входу четвертого элемента И 60 и к пятнадцатому выходу блока, пятый выход второго дешифратора 68 подключен к первому входу седьмого элемента И 70 и к третьему входу второго элемента ИЛИ 61, шестой выход второго дешифратора 68 подключен к первому входу восьмого элемента И 71 и к третьему входу третьего элемента ИЛИ 62, седьмой выход второго дешифратора подключен к первому входу девятого элемента И 72, второй вход которого и вторые входы четвертого 60, седьмого 70 и восьмого 71 элементов И подключены к разряду "Вывод данных" первого информационного входа (D1) 19 блока. Второй управляющий вход (V2) 73 блока соединен с вторым и первым входами четвертого 63 и восьмого 74 элементов ИЛИ, третий управляющий вход (V3) 75 блока соединен с вторым и первым входами пятого 64 и девятого 76 элементов ИЛИ, третий и второй входы которых и третий и второй входы четвертого 63 и восьмого 74 элементов ИЛИ соединены с выходом седьмого элемента И 70. Выход первого элемента И 53 подключен к второму входу третьего элемента И 55 и к четырнадцатому выходу блока, выход третьего элемента И55 подключен к шестнадцатому выходу блока, выход восьмого элемента И 71 подключен к третьему входу первого элемента ИЛИ 56 и к десятому выходу блока, выходы первого 56, второго 61, третьего 62, четвертого 63, пятого 64, шестого 67, седьмого 69, восьмого 74, девятого 76 элементов ИЛИ подключены соответственно к девятому, пятому и шестому, одиннадцатому, первому, второму. седьмому, восьмому, третьему, четвертому выходам блока, выход второго триггера 59 подключен к двенадцатому выходу блока.

Временная диаграмма (фиг.4) представлена следующими эпюрами напряжений: 1 импульс на входе установки в "единицу" триггера 58 (фиг.3); 2 сигнал начала работы на инверсном выходе триггера 58; 3 синхросигнал на шестнадцатом выходе блока коммутации; 4 переключающий сигнал на сорок шестом входе временного синхронизатора (фиг.2); эпюра 5 импульсы на выходе элемента И 36; 6 импульсы на выходе импульсно-потенциального вентиля 35; 7 сигнал переполнения на выходе второго счетчика 30; 8 импульсы на первом синхровыходе (С1) сорок седьмого выхода временного синхронизатора; 9 - импульсы на первом установочном выходе (R 1) сорок девятого выходами временного сихронизатора; 10 импульсы на втором синхровыходе (С2) сорок восьмого выхода временного синхронизатора; 11- импульсы на втором установочном выходе (R2) пятидесятого выхода временного синхронизатора; 12 измерительный интервал для второго счетчика 12 (фиг.1); 13 -измерительный интервал для первого счетчика 11; 14 сигнал на втором выходе первого дешифратора 51 (фиг.3).

Схемные решения устройства буферизации и синхронизации для обработки непрерывного сигнала (фиг.1) представлены следующими режимами (фиг.5).

I. Установка исходного состояния.

Канальным сигналом "Сброс" по первому информационному входу 19 (фиг.3) устанавливаются в исходное состояние триггеры 58 и 59 блока коммутации, а на входе 20 задания режима работы двоичный код имеет вид 000. При этом:

а) "1" сигнал на семнадцатом выходе блока коммутации 16 (фиг.1) удерживает в "нулевом" состоянии триггер 13, временной синхронизатор 21, управляемый делитель частоты 23 и в состоянии "Включено" второй информационный вход информационный выход второго мультиплексора 17;

б) "0" сигналы на пятом, шестом, одиннадцатом выходах блока коммутации 16 удерживают в "нулевом" состоянии адресные счетчики блоков буферной памяти 15 и оперативной памяти 22;

в) "0" сигнал на седьмом и восьмом выходах блока коммутации 16 удерживают в состоянии "Включено" третий информационный вход информационный выход третьего мультиплексора 24.

II. Режим тестирования (фиг.6).

1. Чтение входа начальной загрузки 25 (фиг.1).

Выполнение подпрограммы осуществляется в исходном состоянии устройства, когда на входе 20 задания его режима работы присутствует код 000, при этом вход начальной загрузки 25 посредством мультиплексора 24 подключен к информационному выходу 26.

2. Чтение ОЗУ блока буферной памяти 15.

Выполнение подпрограммы осуществляется установкой двоичного кода 001 по входу 20 задания режима работы (фиг.3). Сигнал "единица" на первом выходе второго дешифратора 68 открывает пятый элемент И 65 и проходит второй 61 и шестой 67 элементы ИЛИ. Единичный сигнал на выходе шестого элемента ИЛИ 67 (седьмой выход блока коммутации) по управляющему входу (V1) третьего мультиплексора 24 (фиг. 1) создает канал прохождения информации: выход ОЗУ блока буферной памяти 15 третий мультиплексор 24 -выход 26 устройства. Единичный сигнал (фиг. 3) на выходе второго элемента ИЛИ 61 (пятый и шестой выходы блока коммутации) дает разрешение на работу адресных счетчиков двух узлов памяти блока буферной памяти (фиг.1). Открытый пятый элемент И 65 (фиг.3) пропускает импульсы "Ввод данных", формируемых ЭВМ. Эти импульсы устанавливают в "ноль" второй триггер 59, если было "Требование прерывания", проходят четвертый 63 и пятый 64 элементы ИЛИ (первый и второй выходы блока коммутации) и поступают на сигнальные входы адресных счетчиков двух узлов памяти блока буферной памяти 15 (фиг.1). Перебором состояний этих счетчиков на информационном выходе этого блока выставляются коды, находящиеся в ячейках памяти.

Снятием кода 001 снимается единичный сигнал на первом выходе второго дешифратора 68 (фиг.3) и устанавливается исходное состояние.

3. Запись в ОЗУ блока буферной памяти 15 (фиг.1).

В исходном состоянии вход начальной загрузки 25 вторым мультиплексором 17 подключен к входу блока буферной памяти 15.

Выполнение подпограммы осуществляется установкой двоичного кода 101 по входу 20 задания режима работы (фиг.3). "Сигнал единица" на пятом выходе второго дешифратора 68 открывает седьмой элемент И 70 и проходит второй элемент ИЛИ 61. Единичный сигнал на выходе второго элемента ИЛИ 61 (пятый и шестой выходы блока коммутации) дает разрешение на работу адресных счетчиков двух узлов памяти блока буферной памяти 15 (фиг.1). Открытый седьмой элемент И 70 (фиг.3) пропускает импульсы "Вывод данных", формируемых ЭВМ. Эти импульсы проходят четвертый 63, пятый 64, восьмой 74, девятый 76 элементы ИЛИ (первый, четвертый выходы блока коммутации) и поступают на сигнальные входы (С1, С2), адресных счетчиков и входы записи (W1, W2) двух узлов памяти блока буферной памяти 15 (фиг.1). Перебором состояний этих счетчиков в ячейки памяти записывается информация, поступающая с входа начальной загрузки 25.

Снятием кода 101 снимается единичный сигнал на пятом выходе второго дешифратора 68 (фиг.3) и устанавливается исходное состояние.

4. Чтение ОЗУ блока оперативной памяти 22 (фиг.1).

Выполнение подпрограммы осуществляется установкой двоичного кода 010 по входу 20 задания режима работы (фиг.3). Сигнал "единица" на втором выходе второго дешифратора 68 открывает шестой элемент И 66 и проходит третий 62 и седьмой элементы ИЛИ. Единичный сигнал на выходе седьмого элемента ИЛИ 69 (восьмой выход блока коммутации) по управляющему входу (V2) третьего мультиплексора 24 (фиг.1) создает канал прохождения информации: выход ОЗУ блока оперативной памяти 22 третий мультиплексор 24 информационный выход 26 устройства. Единичный сигнал на выходе третьего элемента ИЛИ 62 (одиннадцатый выход блока коммутации) дает разрешение на работу адресного счетчика блока оперативной памяти 22 (фиг.1). Открытый шестой элемент И 66 (фиг.3) пропускает импульсы "Ввод данных", формируемых ЭВМ. Эти импульсы проходят первый элемент ИЛИ 56 (девятый выход блока коммутации) и поступают на сигнальный вход адресного счетчика блока оперативной памяти 22 (фиг.1). Подбором состояний этого счетчика на информационном выходе этого блока выставляются коды, находящиеся в ячейках памяти.

Снятием кода 010 снимается единичный сигнал на втором выходе второго дешифратора 68 (фиг.3) и устанавливается исходное состояние.

5. Запись в ОЗУ блока оперативной памяти 22 (фиг.1).

Выполнение подпрограммы осуществляется установкой двоичного кода 110 по входу 20 задания режима работы (фиг.3). Сигнал "единица" на шестом выходе второго дешифратора 68 открывает восьмой элемент И 71 и проходит третий элемент ИЛИ 62. Единичный сигнал на выходе третьего элемента ИЛИ 62 (одиннадцатый выход блока коммутации) дает разрешение на работу адресного счетчика блока оперативной памяти 22 (фиг.1). Открытый восьмой элемент И 71 (фиг. 3) пропускает импульсы "Вывод данных" формируемых ЭВМ. Эти импульсы (десятый выход блока коммутации) проходят первый элемент ИЛИ 56 (девятый выход блока коммутации) и поступают на вход записи (W) и сигнальный вход (С) адресного счетчика блока оперативной памяти 22 (фиг.1). Перебором состояний этого счетчика в ячейки памяти записывается информация, поступающая с входа начальной загрузки 25.

Снятием кода 110 снимается единичный сигнал на шестом выходе второго дешифратора 68 (фиг.3) и устанавливается исходное состояние.

6. Чтение входного регистра временного синхронизатора (фиг.1).

Выполнение подпрограммы осуществляется установкой двоичного кода О11 по входу 20 задания режима работы (фиг.3). Сигнал "единица" на третьем выходе второго дешифратора 68 проходит шестой 67 и седьмой 69 элементы ИЛИ. Единичный сигнал на выходах шестого 67 и седьмого 69 элементов ИЛИ (седьмой и восьмой выходы блока коммутации) по управляющим входам (V1 и V2) третьего мультиплексора 24 (фиг.1) создает канал прохождения информации: входной регистр временного синхронизатора 21 третий мультиплексор 24 - информационный выход 26 устройства.

Снятием кода 011 снимается единичный сигнал на третьем выходе второго дешифратора 68 (фиг.3) и восстанавливается исходный канал прохождения информации.

7. Запись во входной регистр временного синхронизатора 21 (фиг.1).

Выполнение подпрограммы осуществляется установкой двоичного кода 111 по входу 20 задания режима работы (фиг.3). Сигнал "единица" на седьмом выходе второго дешифратора 68 открывает девятый элемент И 72. Открытый девятый элемент И 72 пропускает импульс "Вывод данных", формируемый ЭВМ. Этот импульс (тринадцатый выход блока коммутации) поступает на вход записи (W) временного синхронизатора 21 (фиг.1).

Снятием кода 111 снимается единичный сигнал на седьмом выходе второго дешифратора 68 (фиг.3) и устанавливается исходное состояние.

8. Имитация измерения.

Выполнение подпрограммы осуществляется установкой двоичного кода 100 по входу 20 задания режима работы (фиг.3). Сигнал "единица" на четвертом выходе второго дешифратора 68 открывает четвертый элемент И 60 (пятнадцатый выход блока) и по управляющему входу (2) первого мультиплексора 14 (фиг. 1) создает канал прохождения импульсов:контрольный генератор 4 первый мультиплексор 14 счетный вход счетчиков 11, 12. Открытый четвертый элемент И 60 пропускает импульс "Вывод данных", формируемый ЭВМ, который устанавливает в "единицу" первый триггер 58 (фиг. 3) "Начала работы". Таким образом, режим имитации измерения заключается в том, что на вход счетчиков 11, 12 (фиг.1) подаются импульсы от контрольного генератора 4, а запуск режима осуществляется от ЭВМ.

Дальнейшее описание аналогично режиму измерения.

III. Подготовительный режим.

1. Загрузка ОЗУ блока оперативной памяти 22 (фиг.1). В этом режиме в соответствии с п.11.5 необходимо загрузить исходные данные по сканированию пространства. Эти данные представляют собой последовательный ряд кодов, где X1 первая кодовая комбинация, задающая режим пропуска высотного интервала; Х2 вторая кодовая комбинация, устанавливающая конец измерения; Н код, устанавливающий значение высотного интервала.

Очевидно, что кодовое значение высотного интервала Н не должно быть равно указанным кодовым комбинациям X1, Х2 (Н ≠ X1, Х2) и изменяется в пределах: (1)

(1)

где n 8, а 2n 16-разрядный код входа начальной загрузки 25 устройства.

Разрешающая способность устройства по высоте Н есть минимальное кодовое значение высотного интервала Н (Н 1) которое соответствует временному интервалу следующим образом: (2)

(2)

где С скорость распространения света.

2. Загрузка временного синхронизатора 21.

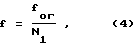

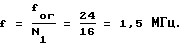

Временной синхронизатор имеет внутренний опорный генератор с фиксированным значением частоты for, делением которой формируется выходная частота f: (3)

(3)

Для формирования выходных импульсов с регулируемой длительностью в блоке предусмотрена механическая установка кода.

Программируемым параметром блока является запись кода (режим 11.7) во входной 16-разрядный регистр. Разряды О 7 и 8 1 5 этого кода образуют две управляющие команды N1 и N2 соответственно (или дополнительный код  ).

).

Временной синхронизатор характеризуется следующими программно изменяемыми выходными параметрами: f, tс, tR и tпп,,

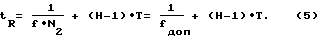

где tc длительность выходных сихроимпульсов С1, С2; tR - длительность выходных установочных сигналов R1, R2; tnn длительность переходных процессов или интервал времени между сигналами tc и tR, и которые связаны с вышеуказанными входными параметрами for, X, N1 и N2 следующими зависимостями:

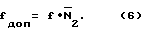

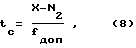

Из формулы (5) вытекает, что во временном синхронизаторе формируется дополнительная частота fдоп в соответствии с выражением:

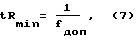

При значении высотного интервала Н 1 формула (5) приобретает вид:

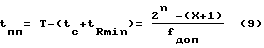

где tRmin минимальная длительность установочного сигнала tR.

Из формулы (9) вытекает, что при значении X + 1 2n fnn 0. Этот крайний случай реализован в прототипе.

Из формулы (9) вытекает, что при значении X + 1 2n fnn 0. Этот крайний случай реализован в прототипе.

Варьируя значениями tc. tR. tnn в соответствии с граничной частотой блоков устройства, можно устанавливать требуемую разрешающую способность по входу, а программируя соответствующим образом выходную частоту f, можно изменять разрешающую способность по высоте, т.е. осуществлять программное сканирование объекта исследования.

IV. Режим измерения.

В момент излучения локатора на информационном входе 3 устройства буферизации и синхронизации для обработки непрерывного сигнала (фиг.1) устанавливается импульсный поток, а на запускающем входе 18 появляется импульс запуска (фиг.4. эпюра 1). Этим импульсом устанавливается в "единицу" триггер "Начала работы" 58 (фиг.3). "Единичный" сигнал этого триггера открывает первый элемент И 53 и проходит второй 61 и третий 62 элементы ИЛИ. При отсутствии управляющего кода X1 ("пропуск") "единица" на выходе первого элемента И 53, воздействуя по управляющему входу (V1) на первый мультиплексор 14 (фиг. 1), подключает входную цепь 3 к счетным входам счетчиков 11, 12, а"единица" на выходах "5", "6", "11", блок управления 16 дает разрешение на функционирование адресных счетчиков блока буферной 15 и оперативной 22 памяти. "Нулевой" сигнал (фиг.4, эпюра 2) на инверсном выходе этого триггера 58 (фиг. 3) дает разрешение на работу временного синхронизатора 21 (фиг.1), управляемого делителя частоты 23, триггера 17 и производит по входу управления  переключение мультиплексора 17, подключая к блоку буферной памяти 15 выходы счетчиков 11, 12.

переключение мультиплексора 17, подключая к блоку буферной памяти 15 выходы счетчиков 11, 12.

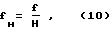

На частотном выходе временного синхронизатора 21 устанавливается частота f. Импульсы этой частоты при значениях кода блока оперативной памяти Н (H≠0;X1;X2) проходят управляемый делитель частоты 23 в соответствии с выражением:  где fн частота на выходе управляемого делителя частоты 23. Частота fн, воздействуя на четвертый управляющий вход (V4) блока коммутации 16, затем снимается с его шестнадцатого и девятого выходов (фиг. 4, эпюра 3), производя переключение каналов измерения с помощью триггера 13 (фиг. 4, эпюра 4) и изменяя по заднему фронту состояние адресного счетчика блока оперативной памяти 22. Каждое переключение триггера 13 сопровождается формированием пары сигналов С1. RI или С2. R2 (фиг.4, эпюры 8, 9, 10, 11 соответственно) во временном синхронизаторе 21. Выходные синхросигналы С1, С2 временного синхронизатора 21 коммутируются блоком коммутации 16, определяя режим записи в блок буферной памяти 15 следующим образом.

где fн частота на выходе управляемого делителя частоты 23. Частота fн, воздействуя на четвертый управляющий вход (V4) блока коммутации 16, затем снимается с его шестнадцатого и девятого выходов (фиг. 4, эпюра 3), производя переключение каналов измерения с помощью триггера 13 (фиг. 4, эпюра 4) и изменяя по заднему фронту состояние адресного счетчика блока оперативной памяти 22. Каждое переключение триггера 13 сопровождается формированием пары сигналов С1. RI или С2. R2 (фиг.4, эпюры 8, 9, 10, 11 соответственно) во временном синхронизаторе 21. Выходные синхросигналы С1, С2 временного синхронизатора 21 коммутируются блоком коммутации 16, определяя режим записи в блок буферной памяти 15 следующим образом.

На временном отрезке t1 (фиг. 4, эпюра 12) oтраженный сигнал поступает во второй счетчик 12, cигналом С1 (фиг.4, эпюра 8I, третий выход блока коммутации 16) информация первого счетчика 11 перезаписывается в первый узел памяти блока буферной памяти 15: задним фронтом этого сигнала (первый выход блока коммутации 16) адресный счетчик первого узла памяти буферной памяти 15 меняет свое состояние; сигналом R1 (фиг.4, эпюра 9) с выхода временного синхронизатора 21 очищается первый счетчик 11.

На временном отрезке t2 (фиг.4, эпюра 13), наоборот, отраженный сигнал поступает в первый счетчик 11 сигналом С2 (фиг.4, эпюра 10 четвертый выход блока коммутации 16) информация второго счетчика 12 перезаписывается во второй узел памяти блока буферной памяти 15 задним фронтом этого сигнала (второй выход блока коммутации 16) адресный счетчик второго узла памяти блока буферной памяти 15 меняет свое состояние сигналом R2 (фиг.4, эпюра 11) с выхода временного синхронизатора 21 очищается второй счетчик 12.

По команде "Пропуск" (код X1 на выходе блока оперативной памяти 22) "нулевой" сигнал на выходе X1 первого дешифратора 51 (фиг.3) закрывает первый элемент И 53, в результате блокируется третий элемент И 55 (этим запрещается прохождение импульсов fн с выхода управляемого делителя частоты 23 на вход триггера 13 и временного синхронизатора 21) и первый мультиплексор 14 (фиг.1). Длительность "пропуска" определяется кодом X1 и фиксированным коэффициентом деления управляемого делителя частоты 23, который формируется самим делителем при входном коде Х1.

По команде "Конец" (код Х2 на выходе блока оперативной памяти 22) "единичный" сигнал на выходе Х2 второго дешифратора 51 (фиг.4, эпюра 4) открывает второй элемент И 54 (фиг. 3). По окончании входного импульса fн (инверсный вход второго элемента И 54) триггер "Начала работы" 58 устанавливается а "ноль", в результате все блоки устройства принимают исходное состояние. По перепаду этого триггера 58 устанавливается в "единицу" второй триггера 59, выставляя для ЭВМ сигнал "Требования прерывания". ЭВМ по подпрограмме, описание режимом 11.2, считывает накопленную в блоке буферной памяти 15 информацию при этом второй триггер 59 устанавливается в "ноль", снимая сигнал" Требование прерывания".

Временной синхронизатор (фиг.2) характеризуется следующими особенностями узлов.

Входной 16-разрядный регистр 31 хранит 2n-разрядный двоичный код N, разряды 0 7 и 8 15 которого образуют управляющие команды N1 и N2. Первый счетчик 29 n-разрядный управляемый делитель частоты с кодом пред-установки N1. в котором выход старшего разряда используется для формирования выходной частоты f Временного синхронизатора, а один из выходов оставшихся разрядов для формирования дополнительной частоты fдоп. Из сказанного следует, что код N1 должен удовлетворять условию:

0≅ N1≅ 2n-22. (11).

Дополнительная частота устанавливается путем дешифрации на адресном входе мультиплексора 33 кода N2, который в соответствии с вышесказанным выбирает один из младших разрядов первого счетчика 29 и должен соответствовать выражению:

N2= 2m. (12)

где m цифра из ряда: 0≅m≅n-2. (13)

Код N2 является также кодом предустановки n-разрядного счетчика 30. Выходы каждого из разрядов счетчика 30 с помощью набора перемычек НП подключается в кодовой комбинации X к управляющим входам импульсно-потенциального вентиля 35. Значение кодовой комбинации должно удовлетворять условию: N2<X<2n (14)

Поскольку технические характеристики блоков устройства на этапе проектирования являются исходными данными то в соответствии с этими данными выбирается и фиксируется с помощью перемычек значение X.

При наличии "единичных" сигналов на входах управления импульсно-потенциальный вентиль 35 осуществляет параллельный nepeнос импульсов с входа (C) на выход.

Выходной регистр 32 представляет собой четыре D-триггера с независимыми входами занесением информации и установки нуля и единицы.

Рассмотрим работу временного синхронизатора (фиг.2) на примере фиксированных значений управляющих команд Х 11111110 N1 1111000  N2 11111100

N2 11111100  и значении частоты опорного генератора for 24 МГц.

и значении частоты опорного генератора for 24 МГц.

Исходное состояние временного синхронизатора удерживается установочным сигналом R по входу 43 и характеризуется следующим образом: триггер 34 - "ноль"; второй счетчик 30 "ноль"; первый счетчик 29-код N1 (11110000); выходной регистр 32-код 0,4.0,1(1100).

Снятие сигнала R (фиг.4, эпюра 2) связано с началом работы временного синхронизатора, при этом первый счетчик 29 дозаполняется от частоты опорного генератора  импульсами и по переполнению снова устанавливается в код N1, циклически формируя выходную частоту f 1,5 МГц. Дешифрированием кода на выходе мультиплексора 33 устанавливается дополнительная частота fдоп 6,0 МГц. Переключающий вход (Q) 46 (фиг.4, эпюра 4) имеет единичное состояние, временной синхронизатор находится в ожидании поступления синхросигнала "С"(фиг.4, эпюра 3) по синхровходу 45.

импульсами и по переполнению снова устанавливается в код N1, циклически формируя выходную частоту f 1,5 МГц. Дешифрированием кода на выходе мультиплексора 33 устанавливается дополнительная частота fдоп 6,0 МГц. Переключающий вход (Q) 46 (фиг.4, эпюра 4) имеет единичное состояние, временной синхронизатор находится в ожидании поступления синхросигнала "С"(фиг.4, эпюра 3) по синхровходу 45.

Поступление синхросигнала "С" приводит к переводу переключающего сигнала (Q) в нулевое состояние и связано с началом измерения.

Поскольку переключающий сигнал (Q) задержан на элементе И 38 относительно синхросигнала С, то по С-сигналу произойдет запись "единицы" в первый разряд и установка "нулей" в третьем и четвертом разрядах регистра 32 (фиг.4, эпюры 8,9,11 соответственно). Кроме этого, устанавливается в "единицу" триггер 34, а второй счетчик З0 в код N2 (1111 1100).

По установке в "единицу" триггера 34 открывается элемент И 36, который пропускает на вход второго счетчика 30 частотный сигнал fдоп (фиг.4, эпюра 5) до пояснения его импульса переполнения P+ (фиг.4, эпюра 7). Импульс переполнения второго счетчика 30 подготавливает информационный вход триггера 34 и следующий последний сигнал установит этот триггер 34 в "ноль" и закроет элемент И36. В результате закончится временной интервал Т и второй счетчик 30 будет находиться в исходном состоянии. На этом временном отрезке по достижении до втором счетчике 30 кода Х=1111 1110 откроется вентиль 35 и пропустит два оставшихся импульса, на выход (фиг.4, эпюра 6). Передним фронтом импульса на выходе вентиля 35 устанавливается в "ноль" первый разряд выходного регистра 32, тем самым заканчивается выходной синхросигнал С1 (фиг.4, эпюра 8). С появлением импульса переполнения второго счетчика 30 устанавливается в "единицу" третий разряд выходного регистра 32, в результате "единицей" станет выходной установочный сигнал R1(фиг. 4, эпюра 9) который будет удерживаться до прихода следующего синхросигнала "С" по входу 45 временного синхронизатора.

Работа временного сихронизатора с приходом следующего синхросигнала "С" по входу 45 повторится с той лишь разницей, что переключающий сигнал (Q) по входу 46 (фиг.4, эпюра 4) перейдет в "единичное" состояние, в результате будет сформирована пара выходных импульсов С2 и R2 (фиг.4, эпюры 10 и 11 соответственно). В последующем весь процесс работы временного синхронизатора повторяется.

Пример программирования параметров выходных сигналов временного синхронизатора.

Пусть for= 24 МГц, X1111 1110, N1=11110000 ( 10000), N21111 1100 (

10000), N21111 1100 ( 100). Тогда, с учетом приведенных формул:

100). Тогда, с учетом приведенных формул:  T = 1/f≈ 666 нс.

T = 1/f≈ 666 нс.

tпп= T-(tс+tRmin)≈ 166 нс.

tпп= T-(tс+tRmin)≈ 166 нс.

С такими характеристиками создало устройство буферации и синхронизации для обработки непрерывного сигнала в котором узел содержащий опорный генератор 28, первый счетчик 29, первый элемент ИЛИ З7 (фиг.2), имеет граничную частоту, работы 30 МГц (серия 130), блок частоты 1 (фиг.1) 100 МГц (серия 100), блок буферной памяти 15 1,5 МГц (серия 505РУ6) и остальные узлы и блоки с граничной частотой 10 МГц (серия1ЗЗ и 541РУ2).

Преимущество предлагаемого устройства буферизации и синхронизации для обработки непрерывного сигнала состоит в расширении области применения за счет реализации возможности изменения пара метров выходных сигналов.

Устройство обладает дополнительными функциями: возможность сканирования пространства с применением сменных блоков, имеющих равную граничную частоту;

программирование разрешающей способности по высоте.

Улучшены основные технические характеристики: разрешающая способность по информационному входу: разрешающая способность по высоте: энергопотребление и помехозащищенность.

Расширить функциональные возможности устройства при одновременном повышении его технических характеристик стало возможно благодаря программированию параметров управляющих сигналов с учетом частотных характеристик входящих в него блоков.

Экономический эффект при использовании устройства буферизации и синхронизации для обработки непрерывных сигналов состоит в повышении качества проводимых измерений и в расширении области применения.

Перечисленные преимущества являются определяющими при создании устройств буферизации для обработки непрерывного сигнала, которые эксплуатируются а экстремальных условиях и труднодоступных местах. ЫЫЫ2 ЫЫЫ4 ЫЫЫ6

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| Параллельный логический мультиконтроллер | 2016 |

|

RU2634199C1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

Изобретение относится к области радиотехники и вычислительной техники и предназначено для использования в локаторах дистанционного действия. Целью изобретения является расширение области применения за счет реализации возможности изменения параметров выходных сигналов. Устройство содержит входной формирователь импульсов, контрольный генератор, триггер, первый мультиплексор, первый и второй измерительные счетчики, образующие блок высокой частоты, в который введена группа из шести формирователей импульсов, второй и третий мультиплексоры, временной синхронизатор, управляемый делитель частоты, блок коммутации, два узла памяти блока буферной памяти и блок оперативной памяти. Информационный вход и запускающий вход подключаются к приемнику локатора. Информационные входы начальной загрузки, признаков состояния, задания режима работ и информационный выход посредством интерфейса параллельного обмена подключаются к ЭВМ. Устройство программно-управляемое. В режиме тестирования осуществляется проверка работоспособности его узлов и блоков. В подготовительном режиме блоки и узлы памяти загружаются программируемыми параметрами сканирования пространства и параметрами выходных сигналов синхронизации. В режиме имитации работы осуществляется проверка работоспособности устройства на граничной частоте. Режим измерения начинается при наличии сигнала "Зонд" на запускающем входе и импульсного потока на информационном входе и заканчивается появлением сигнала "требование прерывания". Изобретение может быть использовано в метеорологических лидарах дистанционного исследования параметров атмосферы в интересах метеорологического прогнозирования, экологии и пр. 2 з.п. ф-лы, 6 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР N 1248439, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N 1635783, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1996-06-27—Публикация

1990-06-07—Подача