Изобретение относится к вычислительной технике и может быть использовано для -обнаружения единичных ошибок при передаче цифровой ин формации в вычислительных маишнах.

Известно устройство для контроля на четность передачи цифровой информации от одного устройства в вычислительной машине к другому, содержащее элементы И и ИЛИ и обеспечивающее контроль передачи цифровой информации l}.

Устройство не обладает самоконтролем, что является его основным недостатком.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля на четность цифровой информации, содержащее регистр и элементы И, ИЛИ и обеспечивающее формирование суммы по всех единиц информационной части слова и сравнение результата с контрольным разрядом слова с выработкой сигнала о сбое числа 2.

Недостатком данного устройства является отсутствие самоконтроля, что при больЫом объеме пересылок цифровой информации в вычислительных машинах, а следовательно, и большом

.количестве схем сверток, существенно снижает его надежность.

Цель изобретения - повышение надежности вычислительного устройства путем повышения достоверности работы схем контроля.

Поставленная цель достигается тем, что в устройство для контроля двоичного кода на четность, содержа10щее приемный регистр, первый, второй ,и третий элементы И, первый, второй и третий элементы ИЛИ, первый, второй и третий элементы И с одним инверсным входом, причем информацион15ные входы устройства соединены с входом приемного регистра, установочный и управлякхций входы устройства соединены соответственно с входом начальной установки и управляющим вхо

20 дрм приемного регистра, каждый выход которого соединен с первыми входами соответствующего элемента И и элемента ИЛИ, выходы каждого элемента И и элемента ИЛИ соединены соответст25венно с инверсным и прямым входами соответствующего элемента И с одним инверсным входом, выходы первого и второго элементов И с одним инверсным входом соединены с вторыми входами

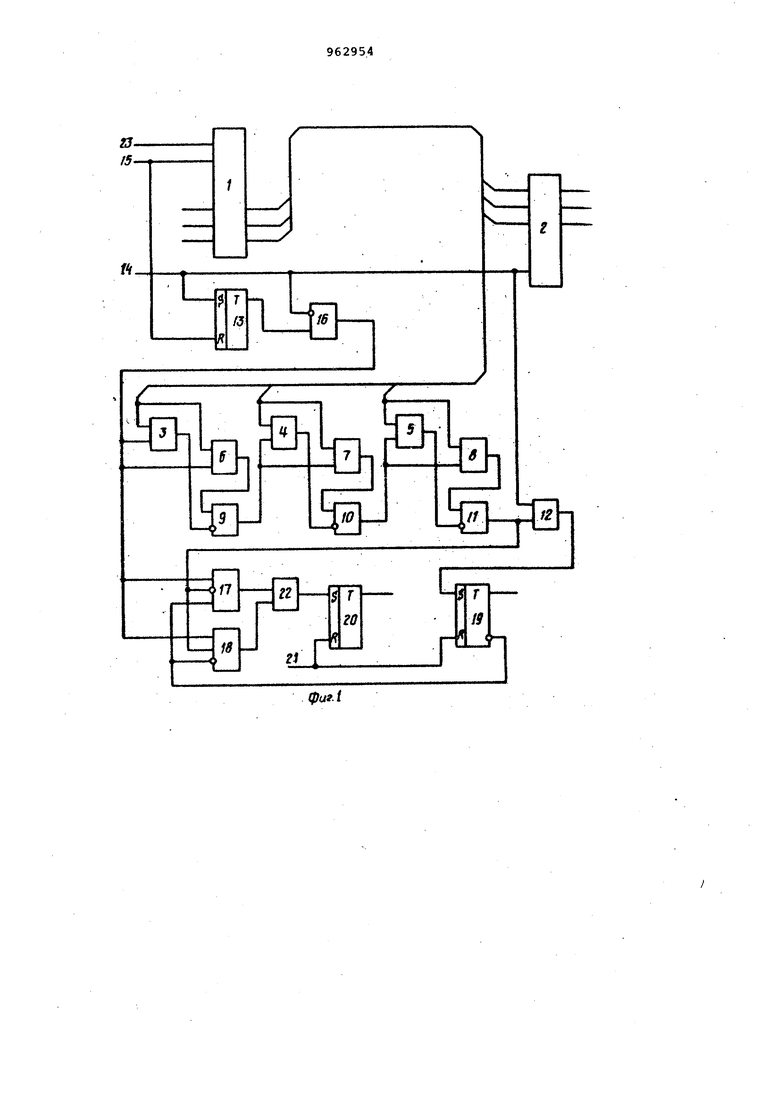

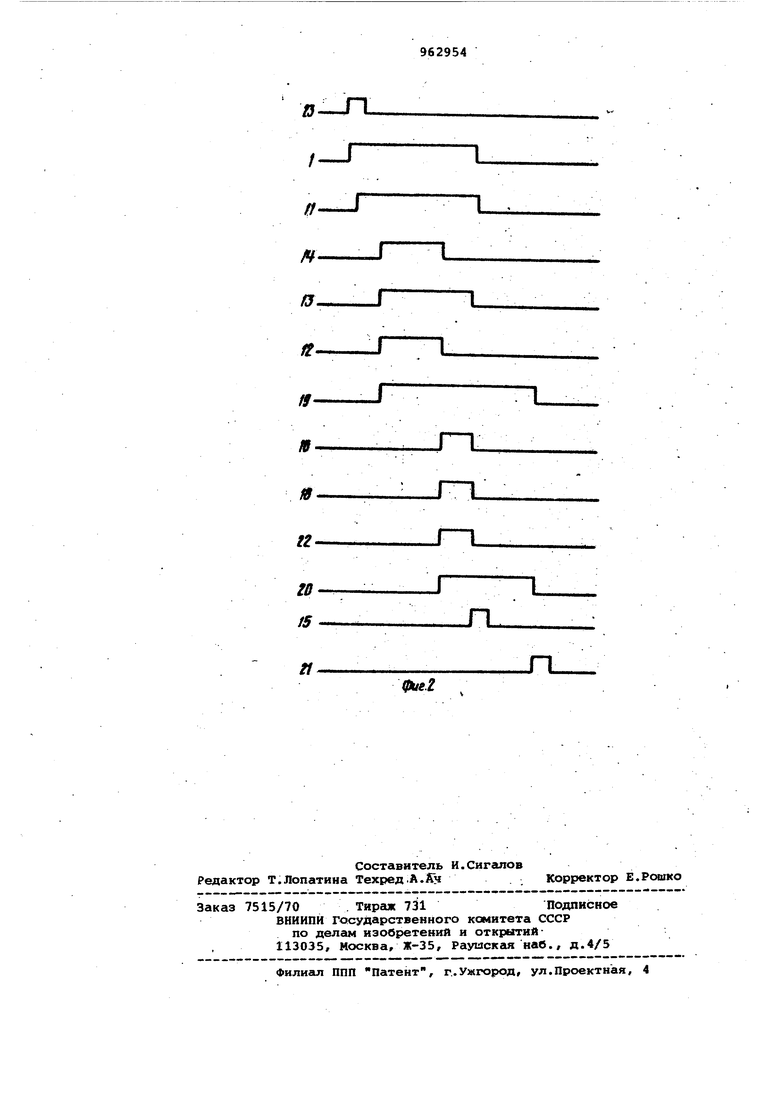

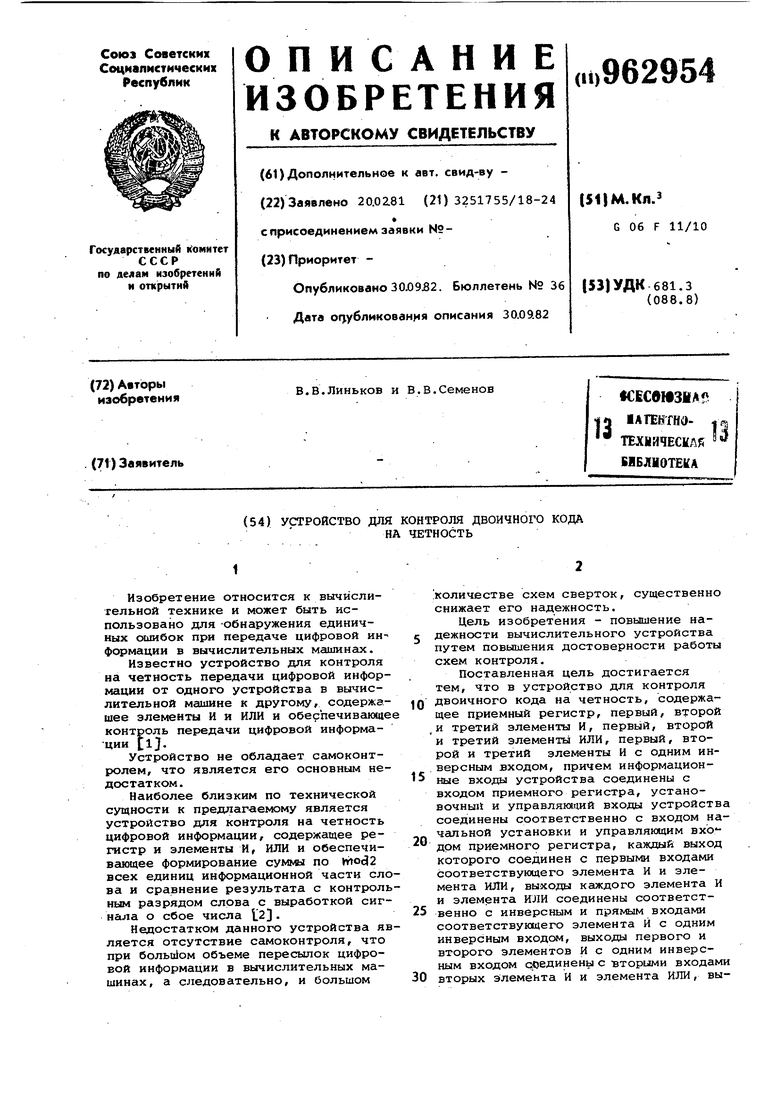

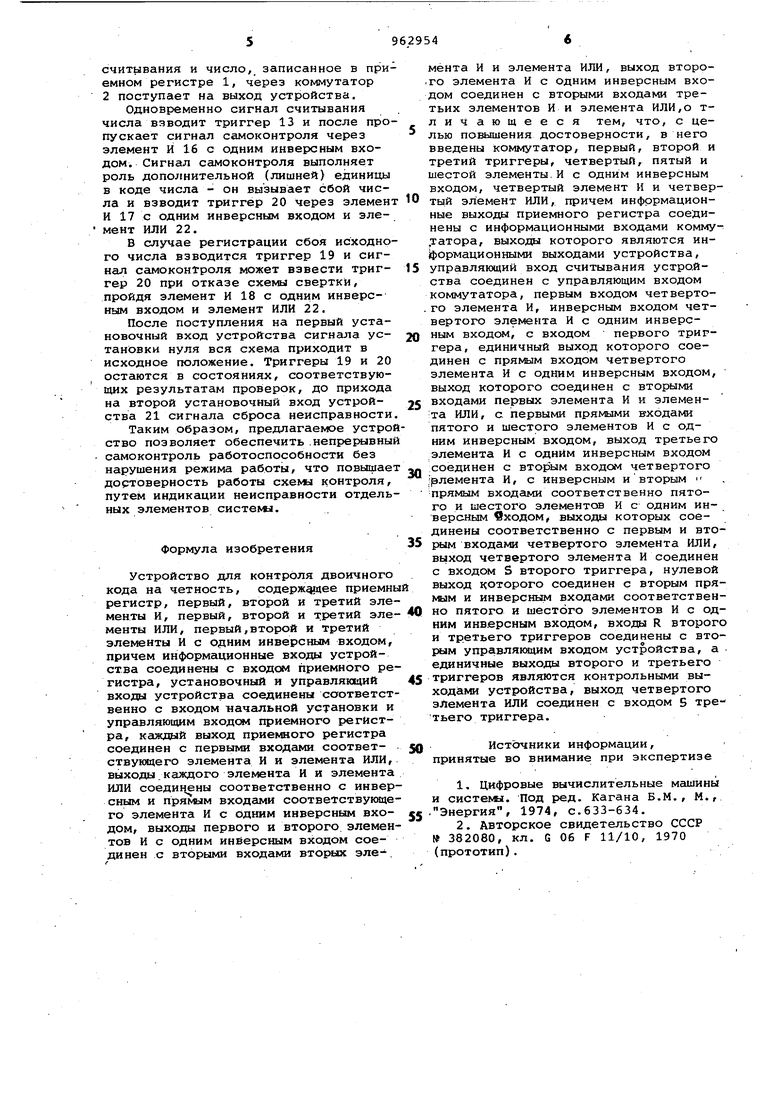

30 вторых элемента И и элемента ИЛИ, выход второго элемента И с одним инвер ным входел соединен с вторыми входами третьих элементов И и ИЛИ, в устройство введены коммутатор, первый, второй и третий триггеры, четвертый, пятый и шестой элементы И с одним инверсным входом, четвертый элемент И и четвертый элемент ИЛИ, причем информационные выходы приемного ре гистра соединены с информационными входами коммутатора, выходы которого являются информационными выходами устройства, управляющий вход считыва ния устройства соединен с управляющи входом коммутатора, первым входом четвертого элемента И, инверсным BXO дом четвертого элемента И с одним инверсным входом, с бходом S первого триггера, единичный выход которого соединен с прямым входом четвертого элемента И с одним инверсным входом, выход которого соединен с вторыми входами первых элемента И, элемента ИЛИ, с первыми прямыми входами пятог и шестого элементов И с одним инаерс ным входом, выход третьего элемента с одним инверсным входом соединен с вторым входом четвертого элемента И, с инверсным и вторым прямым бходами соответственно и шестого элементов И с одним инверсным входом, выхода которых соединены соответстве но с первым и вторым входами четвертого элемента ИЛИ, выход четвертого элемента И соединен с входом второ го триггера, нулевой выход которого соединен с вторым прямым и инверсным входами соответственно пятого и шестого элементов.И с одним инверсным входом, входы R второго л третьего триггеров соединены с вторым управляющим входом устройства, а единичные выходы второго и третьего триггеров являются контрольными выходами устройства,выхо четвертого элемента и соединен с вхо дом S третьего триггера. Сущность предлагаемого изобретени состоит в обеспечении им текущего самоконтроля без нарушения режима работы устройства, что является возможным для широкого класса регистров с предварительной установкой в нулевое состояние, на фиг.1 приведена функциональная электрическая схема устройства; на фиг.2 - эпюры напряжения на соответствующих шинах и выходах соответству ющих элементов. Устройство для контроля двоичного кола на четность состоит из приемного регистра 1, информационные входы которого являются информационными входами устрюйства, а информационные выходы соединены с информационными входами коммутатора 2, выходы которого являются информационными выходами устройствам а также с первыми входами соответствующих элементов И 3-5 и первыми входами соответствующих элементов ИЛИ 6-8, вторые входы элементов И 4 и 5 соединены с вторыми входами соответствг ющих элементов ИЛИ 7и 8 и с выходами соответствующих элементов И 9 и 10 с одним инверсным входом, прямые входы которых соединены с выходами соответствующих элементов ИЛИ 6 и 7, а инверсные входы с выходами соответствующих элементов И 3 и 4. Выход .элемента И 5 соединен с инверсным входом элемента И 11 с одним инверсным входом, с прямым входом которого соединен выход элемента ИЛИ 8. Выход элемента И 11 с одним инверсным входом соединен с первым входом элемента И 12. Кроме того, устройство содержит R-S триггер 13, единичный вход которого соединен с управляющим входом 14 считывания устройства и соответственно с управляющим входом коммутатора 2 и вторым входом элемента И 12, а нулевой входс первым установочным входом 15 устройства и установочным входом регистра 1. Единичный выход триггера 13 соединен с прямьм входом элемента И 16 с одним инверсным входом, инверсный вход которого соединен с управляющим входом 14 считывания, а выход с вторыми входами элемента И 3, элемента ИЛИ 6 и первыми входами элем нтов И 17 и 18 с одним инверсным входом. Инверсный вход элемента 17 и второй прямой вход элемента 18 соединены с выходом элемента И 11 с одним инверсным входом, а второй прямой вход элемента 17 и инверсный вход элемента 18 - с нулевым выходом R-S триггера 19, вход которого соединен с выходом элемента И 12, а другой вход вместе с входом R-S триггера 20 - с вторым управляющим входом 21 устройства. С входом R-S триггера 20 соединен выход элемента ИЛИ 22, входы которого соединены с выходами элементов И 17 и 18 с одним инверсным входом. Первый управляющий вход 8устройства соединен с соответствующим входом приемного регистра. Устройство работает следующим образом. На информационные входы устройства поступает контролируемое число вместе со своим контрольным разрядом, после чего на первый управляющий вход идет сигнал записи и число записывается в приемный регистр. Схема свертки по модулю два, состоящая из элеl eHTOB И 9 и 10 с одним инверсным входом и элементов ИЛИ б и 7, вырабатывает результат свертки по модулю два контролируемого числа и сравнивает его с контрольным разрядом числа на элементе И 5, элементе ИЛИ 8 и элементе И 11 с одним инверсным входом. Затем на управляющий вход считывания устройства поступает сигнал считывания и число, записанное в приемном регистре 1, через коммутатор 2 поступает на выход устройства. Одновременно сигнал считывания числа взводит триггер 13 и после пропускает сигнал самоконтроля через элемент И 16 с одним инверсным входом. Сигнал самоконтроля выполняет роль дополнительной (лишней) единицы в коде числа - он вызывает сбой числа и взводит триггер 20 через элемент И 17 с одним инверсным входом и элемент ИЛИ 22. В случае регистрации сбоя исходного числа взводится триггер 19 и сигнал сги оконТроля может взвести триггер 20 при отказе схемы свертки, пройдя элемент И 18 с одним инверсным входом и элемент ИЛИ 22. После поступления на первый установочный вход устройства сигнала установки нуля вся схема приходит в исходное положение. Триггеры 19 и 20 остаются в состояниях, соответствующих результатам проверок, до прихода на второй установочный вход устройства 21 сигнала сброса неисправности Таким образом, предлагаемое устрой ство позволяет обеспечить .непрерывный самоконтроль работоспособности без нарушения режима работы, что повышает достоверность работы схемы контроля, путем индикации неисправности отдельных элементов систеи«л. Формула изобретения Устройство для контроля двоичного кода на четность, содержаддее приемны регистр, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ, первый,второй и третий элементы И с одним инверсным входом, причем информационные входы устройства соединены с входсм приемного регистра, установочный и управляющий входы устройства соединены соответственно с входом начальной установки и управляющим входом приемного регистра, каждый выход приемного регистра соединен с первыми входами соответствующего элемента И и элемента ИЛИ, выходы каждого элемента И и элемента ИЛИ соединены соответственно с инверсным и прямым входами соответствукяцего элемента И с одним инверсным входом, выходы первого и второго элементов и с одним инверсным входом соединен с вторыми входами вторых эле-. мента И и элемента ИЛИ, выход второ.го элемента И с одним инверсным входом соединен с вторыми входами третьих элементов И и элемента ИЛИ,о тличающееся тем, что, с целью повышения достоверности, в него введены коммутатор, первый, второй и третий триггеры, четвертый, пятый и шестой элементы. И с одним инверсным входом, четвертый элемент И и четвертый элемент ИЛИ, причем информационные выходы приемного регистра соединены с информационными входами комму.татора, выходы которого являются ин(формационными выходами устройства, управляющий вход считывания устройства соединен с управляющим входом коммутатора, первым входом четвертого элемента И, инверсным входом четвертого элемента И с одним инверсным входом, с входом первого триггера, единичный выход которого соединен с прямым входом четвертого элемента И с одним инверсным входом, выход которого соединен с вторыми входами первых элемента И и элемента ИЛИ, с первыми прямыми входами пятого и шестого элементов И с одним инверсным входом, выход третьего элемента И с одним инверсным входом :соединен с вторым входом четвертого ;рлемента И, с инверсным и вторым iпрямым входашш соответственно пятого и шестого элементов и с одним инверсным входом/ выходы которых соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход четвертого элемента И соединен с входом S второго триггера, нулевой выход которого соединен с вторым прямым и инверсным входами соответственно пятого и шестого элементов И с одним инверсным входом, входы R второго и третьего триггеров соединены с вторым управлякнцим входом устройства, а единичные выходы второго и третьего триггеров являются контрольными выходами устройства, выход четвертого элемента ИЛИ соединен с входом S третьего триггера. Источники информации, принятые во внимание при экспертизе 1.Цифровые вычислительные машины и систекы. Под ред. Кагана Б.М., М., Энергия, 1974, с.633-634. 2.Авторское свидетельство СССР № 382080, кл. G 06 F 11/10, 1970 (прототип).

гз

fS

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1265860A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛУЧЕНИЕМ ОЦЕНКИ КАЧЕСТВА ЗНАНИЙ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2001 |

|

RU2248610C2 |

| Микропрограммное вычислительное устройство | 1981 |

|

SU1008741A1 |

| Устройство для контроля четности двоичного последовательного кода | 1989 |

|

SU1702373A1 |

| Устройство для вывода информации | 1984 |

|

SU1238090A1 |

| Счетное устройство с предварительной уставкой кода | 1982 |

|

SU1027832A1 |

| Устройство для управления ленточным перфоратором | 1989 |

|

SU1735876A1 |

a-j

/у . /г

12 -тат

18

ZJ

5 г

19

гЩ

а-П

ff1418

гв

/5

ГП.

П

Фие2 ;

Авторы

Даты

1982-09-30—Публикация

1981-02-20—Подача