Изобретение ОТРЮСИТСЯ к вычислительной технике, в частности к устройствам и системам микропрог раммного управления, и может быть использовано при построении отказоустойчивых ЭВМ, АСУ технологическими процессами и контроллеров с микропрограммным управлением.

Цель изобретения - повышение отка- зоустойчивости устройства а

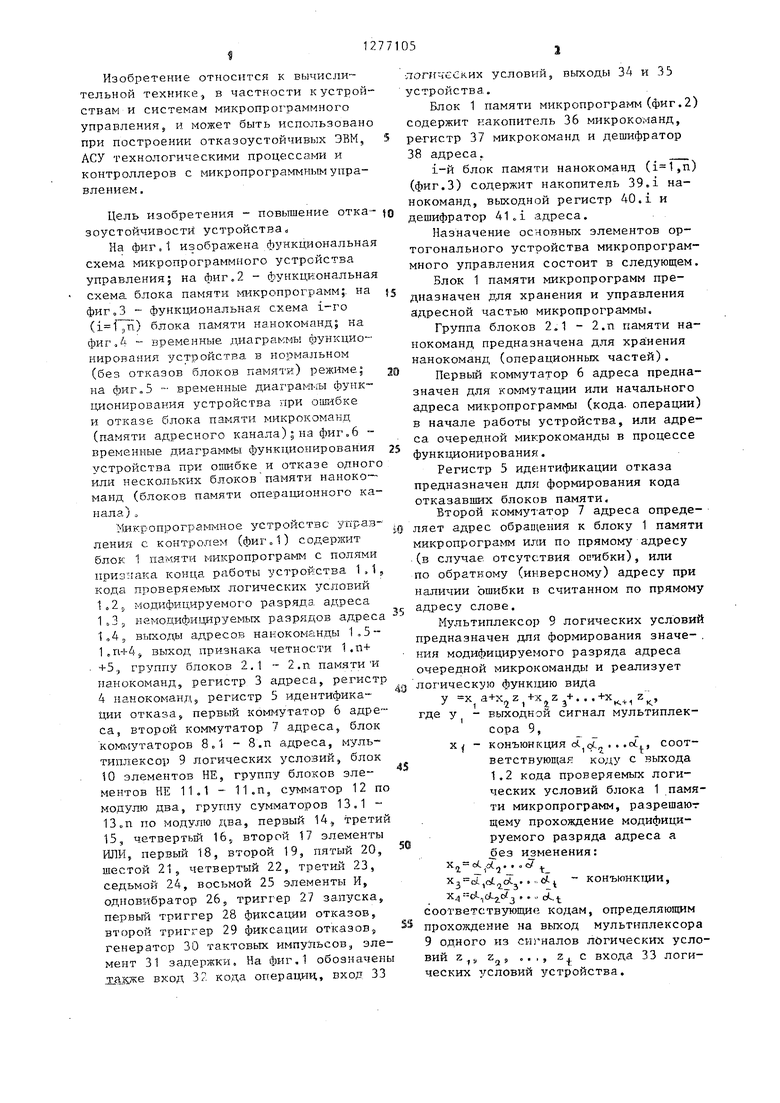

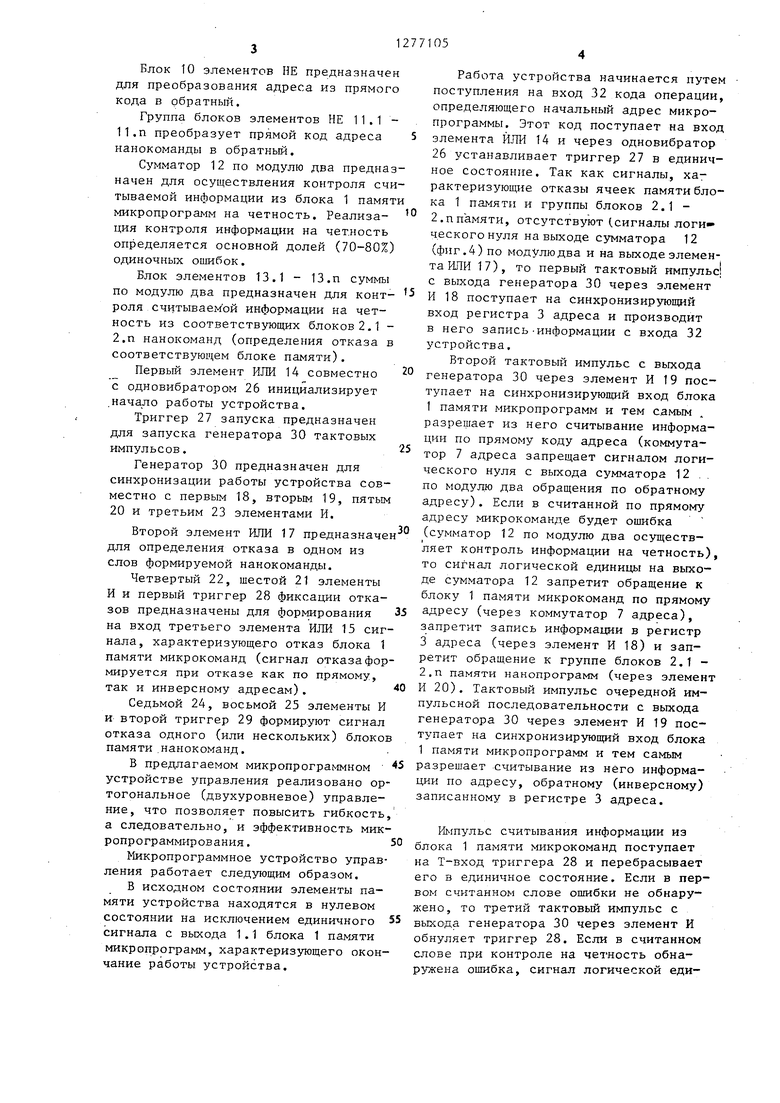

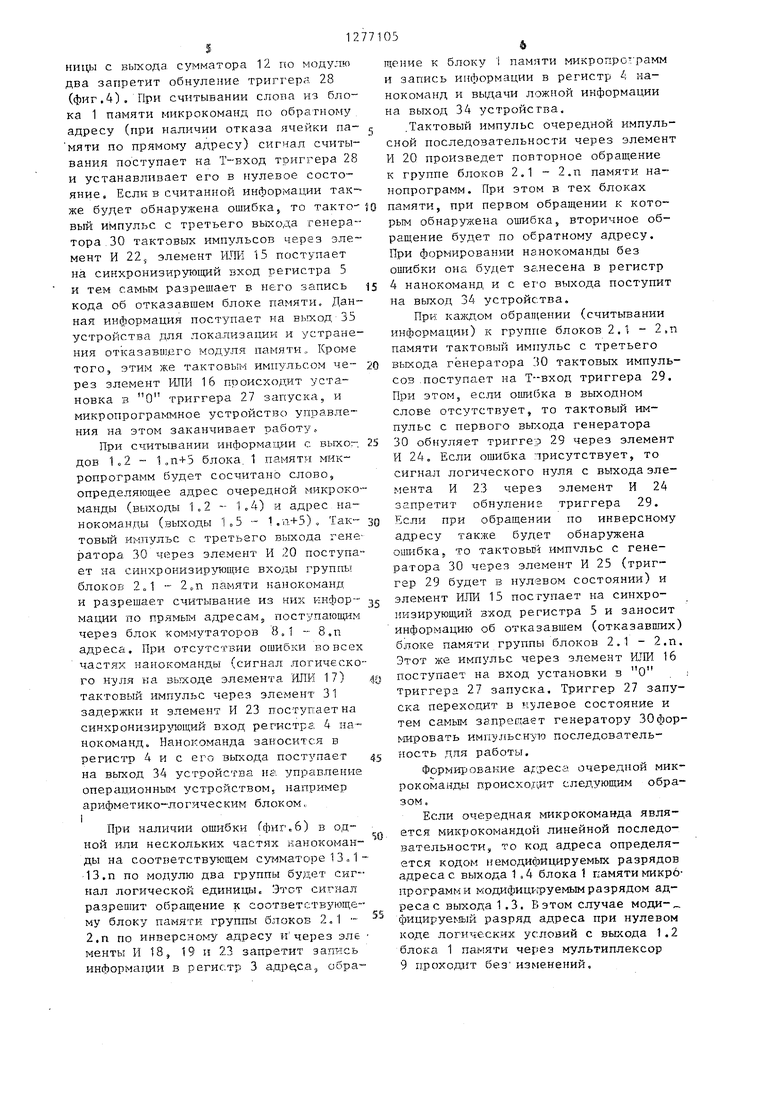

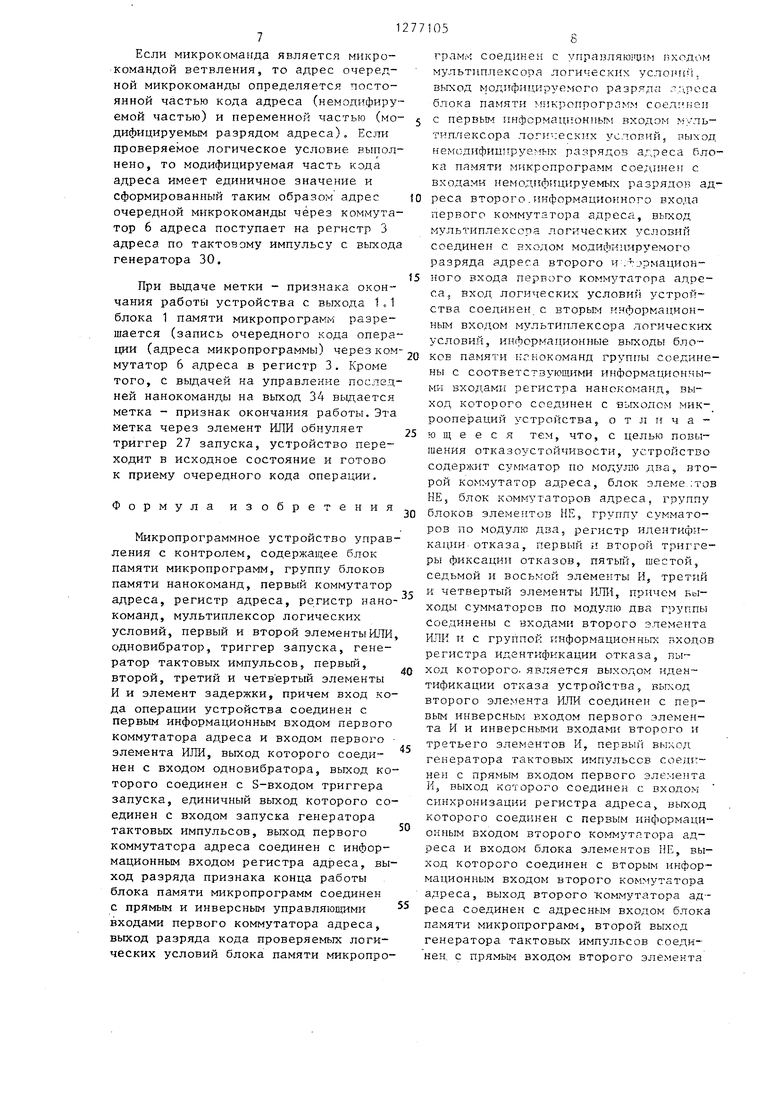

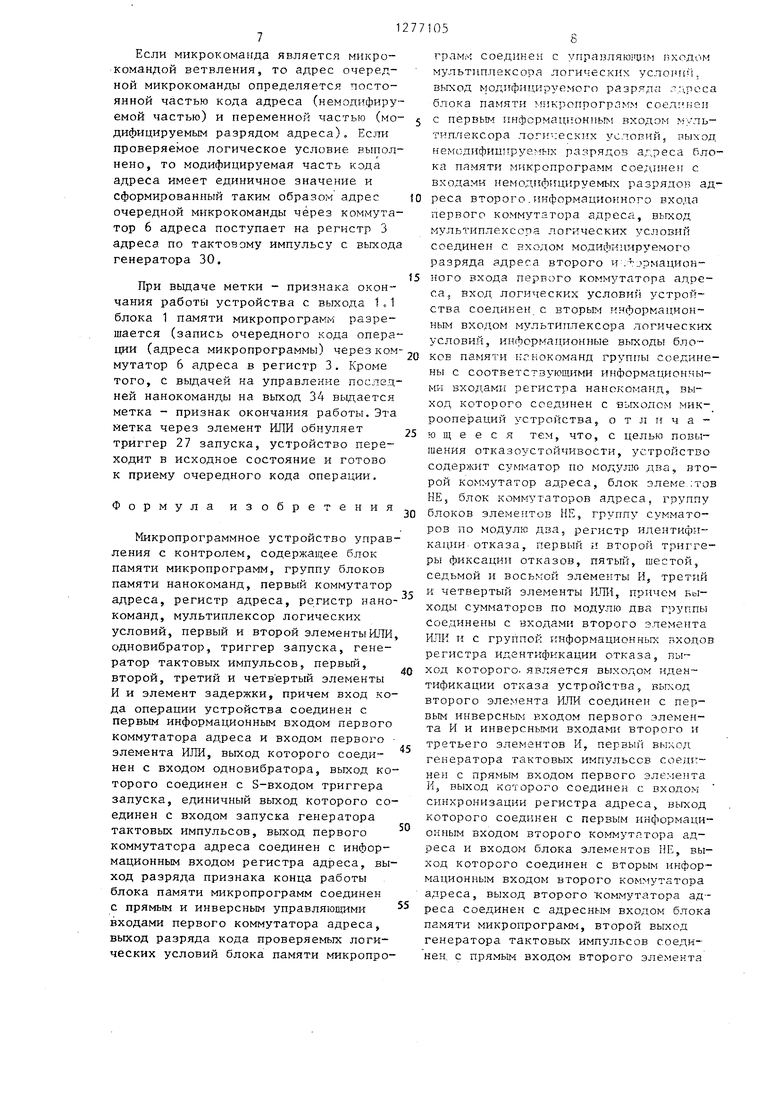

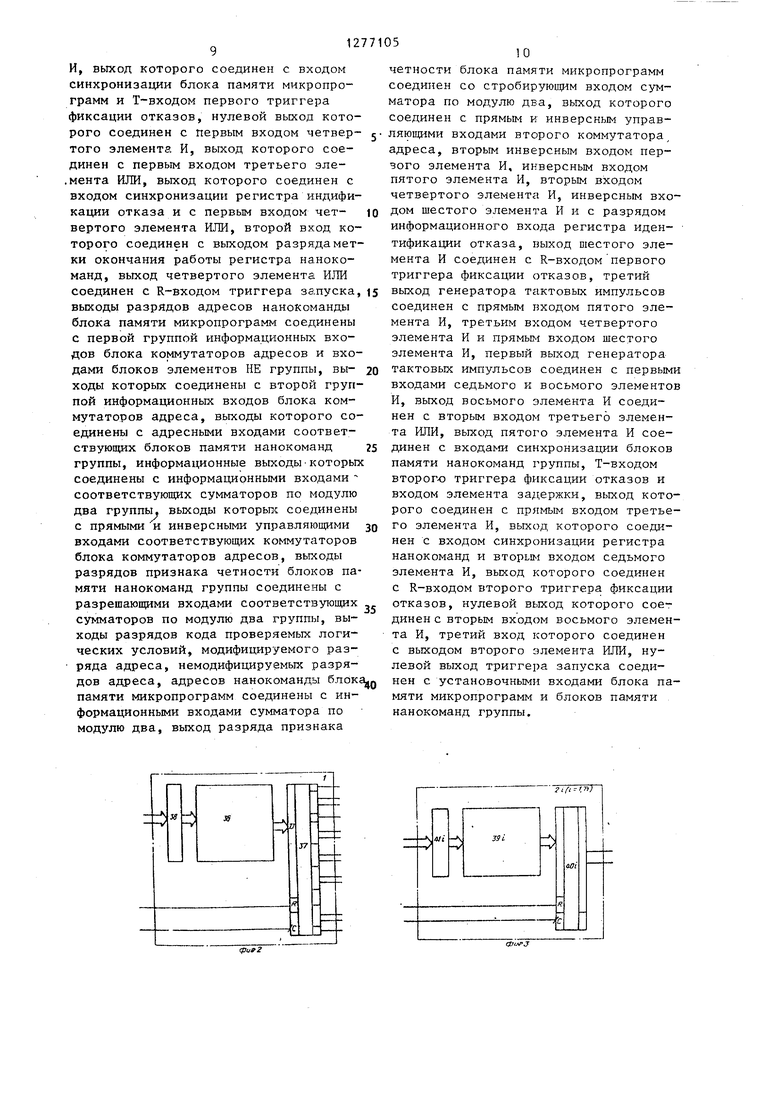

На фиг.1 изображена функциональная схема микропрограммного устройства управления; на фиг,2 - ф ункциональная схема блока памяти микропрограмм;, на фиг,3 функциональная схема i-ro блока памяти наноконанд; на фиг,4 -- временные диаграммы функционирования устройства в нормальном (без отказов блоков памяти) режиме; на фиг,5 - временные диаграммы функционирования устройства при ошибке и отказе блока памяти микрокоманд (памяти адресного канала);на фиг„6 - временные диаграммы, функционирования устройства при опшбке и отказе одного или нескольких блоков памяти наноко- манд (блоков памяти операционного канала) ,

Микропрограммное устройстве управ- ления с контролем (фиГо1) содержит блок 1 памяти микропрограмм с полями признака конца работы устройства 1.1, кода проверяемых логических условий 1.2j модифицируемого разряда, адреса 1,3, нe юдифи..JJi:pyeмьпc разрядов адреса 1о4,, выходы адресов нанокоманды 1.5-- 1,п-1-4,, выход признака четности 1 ,п4- . +5,, группу блоков 2,1 - 2.п памяти и на.нокоманд, регистр 3 адреса, регистр 4 нанокомандз регистр 5 идентификации отказаS первый коммутатор 6 адреса, второй коммутатор 7 адреса, блок коммутаторов 8„1 8.п адреса, мультиплексор 9 логических условий, блок 10 элементов НЕ, группу блоков элементов НЕ 11.1 - 11.ц, cyMi iaTop 12 по модулю два, группу сумматоров 13,1 - 13„п по модулю два, первый 14, третий 15, четвертьй 16. второй 17 элементы ИЛИ, первый 18, второй 19, пятый 20, шестой 21, четвертый 22, третий 23, седьмой 24, восьмой 25 элементы И, одновибратор 26, триггер 27 запуска, первый триггер 28 фиксации отказов, второй триггер 29 фиксации отказов, генератор 30 тактовых импуй шсов, элемент 31 задержки. На фиг,1 обозначены Л1а;(57ке вход 37. кода операции, вход 33

° 5

,

3

5

логи-ч-еских условий, выходы 34 и 35 устройства..

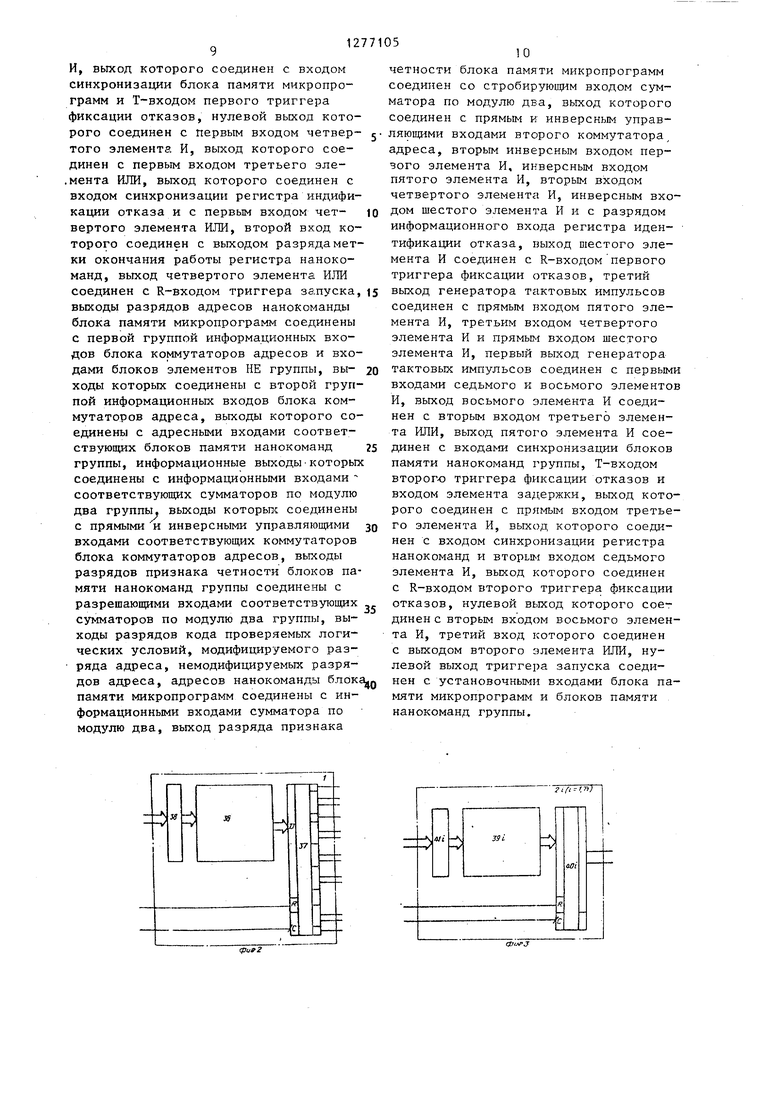

Блок 1 памяти микропрограмм (фиг.2) содержит накопитель 36 микрокоманд, регистр 37 микрокоманд и дешифратор 38 адреса.

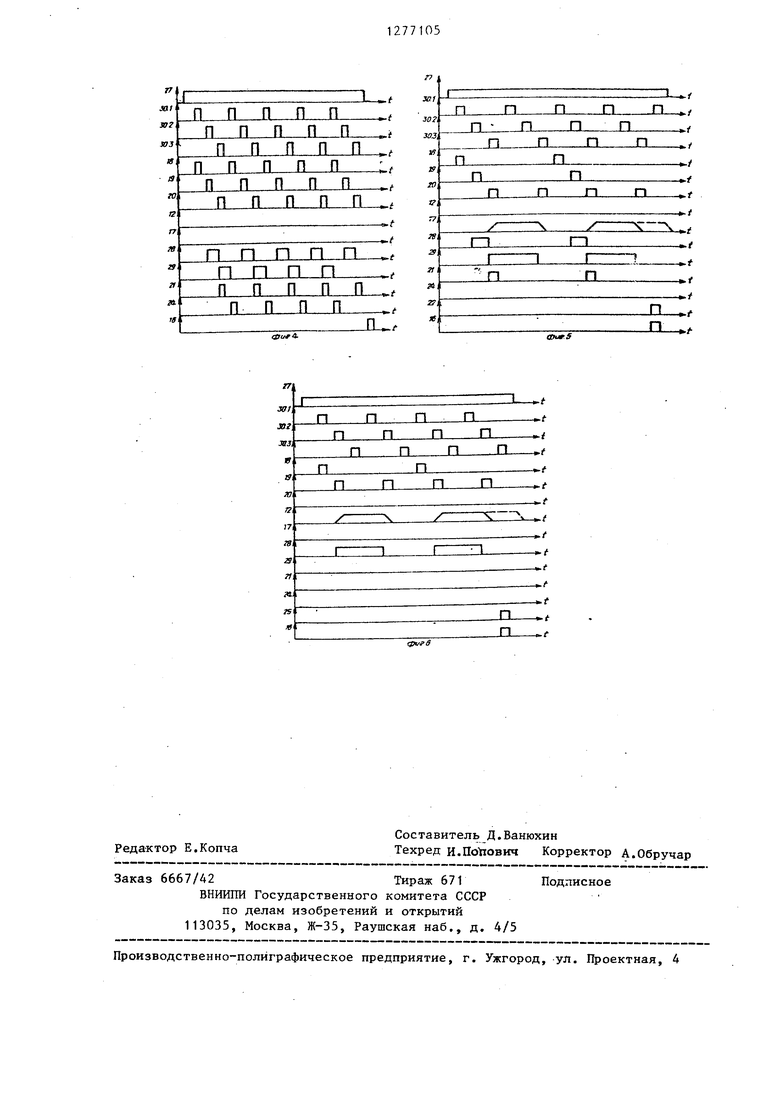

L-й блок памяти нанокоманд (,п) (фиг.З) содержит накопитель 39.i нанокоманд, выходной регистр 40.1 и дешифратор 41„i адреса.

Назначение основных элементов ортогонального устройства микропрограммного управления состоит в следующем.

Блок 1 памяти микропрограмм предназначен для хранения и управления адресной частью микропрограммы.

Группа блоков 2.1 - 2.п памяти нанокоманд предназначена для хра:нения нанокоманд (операционных частей).

Первый коммутатор 6 адреса предназначен для коммутации или начального адреса микропрограммы (кода, операции) в начале работы устройства, или адреса очередной микрокоманды в процессе функционирования.

Регистр 5 идентификации отказа предназначен для формирования кода отказавших блоков памяти.

Второй коммутатор 7 адреса определяет адрес обращения к блоку 1 памяти микропрограмм или по прямому адресу (в случае отсутствия оп-ибки), или по обратному (инверсному) адресу при наличии ошибки в считанном по прямому адресу слове.

Мультиплексор 9 логических условий предназначен для формирования знача- . кия модифицируемого разряда адреса очередной микрокоманды и реализует логическую функцию вида

у ..., где у - выходной сигнал мультиплексора 9,

X - конъюнкция с оС . . .oi., соответствующая коду с выхода 1.2 кода проверяемых логических условий блока 1 памяти микропрограмм, разрешаюг тему прохождение модифицируемого разряда адреса а без изменения:

,d.oL . . .-Ы - КОНЪЮНКЦИИ, X,oL,f.2. ° t

соответствующие кодам, определяющим прохождение на выход мультиплексора 9 одного из сиг налов логических условий z, ,.,, входа 33 логических условий устройства.

Блок 10 элементов НЕ предназначен для преобразования адреса из прямого кода в рбратный.

Группа блоков элементов НЕ 11.1- 11.П преобразует прямой код адреса нанокоманды в обратный.

Сумматор 12 по модулю два предназначен для осуществления контроля считываемой информации из блока 1 памят микропрограмм на четность. Реализа- ция контроля информации на четность определяется основной долей (70-80%) одиночных ошибок.

Блок элементов 13.1 - 13.п суммы по модулю два предназначен для конт- роля считываемой информации на четность из соответствующих блоков 2,1 - 2,п нанокоманд (определения отказа в соответствующем блоке памяти).

Первый элемент ИЛИ 14 совместно с одновибратором 26 инициализирует .начало работы устройства.

Триггер 27 запуска предназначен для запуска генератора 30 тактовых импульсов,

Генератор 30 предназначен для синхронизации работы устройства совместно с первым 18, вторым 19, пятым 20 и третьим 23 элементами И.

Второй элемент ИЛИ 17 предназначен для определения отказа в одном из слов формируемой нанокоманды.

Четвертый 22, шестой 21 элементы И и первый триггер 28 фиксации отказов предназначены для фор дарования на вход третьего элемента ИЛИ 15 сигнала, характеризующего отказ блока 1 памяти микрокоманд (сигнал отказа формируется при отказе как по прямому, так и инверсному адресам).

Седьмой 24, восьмой 25 элементы И и второй триггер 29 формируют сигнал отказа одного (или нескольких) блоков памяти .нанокоманд.

В предлагаемом микропрограммном устройстве управления реализовано ортогональное (двухуровневое) управление, что позволяет повысить гибкость а следовательно, и эффективность микропрограммирования.

Микропрограммное устройство управления работает следующим образом.

В исходном состоянии элементы памяти устройства находятся в нулевом состоянии на исключением единичного сигнала с выхода 1,1 блока 1 памяти микропрограмм, характеризующего окончание работы устройства.

Работа устройства начинается путе поступления на вход 32 кода операции определяющего начальный адрес микропрограммы. Этот код поступает на вход элемента ИЛИ 14 и через одновибратор 26 устанавливает триггер 27 в единичное состояние. Так как сигналы, ха- paктepизyющ ie отказы ячеек памяти блока 1 памяти и группы блоков 2,1 - 2.ппамяти, отсутствуют {.сигналы логического нуля на выходе сумматора 12 (фиг, 4) по модулю два и на выходе элемента ИЛИ 17), то первый тактовый импульс с выхода генератора 30 через элемент И 18 поступает на синхронизирующий вход регистра 3 адреса и производит в него запись-информации с входа 32 устройства.

Второй тактовый импульс с выхода генератора 30 через элемент И 19 поступает на синхронизирующий вход блока 1 памяти микропрограмм и тем самым . разрешает из него считывание информации по прямому коду адреса (коммутатор 7 адреса запрещает сигналом логического нуля с выхода сумматора 12.. по модулю два обращения по обратному адресу). Если в считанной по прямому адресу микрокоманде будет ошибка (сумматор 12 по модулю два осуществляет контроль информации на четность) то сигнал логической единицы на выходе сумматора 12 запретит обращение к блоку 1 памяти микрокоманд по прямому адресу (через коммутатор 7 адреса), запретит запись информации в регистр 3 адреса (через элемент И 18) и запретит обращение к группе блоков 2,1 - 2.П памяти нанопрограмм (через элемен И 20), Тактовый импульс очередной импульсной последовательности с выхода генератора 30 через элемент И 19 поступает на синхронизирующий вход блока 1 памяти микропрограмм и тем самым разрешает считывание из него информации по адресу, обратному (инверсному) записанному в регистре 3 адреса,

Импульс считывания информации из блока 1 памяти микрокоманд поступает на Т-вход триггера 28 и перебрасывает его в единичное состояние. Если в первом считанном слове ошибки не обнаружено, то третий тактовый импульс с выхода генератора 30 через элемент И обнуляет триггер 28, Если в считанном слове при контроле на четность обнаружена ошибка, сигнал логической единнцы с выхода, сумматора 12 по модулю два запретит обнуление триггера 28 (фиг,4). При считывании слова из блока 1 памяти микрокоманд по обратному адресу (при наличии отказа ячейки па- мяти по прямому адресу) сигнал считывания поступает на триггера 28 и устанавливает его в нулевое состояние. Если в считанной информации также будет обнаружена ошибка, то такто вый импульс с третьего выхода генератора,30 тактовых импульсов через элемент И 22, элемент ИЛИ 15 поступает на синхронизирукиций вход регистра 5 и тем самым разрешает в него запись кода об отказавшем блоке памяти. Данная информация поступает на выход 35 устройства для локгглизадии и устранения oTKasaBiiJiiro модуля памяти,. Кроме того, этим же тактовым импульсом через элемент КПИ 16 происходит установка в О триггера 27 запуска, и микропрограммное устройство управления на этом заканчивает работу..

При считывании информа) с выходов 1„2 1.П-1-5 блока, 1 памяти микропрограмм будет сосчитано слово, определяющее адрес очередной микрокоманды (выходы 1 .2 - 1„4) и адрес на- нокоманды (выходы - 1 .а+5) , Тактовый импульс с, третьего гене- ратора 30 через элемент И 20 поступает на синхронизирующие входы группы блоков 2.1 - 2„п памяти нанокоманд и разрешает считывание из них информации по прямьм адресам, поступающим через блок коммутаторов 8,1 - 8,п адреса. При отсутствии ошибки во всех частях нанокоманды (сигнал логического нуля на выходе элемента ШШ 17) тактовый импульс через элемент 31 задержки и элемент И 23 поступает на синхронизирлтощий вход, регистра 4 нанокоманд Нанокоманда зав:оситс,я в регистр 4 и с его вьглода поступает на выход 34 устройства на управление операционным устройством, например арифметико-логическим блоком,.

При наличии ошибки Сфиг.б) в одной или нескольких частях канокоман- ды на соответствующем cyt/iMaTope 13., 1- 13.П по модулю два группы будет сигнал логической единицы. Этот сигнал разрешит обращение к соответствующему блоку памяти группы блоков 2,1 - 2.П по инверсному адресу и через эле ментъ И 18, 19 и 23 запретит запись информации в регистр 3 адре,са5 обра0

5

0

5

0

5

5

0

5

щение к блоку 1 памяти микропрот рамм и запись информации в регистр 4 нанокоманд и выдачи ложной информации на выход 34 устройства.

.Тактовый импульс очередной импульсной последовательности через элемент И 20 произведет повторное обращение к группе блоков 2.1 - 2.и памяти на- нопрограмм. При этом в тех блоках памяти, при первом обращении к которым обнаружена ошибка, вторичное обращение будет по обратному адресу. При формировании нзнокоман.ды без ошибки она будет занесена в регистр 4 нанокоманд и с его выхода поступит на выхо.д 34 устройства.

При каждом обрап1;ении (считывании информации) к группе блоков 2,1 - 2,п памяти тактовый импульс с третьего выхода генератора 30 тактовых импульсов ,поступает на Т--ВХОД триггера 29. При этом, если ошибка в выходном слове отсутствует, то тактовый импульс с первого выхода генератора 30 обнуляет триггер 29 через элемент И 24. Если ошибка лрисутствует, то сигнал логического нуля с выхода элемента И 23 через элемент И 24 запретит обнуление триггера 29. ЕС.ЛИ при обращении по инверсному адресу также будет обнаружена оишбка. то тактовьп HMnvnbc с генератора 30 через элемент И 25 (триггер 29 будет в нулевом состоянии) и элемент ИЛИ 15 поступает на синхронизирующий вход регистра 5 и заносит информацию об отказавшем (отказавших) блоке памяти группы блоков 2.1 - 2.п. Этот же импульс через элемент ИЛИ 16 поступает на вход установки в О ; триггера 27 запуска. Триггер 27 запуска переходит в нулевое состояние и тем самым запрещает генератору 30формировать импульсную последовательность для работы.

Формирование afcpecs, очередной микрокоманды происходит следующим образом.

Если очередная микрокоманда является микрокомандой линейной последовательности, то код адреса определяется кодом немодифицируемых разрядов адреса с выхода 1 ,4 блока 1 памяти микропрограмм и мo xифицI-ipyeмымразрядом адреса с выхода 1.3. В этом случае моди-„ фицируе№1й разряд адреса при нулевом коде логических условий с выхода 1.2 блока 1 памяти через мультиплексор 9 проходит без изменений.

Если микрокоманда является микрокомандой ветвления, то адрес очередной микрокоманды определяется постоянной частью кода адреса (немодифиру- емой частью) и переменной частью (мо- дифицируемым разрядом адреса). Если проверяемое логическое условие выполнено, то модифицируемая часть кода адреса имеет единичное значение и сформированный таким образом адрес очередной микрокоманды через коммутатор 6 адреса поступает на регистр 3 адреса по тактовому импульсу с выхода генератора 30,

При вьщаче метки - признака окончания работы устройства с выхода блока 1 памяти микропрограмм разрешается (запись очередного кода операции (адреса микропрограммы) через коммутатор 6 адреса в регистр 3. Кроме того, с вьщачей на управление последней нанокоманды на выход 34 вьщается метка - признак окончания работы. Эта метка через элемент ИЛИ обнуляет триггер 27 запуска, устройство переходит в исходное состояние и готово к приему очередного кода операции.

Формула изобретения

Микропрограммное устройство управления с контролем, содержащее блок памяти микропрограмм, группу блоков памяти нанокоманд, первый коммутатор адреса, регистр адреса, регистр нанокоманд, мультиплексор логических условий, первый и второй элементыИЛИ, одновибратор, триггер запуска, генератор тактовых импульсов, первый, второй, третий и четвертый элементы И и элемент задержки, причем вход кода операции устройства соединен с первым информационным входом первого коммутатора адреса и входом первого элемента ИЛИ, выход которого соединен с входом одновибратора, выход которого соединен с S-входом триггера запуска, единичный выход которого соединен с входом запуска генератора тактовых импульсов, вьгход первого коммутатора адреса соединен с информационным входом регистра адреса, выход разряда признака конца работы блока памяти микропрограмм соединен с прямым и инверсным управляющими входами первого коммутатора адреса, выход разряда кода проверяемых логических условий блока памяти микропроjю

0

15

5

0

5

0

5

грамм соединен с управляюпц м лходом мультиплексора логических услорг ;, выход модифицируе ого разряда с .-фсса блока памяти микропрогр тмм соелинеп с первым пнформацион ьг -; входом мультиплексора логи :еских условий, выход нeмoдифициpye fыx разрядов адреса блока памяти микропрограмм соединен с входами немодифицируемых разрядов адреса второго.информационного входа первого коммутатора адреса, выход мультиплексора логических услов1 Гй соединен с входом модифицируемого разряда адреса второго и . Jp iaциoн- ного входа первого коммутатора адреса, вход логических условий устройства соединен с вторым информационным входом мультиплексора логических условий, информационные выходы блоков паьшти мг нокоманд группы соединены с соответствующими ир1формационны- ми вхо/тами регистра нанокоманд, выход которого соединен с выходом микроопераций устройства, отличающееся тем, что, с целью ПОБЕЛ- шения отказоустойчивости, устройство содержит сумматор по модулю два, второй коммутатор адреса, блок элеме :тов НЕ, блок коммутаторов адреса, группу блоков элемеЕ1тов НЕ, группу сумматоров по модулю два, регистр идентификации отказа, первый и второй триггеры фиксации отказов, пятый, шестой, седьмой и восьмой элементы И, третий и четвертый элементы lUIIi, причем вь1- ходы сумматоров по модулю два группы соединены с входами второго элемента ИЛИ и с группой информационных входов регистра идентифр кации отказа, выход которого, является выходом идентификации отказа устройства, вьгход второго ИЛИ соединен с первым инверсным входом первого элемента И и инверсными входами второго и третьего элементов И, первый выход генератора тактовых импульсов соединен с прямым входом первого эле:-;ента И, выход которого соединен с входом синхронизации регистра адреса вьгход которого соединен с первым информационным входом второго коммутатора адреса и входом блока элементов НЕ, выход которого соединен с вторым информационным входом второго коммутатора адреса, выход второго коммутатора адреса соединен с адресным входом блока памяти микропрограмм, второй выход генератора тактовых импульсов соединен, с прямым входом второго элемента

И, вькод которого соединен с входом синхронизации блока памяти микропрограмм и Т-входом первого триггера фиксации отказов, нулевой вькод которого соединен с первым входом четвер- с того элемента И, выход которого соединен с первым входом третьего эле- .мента ИЛИ, вькод которого соединен с входом синхронизации регистра индифи- кации отказа и с первым входом чет- ю вертого элемента ИЛИ, второй вход которого соединен с выходом разряда метки окончания работы регистра наноко- манд, выход четвертого элемента ИЛИ соединен с R-входом триггера запуска, 15 выходы разрядов адресов нанокоманды блока памяти микропрограмм соединены с первой группой информационных входов блока коммутаторов адресов и входами блоков элементов НЕ группы, вы- 20 ходы которых соединены с второй группой информационных входов блока коммутаторов адреса, выходы которого соединены с адресными входами соответствующих блоков памяти нанокоманд 25 группы, информационные выходы-которых соединены с информационными входами соответствующих сумматоров по модулю два группы, выходы которьпс соединены с прямыми и инверсными управляющими зо входами соответствующих коммутаторов блока коммутаторов адресов, выходы разрядов признака четности блоков памяти нанокоманд группы соединены с разрешающими входами соответствующих сумматоров по модулю два группы, выходы разрядов кода проверяемых логических условий, модифицируемого разряда адреса, немодифицируемых разря10

четности блока памяти микропрограмм соединен со стробирующим входом сумматора по модулю два, выход которого соединен с прямым и инверсным управляющими входами второго коммутатора адреса, вторым инверсным входом первого элемента И, инверсным входом пятого элемента И, вторым входом четвертого элемента И, инверсным входом шестого элемента И и с разрядом информационного входа регистра идеи- тификации отказа, выход шестого элемента И соединен с R-входом первого триггера фиксации отказов, третий выход генератора тактовых импульсов соединен с прямым входом пятого элемента И, третьим входом четвертого элемента И и прямым входом шестого элемента И, первый выход генератора тактовых импульсов соединен с первыми входами седьмого и восьмого элементов И, выход восьмого элемента И соединен с вторым входом третьего элемента ИЛИ, выход пятого элемента И соединен с входами синхронизации блоков памяти нанокоманд группы, Т-входом второго триггера фиксации отказов и входом элемента задержки, выход которого соединен с прямым входом третьего элемента И, выход которого соединен с входом синхронизации регистра нанокоманд и BTOPLIM входом седьмого элемента И, выход которого соединен с R-входом второго триггера фиксации отказов, нулевой выход которого соединен с вторым входом восьмого элемента И, третий вход которого соединен с вьЕходом второго элемента ИЛИ, нулевой выход триггера запуска соедидов адреса, адресов нанокоманды блока нен с установочными входами блока па- памяти микропрограмм соединены с ин-мяти микропрограмм и блоков памяти формационными входами сумматора по нанокоманд группы. модулю два, выход разряда признака

1277105

10

четности блока памяти микропрограмм соединен со стробирующим входом сумматора по модулю два, выход которого соединен с прямым и инверсным управляющими входами второго коммутатора адреса, вторым инверсным входом первого элемента И, инверсным входом пятого элемента И, вторым входом четвертого элемента И, инверсным входом шестого элемента И и с разрядом информационного входа регистра идеи- тификации отказа, выход шестого элемента И соединен с R-входом первого триггера фиксации отказов, третий выход генератора тактовых импульсов соединен с прямым входом пятого элемента И, третьим входом четвертого элемента И и прямым входом шестого элемента И, первый выход генератора тактовых импульсов соединен с первым входами седьмого и восьмого элементо И, выход восьмого элемента И соединен с вторым входом третьего элемента ИЛИ, выход пятого элемента И соединен с входами синхронизации блоков памяти нанокоманд группы, Т-входом второго триггера фиксации отказов и входом элемента задержки, выход которого соединен с прямым входом третьего элемента И, выход которого соединен с входом синхронизации регистра нанокоманд и BTOPLIM входом седьмого элемента И, выход которого соединен с R-входом второго триггера фиксации отказов, нулевой выход которого соединен с вторым входом восьмого элемента И, третий вход которого соединен с вьЕходом второго элемента ИЛИ, нулевой выход триггера запуска соединен с установочными входами блока па- мяти микропрограмм и блоков памяти нанокоманд группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в цифровых системах с повышенной надежностью. Цель изобретения - повышение надежности функционирования. Устройство содержит блоки памяти микрокоманд 1 и нанокоманд 2.1 - 2.п, регистры адреса 3, микроопераций 4, отказа 5, коммутаторы адреса 6,7,8.1 - 8.п, мультиплексор 9, элементы НЕ 10., 11.1 - 11.П, сумматоры по модулю два 12, 13. Г - 13.п, элементы ИЛИ 14-17, И 18-25, одновибратор 26, триггеры 27-29, генератор импульсов 30, элементы задержки 31. Новык И в устройстве являются сумматоры по модулю два 12, 13.1 - 13.П, коммутаторы адреса 7, 8.1 - 8.П, регистр 5, триггеры 28, 29, элементы НЕ 10, 11.1 - 11.п, пятый 22, восьмой 25 элементы И, третий 16 и четвертый 17 элементы ИЛИ. 6 ил, (Л го сд cpue.l

(pufZ

fift-ijfi

-

3Si

aoi

фаг

П rL

Л

XL

П

JCL

Л

ПЛ

OL

XL

XL

XL

XL

XL

П XICL

XL

JDL

-./ -.i -./ -./ -.# -.f

XDЛ

arufS

JDL

XL

XL

XL

n

XL

XL

XL

XL

II

XL

ПП ПX

П П ПП

Редактор Е.Копча

Заказ 6667/42Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

XL

XL

XL

XL

XL

XL

ПП ПXL

XL

.f

./

XL

Л

-./ - -( . -«./

Составитель Д.Ванюхин

Техред И.По тович Корректор А.Обручар

Подписное

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103231A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1985-05-07—Подача