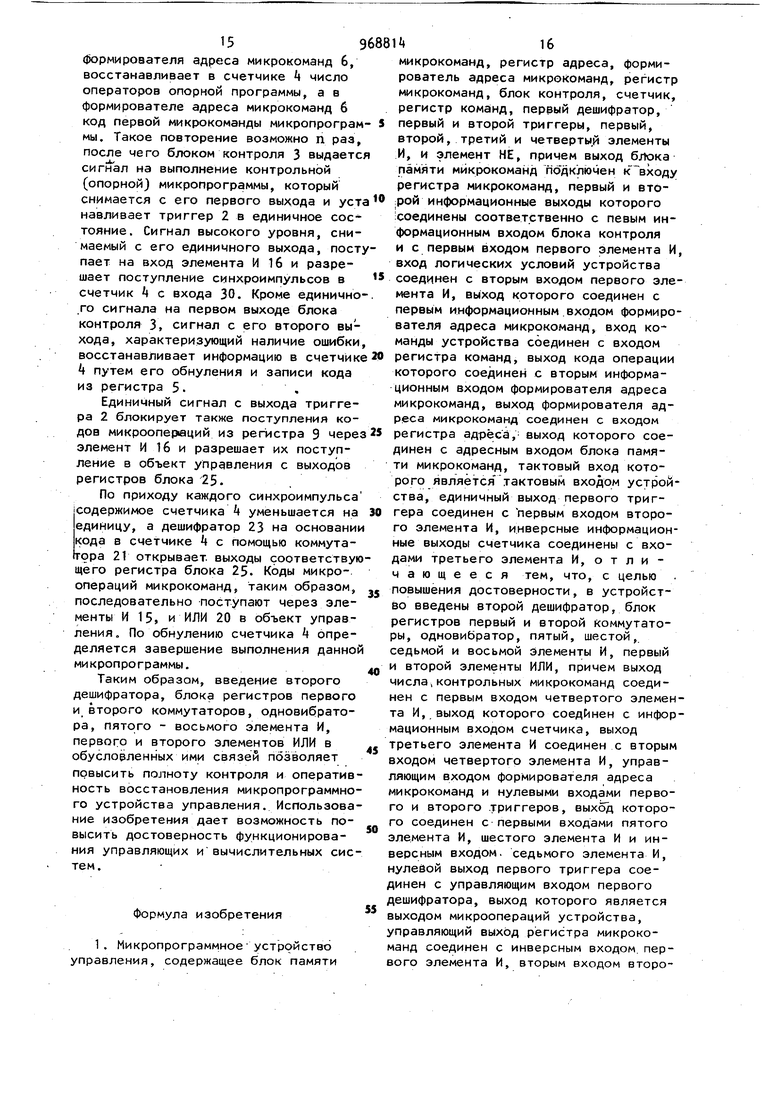

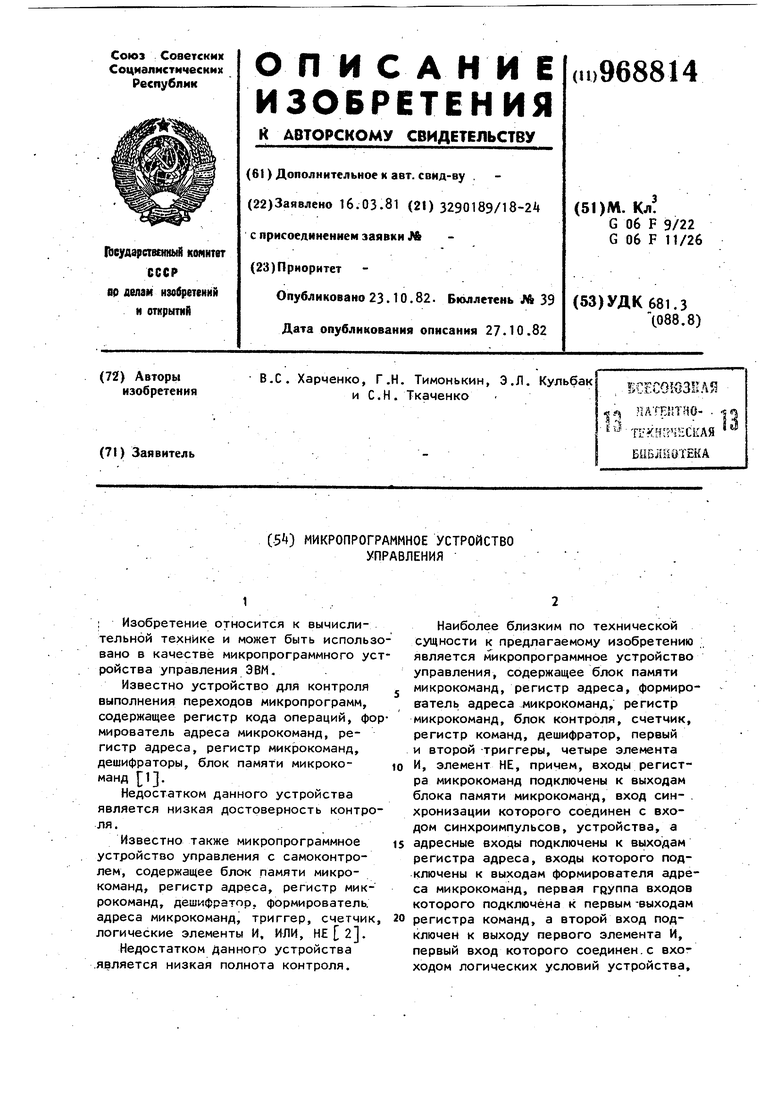

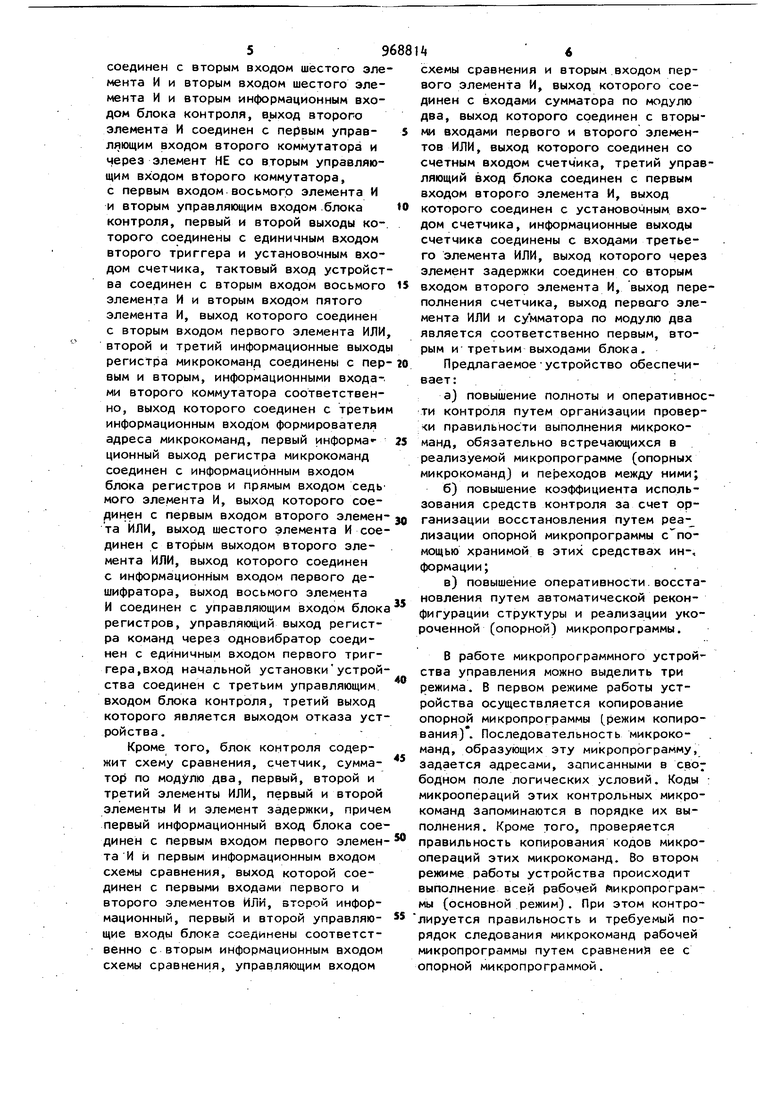

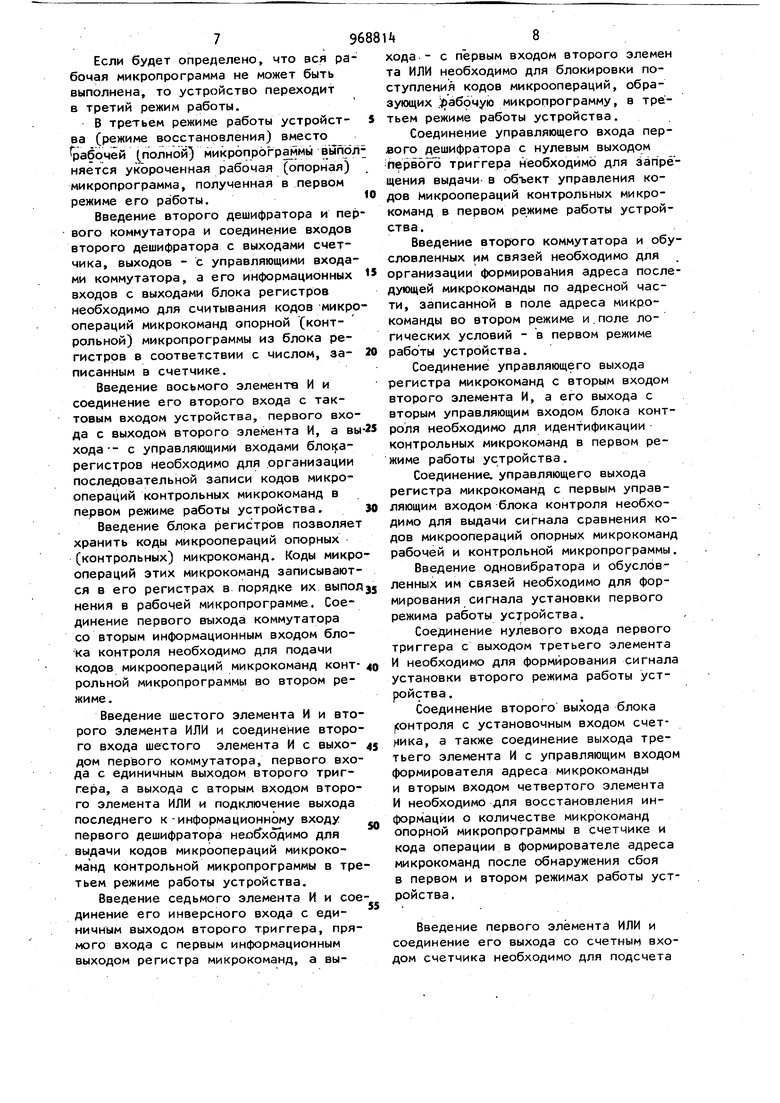

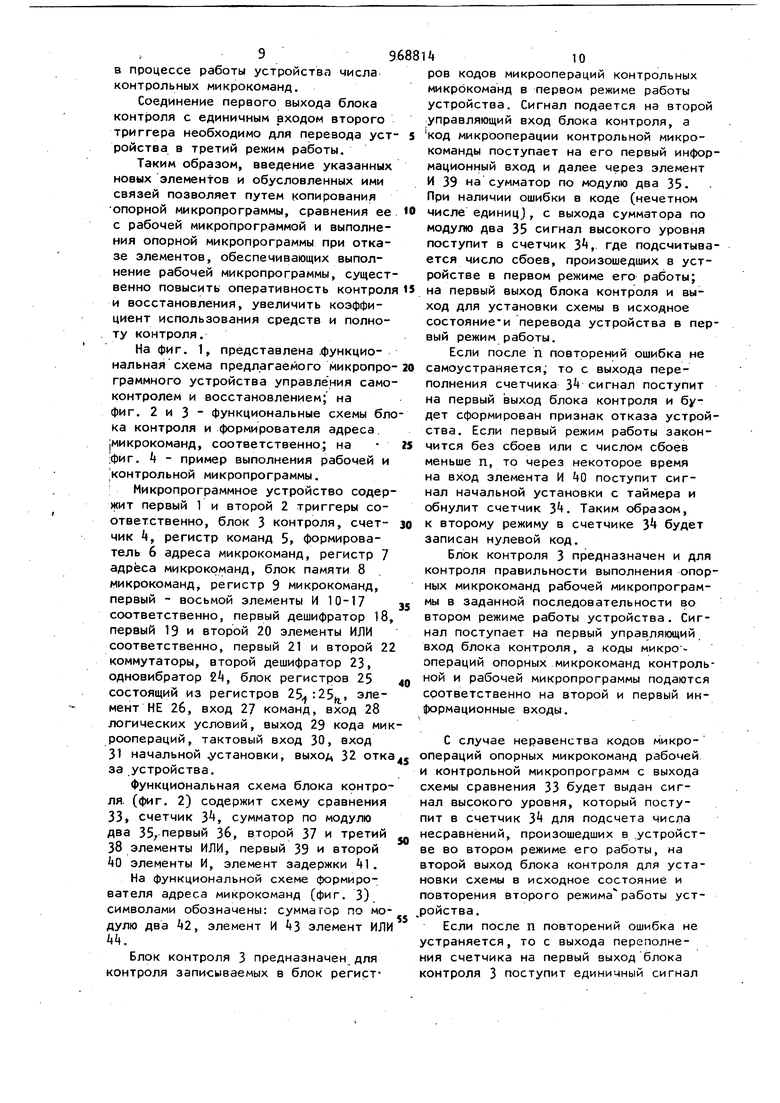

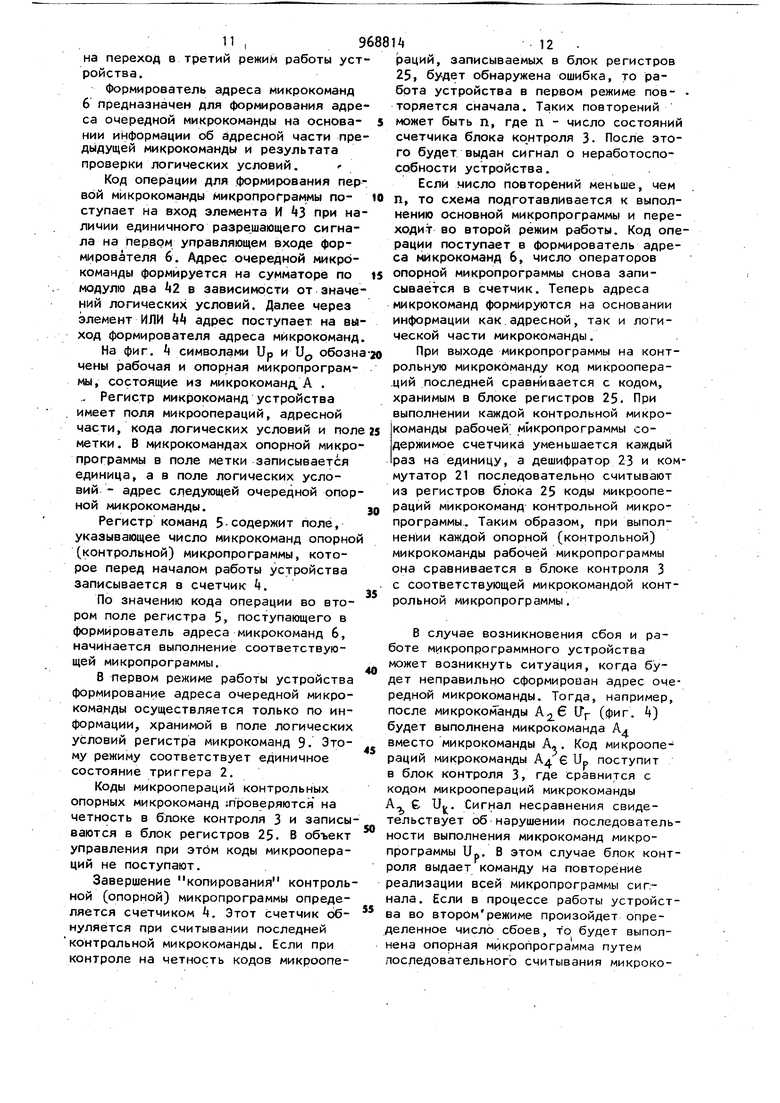

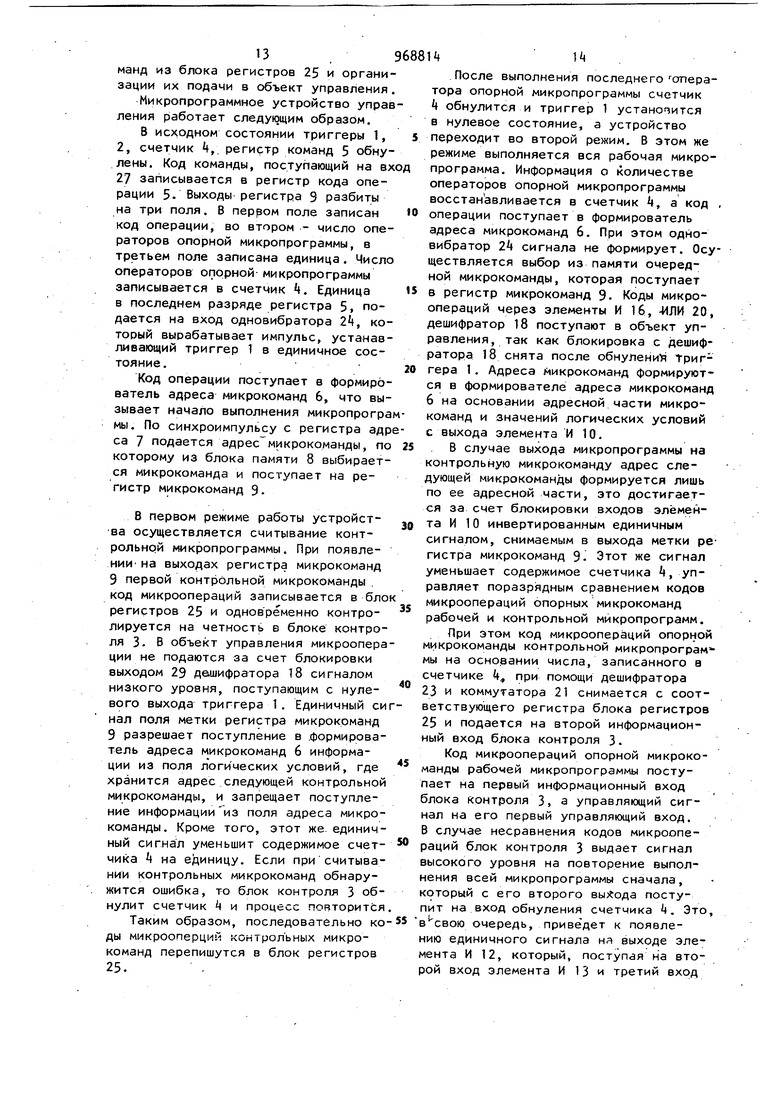

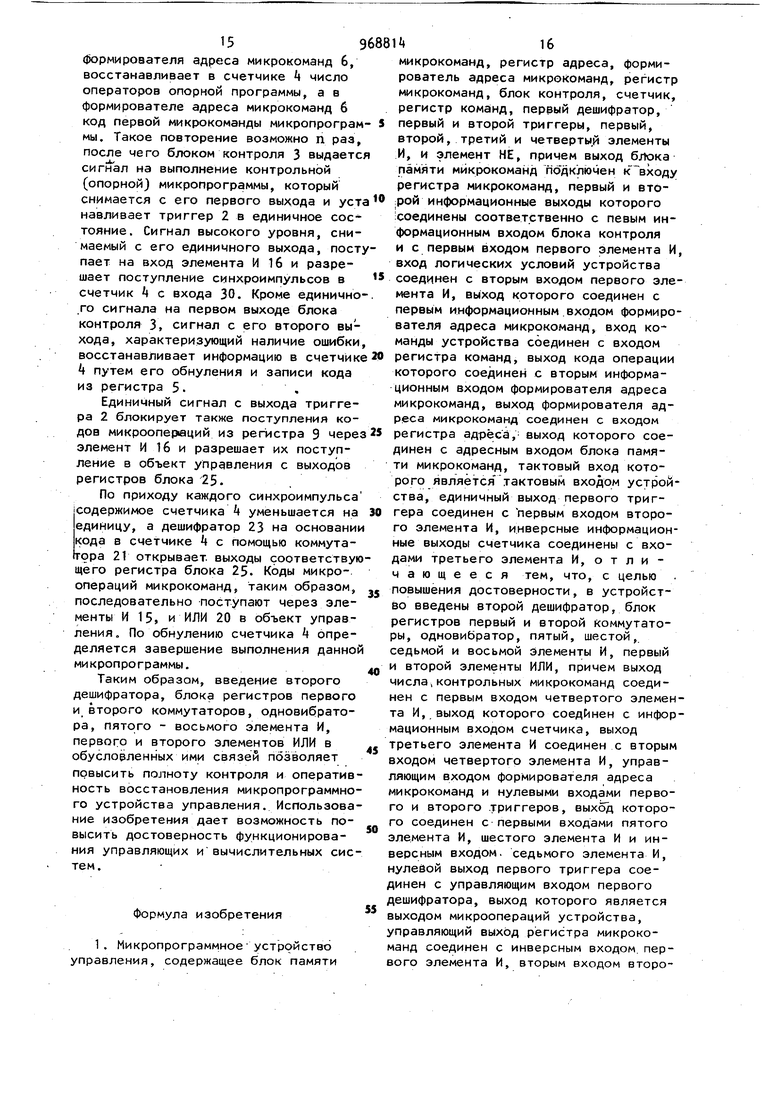

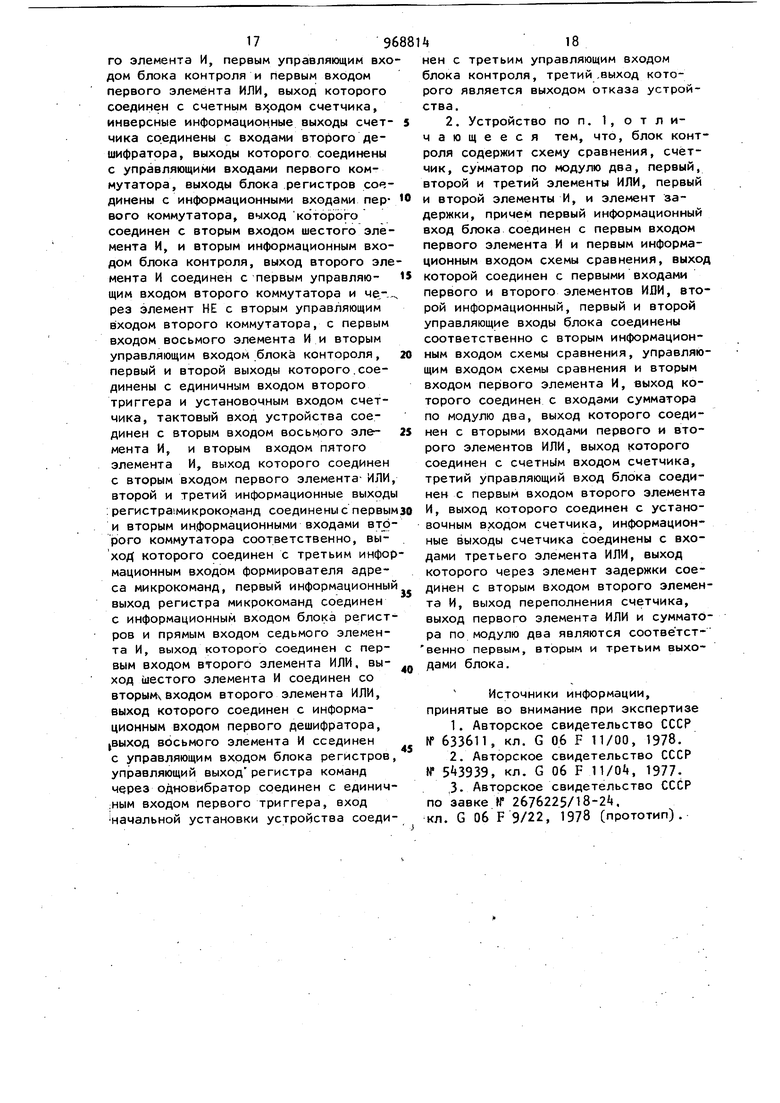

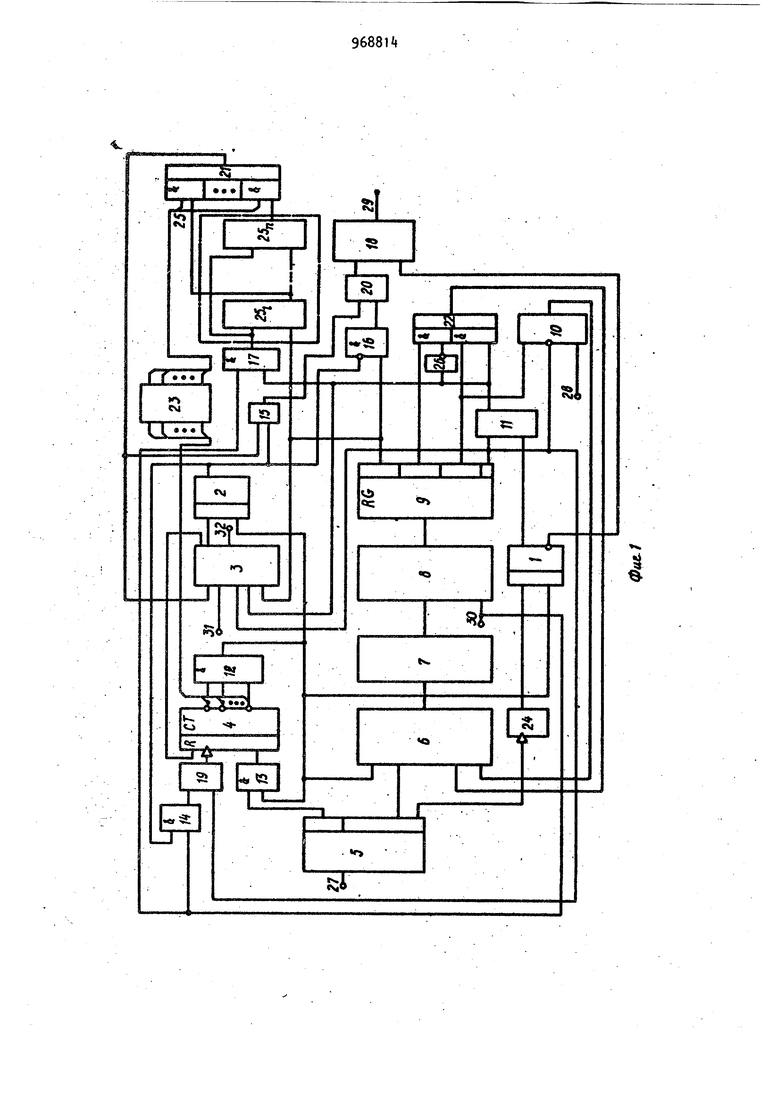

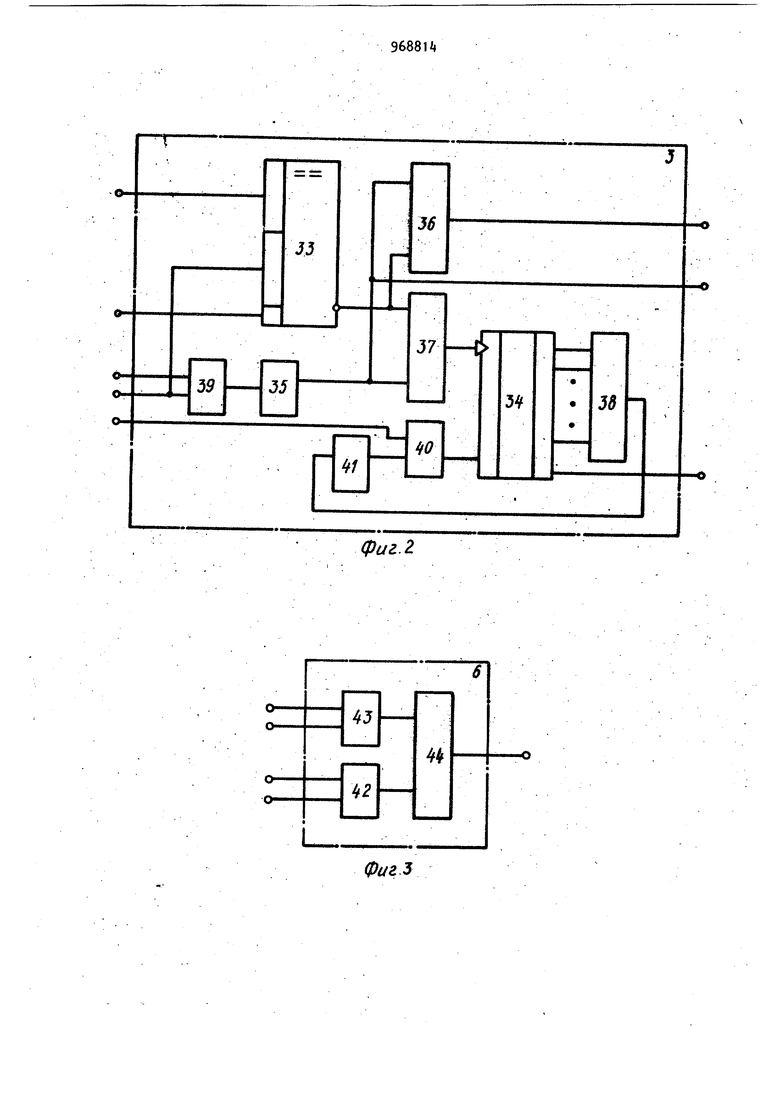

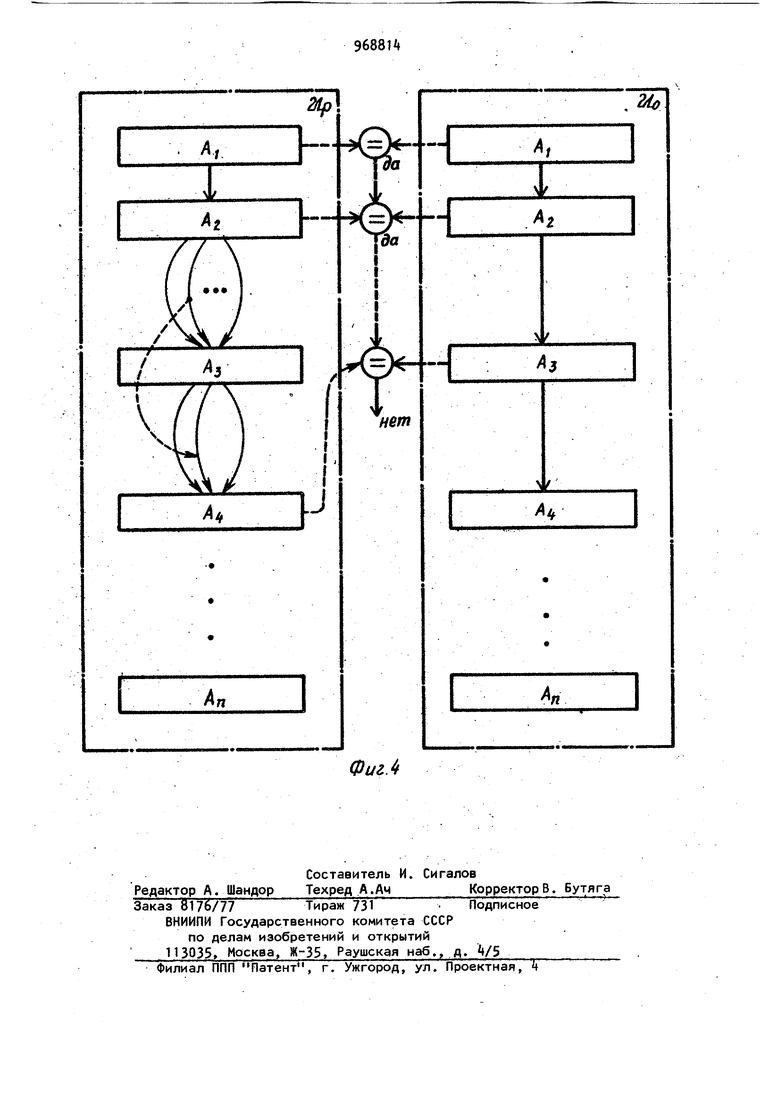

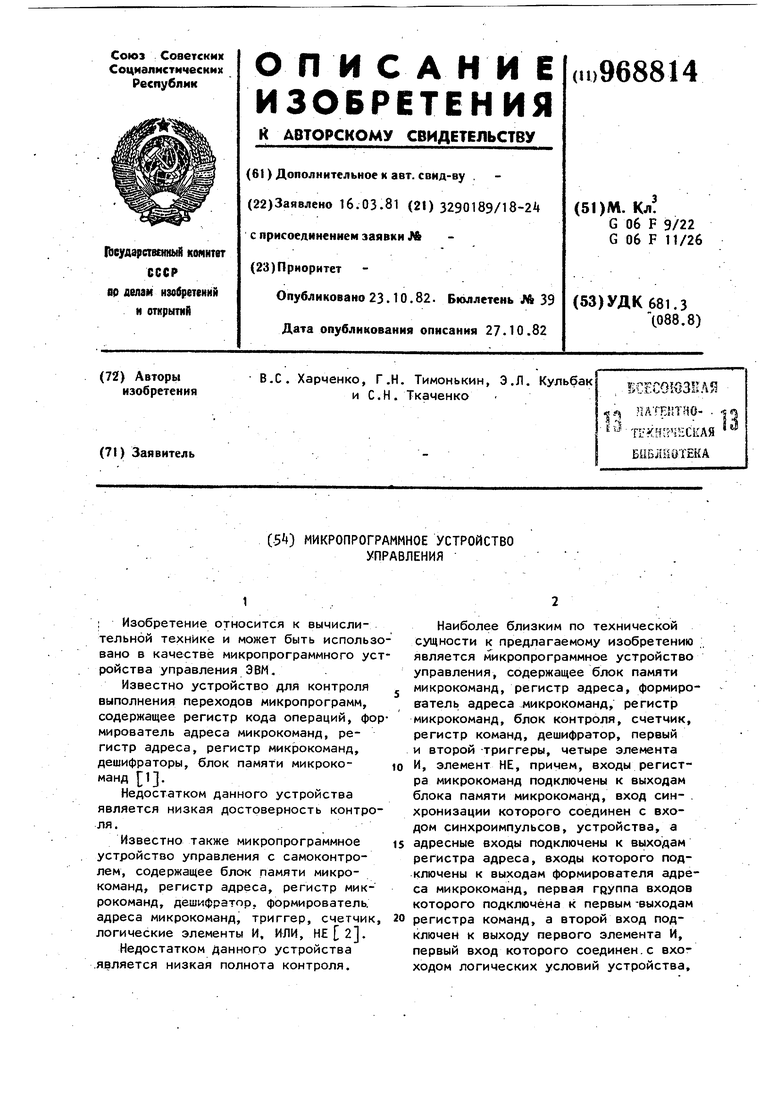

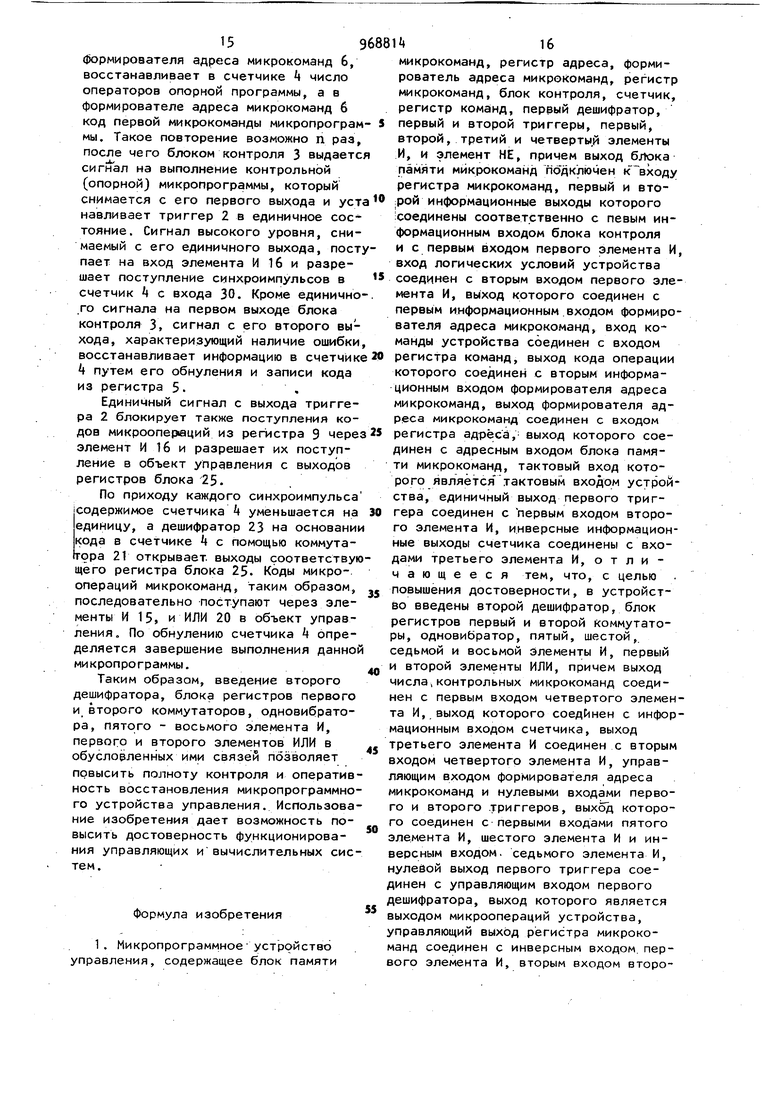

1. .. ; Изобретение относится к вычислительной технике и может быть использ вано в качестве микропрограммного ус ройства управления ЭВМ. Известно устройство для контроля выполнения переходов микропрограмм, содержащее регистр кода операций, фо мирователь адреса микрокоманд, регистр адреса, регистр микрокоманд, дешифраторы, блок памяти микрокоманд р. Недостатком данного устройства является низкая достоверность контро ля. Известно также микропрограммное устройство управления с самоконтролем, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, дешифратор, формирователь, адреса микрокоманд, триггер, счетчик логические элементы И, ИЛИ, . Недостатком данного устройства .является низкая полнота контроля. Наиболее близким по технической сущности к предлагаемому изобретению является микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, формирователь адреса микрокоманд, регистр микрокоманд, блок контроля, счетчик, регистр команд, дешифратор, первый и второй триггеры, четыре элемента И, элемент НЕ, причем, входы регистра микрокоманд подключены к выходам блока памяти микрокоманд, вход син- . хронизации которого соединен с входом синхроимпульсов, устройства, а адресные входы подключены к выходам регистра адреса, входы которого подключены к выходам формирователя адреса микрокоманд, первая гйУппа входов которого подключена к первым -выходам регистра команд, а второй вход подключен к выходу первого элемента И, первый вход которого соединен.с вхоходом логических условий устройства. а второй вход подключен к первому выходу регистра микрокоманд; единичный выход первого триггера подключен к первому входу второго элемента И, . второй выход регистра микрокоманд подключен к первому.входу блока конт роля, выходы счетчика соединены со входами третьего элемента И З. Недостатками данного устройства являются низкий коэффициент испольэо вания средств контроля. В извectнoм. не реализована возможность использо.вания одних и тех же аппаратных средств как для контроля так и для хранения, восстановления и выполнени укороченной (опорной) микропрограммы в случае невозможности реализации всей микропрограммы. Отсутствие возможности автоматического восстановле ния информации устройством, приводит к низкой оперативности восстановления а, следовательно и к его низкой функциональной надежности. Недостатком является и низкая полнота контроля. В данном устройстве контроль осуществ ляется . путём сканирования всех микрокоманд различных хранимых микропрограмм, подряд, а не избирательной проверки наиболее важных (опорных) операторов, которые в микропрограмме выполняются всегда, и переходов между ними. Низкая достоверность функционирования. Этот недостаток обусловлен тем что в известном не осуществляется контроль в процессе функционирования, а производится только профилактический контроль в режимах ожидания. Сбои возникающие в процессе выполнения микропрограммы данным устройством, не обнаруживаются. Указанные недостатки существенно снижают достоверность работы известного и сужают область его применения 1 , Целью изобретения является повышение достоверности функционирования устройства. Поставленная.цель достигается тем что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, формирователь адреса мик)окоманд, регистр микрокоманд, блок контроля, счетчик, регистр команд, первый дешифратор, пе;рвый и второй триггеры, первый, второй, третий и четвертый элементы И и элемент НЕ, причем выход блока памяти микрокоманд подключен к входу регистра микрокоманд, первый и второй информационные выходы которого соединены соответственно с первым информационным входом блока контроля и с первым входом первого элемента И, . вход логических условий устройства соединен с вторым входом первого, элемента И, выход которого соединен с первым информационным входом формирователя адреса микрокоманд, вход команды устройства соединен с входом регистра команд, выход кода операции которого соединен с вторым информационным входом формирователя адреса микрокоманд, выход формирователя адреса /микрокоманд соединен с входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, тактовый вход которого является тактовым входом :устройства, единичный выход первого триггера соединен с первым входом второго элемента И, инверсные информационные выходы счетчика соединены с входами третьего элемента И, дополните 1ьно введены второй дешифратор, блок регистров, первый и второй коммутаторы, одновибратор, пятый, шестой, седьмой и восьмой элементы И, первый и второй элементы ИЛИ, причем выход числа контрольных микрокоманд соединен с первым входом четвертого элемента И, выход которого соединен с информационным входом счетчика, выход третьего элемента И соединен со вторым входом четвертого элемента И, управляющим входом формирователя адреса микрокоманд и нулевыми входами первого и второго триггеров, выход которого соедине1Н с первыми входами пятого элемента И, шестого элемента И и инверсным входом седьмого элемента И, нулевой выход первого триггера соединен с управляющим входом первого дешифратора, выход которого является выходом микрокоопераций устройства, управляющий выхрд регистра микрокоманд соединен с инверсным входом первого элемента И, вторым входом второго элемента И, первым управляющим входом блока контроля и первым входом первого элемента ИЛИ, выход которого соединён со счетным входом счетчика, инверсные информационные выходы счетчика соединены с входами второго дешифратора, выходы которого соединены с управляющими входами первого коммутатора, выходы блока регистров соединены с информационными входами первого коммутатора, выход которого соединен с вторым входом шестого эле мента И и вторым входом шестого элемента И и вторым информационным входом блока контроля, выход второго элемента И соединен с первым управляющим входом второго коммутатора и через элемент НЕ со вторым управляющим входом второго коммутатора, с первым входом восьмого элемента И и вторым управляющим входом блока контроля, первый и второй выходы которого соединены с единичным входом второго триггера и установочным входом счетчика, тактовый вход устройст ва соединен с вторым входом восьмого элемента И и вторым входом пятого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ второй и третий информационные выход регистра микрокоманд соединены с пер вым и вторым, информационными входами второго коммутатора соответственно, выход которого соединен с третьи информационным входом формирователя адреса микрокоманд, первый информа-ционный выход регистра микрокоманд соединен с информационным входом блока регистров и прямым входом седь мого элемента И, выход которого соединен с первым входом второго элемен та ИЛИ, выход шестого элемента И сое динен с вторым выходом второго элемента ИЛИ, выход которого соединен с информационным входом первого дешифратора, выход восьмого элемента И соединен с управляющим входом блок регистров, управляющий выход регистра команд через одновибратор соединен с единичным входом первого триггера, вход начальной установкиустрой ства соединен с третьим управляющим входом блока контроля, третий выход которого является выходом отказа уст ройства. Кроме того, блок контроля содержит схему сравнения, счетчик, сумматор по модулю два, первый, второй и третий элементы ИЛИ, первый и второй элементы И и элемент задержки, приче первый информационный вход блока сое динен с первым входом первого элемен та И и первым информационным входом схемы сравнения, выход которой соединен с первыми входами первого и второго элементов ИЛИ, второй информационный, первый и второй управляющие входы блока соединены соответственно с вторым информационным входом схемы сравнения, управляющим входом схемы сравнения и вторым .входом первого элемента И, выход которого соединен с входами сумматора по модулю два, выход которого соединен с вторыми входами первого и второго элементов ИЛИ, выход которого соединен со счетным входом счетчика, третий управляющий вход блока соединен с первым входом второго элемента И, выход которого соединен с установочным входом счетчика, информационные выходы счетчика соединены с входами третьего элемента ИЛИ, выход которого через элемент задержки соединен со вторым входом второго элемента И, выход переполнения счетчика, выход первого элемента ИЛИ и сумматора по модулю два является соответственно первым, вторым и третьим выходами блока. Предлагаемоеустройство обеспечивает:а)повышение полноты и оперативности контроля путем организации проверки правильности выполнения микрокоманд, обязательно встречающихся в реализуемой микропрограмме (опорных микрокоманд) и переходов между ними; б)повышение коэффициента использования средств контроля за счет организации восстановления путем реа- лизации опорной микропрограммы с помощью хранимой в этих средствах ин-, формации; в)повышение оперативности.восстановления путем автоматической реконфигурации структуры и реализации укороченной (опорной) микропрограммы. В работе микропрограммного устройства управления можно выделить три режима. В первом режиме работы устройства осуществляется копирование опорной микропрограммы (режим копирования). Последовательность микрокоманд, образующих эту микропрограмму, задается адресами, записанными в с.во бодном поле логических условий. Коды : микроопераций этих контрольных микрокоманд запоминаются в порядке их выполнения. Кроме того, проверяется правильность копирования кодов микроопераций этих микрокоманд. Во втором режиме работы устройства происходит выполнение всей рабочей микропрограммы (основной режим). При этом контролируется правильность и требуемый порядок следования микрокоманд рабочей микропрограммы путем сравнений ее с опорной микропрограммой. 79 Если будет определено, что вся рабочая микропрограмма не может быть выполнена, то устройство переходит в третий режим работы. В третьем режиме работы устройства (режиме восстановления) вместо рабочей (1олной) микропрограммы выпрл няется укороченная рабочая (опорная) микропрограмма, полученная в первом режиме его работы. Введение второго дешифратора и пер вого коммутатора и соединение входов второго дешифратора с выходами счетчика, выходов - с управляющими входами коммутатора, а его информационных входов с выходами блока регистров необходимо для считывания кодов микро операций микрокоманд опорной (контрольной) микропрограммы из блока регистров в соответствии с числом, записанным в сметчике. Введение восьмого элемента И и соединение его второго входа с тактовым входом устройства, первого входа с выходом второго элемента И, а вы хода-- с управляющими входами бло арегистров необходимо для организации последовательной записи кодов микроопераций контрольных микрокоманд в первом режиме работы устройства. Введение блока регистров позволяет хранить коды микроопераций опорных (контрольных) микрокоманд. Коды микро операций этих микрокоманд записываются в его регистрах в порядке их выпоя нения в рабочей микропрограмме. Соединение первого выхода коммутатора со вторым информационным входом блока контроля необходимо для подачи кодов микроопераций микрокоманд контрольной микропрограммы во втором режиме. Введение шестого элемента И и второго элемента ИЛИ и соединение второго входа шестого элемента И с выходом первого коммутатора, первого входа с единичным выходом второго триггера, а выхода с вторым входом второго элемента ИЛИ и подключение выхода последнего к-информационному входу первого дешифратора необходимо для выдачи кодов микроопераций микрокоманд контрольной микропрограммы в тре тьем режиме работы устройства. Введение седьмого элемента И и сое динение его инверсного входа с единичным выходом второго триггера, прямого входа с первым информационным выходом регистра микрокоманд, а выUхода - с первым входом второго элемен та ИЛИ необходимо для блокировки поступления кодов микроопераций, образующих .Цйабрчую микропрограмму, в третьем режиме работы устройства. Соединение управляющего входа первого дешифратора с нулевым выходом первого триггера необходимо для запрещения выдачи в объект управления кодов Микроопераций контрольных микрокоманд в первом режиме работы устройства. Введение второго коммутатора и обусловленных им связей необходимо для организации формирования адреса последующей микрокоманды по адресной части, записанной в поле адреса микрокоманды во втором режиме и.поле логических условий - в первом режиме работы устройства. Соединение управляющего выхода регистра микрокоманд с вторым входом второго элемента И, а его выхода с вторым управляющим входом блока контроля необходимо для идентификации контрольных микрокоманд в первом режиме работы устройства. Соединение, управляющего выхода регистра микрокоманд с первым управляющим входом блока контроля необходимо для выдачи сигнала сравнения кодов микроопераций опорных микрокоманд рабочей и контрольной микропрограммы. Введение одновибратора и обусловленных им связей необходимо для формирования сигнала установки первого режима работы устройства. Соединение нулевого входа первого триггера с выходом третьего элемента И необходимо для формирования сигнала установки второго режима работы устройства. Соединение второго выхода блока |Сонтроля с установочным входом счетника, а также соединение выхода третьего элемента И с управляющим входом формирователя адреса микрокоманды и вторым входом четвертого элемента И необходимо для восстановления информации о количестве микрокоманд опорной микропрограммы в счетчике и кода операции в формирователе адреса микрокоманд после обнаружения сбоя в первом и втором режимах работы устройства. Введение первого элемента ИЛИ и соединение его выхода со счетным входом счетчика необходимо для подсчета 99 в процессе работы устройствп числа контрольных микрокоманд. Соединение первого выхода блока контроля с единичным входом второго триггера необходимо для перевода уст ройства в третий режим работы. Таким образом, введение указанных новмх элeмeнtoв и обусловленных ими связей позволяет путем копирования опорной микропрограммы, сравнения ее с рабочей микропрограммой и выполнения опорной микропрограммы при отказе элементов, обеспечивающих выполнение рабочей микропрограммы, сущест венно повысить оперативность контрол и восстановления, увеличить коэффициент использования средств и полноту контроля. На фиг. 1, представлена .функциональная схема предлагаемого микропро граммного устройства управления само контролем и восстановлением; на фиг. 2 и 3 функциональные схемы бл ка контроля и формирователя адреса. |микрокоманд, соответственно; на ;фиг. Ц - пример выполнения рабочей и |контрольной микропрограммы, ; Микропрограммное устройство содер жит первый 1 и второй 2 триггеры соответственно, блок 3 контроля, счетчик А, регистр команд 5, формирователь 6 адреса микрокоманд, регистр 7 адреса микрокоманд, блок памяти 8 микрокоманд, регистр 9 микрокоманд, первый - восьмой элементы И 10-17 соответственно, первый дешифратор 18 первый 19 и второй 20 элементы ИЛИ соответственно, первый 21 и второй 2 коммутаторы, второй дешифратор 23, одновибратор 24, блок регистров 25 СОСТОЯЩИЙ из регистров 25 , элемент НЕ 26, вход 27 команд, вход 28 логических условий, выход 29 кода ми роопераций, тактовый вход 30, вход 31 начальной установки, выход 32 отк за устройства. Функциональная схема блока К9нтро ля. (фиг. 2) содержит схему сравнения 33, счетчик З, сумматор по модулю два 35, первый 36, второй 37 и третий 38 элементы ИЛИ, первый 39 и второй ЦО элементы И, элемент задержки А1. На функциональной схеме формирователя адреса микрокоманд (фиг. 3) символами обозначены: сумматор по мо дулю два 2, элемент И 3 элемент ИЛ Itk, Блок контроля 3 предназначен для контроля записываемых в блок регистiров кодов микроопераций контрольных микрокоманд в первом режиме работы устройства. Сигнал подается на второй управляющий вход блока контроля, а код микрооперации контрольной микрокоманды поступает на его первый информационный вход и далее через элемент И 39 на сумматор по модулю два 35. При наличии ошибки в коде (нечетном числе единиц) , с выхода сумматора по модулю два 35 сигнал высокого уровня поступит в счетчик 3, где подсчитывается число сбоев, произошедших в устройстве в первом режиме его работы; на первый выход блока контроля и выход для установки схемы в исходное состояниеи перевода устройства в первый режим работы. Если после h повторений ошибка не самоустраняется; то с выхода переполнения счетчика 3 сигнал поступит на первый выход блока контроля и будет сформирован признак отказа устройства. Если первый режим работы закончится без сбоев или с числом сбоев меньше п, то через некоторое время на вход элемента И ЧО поступит си1- нал начальной установки с таймера и обнулит счетчик . Таким образом, к второму режиму в счетчике 3 будет записан нулевой код. Блок контроля 3 предназначен и для контроля правильности выполнения опорных микрокоманд рабочей микропрограммы в заданной последовательности во втором режиме работы устройства. Сигнал поступает на первый управляющий вход блока контроля, а коды микроопераций опорных микрокоманд контрольной и рабочей микропрограммы подаются соответственно на второй и первый информационные входы. С случае неравенства кодов микропераций опорных микрокоманд рабочей И контрольной микропрограмм с выхода схемы сравнения 33 будет выдан си нал высокого уровня, который поступит в счетчик З для подсчета числа несравнёний, произошедших в .устройстве во втором режиме его работы, на второй выход блока контроля для установки схемы в исходное состояние и повторения второго режима работы устройства. Если после п повторений ошибка не устраняется, то с выхода переполнения счетчика на первый выходблока контроля 3 поступит единичный сигнал на переход в третий режим работы уст ройства. Формирователь адреса микрокоманд 6 предназначен для формирования адре са очередной микрокоманды на основаНИИ ийформации об адресной части пре дыдущей микрокоманды и результата проверки логических условий. Код операции для формирования пер вой микрокоманды Микропрограммы поступает на вход элемента И 3 при на личии единичного разрешающего сигнала на первом управляющем входе формирователя 6. Адрес очередной микрокоманды формируется на сумматоре по модулю два k2 в зависимости от значе ний логических условий. Далее через элемент ИЛИ 4 адрес поступает на вы ход формирователя адреса микрокоманд На фиг. Ц символами Up и U, обозн чены рабочая и опорная микропрограммы, состоящие из микрокоманд, А . . Регистр микрокоманд устройства имеет поля микроопераций, адресной части, кода логических условий и пол метки. В микрокомандах опорной микро программы в поле метки записывается единица, а в поле логических условий - адрес следующей очередной опор ной микрокоманды. Регистр команд 5-содержит поле, указывающее число микрокоманд опорно (контрольной) микропрограммы, которое перед началом работы устройства записывается в счетчик k, По значению кода операции во втором поле регистра 5, поступающего в формирователь адреса микрокоманд 6, начинается выполнение соответствующей микропрограммы. В первом режиме работы устройства формирование адреса очередной микрокоманды осуществляется только по информации, хранимой в поле логических условий регистра микрокоманд 9. Этому режиму соответствует единичное состояние триггера 2, Коды микроопераций контрольных опорных микрокоманд ;п|эоверяются на четность в блоке контроля 3 и записываются в блок регистров 25. В объект управления при этбм коды микроопераций не поступают. Завершение копирования контрольной (опорной) микропрограммы определяется счетчиком Ц, Этот счетчик обнуляется при считывании последней контрольной микрокоманды. Если при контроле на четность кодов микроопераций, записываемых в блок регистров 25, будет обнаружена ошибка, то работа устройства в первом режиме пов- . торяется сначала. Таких повторений может быть п, где п - число состояний счетчика блока контроля 3. После этого будет выдан сигнал о неработоспособности устройства. Если нисло повторений меньше, чем п, то схема подготавливается к выполнению основной микропрограммы и переходит во второй режим работы. Код операции поступает в формирователь адреса микрокоманд 6, число операторов опорной микропрограммы снова записывается в счетчик. Теперь адреса микрокоманд формируются на основании информации как.адресной, так и логической части микрокоманды. При выходе микропрограммы на контрольную микрокоманду код микроопера,ций последней сравнивается с кодом, хранимым в блоке регистров 25. При выполнении каждой контрольной микрокоманды рабочей микропрограммы содержимое счетчика уменьшается каждый раз на единицу, а дешифратор 23 и коммутатор 21 последовательно считывают из регистров блока 25 коды микроопераций микрокоманд контрольной микропрограммы. Таким образом, при выполнении каждой опорной (контрольной) микрокоманды рабочей микропрограммы она сравнивается в блоке контроля 3 с соответствующей микрокомандой контрольной микропрограммы. В случае возникновения сбоя и работе микропрограммного устройства может возникнуть ситуация, когда будет неправильно сформирован адрес очередной микрокоманды. Тогда, например, после микрокоманды U (фиг. 4) будет выполнена микрокоманда Ах вместо микрокоманды А,. Код микроопераций микрокоманды А € Up поступит в блок контроля 3, где сравнится с кодом микроопераций микрокоманды , Uo. Сигнал несравнения свидетельствует об нарушении последовательности выполнения микрокоманд микропрограммы Up. В этом случае блок контроля выдает команду на повторение реализации всей микропрограммы сигнала. Если в процессе работы устройства во вторОмрежиме произойдет определенное число сбоев, то будет выполнена опорная микропрограмма путем последовательного считывания микрокоманд из блока регистров 25 и организации их подачи в объект управления. Микропрограммное устройство управ ления работает следунзщим образом. В исходном состоянии триггеры 1, 2, счетчик 4/. регистр команд 5 обнулены. Код команды, поступающий на вх 27 записывается в регистр кода операции 5. Выходы регистра 3 разбиты на три поля. В перром поле записан код операции, во втором - число операторов опорной микропрограммы, в третьем поле записана единица. Число операторов опорной микропрограммы записывается в счетчик . Единица в последнем разряде регистра 5, подается на вход одновибратора 24, который вырабатывает импульс, устанавливающий триггер 1 в единичное состояние. Код операции поступает в формирователь адреса микрокоманд 6, что вызывает начало выполнения микропрогра мы. По синхроимпульсу с регистра адр са 7 подается адрес микрокоманды, по которому из блока памяти 8 выбирается микрокоманда и поступает на регистр микрокоманд 9. В первом режиме работы устройства осуществляется считывание контрольнрй микропрограммы. При появлении на выходах регистра микрокоманд 9 первой контрольной микрокоманды , код микроопераций записывается в бло регистров 25 и одновременно контролируется на четность в блоке контроля 3. В объект управления микроопера ции не подаются за счет блокировки выходом 29 дешифратора 18 сигналом низкого уровня, поступающим с нулевого выхода триггера 1. Единичный си нал поля метки регистра микрокоманд 9 разрешает поступление в .формирователь адреса микрокоманд 6 информации из поля логических условий, где хранится адрес следующей контрольной микрокоманды, и запрещает поступление информациииз поля адреса микрокоманды. Кроме того, этот же. единичный сигнал уменьшит содержимое счетчика t на единицу. Если при считывании контрольных микрокоманд обнаружится ошибка, то блок контроля 3 обнулит счетчик k и процесс повторится Таким образом, последовательно ко ды микрооперций контрольных микрокоманд перепишутся в блок регистров 25. .После выполнения последнего оператора опорной микропрограммы счетчик k обнулится и триггер 1 установится в нулевое состояние, а устройство переходит во второй режим. В этом же режиме выполняется вся рабочая микропрограмма. Информация о количестве операторов опорной микропрограммы восстанавливается в счетчик , а код , операции поступает в формирователь адреса микрокоманд 6. При этом одновибратор 2Ц сигнала не формирует. Осуществляется выбор из памяти очередной микрокоманды, которая поступает в регистр микрокоманд 9. Коды микроопераций через элементы И 16, -ИЛИ 20, дешифратор 18 поступают в объект управления, так как блокировка с дешифратора 18 снята после обнулений Триггера 1 . Адреса 1икрокомаид формируются в формирователе адреса микрокоманд 6 на основании адресной части микрокоманд и значений логических условий с выхода элемента И 10. В случае выхода микропрограммы на контрольную микрокоманду адрес следующей микрокоманды формируется лишь по ее адресной части, это достигается за счет блокировки входов элемента И 1 О инвертированным единичным сигналом, снимаемым в выхода метки регистра микрокоманд 9. Этот же сигнал уменьшает содержимое счетчика l, управляет поразрядным сравнением кодов микроопераций опорных микрокоманд рабочей и контрольной микропрограмм. При этом код микроопераций опорной микрокоманды контрольной микропрограмммы на основании числа, записанного в счетчике i, при помощи дешифратора 23 и коммутатора 21 снимается с соответствующего регистра блока регистров 25 и подается на второй информационный вход блока контроля 3. Код микроопераций опорной микрокоманды рабочей микропрограммы поступает на первый информационный вход блока контроля 3, а управляющий си1- нал на его первый управляющий вход. В случае несравнения кодов микроопераций блок контроля 3 выдает сигнал высокого уровня на повторение выполнения всей микропрограммы сначала, который с его второго вы)ода поступит на вход обнуления счетчика Ц. Это, в свою очередь, приведет к появлению единичного сигнала на выходе элемента И 12, который, поступая на второй вход элемента И 13 и третий вход формирователя адреса микрокоманд 6, восстанавливает в счетчике 4 число операторов опорной программы, а в формирователе адреса микрокоманд 6 код первой микрокоманды микропрограм мы. Такое повторение возможно п раз, после 46 го блоком контроля 3 выдается сигнал на выполнение контрольной (опорнойJ микропрограммы, который снимается с его первого выхода и уста навливает триггер 2 в единичное состояние. Сигнал высокого уровня, снимаемый с его единичного выхода, посту пает на вход элемента И 16 и разрешает поступление синхроимпульсов в счетчик с входа 30. Кроме единичного сигнала на первом выходе блока контроля 3, сигнал с его второго выхода, характеризующий наличие ошибки. восстанавливает информацию в счетчик путем его обнуления и записи кода из регистра 5., Единичный сигнал с выхода триггера 2 блокирует также поступления кодов микроопераций иэ регистра 9 чере элемент И 16 и разрешает их поступление в объект управления с выходов регистров блока 25. По приходу каждого синхроимпульса содержимое счетчика Ц уменьшается на единицу, а дешифратор 23 на основани кода в счетчике Ц с помощью коммутатора 21 открывает, выходы соответствую щего регистра блока 25. Коды микроопераций микрокоманд, таким образом, последовательно поступают через элементы И 15, и ИЛИ 20 в объект управления. По обнулению счетчика k определяется завершение выполнения данно микропрограммы. Таким образом, введение второго дешифратора, блока регистров первого и второго коммутаторов, одновибратора, пятого - восьмого элемента И, первого и второго элементов ИЛИ в обусловленных ими связей позволяет повысить полноту контроля и оператив ность восстановления микропрограммно го устройства управления. Использова ние изобретения дает возможность повысить достоверность функционирования управляющих и вычислительных сис тем. Формула изобретения 1. Микропрограммное-устройство управления, содержащее блок памяти микрокоманд, регистр адреса, формирователь адреса микрокоманд, регистр микрокоманд, блок контроля, счетчик, регистр команд, перэый дешифратор, первый и второй триггеры, первый, второй, третий и четверты.й элементы И, и элемент НЕ, причем выход блока пам;яти микрокоманд подключен к входу регистра микрокоманд, первый и вто:рой информационные выходы которого соединены соответственно с певым информационным входом блока контроля и с первым входом первого элемента И, вход логических условий устройства соединен с вторым входом первого элемента И, выход которого соединен с первым информационным входом формирователя адреса микрокоманд, вход команды устройства соединен с входом регистра команд, выход кода операции которого соединен с вторым информационным входом формирователя адреса микрокоманд, выход формирователя адреса микрокоманд соединен с входом регистра адреса,- выход которого соединен с адресным входом блока памяти микрокоманд, тактовый вход которого является тактовым входом устройства, единичный выход первого триггера соединен с первым входом второго элемента И, инверсные информационные выходы счетчика соединены с входами третьего элемента И, о т л и чающееся тем, что, с целью повышения достоверности, в устройство введены второй дешифратор, блок регистров первый и второй коммутаторы, одновиЬратор, пятый, шестой, седьмой и восьмой Злементы И, первый и второй элементы ИЛИ, причем выход числа,контрольных микрокоманд соединен с первым входом четвертого элемента И, выход которого соединен с информационным входом счетчика, выход третьего элемента И соединен с вторым входом четвертого элемента И, управляющим входом формирователя адреса микрокоманд и нулевыми входами первого и второго триггеров, выход которого соединен с первыми входами пятого элемента И, шестого элемента И и инверсным входом, седьмого элемента И, нулевой выход первого триггера соединен с управляющим входом первого дешифратора, выход которого является выходом микроопераций устройства, управляющий выход регистра микрокоманд соединен с инверсным входом, первого элемента И, вторым входом второ179го элемента И, первым управляющим вхо дом блока контроля и первым входом первого элемента ИЛИ, выход которого соединен с счетным счетчика, инверсные информационные выходы счетчика соединены с входами второго дешифратора, выходы которого соединены с управляющими входами первого коммутатора, выходы блока регистров соединены с информационными входами первого коммутатора, вчход которого соединен с вторым входом шестого элемента И, и вторым информационным входом блока контроля, выход второго эле мента И соединен с первым управляющим входом второго коммутатора и че,рез элемент НЕ с вторым управляющим входом второго коммутатора, с первым входом восьмого элемента И и вторым управляющим входом блока контороля, первый и второй выходы которого.соединены с единичным входом второго триггера и установочным входом счетчика, тактовый вход устройства соединен с вторым входом восьмого элемента И, и вторым входом пятого элемента И, выход которого соединен с вторым входом первого элемента- ИЛИ второй и третий информационные выходы ; регистра1микрокоманд соединены с первым и вторым информационными входами вто рого коммутатора соответственно, выход которого соединен с третьим инфор мационным входом формирователя адреса микрокоманд, первый информационный выход регистра микрокоманд соединен с информационным входом блока регист ров и прямым входом седьмого элемента И, выход которого соединен с первым входом второгсэ элемента ИЛИ, выход iuecToro элемента И соединен со вторымчвходом второго элемента ИЛИ, выход которого соединен с информационным входом первого дешифратора, |выход восьмого элемента И ееединен с управляющим входом блока регистров управляющий выходрегистра команд через одновибратор соединен с единич;ным входом первого триггера, вход начальной установки устройства соедиС третьим управляющим входом нем блока контроля, третий .выход которого является выходом отказа устройства. 2. Устройство по п, 1, отличающееся тем, что, блок контроля содержит схему сравнения, счётчик, сумматор по модулю два, первый, второй и третий элементы ИЛИ, первый и второй элементы И, и элемент задержки, причем первый информационный вход блока соединен с первым входом первого элемента И и первым информационным входом схемы сравнения, выход которой соединен с первыми входами первого и второго элементов ИЛИ, второй информационный, первый и второй управляющие входы блока соединены соответственно с вторым информационным входом схемы сравнения, управляющим входом схемы сравнения и вторым входом первого элемента И, выход которого соединен с входами сумматора по модулю два, выход которого соединен с вторыми входами первого и второго элементов ИЛИ, выход которого соединен с счетным входом счетчика, третий управляющий вход блока соединен с первым входом второго элемента И, выход которого соединен с установочным входом счетчика, информационные выходы счетчика соединены с входами третьего элемента ИЛИ, выход которого через элемент задержки соединен с вторым входом второго элемента И, выход переполнения счетчика, выход первого элемента ИЛИ и сумматора по модулю два являются соответствеино первым, вторым и третьим выходами блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 633611, кл. G 06 F 11/00, 1978. 2.Авторское свидетельство СССР N , кл. G 06 F 11/0, 1977. ,3- Авторское свидетельство СССР по завке Г 2676225/18-2, кл. G Об F 9/22, 1978 (прототип).

59

25

5d

3-

4фиг. 2

ФигЗ

A,

А„

Лп

, 2

1 I

Js

AS

нет

A

n

ФигЛ