ментов И, выход первого блока элементов И подключен к второму входу первого блока элементов ИЛИ, выход второго блока элементов, И подключен к адресному вход блока управляющей памяти, выход третьего блока элементов И подключен к входу второго буферного регистра, выход кото-; рого соединен с первым входом четвертой го блока элементов И, йыход которого соединен с входом третьего буферного регистра, выход которого соединен с первым входом пятого блока элементов И, . выход которого соединен с вторым выходом второго блока элементов ИЛИ, четвертый и пятый выходы блока контроля соединены соответственно с вторым и третьим входами блока управления, восьмой выход которого соединен с вторым входом четвертого блока элементов И и через элемент задержки - с вторым входом третьего блока элементов И, девятый выход блока управления соединен с вто - г рыми входами первого и пятого блоков элементов И и с инверсным входом второго блока элементов И, первый и десятый выходы блока управления соединены с первым и вторым входами элемента ИЛИ вьрсод которого соединен с вторым входом второго блока элементов И, одиннадцатый, третий, шестой и пятый выходы блока управления соединены с первым, вторым, третьим и четвертым управляющими входами блока контроля,, первый, второй, третий, четвертый и пятый управляющие входы устройства соединены соответственно с четвертым, пятым, шестым, седьмым и восьмым входами блока управления.

2. Устройство по п. 1,отличаю:Щ ее с я тем, что блок управления содержит триггер режима, девять элементов И, три элемента задержки, четыре элемента ИЛИ, счетчик и дешифратор, первый выход которого соединен с девятым выходом блокауправления и с первым входом первого элемента ИЛИ, выход которого соединен с седшым выходом блока управления, второй выход дешифратора соединен с вторым входом первого элемента ИЛИ, третий выход дешифратора соединен с первым входом первого элемента И, выход которого соединен с пятым выходом блока управления, четвертый выход дешифратора через второй и третий элементы ИЛИ соединен соответственнос и третьим выходами блока управления, пятый выход дешифратора соединен с первым инверсным входом второго элемента И и с первым входом третьего элемента И, выхоц которого соединен с первым.

входом четвертого элемента ИЛИ, выход которого соединен с динамическим входом счетчика, выходы которого соединены с входами дешифратора, третий вход блока управления соединен с вторым инверсным входом второго элемента И и с первым входом четвертого элемента И, выхог которого соединен с вторым входом четвертого элемента ИЛИ, пятый вход блока управления соединен с вторым входами третьего и четвертого элементов И и с первым прямым входом второго элемента И, выход которого соединен с шестым выходом блока управления, через первый элемент задержки с первым входом пятого элемента И, выход которого соединен с вторым выходом блока управления, выход второго элемента И соединен с первым входом шестого элемента И, выход которого соединен с восьмым .выходом блока управления, вторые входы первого, пятого и шестого элементов И соединены с первым входом блока управления, четвертый вход блока управления соединен с первым входом седьмого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ и через второй элемент задержки - с третьим входом первого элемента ИЛИ, и че-г рез третий элемент задержки - с четвертым выходом блока управления, прямой вход второго элемента И соединен с BTopbnvi входом блока управления вторым и третьим входами соответственно седьмого и первого элементов И, второй вход блока управления, соединен с единичным входом триггера режима, нулевой вход которого соединен с третьим входом блока управления, единичный выход триггера режима соединен с первым входом восьмого элемента И, выход которого соединен с третьим входом, седьмого элемента И, с одиннадцатым выходом блока управления и с вторым входом второго элемента ИЛИ, нулевой выход триггера режима соединен с первым входом девятого элемента И, выход которо о соединен с десятым выходом блока управления, третьим прямым и третьим входами соответственно второго и четбертого элементов И, вторые входы восьмого и девятого элементов И соединены с первым входом блока управления.

3. Устройство по п. I, отличающ е ее я тем, что .блок формирования адреса содерткит шифратор, элемент ИЛИ, элетлент И, два блока элементов И и два .счетчика, причем информационный вход блока соединен с первым входом первого

.блока элементов И, выход которого соединен с входом шифратора, выход которого соединен с установочНьтм входом первого счетчика, выходы которого являют- . ся вторым выходом блока формирования адреса, пятый управляющий вход блока формирования адреса соединен с вторыми входами первого блока элементов И, четвертый и второй управляющие входы блока формирования адреса соединены с входами элемента И, выход которого соединен с динамическим входом счетчика и через элемент ИЛИ - с динамическим входом второго счетчика, выход которого через второй блок элементов И соединен с первым выходом блока формирования адреса, первый управляющий вход блока формирования адреса соединен с вторыми входами второго блока элементов И, третий управляющий вход блока соединен с вторым входом влемента ИЛИ.

4. Устройство по п. I, отличающее с я тем, что блок контроля содержит узел контроля четности, блок элементов ИЛИ, три элемента И ЛИ,-инвертор, три элемента задержки, четыре элем«1та И, два триггера дешифратор и счетчик, выходы которого соединены с входами дешифратора, первый выход которого через инвертор соединен с первым выходсФл блока контроля, второй выход деип ратора соединен соответствейно с первыми входами первого, второго и прямым входом третьего элалентов И, первый, второй информационные входы блока контрс51ля соединены с .входами блока элементов ИЛИ, которого соединен

с входом узла контроля четности, ЬыхоДТ которого соединен соответственно с первы и инверсным входами четвертого и пятого элементов И, второй и третий управляющие входы блока соедин ы с входами первого элемента ИЛИ, выход которого че |Ьев первый задержки соединен с вторым входом четвертого элемента И, выход которого соединен с входом счетчика, выход которого соединен с входом дещифратора .выход первого элемента задержки через второй элемент задержки соединен соответствевно с прямым и вторым входами пятого и первого элементов И, выходы которых соединены с входами второго элем«1та ИЛИ, выход которого соединен с входом установки в нуль счетчика, первый управляющий вход блока соединен соответственно с вторым и инверсным входами второго я третьего И, ыход второго элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, а выход - с единичным входом первого триггера, инв х:ный выход которого соединен с четвертым выходом блока, выход третьего элемента И соединен с третьим выходом блока, со счетным входом второго триггера и с первым входом шестого элемента И, второй вход которого через третий элемент задержки соединен с пятым выходом блока и прямым выходом второго триггера, вход которого соединен с четвертым входом блока, а инверсный выход - с вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

1.МИКРОПРОГРАММНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок формирования адреса, блокутгравления, блок основной памяти, блок управляющей памяти, арифметический блок, коммутатор, регистр операнда, буферный регистр, регистр адреса микрокоманд и регистр адреса команд, выходы которого соединены с первой группой входов буферного регистра, выходы которого соединены с адресными входами блЪка основной памяти, выход которого соединен с первым информационным входом коммутатора, первый выход которого соединен с первым входом арифметического блока, выход которого соедини с входом регистра операнда, первый выход которого соединен с вторым входом арифметического блока, второй выход регистра операнда соединен с первым управляющим входом Коммутатора, второй выход которого соединен с лервым информационныкТ входом регистра адреса микрокоманд, второй информационный вход которого соединен с первым выходом блока формирова ния адреса, второй выход которого соединен с второй группой входов буферного регистра, первый и второй выходы блока управления соединены соответственно с вторым и третьим управляющими входами коммутатора, третий выход блока управления соединен с управляющими входами буферного регистра и блока основной памяти и с первым управляющим входом блока формирования адреса, второй и третий управляющие входы которого соединены соответственно с четвертым и пятым выходами блока управления, шестой и седьмой выходы которого соединены соответственно с первым и вторым управляющими входами блока управЛЕПощей памяти, выход которого соединен с входом регистра микрокоманд, выход которого соединен с вторым информацион- О ным входом -коммутатора, о т л нч а.ю(Л щ е е с я тем, что, с целью повыщення «. - отказоустойчивости и быстродействия, оно : : дополнительно содержит два буферных| регистра, элемент ИЛИ, два блока эле-, ментов ИЛИ, пять блоков элементов И, элемент задержки и блок контроля, первый выход которого соединен с первым входом блока управления и четвертым управляющим входом блока формирования адреса, второй выход блока контроля соединен с 00 J четвертым управляющим входом коммутатора, третий выход которого соединен с первым информационным входом блока кона 4 роля и с первым входом первого блока эл&ментов И, выход KOTOporiCKсоединен с 12нформаш1он 1ым входом блока управляющей памяти, выход KOTopioro соединен с вторым информационным входом блока конт роляутретяй выход которого соединен с пятым управляющим входом блока формирования адреса, выход регистра адреса микрокоманд соединен с информационным входом блока формир ания адреса и с первыми входами первого второго и третьего блоков эле

Изобретение относится к автоматике и вычислительной тезшике и может быть использовано в устройствах управления цифровых вычислительных машин.

Известен микропрограмный процессор с восстановлением при сбоях, содержащий блок сопряжения с памятью, блок памяти, блок регистров, блок управпен Е я регистрмикрокоманд регистр адреса микрокоманд, коммутатор выдачи, арнф сетикологический блок, блок контроля, счетчик сбоев, коммутатор, приема, регистр адрв- са приема, регистр исходной инфортлашш, рет-истр адреса повтора; яяементы И Щ,

Недостатком этого процесса является низкая функциональная надежность и низкое быстродействие, обусловленные невоз-

можностью автоматического восстаковлевия микрокоманд при jowjasax ячеек блока памяти.

Нанболее близким по технической сущности и достигаемому результату к предлагаемому является вычислительное устройство, содержащее блок формирования адреса, блок управления, блок основной памяти, блок управляющей памяти аря4)метячеокий блок, та тор, регистр операнда,

буферный регистр, регистр адреса микрокоманд, регистр микрокоманд и регистр адреса команд, выходы которого соединены с первой группой входов буферного регистра, выходы которого соединены с первой 4 руппрй входов блока основной памяти, выходы которого через коммутатор соединены с первой группой входов арифметического блока, выходы которого соединены с входами регистра операнда, первая группа выходов которого соединена с второй грутатой входов арифметического блока вторая группа выходов регистра операнда соединена с второй группой входов коммутатора, вторая группа выходов соединена с первой группой входов регистра адреса микрокоманды, вторая группа входов которого соединена с первой группой выходов блока формирования адреса, вто рая группа выходов которого соединена с второй группой входов буферного регист ра, причем первый и второй выходы блока управления соединены соответственно с первым и вторым управляющими- входами коммутатора, третий выход блока у фавления соединен с управляющими входами буферного регистра и блока основной памяти и с первым управляющим входом бл ка формирования адреса, второй и третий управляющие входы которого соединены соответственно с четвертые и пятым выходами блока управления, шестой и седьмой выходы которого соединены соответс венно с первым и вторым управляющими входами блока управляющей памяти, выходы которого соединены с входами регистра микрокоманд, выходы которого сое динены с третьей группой входов коммутатора .2 . Недостатками этого устройства являются низкая функциональная надежность и н кое быстродействие, Низкая функциональная надежность ус ройства обусловлена отсутствием контроля микрокоманд при переписи их в блок управляющей памяти и считывании.из него, а так же невозможностью автоматического восст новления правильного значения микрокоманды при сбоях или при отказе соответствующей ячейки блока управляющей памяти. Низкое быстродействие устройства обусловлено тем, что в нем восстановление правильного значения микрокоманды при сбоях воаможко лишь путем повторного выполнения всей микропрограммы а при отказах ячеек блока управляющей памяти - путем перезаписи всей микропрограммы, в то время как вполне достаточно было бы повторить считывание или перепись лишь забракованной микрокоманды. Цель изобретения - повыщение отказоустойчивости и быстродействия устрюйства. Поставленная цель достигается тем, НТО в устройство, содержащее блок форми рования адреса, блок управления, блок основнс памяти, .блок управляющей памяти, арифметический блок, коммутатор, регистр операнда, буферный регистр, регистр адреса микрокоманд и регистр адреса команд, выходы которого соединены с первой группой входов буферного регистра, выходы которого соединены с адресными входами блока основной памяти, выход которого соединен с первым информационным входом коммутатора, первый выход которого соединен с первым входом арифметического блока, выход которого соединен с входом регистра операнда, первый выход которого соединен с вторым входом ариф1- метического блока, второй выход регистра операнда соединен с первым управляющим входом коммутатора, второй выход которого соединен с первым информационным входом регистра адреса микрокоманды, второй информационный вход которого соединен с первым выходом блока формирования адреса, второй выход которого соединен с второй группой входов буферного регистра, первый и второй выходы блока управления соединены соответственно с вторык1 и третьим управляющими входами коммутатора, третий выход блока управления соединен с управляющими входами буферного регистра и блока основной памяти и с первым управляющим входом блока формирования адреса, второй и третий управляющие входы которого соединены соответственно с четвертым и пятым выходами блока управления, шестой и седьмой выходы которого соединены соответственно с первым и вторым управляющим входами блока управляющей памяти, выход которого соединен с входом регистра микрокоманд, выход которого соединен с вторым информационным входом коммутатора, дополнительно введены два буферных регистра, элемент ИЛИ, два блока элементов ИЛИ, пять блоков элементов И, элемент задержки и блок контроля, первый выход которого соединен с первым входом блока управления и 4eTBepTbnvi утфавлякяцим входом блока формирования адреса, второй выход блока контроля соединен с четвертым управляю1цим входом коммутатора, третий выход которого соединен с первым информационным входом блока конт510роля и с первым входом первого блока элементов И, выход которого соединен с информационным входом блока управляю щей памяти, выход которого соединен d вторым информационным входом блока кон роля, третий выход которого соединен с |1ятым управляющим входом блока формирования адреса, выход регистра адреса микрокоманд соединен с информационным входом блока формирования адреса и с первыми входами первого, второго и третьего блоков элементов И, выход первого блока элементов И подключен к второму входу первого блока элементов ИЛИ, выход второго блока элементов И подключен к адресному входу блока управ ляющей памяти, выход третьего блока эле ментов И подключен к входу второго буферного регистра, выход которого соедине с первым входом четвертого блока элементов И, выход которого соединен с вхо дом третьего регистра, выход которого соединен с первым входом пятого блока элементов И, выход которого соединен с вторым входом второго блока элементов ИЛИ, четвертый и пятый выходы блока контроля соединены соответственно с вторым и третьим выходами блока управления, восьмой выход которого соединен с вторым входом четвертого блока элементов И и через элемент-задержки с вторым входом третьего блока элементов И, девятый выход блока управления соединен с вторыми входами первого и пятого блоков элементов И и с инверсным входом второго блока эле ментов И,-первый и десятый выходы блока управления соединены с первым и вторым входами элемента ИЛИ, выход которого соединен с вторым входом второго блока элементо И, одиннадцатый третий, шестой и пятый выходы блока управления соединены соо- ветственно с первым j вторым третьим и четвертым управляющими ёходами блока контроля, первый второй,третий, четвер, тый и пятый управл51к}шке входы устройст ,ва соединены соответственно с четвер « тъкл, пятым, шестым, седьмым н восьмым входами блока управления. , При этом блок управления содержит триггер режима, девять элементов И, три элемента задержки, четыре элемента ИЛИ, счетчик и дешифратор, первый выход которого соединен с девятым выходом блока управления в с первым входсм первого элемента ИЛИ, выход которого соединен с седьмым выходом блока управления, второй выход дешифратора соединен с вторым входом первого элемента 416 ИЛИ, третий выход дешифратора соединен с первым входом первого элемента И, выход которого соединен с пятым выходом блока управление четвертый выход деип ратора через второй и третий элементы ИЛИ соединен соответственно с первым и третьим выходами блока управления, пятый выход дешифратора соединен с первым инверсным-входом второго элемента И и с первым входом третьего элемента И, выход которого соединен с первым входом четвертого элет 1ента ИЛИ, выход которого соединен с динамическим входом счетчика, выходы которого соё-динены с входами дещифратора, третий вход блока управления соединен с вторым инверсным входом второго элемента И.и с первым входом 1етвертого элемента.И, выход которого соединен с вторым входом четвертого элемента ИЛИ, пятый вход блока управления соединен с вторыми входами третьего и четвертого элементов И : и с первым прямым входом второго элемента И, выход которого соединен с шестым выходом блока управления, через первый элемент задержки с первым входом пятого элемента И, выход которого соединен -с вторым выходом блока управления, выход второго элемента И соединен с первым входом шестого эл-емента И, выход которого соединен d- восьмым выходом блока управления, .вторые входь первого , пятого и шестого элементов Исоединены с первым входом блока управления, четвертый вход блока управления соединен с первым входом седьмого элемента И, выход которого соединен с вточ рым входом третьего элемента ИЛИ через второй элемент задержки - с третьим входом первого элоу1ента ИЛИ и через третий элемент задернскй - с четвертым выходом блока управления, второй прямой вход второго элемента И соединен с вторым входом блока управления, вторым и третьим входами соответственно седь- . мого и первого элементов И, второй вход блока управлеши соединен с едшгачным входом триггера режима, нулевой вход которого соединен с,, третьим входом блока управления, единичньтй выход триггера режима соединен с первым входом восьмого элемента И, выход которого соединен с третьим входом седьмого элемента И, с одиннадцатым выходом блока управления и с вторым входом второго. эл« 1ента ИЛИ, нулеьой выход триггера режима соединен с первым входом девятого элемента И, выход которого со.единен с десятым выходом блока упраслення.

третьим npsTMbiM и третьим входами соответственно второго и четвертого элементов И, вторые входы восьмого и девятого эпемактов И соединены с первым, входом блока управления.

Кроме того, блок формирования адреса содерюгг шифратор, элемент ИЛИ, И, два блока элементов И и два счетчика, причем информационный вход блока формирования адреса соединен с первым входом первого блока элементов И, выход которого соединен с входом шифратора, выход которого соединен с установочным входом первого счетчика, выходы которого являются вторым выходом блока формирования адреса, пятый управляющий вход блока формирования ад- . реса соединен с вторыми входами первого блока элементов И, четвертый и второй управляющие входы блока формирования адреса соединены с входами элемента И, выход которого соединен с динамическим входом первого счетчика и через элемент ИЛИ - с динамическим входом второго счетчика, выход которого через второй блок элемента И соединен с первым выходом блока формирования адреса, первый управлякнций вход блока формирования адреса соединен с вторыми входами второго блока элементов И, третий управляющий вход блока соединен с вторым входом элемента ИЛИ.

БЛОК контроля содерногг узел контроля четности, блок эпв {ентов ИЛИ, три элемента ИЛИ, инвертор, три элеме гга задержки четыре элемента И, два триггера, дешифратор и счетчик, выходы которого соединены с входами дешифратора, первый выход которого через инвертор соединён с первым выходом блока контроля, второй выход Дешифратора соединен соответственно, с первыми Ходами первого, второго и прямым входом третьего элементов И, первый и второй информаиионаые входы блока контроля соединетгы с входами блока элементов ИЛИ, выход которого соединен с входом узла коатрсотя четности, выход которого соединен соответс- венно с первым и инверсным входами четвертого и пятого элементов.И, второй и третий управляннпие входы блока соединены с входами первого эпемента И ЛИ, выход которого через первый элемент задержки соединен с вторым входом четвертого элем«1та И, выход которого соединен со счетным входом счетчика, выход которог соединен с входом дешифратора, выход первого эпемента задерноси через второй элемент задержки соединен соответственно с прямым и вторым входами пятого и первого элементов И, выходы которых соединены с входами второго элемента ИЛИ, выход которого соединен с входом установки в нуль счетчика, первый управг ляющнй вход блока соединен соответст. венно с вторым и инверсным входами вторс- о и третьего элементов И, выход второго элемента И соединен с первым вхдом третьего элемента ИЛИ, второй вход/ которого соединен с выходом шестого элемента И, а выход - с единичным входом первого триггера, инверсный выход которого соединен с четвертым выходом, бло. ка, выход третьего элемента И соединен с третьим выходом блока, со счетньпч входом второго триггера и с первым входом . шестого элемента И, второй вход которого через третий элемент задержки соеди. вен с пятым выходом блока и пр$гмым выходом второго триггера, вход которого соединен с четвертым управляющим входом блока, а инверсный выход - с вторым выходом блока.

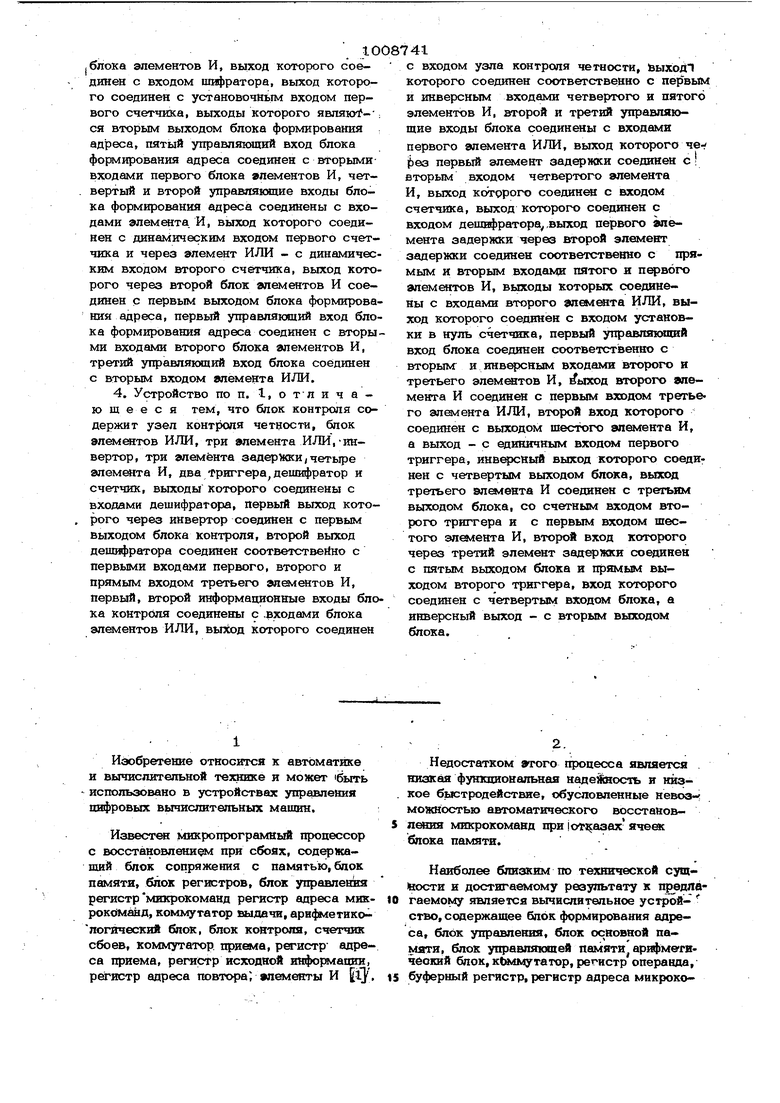

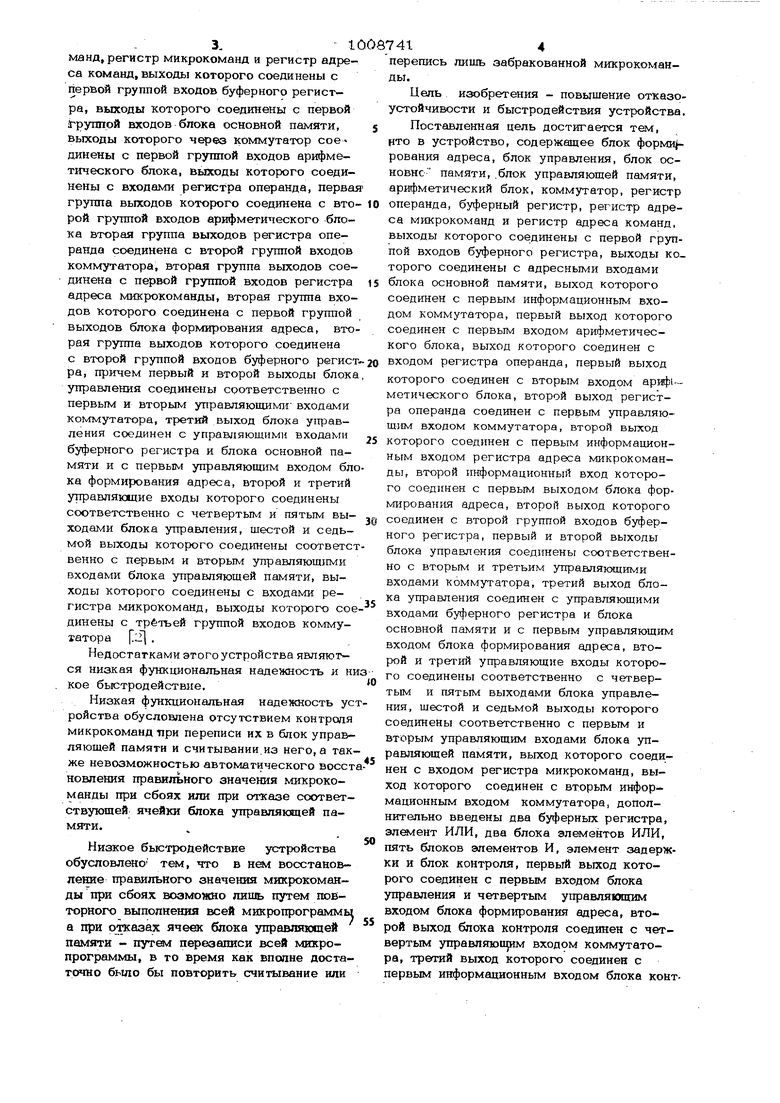

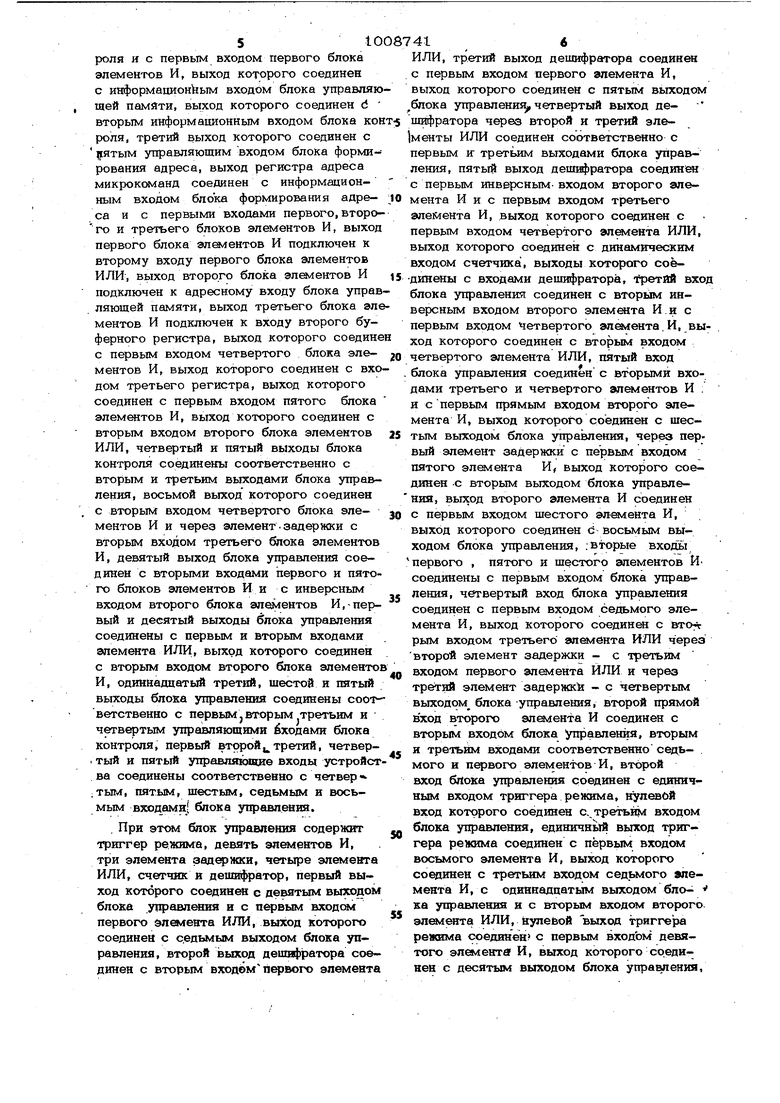

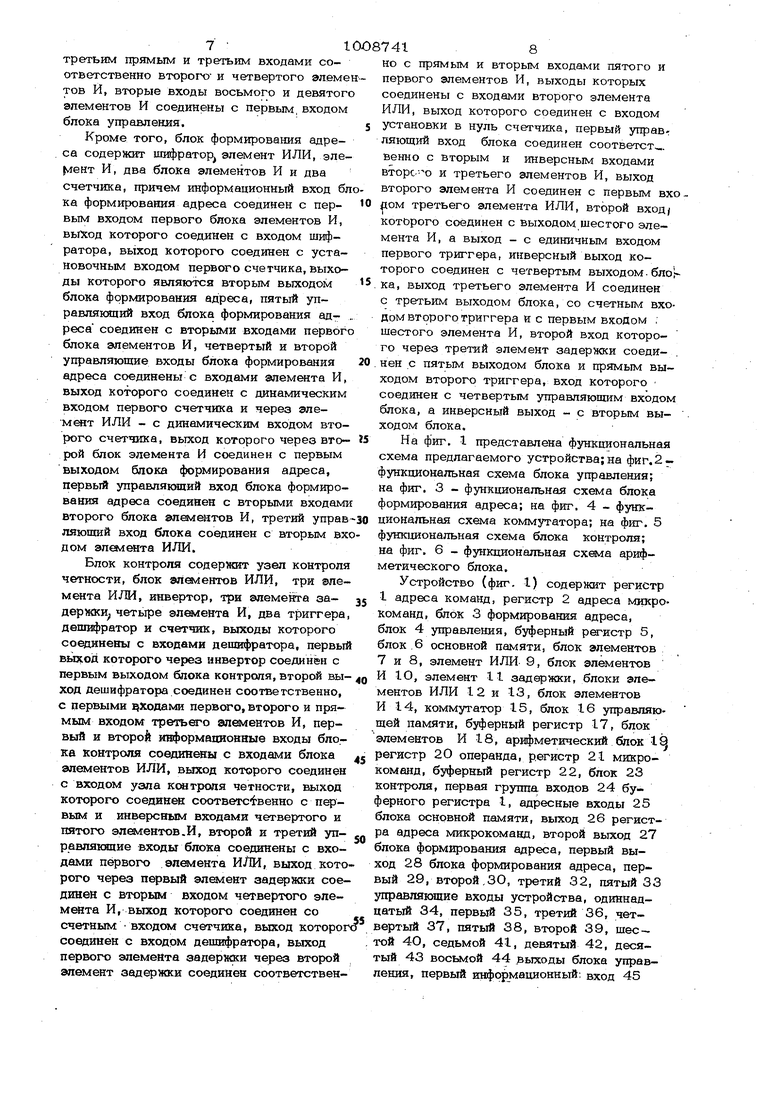

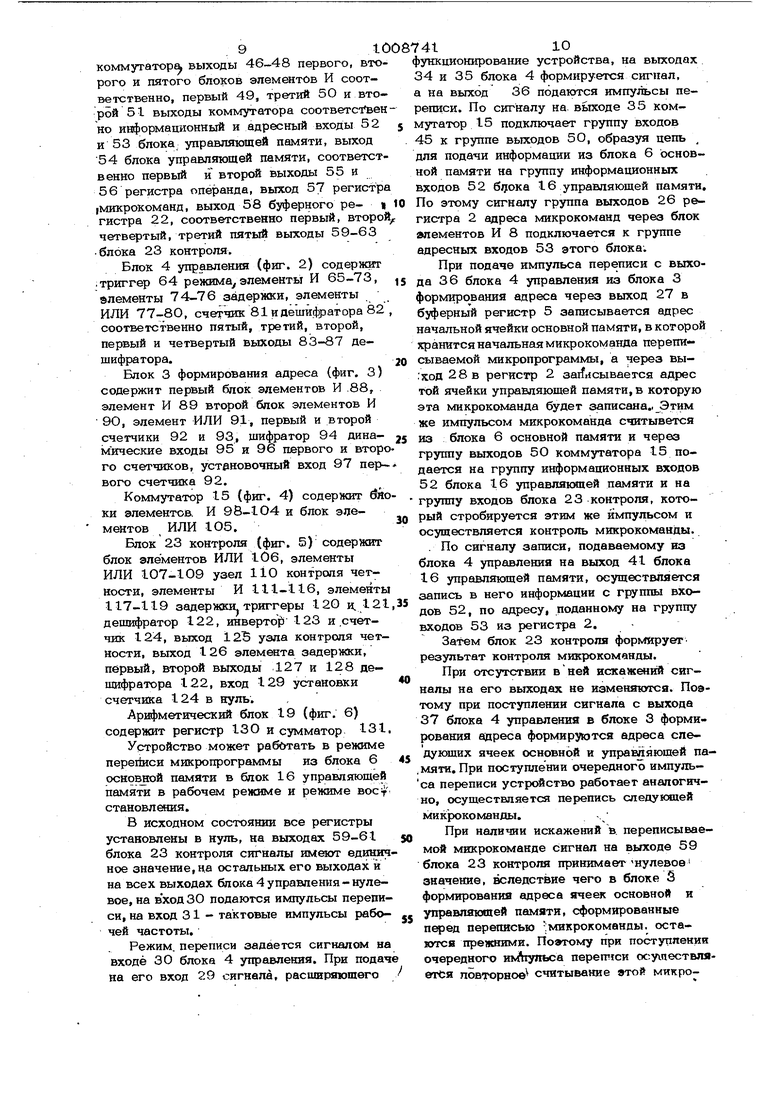

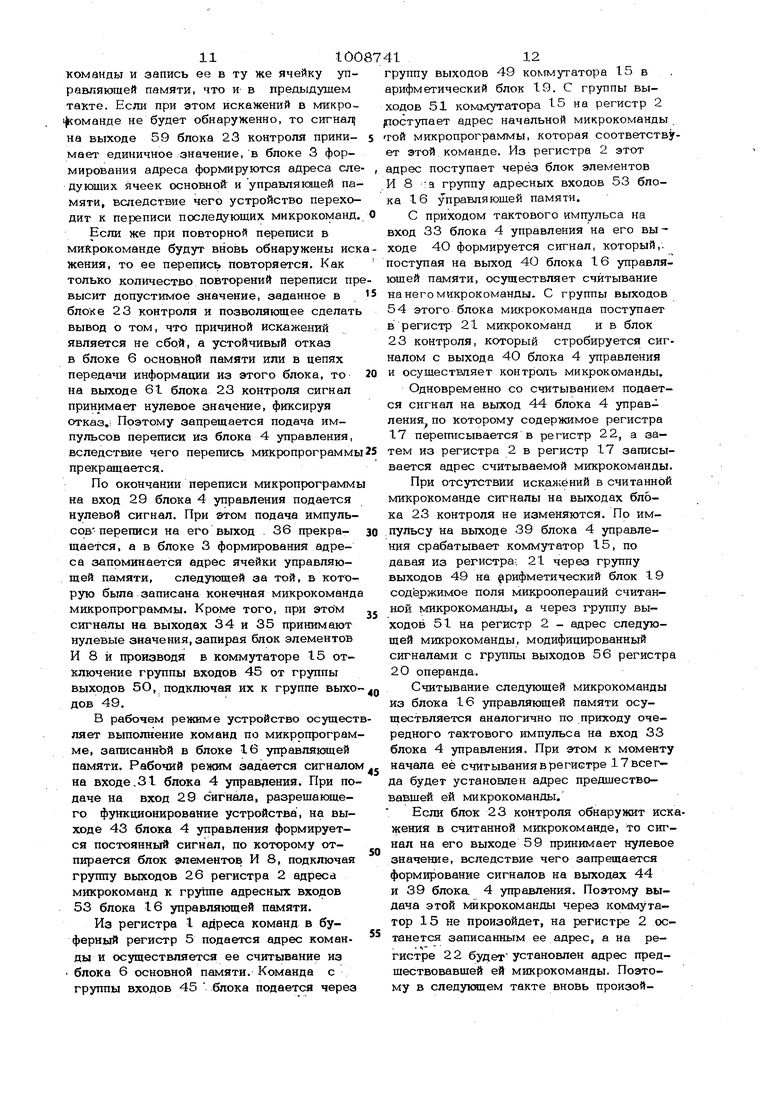

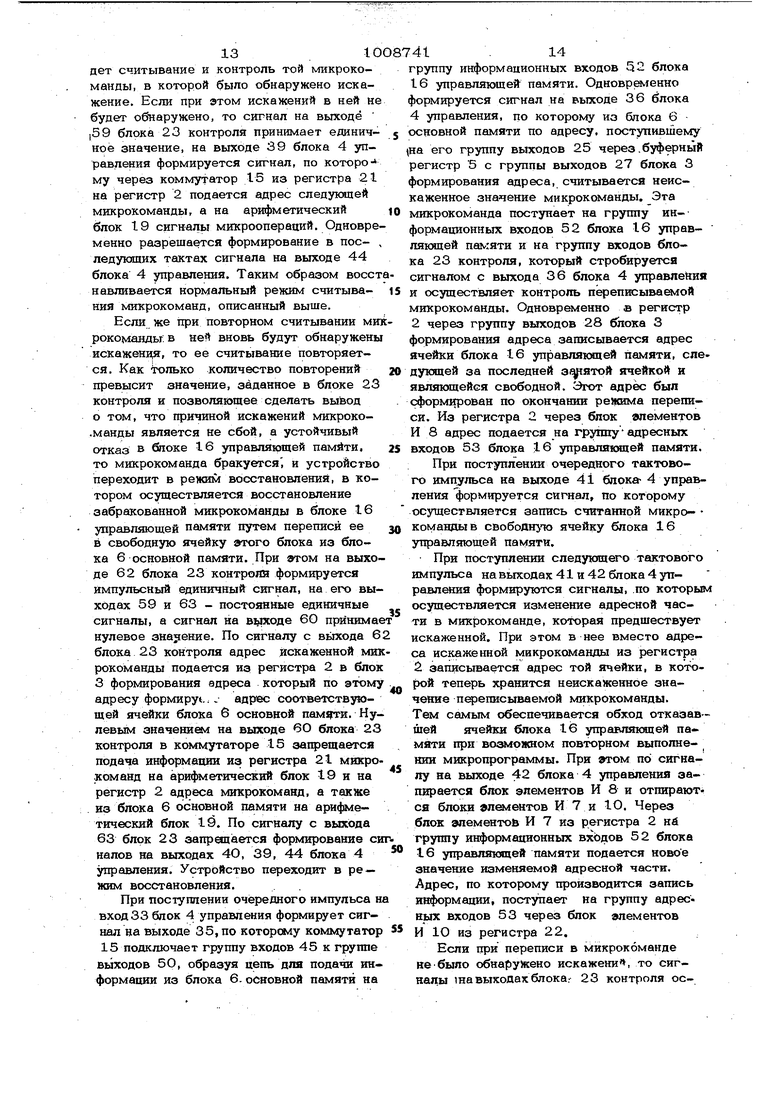

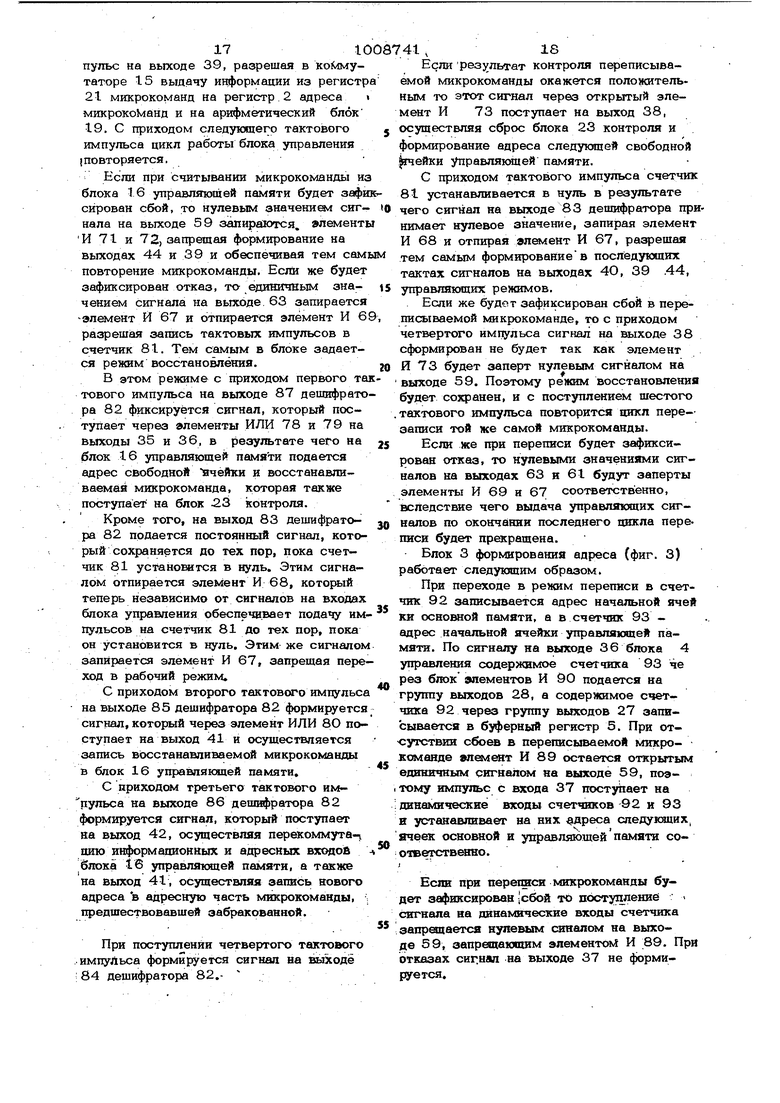

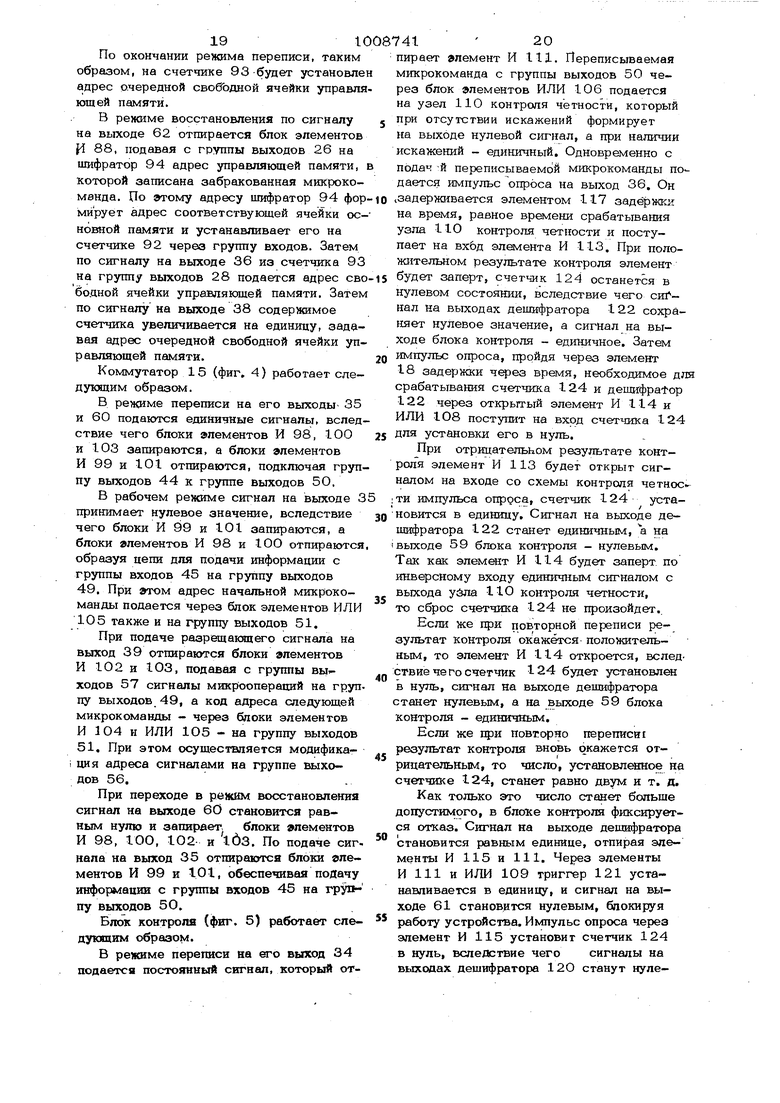

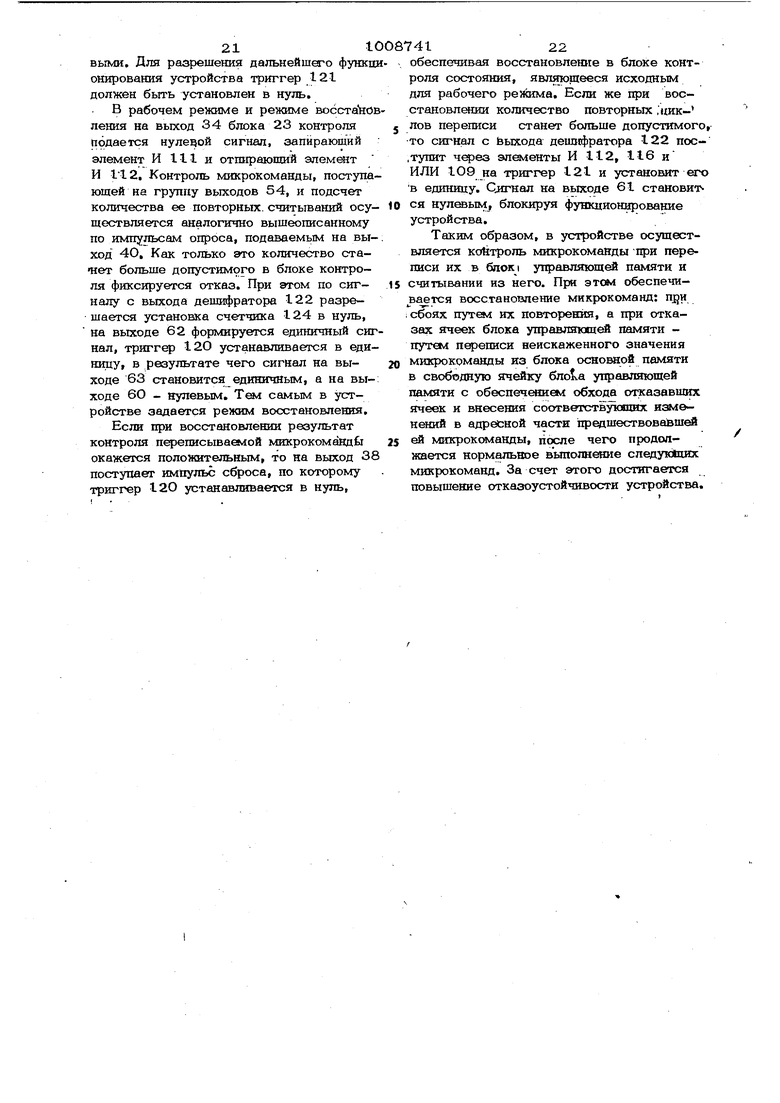

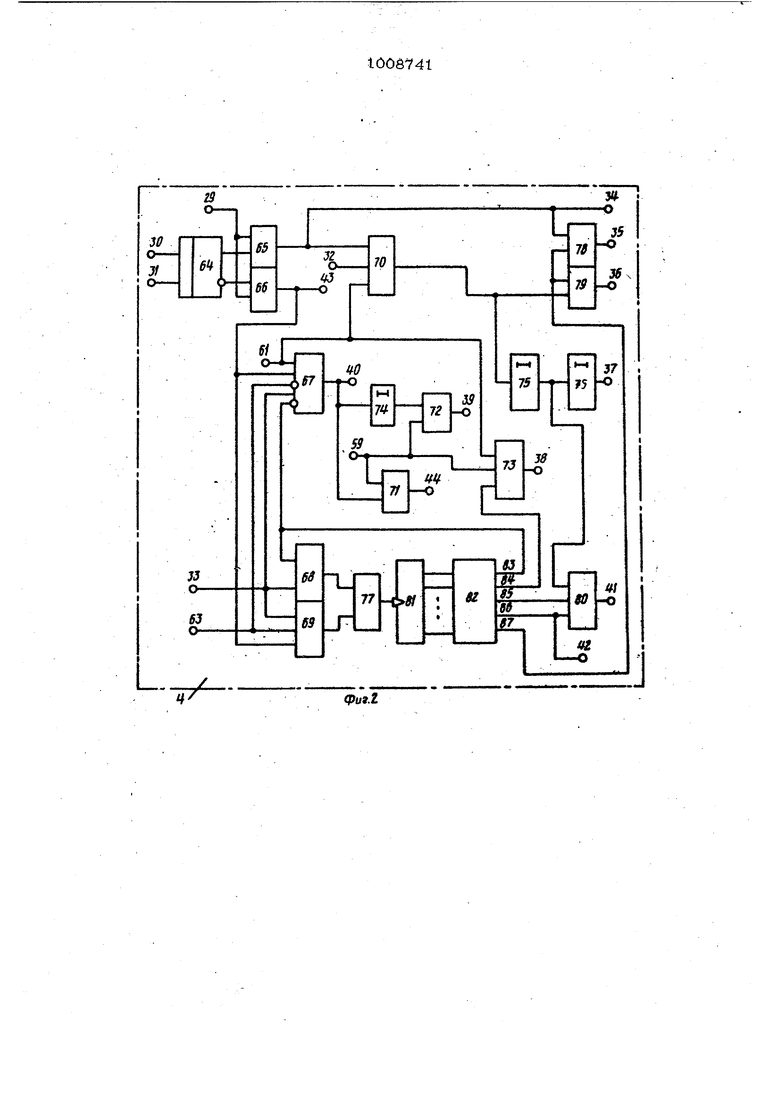

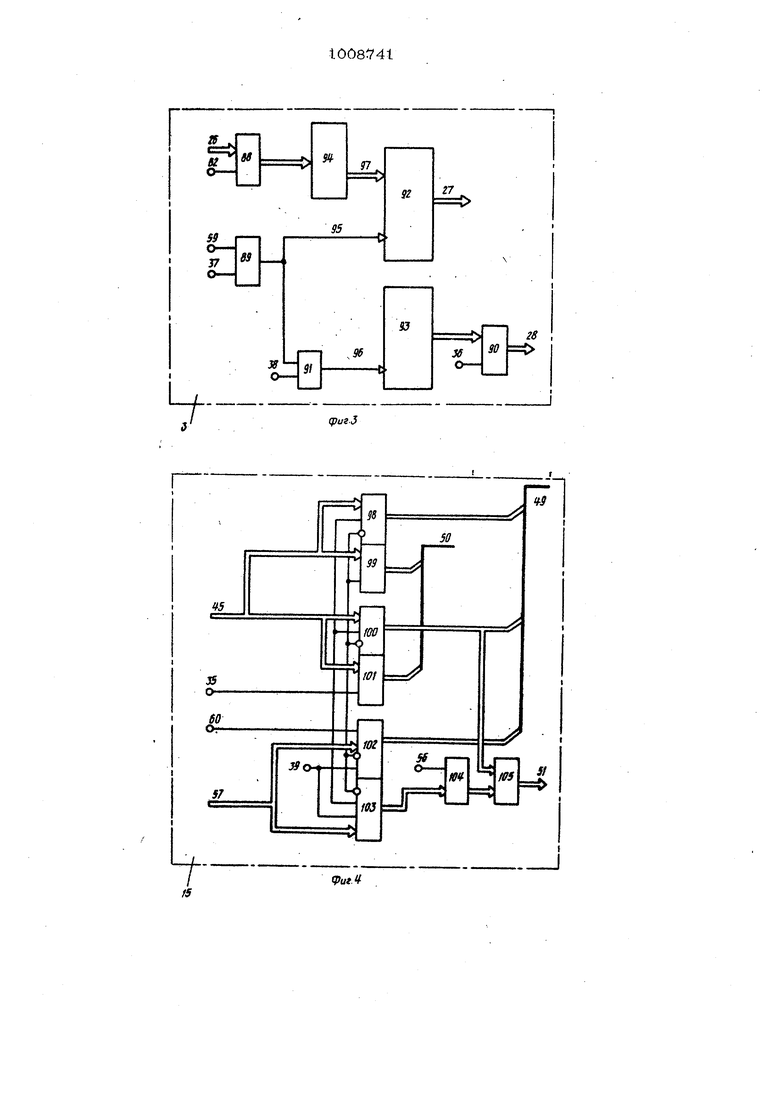

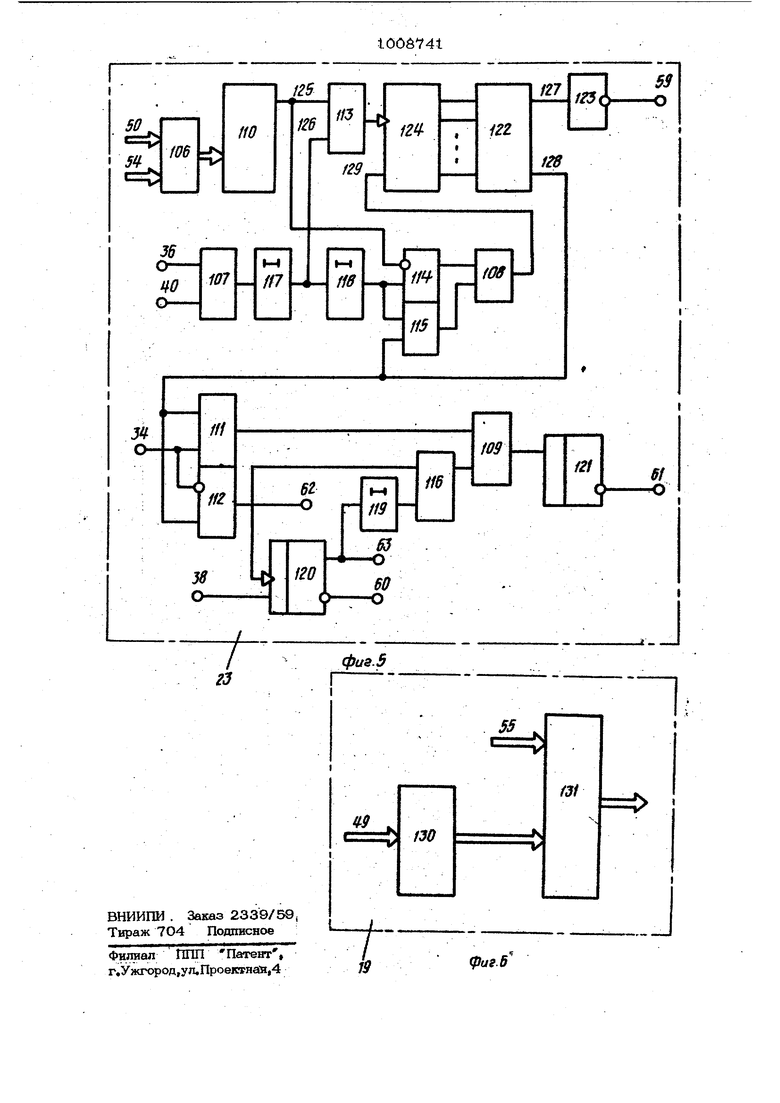

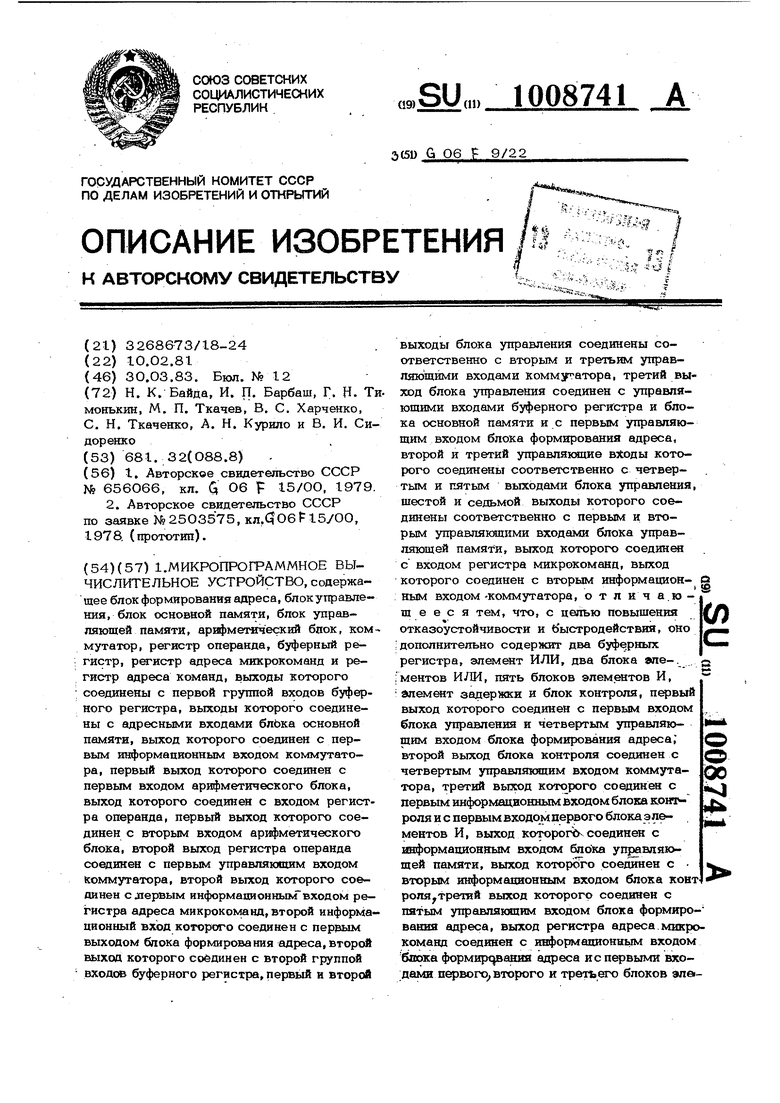

На фиг. 1 представлена функциональная схема предлагаемого устройства;на фиг.2функциональная схема блока управления; на фиг. 3 - функциональная схема блока формирования адреса; на фиг. 4 - функциональная схема коммутатора; на фиг. 5 фунгадаональная схема блока контроля; на фиг. 6 - функциональная схема арифметического блока.

Устройство (фиг. I) содержит регистр I адреса команд, регистр 2 адреса микрокоманд, блок 3 формирования адреса, блок 4 управления, буферный регистр 5, блок .6 основной памяти, блок элементов 7 и 8, элемент ИЛИ- 9, блок элементов И Ю, элемент II задержки, блоки элементов ИЛИ 12 и 13, блок элементов И 14, коммутатор 15, блок 16 утфавляющей памяти, буферный регистр 17, блок элементов И 18, арифметический блок 1 регистр 20 операнда, регистр 21 микрокоманд, буферный регистр 22, блок 23 контроля, первая группа входов 24 буферного регистра I, адресные входы 25 блока основной памяти, выход 26 регистра адреса микрокоманд, второй выход 27 блока формирования адреса, первый выход 28 блока формирования адреса, первый 29, второй,30, третий 32, пятый 33 управляющие входы устройства, одиннадцатый 34, первый 35, третий 36, четвертый 37, пятый 38, второй 39, шес той 4О, седьмой 41, девятый 42, десятый 43 восьмой 44 выходы блока управления, первый информационный; вход 45 910 коммутатора выходы 46-48 первого, второго и пятого блоков элементов И соответственно, первый 49, третий 50 и второй 51 выходы коммутатора соответствен но информационный и адресный входы 52 и 53 блока управляющей памяти, выход 54 блока управляющей памяти, соответственно первый и второй выходы 55 и 56 регистра операнда, выход 57 регистра Микрокоманд, выход 58 буферного ре- « гистра 22, соответственно первый, второй четвертый, третий пятый выходы 59-63 блока 23 контроля. Блок 4 управления (фиг. 2) содержит триггер 64 режима элементы И 65-73, элементы 74-76 задержки, элементы ИЛИ 77-8О, счетчик 81 и дешифратора 82 соответственно пятый, третий, второй, первый и четвертый выходы 83-87 дешифратора. Блок 3 формирования адреса (фиг. 3) содержит первый блок элементов И .88, элемент И 89 второй блок элементов И 9О, элемент ИЛИ 91, первый и второй счетчики 92 и 93, шифратор 94 динамические входы 95 и 96 первого и вторО го счетчиков, установочный вход 97 пер- вого счетчика 92. Коммутатор 15 (фиг. 4) содержит бяо ки элементов, И 98-104 и блок элементов ИЛИ 105. Блок 23 контроля (фиг. 5) содержит блок элементов ИЛИ 106, элементы ИЛИ 107-109 узел 110 контроля четности, элементы И 111-116, элементы 117-119 задержки, триггерь 120 и. 121 дещифратор 122, инверто|з 123 и .счетчик 124, выход 12В узла контроля четности, выход 126 элемента задержки, первый, второй выходы 127 и 128 дешифратора 122, вход 129 установки счетчика 124 в нуль. Арифметический блок 19 (фиг. 6) содержит регистр 13 О и сумматор 131. Устройство может работать в режиме перейиси микропрограммы из блока 6 памяти в блок 16 управляющей памяти в рабочем режиме и режиме восг становления. В исходном состоянии все регистры установлены в нуль, на выходах 59-61 блока 23 контроля сигналы имеют единич ное значение, на остальных его выходах и на всех выходах блока 4 управления - нулевое, на вход 30 подаются импульсы переписи, на вход 31 - тактовые импульсы рабочей частоты. Режим, переписи задается сигналом на входе 30 блока 4 управления. При подаче на его вход 29 сигнала, расширяющего -I о f 4110 функционирование устройства, на выходах 34 и 35 блока 4 формируется сигнал, а На выход 36 подаются импульсы переписи. По сигналу на. выходе 35 коммутатор 15 подключает группу входов 45 к группе выходов 5О, образуя цепь , для подачи информации из блока 6 основной памяти на группу информационных входов 52 16 управляющей памяти. По этому сигналу группа выходов 26 регистра 2 адреса микрокоманд через блок элементов И 8 подключается к группе адресных входов 53 этого блока; При подаче импульса переписи с выхода 36 блока 4 управления из блока 3 формиро вания адреса через выход 27 в буферный регистр 5 записывается адрес начальной ячейки основной памяти, в которой хранится начальная микрокоманда переписываемой микропрограммы, а через вы:ход 28 в регистр 2 записывается адрес той ячейки управляющей памяти, в которую эта микрокоманда будет записана., Этим же импульсом микрокоманда считывется из блока 6 основной памяти и через группу выходов 5 О коммутатора 15 подается на группу информационных входов 52 блока 16 управлякнцей памяти и на группу входов блока 23 контроля, который стробируется этим же импульсом и осуществляется контроль микрокоманды. По сигналу записи, подаваемому из блока 4 управления на выход 41 блока 16 управляющей памяти, осуществляется запись в него информации с группы вхо g, по адресу, поданному на группу входов 53 из регистра 2. Затем блок 23 контроля формирует результат контроля микрокоманды. При отсутствии в ней искажений сигналы на его выходах не изменякугся. Поэтому при поступлении сигнала с выхода 37 блока 4 управления в блоке 3 формирования адреса формируются адреса следующих ячеек основной и упрашяющей памяти. При поступлении очередного импульса переписи устройство работает аналогично, осуществляется перепись следующей микрокоманды. При наличии искажений в переписываемой микрокоманде сигнал на выходе 59 блока 23 контроля принимает нулевое значение, вследствие чего в блоке 5 формированиа адреса ячеек основной и управлякяпей памяти, сформированные перед переписью :микрокоманды, остаются прежними. Поэтому при поступлении очередного нкЛтупьса перешгси сс уществляетСя повторное- считывание втой микро1110команды и запись ее в ту же ячейку управляющей памяти, что и в предыдушем такте. Если при этом искажений в микро1 оманде не будет обнарунсенно, то сигнал} на выходе 59 блока 23 контроля принимает единичное значение, в блоке 3 формирования адреса формируются адреса еле дующих ячеек основной и управляющей па мяти, вследствие чего устройство переходит к переписи последующих микрокоманд Если же при повторной переписи в микрокоманде будут вновь обнаружены ис женин, то ее перепись повторяется. Как только количество повторений переписи пр высит допустимое значение, заданное в блохе 23 контроля и позволяющее сделат вывод о том, что причиной искажений является не сбой, а устойчивый отказ в блоке 6 основной памяти или в цепях передачи информации из этого блока, то на выходе 61 блока 23 контроля сигнал принимает нулевое значение, фиксируя отказ,; Поэтому запрещается подача импульсов переписи из блока 4 управления, вследствие чего перештсь микропрограммы прекращается. По окончании переписи микропрограмм на вход 29 блока 4 управления подается нулевой сигнал. При этом подача импульсов переписи на его выход . 36 прекращается, а в блоке 3 формирования адреса запоминается адрес ячейки управляющей памяти, следующей за той, в которую была записана конечная микрокоманд микропрограммы. Кроме того, при этбм сигналы на выходах 34 и 35 принимают нулевые значения, запирая блок элементов И 8 и производя в коммутаторе 15 отключение группы входов 45 от группы выходов 5О, подключая их к группе выхо дов 49. В рабочем режиме устройство осущест ляет выполнение команд по микропрограм ме, записаннЬй в блоке 16 управляющей памяти. Рабочий режим задается сигналом на входе.31 блока 4 управ тения. При подаче на вход 29 сигнала, разрещающего функционирование устройства, на выходе 43 блока 4 управления формируется постоянный сигнал, по которому отпирается блок элементов И 8, подключая группу выходов 26 регистра 2 адреса микрокоманд к группе адресных входов 53 блока 16 управляющей памяти. Из регистра 1 адреса команд в буферный регистр 5 подается адрес команды и осуществляется ее считывание из блока 6 основной памяти. Команда с группы входов 45 блока подается через 1 группу выходов 49 коммутатора 15 в арифметический блок 19. С группы выходов 51 коммутатора 15 на регистр 2 оступает адрес начальной микрокоманды , ой микропрограммы, которая соответствует этой команде. Из регистра 2 этот адрес поступает через блок элементов И 8 -а группу адресных входов 53 блока 16 управляющей памяти. С приходом тактового импульса на вход 33 блока 4 управления на его выходе 4О формируется сигнал, который,. поступая на выход 4О блока 16 управляющей памяти, осуществляет считывание на него микрокоманды. С группы выходов 54 этого блока микрокоманда поступает в регистр 21 микрокоманд и в блок 23 контроля, который стробируется сигналом с выхода 40 блока 4 управления и осуществляет контроль микрокоманды. Одновременно со считыванием подается сигнал на выход 44 блока 4 управления по которому содержимое регистра 17 переписывается в регистр 22, а затем из регистра 2 в регистр 17 записывается адрес считываемой микрокоманды. При отсутствии искайсёний в считанной микрокоманде сигналы на выходах блока 23 контроля не изменяются. По импульсу на выходе 39 блока 4 управления срабатывает коммутатор 15, по давая из регистра; 21 через группу выходов 49 на рифметический блок 19 содержимое поля микроопераций считанной микрокоманды, а через группу выходов 51 на регистр 2 - адрес следующей микрокоманды, модифицированный сигналами с группы выходов 56 регистра 20 операнда. Считывание следующей микрокоманды из блока 16 управляющей памяти осуществляется аналогично по приходу очередного тактового импульса на вход 33 блока 4 управления. При этом к моменту начала её считывания в регистре 17 всегда будет установлен адрес предшествовавшей ей микрокоманды. Если блок 23 контроля обнаружит искажения в считанной микрокоманде, то сигнал на его выходе 59 принимает нулевое значение, вследствие чего запрещается форми5зование сигналов на выходах 44 и 39 блока 4 управления. Поэтому выдача этой микрокоманды через коммутатор 15 не произойдет, на регистре 2 останется записанным ее адрюс, а на регистре 22 будетустановлен адрес предшествовавшей ей микрокоманды. Поэтому в следующем такте вновь произойдет считывание и контроль той микрокоманды, в которой было обнаружено искажение. Если при этом искажений в ней не будет обнаружено, то сигнал на выходе |59 блока 23 контроля принимает единичкое значение, на выходе 39 блока 4 управления формируется сигнал, по которо- му через коммутатор 15 из регистра 21 на регистр 2 подается адрес следукмцей микрокоманды, а на арифметический блок 19 сигналы микроопераций. Одновре менно разрешается формирование в последуюших тактах сигнала на выходе 44 блока 4 управления. Таким образом восст навливается нормальный режим считывания микрокоманд, описанный выше. Если же при повторном считывании ми рокоманды: в Heit вновь будут обнаружены искажения, то ее считывание повторяется. Как только количество повторений превысит значение, заданное в блоке 23 контроля и позвотшющее сделать вы1вод о том, что причиной искажений микроко.манды является не сбой, а устойчивый отказ в блоке 16 управляющей памйти. то микрокоманда бракуется , и устройство переходит в режим восстановления, в котором осуществляется восстановление забракованной микрокоманды в блоке 16 управляющей памяти путем переписи ее в свободную «гчейку этого блока из блока 6 основной памяти. При этом на выходе 62 блока 23 контроля формируется импульсный единичный сигнал, на его выходах 59 и 63 - постоянные единичные сигналы, а сигнал на 60 принимае нулевое . По сигналу с выхода 6 блока 23 контроля адрес искаженной мик рокоманды подается из регистра 2 в блок 3 формирования адреса который по этому адресу формиру.. адрес соответствующей ячейки блока 6 основной памчгти. Нулевым значение на выходе 6О блока 23 контроля в коммутаторе 15 запрещается подача информации из регистра 21 микрокоманд на арифметический блок 19 и на регистр 2 адреса микрокоманд, а также из блока 6 основной памяти на ари(| ле-тический блок 19. По сигналу с выхода 63 блок 23 запрещается формирование си налов на выходах 4О, 39, 44 блока 4 управления. Устройство переходит в режим восстановления. При поступлении очередного импульса н вход 33 блок 4 управления формирует сигнал на выходе 35, по которому коммутатор 15 подключает группу входов 45 к группе выходов 5О, образуя цепь для подачи информации из блока 6. оСвовной памяти на группу информационных входов 52 блока 16 управляющей памяти. Oднoвpe eннo формируется сигнал на выходе 36 блока 4 управления, по которому из блока 6 основной памяти по адресу, поступившему на его группу выходов 25 через.буферный регистр 5 с группы выходов 27 блока 3 формирования адреса, считывается неискаженное значение микрокоманды. Эта микрокоманда поступает на группу информационных входов 52 блока 16 управлякяцей пакгяти и на группу входов блока 23 контроля, который стробируется сигналом с выхода 36 блока 4 управлейия и осуществляет контроль переписываемой микрокоманды. Одновременно в регистр 2 через группу выходов 28 блока 3 формирования адреса записывается адрес ячейки блока 16 управляющей памяти, еледующей за последней з(ятой ячейкой и являющейся свободной. Этот адрес был сформирован по окончании режима переписи. Из регистра 2 через блок элементов И 8 адрес подается на группу адресных входов 53 блока 16 управляющей памяти. При поступлении очередного тактового импульса на выходе 41 блока- 4 управления формируется сигнал, по которому осуществляется запись считанной микро- команды в свободщто ячейку блока 16 управляющей памяти. При поступлении следующего тактового импульса на выходах 41 и 42 блока 4 управления формируются сигналы, по которым осуществляется изменение адресной части в микрокоманде, которая предшествует искаженной. При этом в нее вместо адреса искаженной микрокоманды из регистра 2 записывается адрес той ячейки, в которой теперь хранится неискаженное значение переписываемой микрокоманды. Тем самым обеспечивается обход отказавшей ячейки блока 16 управляющей памяти прн во мгожном повторном выполнеНИИ микропрограммы. При этом по сигналу на выходе 42 блока 4 управления запирается блок элементов И 8 и отпирают ся блоки элементов И 7 и Ю. Через блок элементоь И 7 из регистра 2 ни труппу информационных входов 52 блока 16 управляющей памяти подается новое значение изменяемой адресной части. Адрес, по которому производится запись информации, поступает на группу адресных входов 53 через блок элементов И 10 из регистра 22. Если при переписи в микрокоманде не было обнаружено искажени, то сигналы ша выходах блока,- 23 контроля ос1510087таются неизменными. При поступлении следующего тактового импульса на блок 4 управления на его выход 38 подается сигнал, по которому в блоке 3 формирования адреса формируется адрес той ячей- j }ки блока 16 управляющей памяти, которая следует за последней занятой ячейкой и является свободной Кроме того, по этому сигналу осуществляется сброс блока 23 Контроля, на выходах которого ю устанавливаются значения сигналов, соответствующие исходному состоянию ройства в рабочем режиме, вследствие чего в коммутаторе 15 осуществляется подключение группы входов 45 к группе is выходов 49 и разрешается подача через него информации из регистра 21 микрокоманд на арифметический блок 19 и на регистр 2 адреса микрокоманд. При поступлении следующего тактового 20 импульса в блоке 4 управления разрешается формирование в следующих тактах сигналов на его выходах 39, 4О и 44. Таким образом, устройство переводится вновь в рабочий режим. В следующем так-25 те КЗ блока 16 управляющей памяти считывается переписанная микрокоманда. Ее адрес был установлен в регистре 2 при переписи. Считывание последующих микрокоманд осуществляется аналогично опи- jo санному выше. Если при переписи в микрокоманде будут обнаружены искажения, то сигнал на. выходе 59 блока 23 контроля принимает нулевое значение и запрещает формирование сигнала на выходе 38 блока 4 управления. Поэтому адреса ячеек блоков 6 и 16 основной и управляющей памяти, сформированные в блоке 3 формирования адреса перед началом переписи микроманды, остаются без изменений. Сброс блока 23 контроля не производится, поэтому комму- татор 15 остается в прежнем состоянии, подключая группу входов 45 к группе выходов 5О. Кроме того, при поступлении следукяцего тактового импульса в блоке 4 управления сохраняется запрет на формирование сигналов на выходах 39, 4О и 44. Вследствие этого, начиная со следующёго такта, повторяется процесс переписи забракованной мшфокоманды в ту же самую ячейку блока 16 управляницей памяти. Как только количество; повторений превысит допустимое значение, сигналы .на выходах 61 и 63 блока 23 контроля принимаютнулевое значение, запрещая формирование сигналов блоком 4 управления и тем самым прекращая работу ройства. 4116 - Блок 4 управления (фиг. 2) работает следующим образом. Пои подаче на вход ЗО сигнала, задающего режима переписи, Ц триггер 64 устанавливается в единичное состоя е. Сигналом на входе 29, разрешающик (|)ункционирование устройства, отпирается элемс::т И 65,выходной сигнал которого поступает на выход 34 и через элем ент ИЛИ 78 - на выход 35, задавая ре жкм- переписи в блоке 23 контроля и коммутаторе 15 соответственно. Так как на выход 61 в исходном для режима пе- . реписи состоянии подан постоянный единичный сигнал, то импульс переписи с входа 32 поступает через элемент И 70 и элемент ИЛИ 79 на выход 36, осуществляя считывание микрокоманд из блока, основной памяти 6 и стробируя блок 3 контроля и блок 3 формирования адреса. Элемент 75 задержйва.ет этот импульс на время, необходимое для считывания информации из блока 6 основной памяти, и через элемент И.ПИ 8О формиРУет на выходе 41 сигнал записи. Элемент 76 задержки через время, необходимое для срабатывания блока 23 контроля, подает на выход 37 сигнал на фррмирование адресов следующих ячеек основной и управляющей памяти в блоке 3 формирования адреса, При поступлении следующего импульса переписи блок работает аналогично. При сбоях алгоритм его работы не изменяется. Если будет зафиксирован отказ блока 6 основной памятн, то нулевым значекк сигнала на входе 3 запрещается формирование импульсов на выходах 36, 37 и 41. При подаче на вход 31 сигнала, задающего рабочий режим, j триггер 64 устанавливается в нуль, и с подачей раз- решающего сигнала на вход 29 отпирается элемент И 66, формируя на выходе 43 постоянный сигнал, по которому выходы регистра 2 адреса микрокоманд подключаются к адресным входам блока 16 управлякнцей памяти. При этом также отпирается элемент И 67. Через него тактовый импульс с входа 33 поступает на выход 40, осуществляя считывание микрокоманды из блока 16 управляющей памяти. Через открытый элемент И 71 импульс поступает также на выход 44 для осуществления переписи адресов в буферные регистры 17 и 22. Элемент 74 задержки через время, необходимое для срабатывания блока 23 контроля, через открытый элемент И 72 формирует им171008741,IS

пульс на выходе 39, разрешая в KoiviMy-Еслирез5 пьтат контроля переписывататоре 15 выдачу информации из регистра емой микрокоманды окажется положитель21 микрокоманд на регистр. 2 адреса микрокоманд и на арифметический блок 19. С приходом следующего тактового импульса цикл работы блока управления повторяется. Если при считывании микрокоманды из блока 16 управл$пощей памяти будет зафик сирован сбой, то нулевым значением сигнала на выходе 59 запираются, элементы И 71 и 72, запрещая формирование на выходах 44 и 39 и обеспечивая тем самы повторение микрокоманды, Ecrai же будет зафиксирован отказ, то- единичным значением сигнала на выходе. 63 запирается -элемент И 67 и отпирается элемент И 69 разрешая загшсь тактовых импульсов в счетчик 81. Тем самым в блоке задается режим восстановления. В этом режиме с приходом первого та тового импульса на выходе 87 дешифрато ра 82 фиксируется сигнал, который поступает через элементы ИЛИ 78 и 79 на выходы 35 и 36, в результате чего на блок 16 управляющей памяти подается адрес свободной ячейки и восстанавливаемая микрокоманда, которая также поступает на блок -23 контроля. Кроме того, на выход 83 дешифратора 82 подается постоянный сигнал, который сохраняется до тех пор, пока счетчик 81 установится в нуль. Этим сигналом отпирается элемент И 68, который теперь независимо от сигналов на входах блока управления обеспечи.вает подачу им пульсов на счетчик 81 до тех пор, пока он установится в нуль. Этим- же сигналом запирается элемент И 67, запрещая пере ход в рабочий режим. С приходом второго тактовеяо импульса на выходе 85 дешифратора 82 формируется сигнал, который через элемент ИЛИ 8О поступает на выход 41 и осуществляется запись восстанавливаемой микрокоманды в блок 16 управляющей памяти, С приходом третьего тактового им пульса на выходе 86 дешифратора 82 формируется сигнал, который поступает на выход 42, осуществляя перекоммута-i. цию информационных и адресных входов блока t6 управляющей памяти, а также на выход 41, осуществляя запись нового адреса в адресную часть микрокоманды, предшествовавшей забракованной. При поступлении четвертого тактового импуЛьса формируется сигнал на выходе : 84 дешифратора 82.ным то этот сигнал через открытый элемент И 73 поступает на выход 38, осуществляя сброс блока 23 контроля и формирование адреса следующей свободной ейки управляющей памяти. С приходом тактового импульса счетчик 81 устанавливается в нуль в результате чего сигнал на выходе 83 дешифратора принимает нулевое значение, запирая элемент И 68 и отпирая элемент И 67, разрешая тем самым формированиев последующих тактах сигналов на выходах 40, 39 .44, зптравляющих режимов. Если же будет зафиксирован сбой в пере 1шсываемой микрокоманде, то с приходом четвертого имцульса сигнал на выходе 38 сформирован не будет так как элемент и 73 будет заперт нулевым сигналом на выходе 59. Поэтому восстановления будет сохранен, и с поступлением шестого тактового импульса повторится цикл пере- записи той же самой микрокоманды. Если же при переписи будет з€ иксирован отказ, то нулевыми значениями сигналов на выходах 63 и 61 будут заперты элементы И 69 и 67 соответственно, вследствие чего выдача управляющих сигналов по окончании последнего цикла переписи будет прекращена. Блок 3 формирования адреса (фиг. 3) работает следующим образом. При переходе в режим переписи в счетчик 92 записывается адрес начальной ячей в счетчик 93 ки основной памяти, а адрес начальной ячейки управляющей памята. По сигналу на выходе 36 блока 4 управления содержимое счетчика 93 че рез блок элементов И 90 подается на группу выходов 28, а содержимое счетчика 92 через группу выходов 27 записывается в буферный регистр 5. При от ;утствии сбоев в переписываемой микрокоманде уп&леяг И 89 остается открытым единичным сигналом на выходе 59, поэтому импульс с входа 37 поступает на динакшческие входы счетчиков 92 и 93 и устанавливает на них адреса следующих, ячеек основной и управляющей памяти соответственно. 1- . Если при перешсси микрокоманды будет зафиксирован |сбой то поступление сигнала на динамические входы счетчика запрещается нулевым синапом на выходе 59, запрещающим злементол И 89. При отказах сиг.нал на выходе 37 не формируется.

образом, на счетчике 93 будет установлен адрес очередной свобЬдной ячейки управляющей памяти.

В рехшме восстановления по сигналу на выходе 62 отпирается блок элементов Н 88, подавая с группы выходов 26 на шифратор 94 адрес управляющей памяти, в которой записана забракованная микрокоманда. По этому адресу шифратор 94 формйрует адрес соответствующей ячейки ос-ионной памяти и устанавливает его на счетчике 92 через группу входов. Затем по сигналу на выходе 36 из счетчика 93 на группу выходов 28 подается адрес свободной ячейки управляющей памяти. Затем по сигналу на выходе 38 содержимое счетчика увеличивается на единицу, задавая адрес очередной свободной ячейки управляющей памяти. Коммутатор 15 (фиг. 4} работает еледующим образом. В режиме переписи на его выходы- 35 и 60 подаются единичные сигналы, вследствие чего блоки элементов И 98, 100 и 103 запираются, а блоки элементов И 99 и 101 отпираются, подключая группу выходов 44 к группе выходов 50, В рабочем режиме сигнал на выходе 3 принимает нулевое значение, вследствие чего блоки И 99 и 101 запираются, а блоки элементов И 98 и ЮО отпираются образуя цепи для подачи информации с группы входов 45 на группу выходов 49, При этом адрес начальной микрокоманды подается через блок элементов ИЛИ 105 также и на группу выходов 51. При подаче разрещакте его сигнала на выход 39 отпираются блоки элементов И 102 и 103, подавая с группы вы-ходов 57 сигналы микроопераций на груп пу выходов 49, а код адреса следующей микрокоманды - через блоки элементов И 1О4 и ИЛИ 1О5 - на группу выходов 51. При этом осуществляется модифика i дня адреса сигналами на группе выходов 56. При переходе в режим восстановления сигнал на выходе 60 становится равным нулю и запирает, блоки элементов И 98, 100, 102- и 1бЗ. По подаче сиг нала на выход 35 отпираются блоки элементов И 99 и 101, обеспечивая подачу информашш с группы входов 45 на группу выходов 50, Блок контропя (фиг. 5) работает еледующим образом. В режиме переписи на его выход 34 подается постоянный сигнал, который отмикрокоманда с группы выходов 50 через блок элементов ИЛИ 106 подается на узел 110 контроля четности, который при отсутствии искажений формирует на выходе нулевой сигнал, а при наличии искажений - единичный. Одновременно с подач :й переписываемой микрокоманды подается импульс опроса на выход 36. Он задерживается элементом 117 задфжки на время, равное времени срабатывания узла 110 контроля четности и поступает на вх&д элемента И 113. При положительном результате контроля элемент будет заперт, счетчик 124 останется в нулевом состоянии, вследствие чего cnf ал на выходах дешифратора 122 сохраняет нулевое значение, а сигнал на выходе блока контроля - единичное. Затем импульс опроса, пройдя через элемент ® задержки через время, необходимое для срабатывания счетчика 124 и дешифрафор 122 через открытый элемент И 114 и ИЛИ 1О8 поступит на вход счетчика 124 для установки его в нуль. При отрицательном результате контроля элемент И 113 будет открыт сиг- налом на входе со схемы контроля четное ти импульса опроса, счетчик 124 установится в единицу. Сигнал на выходе дешифратора 122 станет единичным, а на выходе 59 блока контроля - нулевым. Так как элемент И 114 будет заперт по инверсному входу единичным сигналом с выхода уЗла 110 контроля четности, то сброс счетчика 124 не произойдет., Если же при повторной переписи результат контроля окажется- положительным, то элемент И 114 откроется, вследствие че Го счетчик 124 будет установлен в ну71ь, сигнал на выходе дешифратора станет нулевым, а на выходе 59 блока контроля - единичным. Если же Щ5И повторно nspemictii результат контроля вновь окажется отрицательным, то число, установлошое на счетчике 124, станет равно двум и т, д, Как только это число станет больше допустимого, в блоке контроля фиксируется отказ. Сигнал на выходе дешифратора становится равным единице, отпирая элементы И 115 и 111. Через элементы И 111 и ИЛИ 109 триггер 121 устанавливается в единицу, и сигнал на выходе 61 становится нулевым, блокируя работу устройства. Импульс опроса через элемент И 115 установит счетчик 124 в нуль, вследствие чего сигналы на выходах дешифратора 12О станут нуле2110выми. Для разрешения дальнейшего функц онирования устройства триггер I2t должен быть установлен в нуль. В рабочем режиме и режиме восста в ления на выход 34 блока 23 контроля подается нулевой сигнал, запирающий элемент И 111 и отшфаюпшй элемент И 112, Контроль микрокоманды, поступающей на группу вьпсодов 54, и подсчет количества ее повторных, считываний осушествляется аналогично вышеописанному по импульсам опроса, подаваемым на выход 4О. Как только это количество станет больше допустимого в блоке контроля фиксируется отказ. При этом по сигналу с выхода дешифратора 122 разрешается установка счетчика 124 в нуль, на выходе 62 формируется единичный сиг нал, триггер 12О устанавливается в единицу, в результате чего сигнал на выходе 63 становится единичным, а на выходе 6О - нулевым. Тем самым в устройстве задается режим восстановления. Если при восстановлении результат контроля переписываемой мшсрокомавд& окажется положительным, то на выход 38 поступает импульс сброса, по которому триггер 12О устанавливается в нуль. 4122 обеспечивая восстановлетге в блоке контроля состояния, являющееся исходным для рабочего ренсима. ЕСЛИ же при восстановлении количество повторных ,иик- лов переписи станет больше допустимого, то сигнал с Ьыхода дешифратора 122 пос.тупит через элементы И112, 116и ИЛИ 1О9 на триггер 121 и установит его в единицу. Оигнал на выходе 61 становится нулевым, блокируя функционирование устройства. Таким образом, в устройстве осуществляется койтроль микрокоманды при переписи их в бпок управляющей памяти и счить1вании из него. При этом обеспечи ается восстанотзление микрокоманд: сбоях путем их повторения, а при отказах ячеек блока управляющей памяти путем п еписи неискаженного значения микрокоманды из блока осношюй памяти в свободную ячейку бло1а управляющей памяти с обеспечением обхода отказавших 5гчеек и внесения соответствующих изменений в адресной части предшествовавшей ей микрокоманды, после чего продолжается нормальное выполнение следующих микрокоманд. За счет этого достигается повышение отказоустойчивости устройства.

т

/ТУ

/3

/ /J6

о

О 50 3/ 3 Л

/

CPU9.1

ав

95

S9

85

У7

91

7(риг-J

Т

(РигЛ

/5

N

27

зг

26

И

SO

X

| I | |||

| Микропрограммный процессор с восстановлением при сбоях | 1977 |

|

SU656066A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ДОПОЛНИТЕЛЬНОЕ ОПОРНОЕ УСТРОЙСТВО ДЛЯ ПЛЕЧ И СПИНЫ ВЕЛОСИПЕДИСТА | 2010 |

|

RU2503575C2 |

| (прототип). | |||

Авторы

Даты

1983-03-30—Публикация

1981-02-10—Подача