Изобретение относится к сбору и обработке данных, в частности к устройствам коммутации сообщений и пакетов в сетях ЭВМ.

Известны устройства для формирования кода маршрута в цифровой сети связи с использованием мини-ЭВМ 1.

Недостатками устройств являются высокая стоимость, сложность и сравнительно низкая надежность.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее генератор тактовых импульсов, группу элементов И, группу регистров адресов соседних узлов, счетчик, вход которого соединен с выходом генератора тактовых импульсов, а его вьог-оды - с первыми входами элементов И группы, выходы которых соединены с прямыми входами регистров группы 2

Недостатком устройства является низкая эффективность, обусловленная формированием маршрутов с минимгшьным чисТЕом межузловых связей между узлом отправления и узлом назначения, что не исключает больших временных задержек в промежуточных узлах сети.

Цепь изобретения - повышение быстродействия работы устройства путем

формирования маршрутов между узлагли сети по критерию минимума потерь времени на передачу сообщения.

Поставленная цель достигается тем, что в вычислительное устройство для формирования маряпрута сообщения, содержащее блок управления, генератор тактовых импульсов, счетчик, группу элементов И, группу регистров адре10сов соседних узлов, выходы которых являются выходом устройства, информёщионный вход каждого регистра группы подключен к выходу соответствующего элемента И группы, информаци15онные входы всех элементов И группы объединены и подключены к входу блока управления и выходу счетчика, тактовый вход которого соединен с выходом генератора тактовых импуль20сов, первый и второй выходы блока управления подключены к управляющим входам генератора тактовых импульсов и счетчика соответственно введены группа блоков сравнения и

25 коммутатор, третий вход блока управления подключен к управляющему входу коммутатора, первая группа информационных входов которого является группой входов устройства; вторая

30 группа информационных входов коммутатора соединена с группой выходов счетчика, каждый выход группы выходов коммутатора подключен к первому входу соответствующего блока сравнения группы, второй и третий входы каждого блока сравнения группы объединены и подключены к четвертому и пятому выходам блока управления, первый и второй выходы каждого блока сравнения группы подключены к управляющим входам соответствующих элементов И и регистров адресов соседних узлов .|

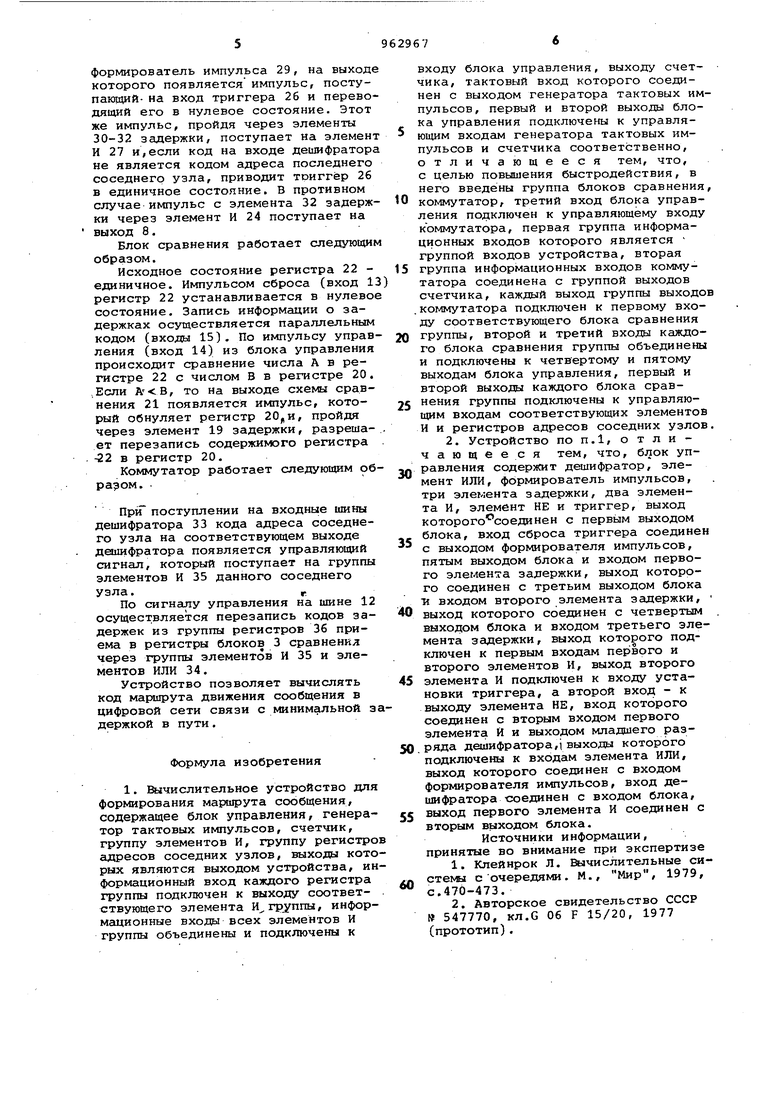

Блок управления содержит дешнф- ратор, элемент ИЛИ, формирователь импульсов, три элемента задержки, два элемента И, элемент НЕ и триггер, выход которого соединен с первым выходом блока, вход сброса триггера соединен с выходом формирователя импульсов, пятым выходом блока и входом первого элемента задержки, выход которого соединен с третьим выходом блока и входом второго элемента задержки, выход которого соединен с четвертым выходом блока и входом третьего элемента задержки, выход которого подключен к первым входам первого и второго элементов И, выход второго элемента И подключен к входу установки триггера, а второй вход - -к выходу элемента НЕ, вхоц которого соединен с вторым входом первого элемента И и выходом младшего разряда дешифратора, выходы которого подключены к входам элемента ИЛИ, выход которого соединен с входом формирователя импульсов вход дешифратора соединен с входом блока, выход первого элемента И соединен с вторым выходом блока.

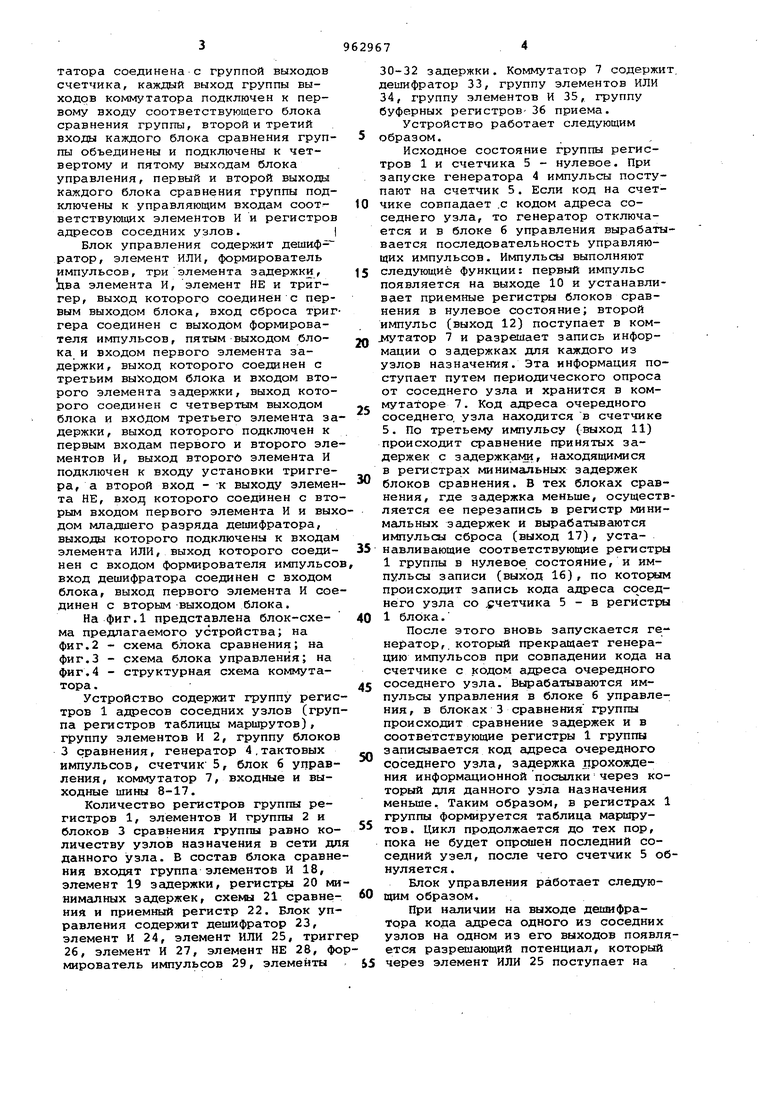

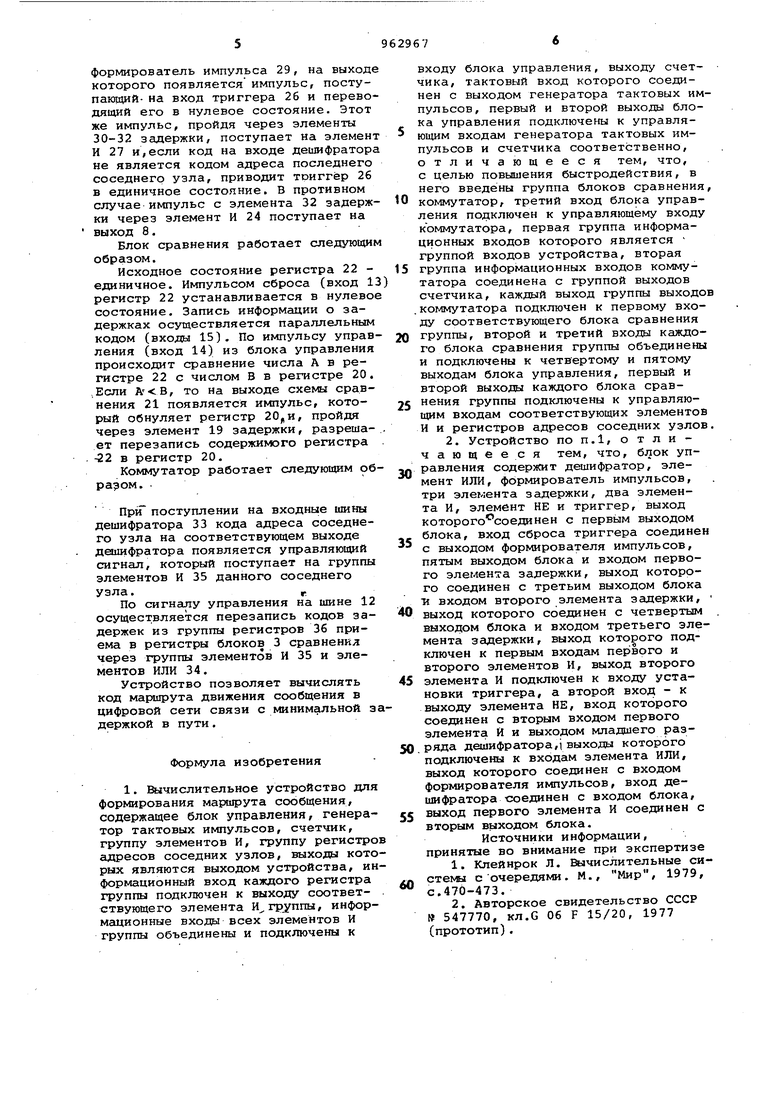

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 - схема блока сравнения; на фиг.З - схема блока управления; на фиг.4 - структурная схема коммутатора .

Устройство содержит группу регистров 1 адресов соседних узлов (группа регистров таблицы маршрутов), группу элементов И 2, группу блоков 3 сравнения, генератор 4,тактовых импульсов, счетчик 5, блок 6 управЛенин, коммутатор 7, входные и выходные шины 8-17.

Количество регистров группы регистров 1, элементов И rpiynnn 2 и блоков 3 сравнения группы равно количеству узлов назначения в сети для данного узла. В состав блока сравнения входят группа элементов И 18, элемент 19 задержки, регистры 20 мияималных задержек, схемы 21 сравнеНИИ и приемный регистр 22. Блок управления содержит дешифратор 23, элемент И 24, элемент ИЛИ 25, тригге 26, элемент И 27, элемент НЕ 28, формирователь импульсов 29, элементы

30-32 задержки. Коммутатор 7 содержи дешифратор 33, группу элементов ИЛИ 34, группу элементов И 35, группу буферных регистров- 36 приема.

Устройство работает следующим образом.

Исходное состояние группы регистров 1 и счетчика 5 - нулевое. При запуске генератора 4 импульсы поступают на счетчик 5. Если код на счетчике совпадает .с кодом адреса соседнего узла, то генератор отключается и в блоке 6 управления вырабатывается последовательность управляющих импульсов. Импульсы выполняют следующие функции: первый импульс появляется на выходе 10 и устанавливает приемные регистры блоков сравнения в нулевое состояние; второй импульс (выход 12) поступает в ком 1утатор 7 и разрешает запись информации о задержках для каждого из узлов назначения. Эта информация поступает путем периодического опроса от соседнего узла и хранится в коммутаторе 7. Код адреса очередного соседнего, узла находится в счетчике 5. По третьему импульсу (выход 11) происходит сравнение принятых задержек с задержка1«ш, находящимися в регистрах минимальных задержек блоков сравнения. В тех блоках сравнения, где задержка меньше, осуществляется ее перезапись в регистр минимальных задержек и вырабатываются импульсы сброса (выход 17), устанавливающие соответствующие регистры 1 группы в нулевое состояние, и импульсы записи (выход 16), по которым происходит запись кода адреса соседнего узла со учетчика 5 - в регистры 1 блока.

После этого вновь запускается генератор , который прекращает генерацию импульсов при совпадении кода на счетчике с кодом адреса очередного соседнего узла. Вырабатываются импульсы управления в блоке 6 управления, в блоках 3 сравнения группы происходит сравнение задержек и в соответствующие регистры 1 группы записывается код адреса очередного соседнего узла, задержка прохождения информационной посылки через который для данного узла назначения меньше. Таким образом, в регистрах 1 группы формируется таблица маршрутов. Цикл продолжается до тех пор, пока не будет опрсяиен последний соседний узел, после чего счетчик 5 обнуляется .

Блок управления работает следующим образом.

При наличии на выходе дешифратрра кода адреса одного из соседних узлов на одном из его выходов появляется разрешающий потенциал, который через элемент ИЛИ 25 поступает на формирователь импульса 29, на выход которого появляется импульс, поступающий- на вход триггера 26 и перево дящий его в нулевое состояние. Этот же импульс, пройдя через элементы 30-32 задержки, поступает на элемен И 27 и,если код на входе дешифратор не является кодом адреса последнего соседнего узла, приводит триггер 26 в единичное состояние. В противном случае импульс с элемента 32 задерж ки через элемент И 24 поступает на выход 8. Блок сравнения работает следующи образом. Исходное состояние регистра 22 единичное. Импульсом сброса (вход 1 регистр 22 устанавливается в нулево состояние. Запись информгщии о задержках осуществляется параллельным кодом (входы 15). По импульсу управ ления (вход 14) из блока управления происходит сравнение числа А в регистре 22 с числом В в регистре 20. .Если , то на выходе схемы сравнения 21 появляется импульс, который обнуляет регистр , пройдя через элемент 19 задержки, разрешает перезапись содержимого регистра -22 в регистр 20. Коммутатор работает следующим об разом. При поступлении на входные шины дешифратора 33 кода адреса соседнего узла на соответствующем выходе дешифратора появляется управляющий сигнал, который поступает на группы элементов И 35 данного соседнего узла. По сигналу управления на шине 12 осуществляется перезапись кодов задержек из группы регистров 36 приема в регистры блоков 3 сравнения через группы элементов И 35 и элементов ИЛИ 34. Устройство позволяет вычислять код маряцрута движения сообщения в цифровой сети связи с минимальной з держкой в пути. Формула изобретения 1. Вычислительное устройство для формирования маршрута сообщения, содержащее блок управления, генератор тактовых импульсов, счетчик, группу элементов И, группу регистро адресов соседних узлов, выходы кото рых являются выходом устройства, ин формационный вход каждого регистра группы подключен к выходу соответствующего элемента И группы, инфорМсщионные входы всех элементов И группы объединены и подключены к входу блока управления, выходу счетчика, тактовый вход которого соединен с выходом генератора тактовых импульсов, первый и второй выходы блока управления подключены к управляющим входам генератора тактовых импульсов и счетчика соответственно, отличающееся тем, что, с целью повьлшения быстродействия, в него введены группа блоков сравнения, коммутатор, третий вход блока управления подключен к управляющему входу коммутатора, первая группа информационных входов которого является группой входов устройства, вторая группа информационных входов коммутатора соединена с группой выходов счетчика, каждый выход группы выходов коммутатора подключен к первому входу соответствующего блока сравнения группы, второй и третий входы каждого блока сравнения группы объединены и подключены к четвертому и пятому выходам блока управления, первый и второй выходы каждого блока сравнения группы подключены к управляющим входам соответствующих элементов И и регистров адресов соседних узлов. 2. Устройство по П.1, отличающееся тем, что, блок управления содержит дешифратор, элемент ИЛИ, формирователь импульсов, три элемента задержки, два элемента И, элемент НЕ и триггер, выход которого соединен с первым выходом блока, вход сброса триггера соединен с выходом формирователя импульсов, пятым выходом блока и входом первого элемента задержки, выход которого соединен с третьим выходом блока и входом второго элемента задержки, выход которого соединен с четвертым выходом блока и входом третьего элемента задержки, выход которого подключен к первым входам первого и второго элементов И, выход второго элемента И подключен к входу установки триггера, а второй вход - к выходу элемента НЕ, вход которого соединен с вторым входом первого элемента И и выходом младшего разряда дешифратора, выходы которого подключены к входам элемента ИЛИ, выход которого соединен с входом формирователя импульсов, вход дешифратора соединен с входом блока, выход первого элемента И соединен с вторым выходом блока. Источники информации, принятые во внимание при экспертизе 1.Клейнрок Л. Вычислительные систекы с очередями. М., Мир, 1979, с.470-473. 2,Авторское свидетельство СССР 547770, кл.С 06 F 15/20, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для формирования маршрута сообщения | 1982 |

|

SU1037269A1 |

| Вычислительное устройство для формирования маршрута сообщения | 1982 |

|

SU1049917A1 |

| Устройство для подсчета количества изображений объектов | 1986 |

|

SU1383413A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1325501A1 |

| Устройство для моделирования узлов коммутации сообщений | 1986 |

|

SU1354203A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Устройство для моделирования маршрутов сообщений и управления процессом коммутации в сети связи | 1980 |

|

SU922757A1 |

jik:

(г

dz:

16

17

1

If

fr

IS

IffI I I I II

fZ

11

Фиг.1

/io2i

18

W

16

Фиг. 2.

.3

Авторы

Даты

1982-09-30—Публикация

1980-12-22—Подача