быстродействия устройства. Устройство содержит группу блоков 1.1,..., 1.8 буферной памяти, три регистра 2,3,4, триггер 5, счетчик 6, блок 7 сравнения, блок 8 выбора направлений генератор 9 тактовых импульсов, группу ключей 10.1,..,,10.8, мультиплексор 11, дешифратор 12, два элемента И 13, 14, группу элементов И 15.1,...,15.8, три элемента ИЛИ 16, 17, 18, три одновибратора 19, 20, 21 и два элемента задержки 22, 23. Сущность изобретения заключается в следующем. Каждый процессорный элемент (ПЭ) в массиве имеет свой адрес (номер строки и столбца), по которому он может идентифицироваться по отношению к другим ПЭ в массиве . Возможны транзитные передачи между ПЭ в массиве по восьми направлеИзобретение относится к вычислительной технике и может быть использовано при пос троении высокопроизводительных матричных, конвейерных, систолических, векторных и других процессоров, в которых в процессе обработки информации происходит движение данных в вычислительной среде.

Цель изобретения - увеличение быстродействия устройства.

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - 4 - функциональные схемы блока сравнения, блока выбора направлений и блока буферной памяти соответственно; на фиг. 5 - временные диаграммы работы устройства; на фиг. 6 - примеры возможных путей прохождения данных между произвольными процессорными элементами (ПЭ) в массиве с использованием предлагаемых устройств.

Устройство (фиг. 1) содержит группу блоков 1 .1, .. .,1 .8 буферной памяти типа первым вошел, первым .вьтел первьй регистр 2, второй регистр 3, третий регистр 4, триггер 5, счетчик 6, блок 7 сравнения, блок 8 выбора направления, генератор 9 тактовых импульсов, демультиплексор, выполненный на группе ключей 10.1,...,10.8

ниям. Предлагаемое устройство позволяет проводить обмен информацией между ПЭ в массиве с учетом кратчайшего геометрического пути и минимальной временной задержки за счет выбора и модификации адреса передачи в каждом транзитном ПЭ массива. Если ПЭ, которомуадресована передаваемая информацияJ- соседний, то передача информации происходит непосредственно без модификации, которая учитывает загрузку направлений сектора передачи. Таким образом, секторизация пространства передач и одновременный анализ загрузки направлений передач позволяет с помощью предлагаемого устройства повысить производитель- .ность и .расширить область его целесообразного использования. 6 ил.

мультиплексор 11, дешифратор 12,первый и второй элементы И 13 и 14, группу 15 .1, . . .,15.8 элементов И, первый, второй и третий элементы ИЛИ

16, 17 и 18, первьш одновибратор 19 по фронту импульса, второй 20 и третий 21 одновибраторы по срезу импульса и первый и второй элементы 22 и 23 задержки. Кроме того, на фиг. 1 показаны вход 24 задания адреса устройства, информационные входы 25.1, ...,25.8 от соседних устройств,вход 26 сброса и вход 27 запуска, а также выходы 28.1,...,28.8 к соседним устройствам и выход 29 к ПЭ.

Блок 7 сравнения (фиг. 2) содержит группу схем 30.1,,. . ,30.16 сравнения, первую и вторую группы элементов ИЛИ 3 1 . 1 ,... ,31 . 16 и 32.1, ...,32.16,

Блок 8 выбора направлений (фиг. 3) содержит узел 33 памяти константы, первый и второй вычитатели 34 и 35,

с первой по четвертую схемы 36 - 39 сравнения, дешифратор, выполненный на первой и второй группах элементов И 40,1,.., ,40.9 и 41 .1,.. .,41.8, группе блоков элементов И 42.1,...,

42.8, группе элементов ИЛИ 43.1,,.., 43.8 и с первого по третий элементах И 44 - 46, элементе ИЛИ 47 и

312

элементе 48 задержки. Каждый блок 1.1, . . ., 1 .8 буферной памяти группь содержит группу регистров 49.1,..,, 49.п, реверсивный счетчик 50 загрузки, первую и вторую группы клю- чей 51.1,...,51.п и 52.1,...,52.П, группу блоков элементов ИЛИ 53.1, ...,53.п-1, первую и вторую группы элементов ИЛИ 54.1,...,54.п и 55.1,...,55.п, группу элементов И 56.1,...,56.п, с первого по четвертый элементы И 57 60.

Группа.блоков 1.1,..., 1.8 предназначена для организации очередей данных, поступающих от восьми со- седних устройств и индикации коэффициента загрузки этих очередей. Первый 2 и второй 3 регистры предназ- начены для хранения адресной и операционной части информации соответст венно во время выбора направления передачи информации. Третий регистр 4 служит для хранения информации, адресованной ПЭ данного устройства. Триггер 5 предназначен для индика- ции наличия информации в блоках 1.1, ...,1.8. Счетчик 6, дешифратор 12 и обусловленные ими связи служат для последовательного цикличного опроса блоков 1 .1, .. . ,1 8. Блок 7 пред назначен для определения наименее загруженного направления в каждом из восьми секторов возможных передач информации. Блок 8 служит для выбора и модификации напра вления передачи поступившей информации.Генератор 9 предназначен для задания двух противофазных последовательностей импульсов, которые задают синхронизацию устройства. Группа клю чей 10.1,...1p.8 предназначена для выдачи пришедшей информации на соседние устройства регулярной однородной структуры. Мультиплексор 11, группа элементов И 15.1,...,15.8, третий элемент ИЛИ 18 и обусловленные ими связи задают запись информации в регистры 2 и 3 от восьми возможных источников информации - соседних аналогичных устройств. Пер- вый элемент И 13 служит для разрешения опроса блоков 1.1,...,1.8, если их очереди не пусты. Второй элемент И 14 предназначен для разреше- ния вьздачи информации по выбранному направлению, если очереди блоков 1.1, . ..,1.8 не пусты. Первый элемент ИЛИ .16 служит для сборки сигналов

724

обнуления счетчика 6. Второй элемент ИЛИ 17, первый одновибратор 19 по фронту импульса, второй одновибратор 20 по срезу импульса и обусловленные ими связи предназначены для задания .единичного и нулевого состояния триггера 5. Третий одновибратор по срезу импульса служит для задания работы счетчика 6 по модулю восемь с целью циклического опроса блоков 1 . 1, . . ., 1.8. Первый элемент 22 задержки служит для задержки закрытия элемента И 14 нулевым сигналом с прямого вьгхода триггера 5 на время выдачи поступившей информации по выходам 28.1, . . . ,28.8 устройства на соседние,устройства регулярной структуры .

Второй элемент 23 задержки обусловлен переходными процессами счетчика 6, дешифратора 12 и мультиплексора 11 и служит для корректной записи принятой информации в регистры 2 и 3 устройства.

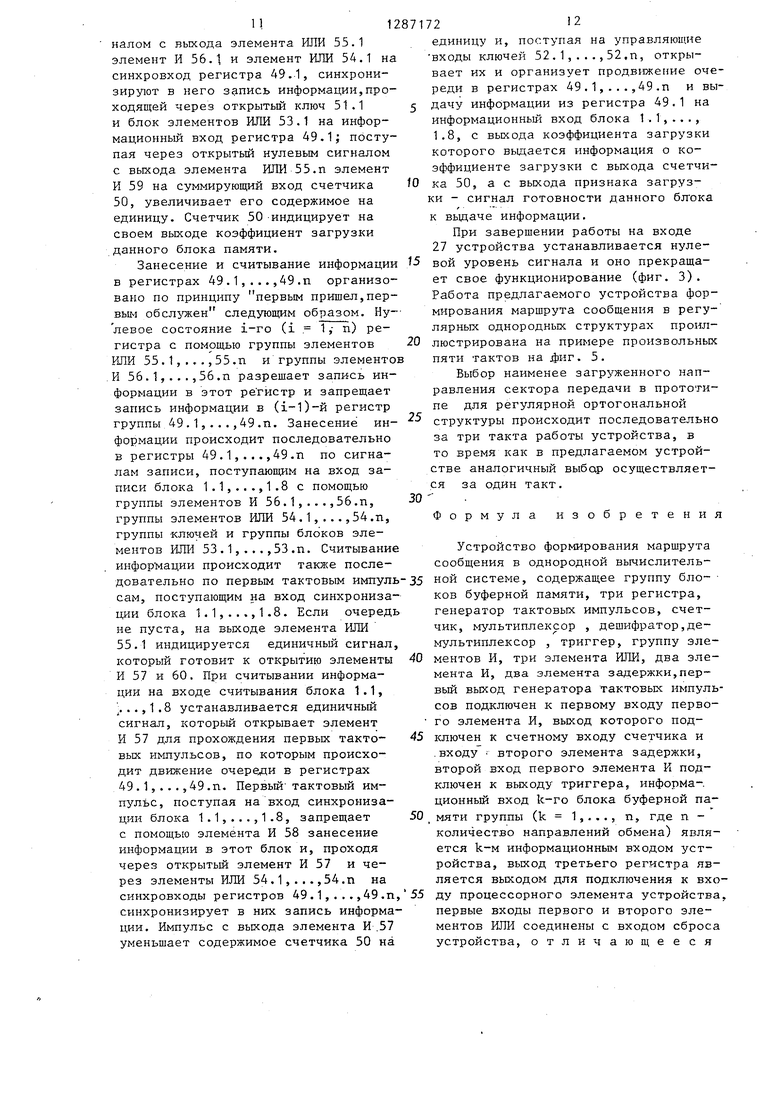

Сихронизация работы предлагаемого устройства происходит по импульсам, которые формируются на первом и втором выходе генератору 9 и представляют собой две противофазные- импульсные последовательности. Такт работы устройства состоит из первого и второго тактовых импульсов, вьщаваемых соответственно с первого и второго выходов генератора 9 (фиг. 5). По первому тактовому импульсу происходит запись принятой информации из блоков 1.1,. ..,1.8 через мультиплексор 11 В регистры 2 и 3 устройства. По второму тактовому импульсу осуществляется выбор и модификация направления дальнейшей передачи принятой информации. Временные диаграммы работы основных элементов предлагаемого устройства без учёта непринципиальных для его функционирования задержек показаны на фиг. 5.

Рассматривается работа предлагаемого устройства формирования маршрута сообщения в регулярньк однородных структурах.

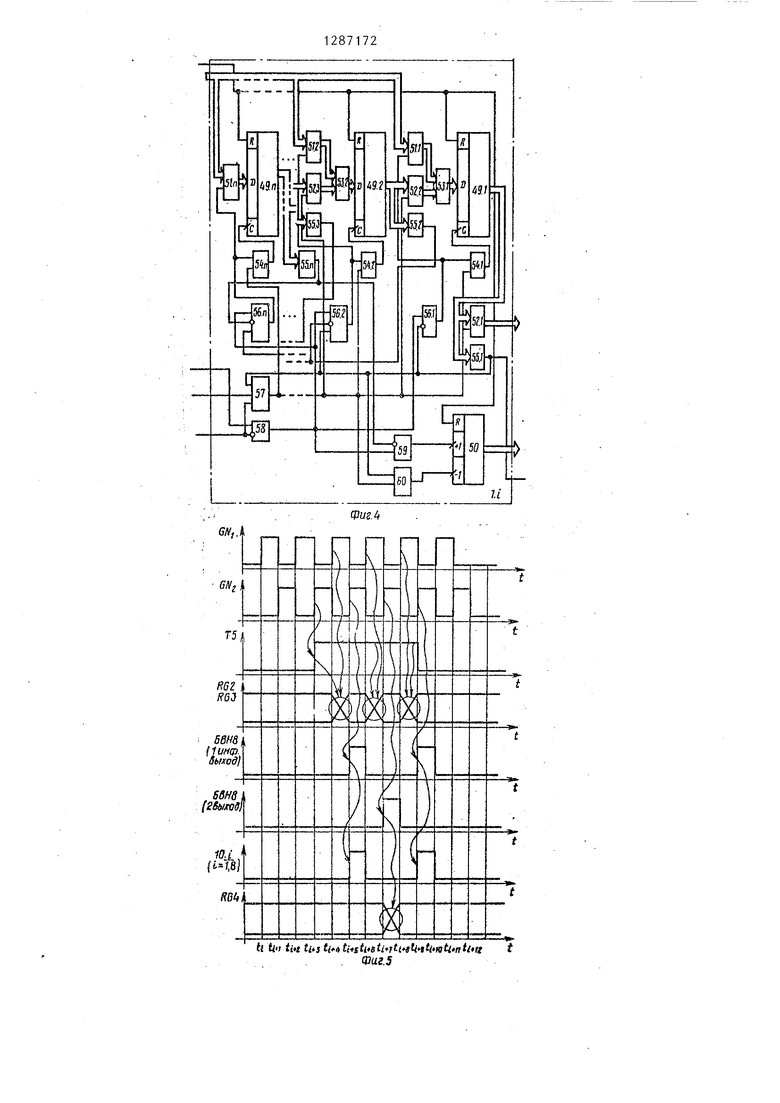

Передача информации между любыг.1И ПЭ в регулярной однородной структуре осуществляется транзитным способом через другие ПЭ массива, например, по восьми возможным направлениям с помощью предлагаемого устройства. Каждому ПЭ в системе (предлагаемому устройству) присваивается определен

512

ный адрес-.(номер строки и номер стол бца в матрице процессорных элемен-- тов), по которому он может идентифицироваться по отношению к другим ПЭ массива. Передающаяся-информация со стоит из двух частей - операционной и адресной. Адресная часть представляет собой код адреса ПЭ, которому предназначена данная операционная часть. Выбор направления передачи .пришедшей информации в предлагаемом |устройстве происходит следующим образом. Адресная часть пришедшей информации сравнивается с адресом данного устройства по номерам строки и столбца и определяется одно из девяти ВОЗМОЖНЫ5С направлений передачи (восемь направлений - на соседние ПЭ, девятое - на обработку данному ПЭ). Одновременно с этим блок 1 сравнения определяет- наименее загруженные направления для всех восьми секторов передачи данных, информация с которого модифицирует выбраное направление передачи данных в блоке 8 выбора направления. Например, для направления Восток анализируются на загрузку три направлени зтого сектора (фиг. 1): Юго-Восток (Ю-В), Восток(В) и Северо- Восток (е-В), для направления Ю-В анализируются направления Б, Ю-В и Юг (Ю) и т.д. Алгоритм выбора минимально загрузкенного направления в каждом из восьми секторов рассмат ривается на примере сектора направления Восток. Пусть коэффициенты загрузки направлений этого сектора следующие: для направления С-В рано А, для направления В - В, для направления Ю-В -- С (под коэффициентом загрузки направления понимается длина очереди в блоке 1.i в соседнем ПЭ по соответствующему направлению) . Если (Б 5 А) А (в 6С) 1, то направлением передачи в этом секторе является в, если (А В)Л (А

и с)- 1, то направление передачи в секторе В определяется направл ени ем С-В, если (С А)Л (А i В) 1, то направление передачи в этом секторе определяется направлением Ю-В Эта информация модифицируется в бл ке 8 направление выбранного сектора

передачи данных. Таким образом дости- 55мент ИЛИ 17 и одновибратор 19 уста- гается .выбор направления передачи ни-н авливает триггер 5 в единичное сое- формации в массиве процессорных эле-тояние. Появившийся единичный уро- меитов по кратчайшему пути с минималь-вень сигнала на прямом выходе триг5

. ной O 5 0 35 45

50

0

задержкой. Особенность алгоритма секторизации - пространства передач, который учитывает как выбор направления передачи, так и временной фактор, заключается в обязательном достижении адресованной информации необходимого ПЭ в массиве (фиг. 1 и 2). Исключение тупиковой ситуации, когда адресуемьш ПЭ - соседний с максимальной задержкой по этому направлению, достигается введением средств в блок 8, которые не позволяют производить модификацию направления передачи в зависимости от загрузки направлений, -если разница между индексами строк и столбцов сравниваемых адресов не превышает единицы. i Перед началом работы на вход 26 устройства подается единичный импульс, который обнуляет все динамические элементы памяти устройства. Одновременно с этим на входе 24 устройства устанавливается код адреса (код строки и код столбца) данного устройства относительно других устройств в регулярной однородной структуре (фиг. 6).

На входе 27 устройства устанавливается единичный уровень сигнала,который запускает генератор 9 тактовых импульсов, на первом и втором выходах которого вырабатываются противофазные импульсные последовательности. При отсутствии информации в блоках 1.1,...,1.8 (входные очереди запросов пусты) на выходах признаков загрузки этих блоков индицируются нулевые сигналы, которые не изменяют нулевое состояние триггера 5, и нулевой сигнал с его прямого выхода запрещает прохождение тактовых импульсов, с генератора 9 через элементы И 13 и 14, запрещая тем самым сдвиг очередей в блоках 1.1,..., 1.8 и выбор направления передачи информации в блок 8.

При поступлении информации от со- . седних ПЭ однородной структуры (например, при передаче данных между процессорными элементами в систолическом массиве) на выходе признака загрузки по крайней мере одного из блоков 1.1,..., 1 .8 появляется единичный сигнал, который через эле71

гера 5 открывает элементы И 13 и 14 для прохождения тактовых импульсов с генератора 9. Первый тактовый импульс генератора 9, проходя через открытый элемент И 13, увеличивает содержимое счетчика 6 на единицу, вследствие чего на втором выходе дешифратора 12 индицируется единичный сигнал, а мультиплексор 11 подготавливается к работе по второму вхо- ду. Если очередь в блоке 1.2 буферной памяти группы не пуста, то единичный сигнал с выхода признака загрузки этого блока поступает на вход элемента И 15.2 группы, откры- вая его и устанавливая через элемент ИЛИ 18 в открытое состояние мультиплексор 11 (в противном случае мультиплексор 11 остается в закрытом состоянии) . Первый такто- вый импульс, задержанный на элементе 23 задержки на время переходных процессов счетчика 6, дешифратора 12 и мультиплексора 11V поступает на входы синхронизации блоков 1. 1,... 1.8 и входы синхронизации регистров 2 и 3 и производит в них запись из того блока 1.1,.л,1.85 на входе считывания которого присутствует единич

ный сигнал с соответствующего выхода

дешифратора 12. Аналогичным образом происходит последовательный циклич- ньш опрос блоков 1.1,...,1.8 и считывание из них информации в регистры 2 и 3 по первым тактовым импуль- сам. Считьшаемая информация из блоков 1.1,...,1.8 состоит из двух частей - адресной и операционной,которая соответственно заносится в регистры 2 и 3. Одновременно с этим блок 7 для каждого сектора восьми возможных направлений определяет наименее загруженное направление и вьщает соответствующие сигналы на блок 8..

По второму тактовому импульсу, поступающему через открытый элемент И 14 на блок 8, происходит выбор и модификация направления передачи информации, вследствие чего в блоке 8 вырабатывается унитарный код,соответствующий определенному направлению передачи информации (или на один из восьми соседних устройст или на обработку ПЭ данного устрой- ства). В зависимости от унитарного кода во время второго тактового импульса происходит выдача принятой на переда гу информации или на сосед

8

-5 О

5

0

5 О 5

0 5

нее устройство через определенный ключ.И 10, 1, . . .,10.8 группы, или на ПЭ данного устройства, переписывая принятую информацию из регистров 2 и 3 в регистр 4, с выхода которого она вьщается на выход 29 устройства непосредственно на обработку данному ПЭ.

Информационные выходы ключей 10.1,...,10.8 и выходы коэффициентов загрузки соответствующих блоков 1 . 1, . . .,1 .8, которые определяют коэффициенты загрузки этих блоков, образуют информационные выходы 28.1,..., 28.8 устройства, которые подключены к соответствующим восьми соседним устройствам в регулярной однородной структуре.

Если все передачи информации от соседних устройств обслужены, то на выходе элемента ИЛИ 17 устанавливается нулевой уровень сигнала, который через одновибратор 20 сбрасывает триггер 5 в нулевое состояние. Элементы И 13 и 14 закрываются нулевым сигналом с прямого выхода триггера 5, и устройство переходит в режим ожидания поступления.следующей информации в блоки 1 .1, . . ., 1 .8 . При пос- тупл ении очередной информации от со- седних устройств работа предлагаемого устройства формирования маршрута сообщения в регулярных однородных структурах протекает аналогично указанному.

Рассматривается функционирование блока 7 сравнения (фиг. 2).

На информационные входы блока 7 поступают коэффициенты загрузки соответствующих направлений от соседних аналогичных устройств.Выход признаков блока 7 состоит из сорока восьми линий таким образом, что каждому из восьми направлений соответствует три шины из двзтс линий для каждого сектора, состоящего из трех направлений, формируются единичные сигналы на линиях второй шины, если выполняется условие (В А) (/ $ : С) 1, на линиях первой шины - при условии (А в) А (А 6 С) 1 и на линиях третьей шины - в случае если (С А) Л (А В) 1, где А,В и С являются коэффициентами загрузки соответствующих трех направлений в секторе. Информация с выхода блока 7 используется для модификации выбора направления передачи с учетом загрузки направлений в сек

912

торе, что происходит в блоке 8 выбора направлений.

Рассматривается работа блока 8 (фиг. 3).

По второму тактовому импульсу с второго выхода генератора 9 инициируется процесс выбора и модификации направления передачи данных (если триггер 5 находится в единичном состоянии, что открывает элемент И 14). Этот импульс с выхода элемента И 14 поступает на входы стробирования первого 34 и второго 35 вычитателей, разрешая их работу, и на вход стробирования считывания узла 33, который постоянно хранит (без разру- информации) код единица. Вы- читатели 34 и 35 вычисляют абсолютную разность (выходной разряд заема не учитывается) между кодами строк и столбцов собственного и пр ишедше- го адреса соответственно. С помощью схем 36 и 37, на вторые входы которых подается код единицы с выхода узла 33, а также с помощью элемен тон И 44, 45 и 46 на выходе элемента ИЛИ 47 формируется единичный сигнал, говорящий о том, что пришедший операнд предназначен .одному из восьми соседних устройств. Этот сигнал служит для запрещения моди- ;фикации передачи информации с уче- ITOM коэффициентов загрузки направлений, если адресуемое устройство - соседнее.

Одновременно с этим схемы 38 и 39 вырабатывают сигналы сравнений собственного и поступившего адреса строкам и столбцам соответственно. Эти сигналы, поступая соответствующим образом на элементы И 40.1, ...,40.8 и 41.1,...,41.8,организуют направления передачи соответственно без модификации и с модификацией, учитывающей загрузку направлений. Элемент И 40.9 служит для выдачи, единичного импульса при совпадении адресов,если пришедшая информация предназначена данному устройству.Информация модификации с учетом загру ки направлений поступает из блока 7 в блок 8, задавая тем самым модификацию переда.чи информации в зависимости от загрузки направлений. Второй тактовый импульс, задержанный на элементе 48 задержки на время воможного формирования на выходе ИЛИ 47 единичного сигнала запрещения модификации, поступает на третьи вхо

10

5

0

5

ды элементов 41.1,...,41.

0

5

0

5

0

55

И,40.1,...,40.9 и 3. Б зависимости от того предназначен .ли текущий адрес соседнему устройству или нет выдача сигнала направления происходит на один из элементов группы ИЛИ 43.1, ...,43.8 или непосредственно с выхода соответствующего элемента И 40.1,...,40.8, минуя группу блоков элементов И модификации 42 . 1, ...,42.8 (если операнд адресован соседнему ПЭ), или с выхода соответствующего элемента И 41 .1,...,41.8 через группу элементов блоков И модификации 42.1, . . .,42.8 (если информация адресована не соседнему и не данному устройству). Если анализ направления в схемах 38 и 39 . соответствует, например, направлению ТЗосток (в) и .если операнд адресован не соседнему ПЭ5То в зависимости от загрузки направлений В, С- В и Ю-В может произойти модификация направления выдачи операнда и замена направления В на направление Ю-В или С-В для данного сектора направлений. Аналогичная модификация в зависимости от загрузки направления может происходить во всех восьми секторах передач информации. Если операнд адресован соседнему устройству, то он передается на него непосредственно без модификации. Таким образом, по второму тактово- гу импульсу генератора 9 блок формирует на своих выходах сигнал передачи информации по одному из девяти возможных направлений (восемь соседних устройств и собственные средства обработки (ПЭ) Поступление на устройство информации может происходить одновременно от восьми соседних устройств и заноситься в соответствующие блоки 1 . 1, . . ., 1 .8.,

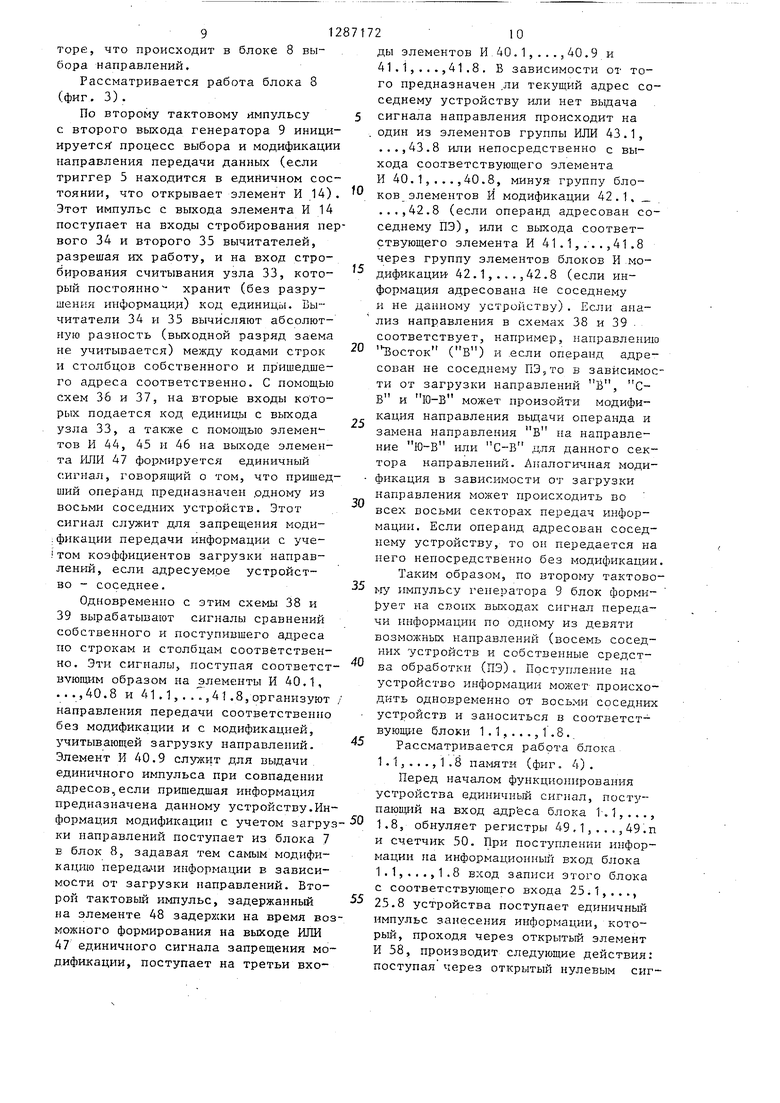

Рассматривается работа блока 1.1,...,1.8 памяти (фиг, 4) .

Перед началом функционирования устройства единичный сигнал, поступающий на вход адр еса блока 1-. 1, .. ., 1.8, обнуляет регистры 49,1,...,49.п и счетчик 50. При поступлении информации на информационный вход блока 1.1,...,1.8 вход записи этого блока с соответствующего входа 25.1,..., 25.8 устройства поступает единичный импульс занесения информации, сото- рый, проходя через открытый элемент И 58, производит следующие действия: поступая через открытый нулевым сиг

П1

налом с выхода элемента ИЛИ 55.1 элемент И 56.1 и элемент ИЛИ 54.1 на синхровход регистра 49.1, синхронизируют в него запись информации,проходящей через открытый ключ 51.1 и блок элементов ИЛИ 53.1 на информационный вход регистра 49.1; поступая через открытый нулевым сигналом с выхода элемента ИЛИ 55.п элемент И 59 на суммирующий вход счетчика 50, увеличивает его содержимое на единицу. Счетчик 50 -индицирует на своем выходе коэффициент загрузки данного блока памяти.

Занесение и считывание информации в регистрах 49.1,...,49.п организовано по принципу первым пришел,пер- въш следующим образом. Ну левое состояние i-ro (i 1,- n) регистра с помощью группы элементов ИЛИ 55.1,...,55.П и группы элементо И 56.1,...,56.п разрешает запись информации в этот регистр и запрещает запись информации в (1-1)-и регистр группы 49.1,...,49.п. Занесение информации происходит последовательно в регистры 49.1,...,49.п по сигналам записи, поступающим на вход записи блока 1.1,...,1.8 с помощью группы элементов И 56.1, . . . ,56.п, группы элементов ИЛИ 54.1,...,54.п, группы ключей и группы блоков элементов ИЛИ 53.1,...,53.п. Считывание информации происходит такзке последовательно по первым тактовым импуль сам, поступающим на вход синхронизации блока 1.1,...,1.8. Если очередь не пуста, на выходе элемента ИЛИ 55.1 индицируется единичный сигнал, который готовит к открытию элементы И 57 и 60. При считывании информации на входе считывания блока 1.1, ...,1.8 устанавливается единичный сигнал, который открывает элемент И 57 для прохождения первых такте- вых импульсов, по которым происходит движение очереди в регистрах 49.1,...,49.п. Первый тактовый импульс, поступая на вход синхронизации блока 1.1,...,1.8, запрещает с помощью элемента И 58 занесение информации в этот блок и, проходя через открытый элемент И 57 и через элементы ИЛИ 54.1,...,54.п на синхровходы регистров 49.1,...,49.п синхронизирует в них запись информации. Импульс с выхода элемента И .57 уменьшает содержимое счетчика 50 на

72

12

0

5

5 О

-5 ЗО 35 0 5 0 5

единицу и, поступая на управляющие ВХОДЫ ключей 52.1,...,52,п, открывает их и организует продвижение очереди в регистрах 49.1,...,49.п и выдачу информации из регистра 49,1 на информационный вход блока 1.1,..., 1.8, с выхода коэффициента загрузки которого выдается информация о коэффициенте загрузки с выхода счетчика 50, ас выхода признака загрузки - сигнал готовности данного бл ока к выдаче информации.

При завершении работы на входе 27 устройства устанавливается нулевой уровень сигнала и оно прекращает свое функционирование (фиг. 3). Работа предлагаемого устройства формирования маршрута сообщения в регу- лярных однородных структурах проиллюстрирована на примере произвольных пяти тактов на иг. 5.

Выбор наименее загруженного направления сектора передачи в прототипе для регулярной ортогональной структуры происходит последовательно за три такта работы устройства, в то время как в предлагаемом устройстве аналогичный выбор осуществляется за один такт.

Формула изобретения

Устройство формирования маршрута сообщения в однородной вычислительной системе, содержащее группу бло ков буферной памяти, три регистра, генератор тактовых импульсов, счетчик, мультиплексор , дешифратор,де- мультиплексор , триггер, группу элементов И, три элемента ИЖ, два элемента И, два элемента задержки,первый выход генератора тактовых импульсов подключен к первому входу первого элемента И, выход которого подключен к счетному входу счетчика и .входу второго элемента задержки, второй вход первого элемента И подключен к выходу триггера, информа-. ционный вход 1с-го блока буферной памяти группы (k 1, . , ., п, где п - количество направлений обмена) является k-M информационны входом устройства, выход третьего регистра является выходом для подключения к входу процессорного элемента устройства, первые входы первого и второго элементов ИЛИ соединены с входом сброса устройства, отличающееся

131

TOM, что,с .целью увеличения быстродействия, в него введены три одно- вибратора, блок сравнения и блок выбора направлений, который содержит четыре схемы сравненияj два вычита- теля, узел памяти константы, элемен задержки и дешифратор, выходы признаков направлений передачи которого подключены к управляющим входам демультиплексора, информационные входы которого соединены с выходами разрядов первого и второго регистров и с информационными входами третего регистра, выходы разрядов перво и второй групп второго регистра подключены соответственно к первым информационным входам третьей и четвертой схем сравнения и к входам вычитаемого первого и второго вычитат лей, первая и вторая группа входов задания адреса устройства соединены соответственно с входами уменьшаемого первого и второго вычитателей и с вторыми информационными входами третьей и четвертой схем сравнения, выходы признаков третьей и четвертой схем сравнения подключены к информационным входам первой группы дешифратора блока выбора направлений, информационные входы второй группы этого дешифратора соединены с выходами признаков первой и второ схем сравнения, первые информационные входы которых соединены с выходами первого и второго вычитателей соответственно, а вторые информаци- oHH)ie входы поразрядно объединены и соединены с выходом узла памяти константы, вход запуска генератора тактовых импульсов является входом запуска устройства, второй выход генератора тактовых импульсов подключен к первому входу второго элемента И, второй вход которого под- , ключей через первый элемент задержки к выходу триггера, а выход подключен к входам стробирования узла памяти константы, первого и второго вычитателей и через элемент задержки блока выбора направлений к входу стробирования дешифратора этого же блока, выход признака совпадения

5

0

5

172

1 адреса которого соединен с входом

синхронизации третьего регистра,выходы признаков и информационные входы блока сравнения соединены с 1, информационными входами третьей группы дешифратора блока выбора направлений и с соответствующими входами коэффициентов загрузки направлений устройства, вход сброса которого соединен с входами сброса с первого по третий регистров и блоков буфер- , ной памяти группы, выходы признаков загрузки которых соединены с входами второго элемента ИЛИ и с первыми входами соответствующих элементов И группы, выходы которых соеди- нены с входами третьего элемента ИЛИ, выход которого соединен с входом стробирования мультиплексора, информационные входы которого соединены с информационными выходами блоков буферной памяти группы, выход счетчика подключен к информа-. ционному входу дешифратора и к адресному входу мультиплексора, выходы разрядов первой и второй группы которого соединены с информационными входами первого и второго регистров соответственно, выходы разря- дов дешифратора соединены с вторы- ш входами соответствующих элементов И группы и с входами считывания соответствуюш;их блоков буферной памяти группы, выход второго элемента задержки подключен к входам синхро- низации первого и второго регистров и блоков буферной памяти группы, выход второго элемента ШШ подключен через первый одновибратор к входу установки триггера, а через второй одновибратор - к входу сброса триггера, выход соответствутощего разряда дешифратора подключен через третий одновибратор к второму входу первого элемента ИЛИ, выход которого подключен к входу сброса счетчика, вход записи и выход коэффициента загрузки k-ro блока буферной памяти группы являются k-M входом соп- 0 ровождения информации и k-выходом коэффициента загрузки направления устройства соответственно.

0

5

0

5

ФааЛ

ti-f fwti r -wf «l

Шиг.5

viXi axixi i ix

-a

i УЧ у УЧ / t x у j у I A,

:

P I , /Л гЛ Л. гл r. r

-

«-

vOrx/T XXT sXT X/T f ХЧ ХЧ /Ч ХЧ /Ч XV X

«:

X

етСхтх1 СС 1х

11 /1 I Г 3 П

-. ШЛVI- - -mJ fIP- --,... Xi5 Txn xixii

If

f Ji

T sXT X/T /Ч XV

X

i«-

с

:

-

x TXTXTXTXTXTXr

.В

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| МОДУЛЬ ДЛЯ ОБМЕНА СООБЩЕНИЯМИ | 2003 |

|

RU2249849C1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| Устройство для обмена данными | 1984 |

|

SU1278874A1 |

Изобретение относится к вычислительной технике и может найти применение при построении высокопроизводительных систолических,конвейерных и других процессоров, в которых в ходе решения задачи происходит движение данных по вычислительной рреде. Цель изобретения - увеличение 1::м.28.1 (f С ЯЬ25.2 tc (X н.

| Ячейка однородной трассирующей сети | 1982 |

|

SU1100616A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство для формирования маршрута сообщения | 1982 |

|

SU1049917A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-26—Подача