Изобретение относится к автоматике и вычислительной технике и может быть использовано для решения задач логического управления, описываемых системой временных булевых функций.5

Цель изобретения- снижение аппаратурных затратна реализацию устройства.

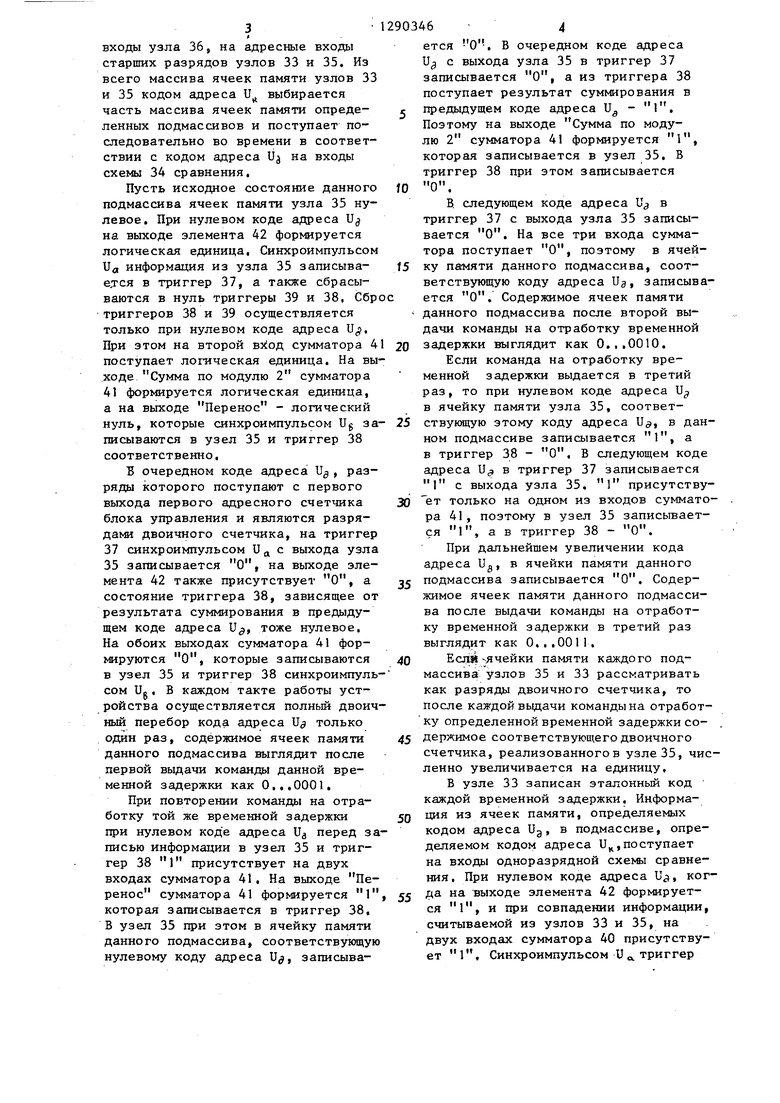

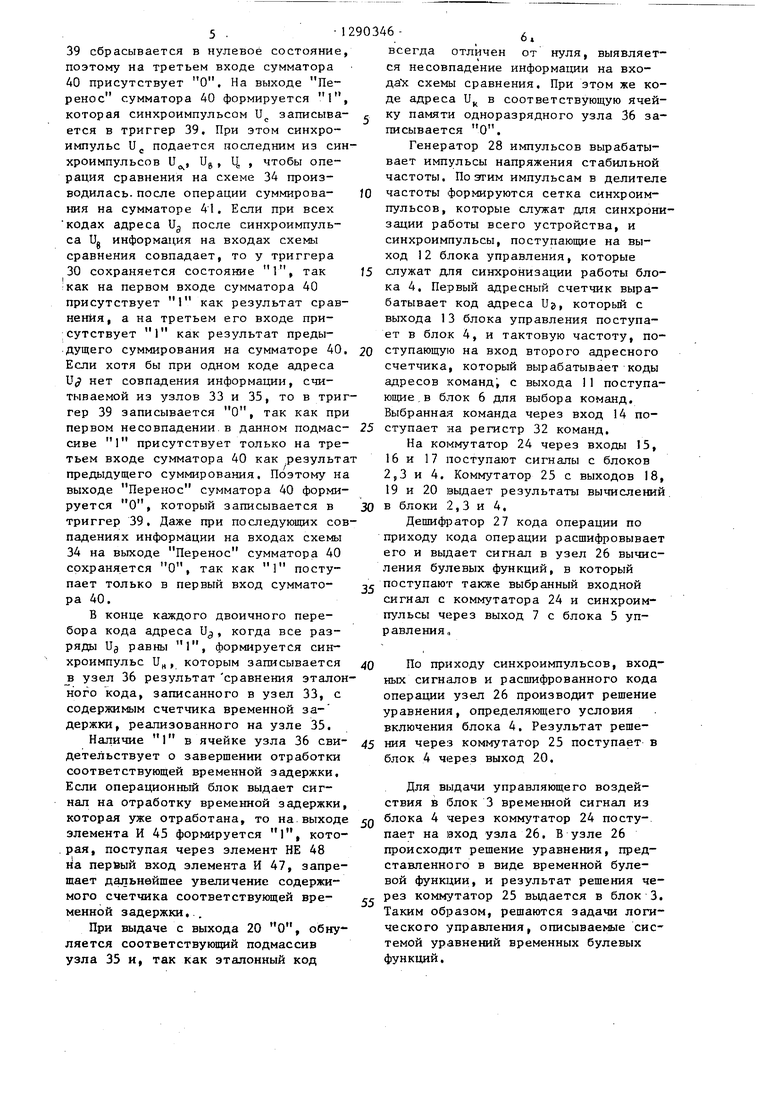

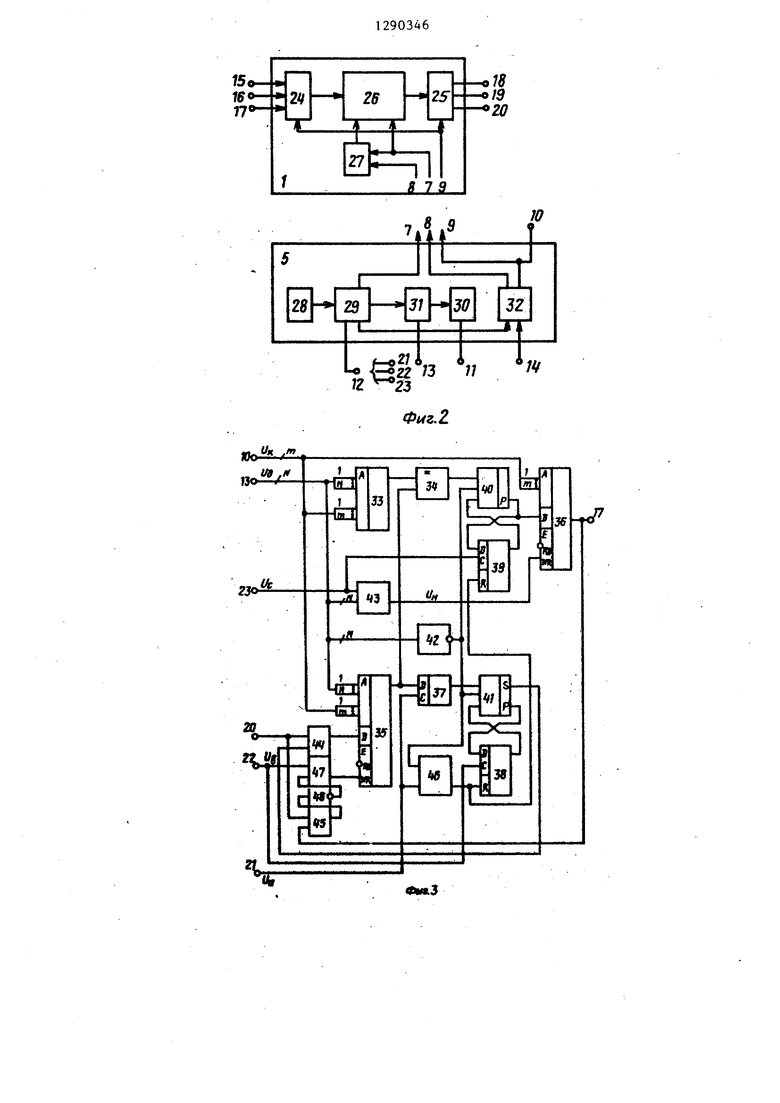

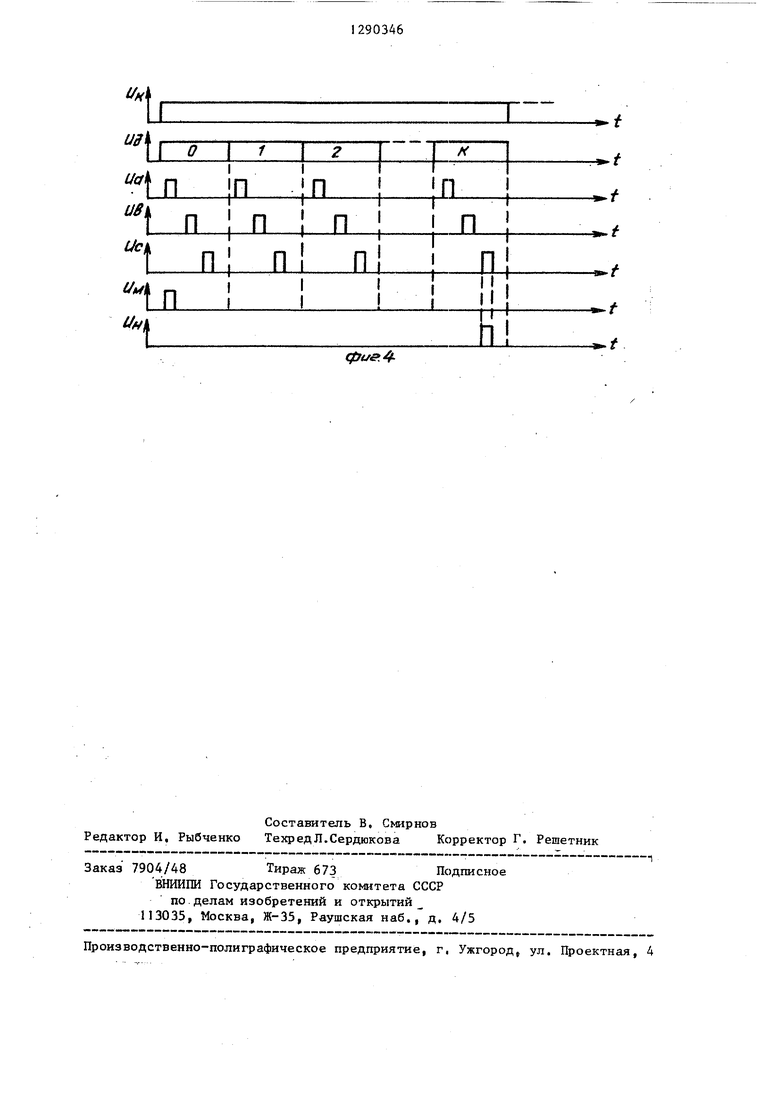

На фиг. 1 представлена блок-схема устройства для решения логичес- jg ких задач по временным булевым функ- .циям; на фиг. 2 - функциональные схемы блока управления и операционного блока; на фиг, 3 - функциональная схема блока формирования времен- |j ных задержек; на фиг. 4 - временная диаграмма работы блока временных задержек.

Устройство содержит операционный блок 1, блок 2 оперативной памяти, 20 блок 3 коммутации, блок 4 формирования временных задержек, блок 5 управления, блок 6 постоянной памяти, с первой по седьмую группы выходов 7-13 блока управления, вход 14 ко- 25 манды блока управления, первый, второй, третий информационные входы 15, 16 и 17 операционного блока, первый, второй, третий информационные выходы 18,19,20 операционного блока, первый, jO второй, третий выходы 21, 22 и 23 шестой группы блока управления г Операционный блок содержит первый и второй коммутаторы 2 и 25 вычислерезультатов вычислений. Блок ввода вывода предназначен для связи с пе риферийными устройствами (устройствами связи с объектом упр авления пультом управления и пр.). Блок фо мирования временных задержек предназначен для реализации необходимых задержек выдачи сигнала согла но алгоритму функционирования,

В узле 33 блока 4 хранятся коды длительности . используемых временных задержек, число разрядов которых определяется исходя из длител ности данной задержки и величины допуска на минимальную задержку.

Старшими разрядами адреса узлов 33 и 35,1 количество которых равно га и совпадает с адресными разрядам узла 36,, определяется адрес времен ной задержки, равный 2 , Младшими адресными разрядаьм узлов 33 и. 35 количество которых равно N, опреде ляется разрядность счетчика каждой временной задержки. При этом инфор мация из ячеек памяти одноразрядны узлов 35 и 33, поступакацая на вход схемы 34 сравнения последовательно во времени в соответствии с кодом адреса Ua в каждой временной задержке, соответствует разрядам сче чика, з 1писанным в узле 33, и разрядам счетчика временной задержки реализованного в узле 35, Разрядность счетчика временной задержки ния булевых функций, узел 26, дешифраторэ равна 2 , при зтом число разрядов 27, Блок управления содержит генесчетчика временной задержки должно быть не меньше числа разрядов кодо задержки: максимальной длительности

ратор 28 тактовых импульсов, делитель 29 частоты, первый и второй счетчики 30 и 31, регистр 32, Блок формирования временных задержек содержит узел 33 постоянной памяти, схему 34 сравнения, первый и второй узлы 35 и 36 оперативной памяти, - первый, второй и третий триггеры 37, 38 и 39, первый и второй сумматоры 40 и 41, злемент ИЛИ-НЕ 42, с пер-, вого по пятый элементы И 43-47, элемент НЕ 48,

По заданному адресу соответствующая логическая переменная из блоков 2,3 и 4 поступает на входы 17, 16 и 15 блока 1, в котором производятся в лчисления логических функций по заданной программе. Результаты вычислений выдаются из блока 1 в блоки 2,3 и 4 на выходы 20, 19 и 18,

Блок оперативной памяти предназначен для хранения промежуточных

результатов вычислений. Блок ввода- вывода предназначен для связи с периферийными устройствами (устройствами связи с объектом упр авления, пультом управления и пр.). Блок формирования временных задержек предназначен для реализации необходимых задержек выдачи сигнала согласно алгоритму функционирования,

В узле 33 блока 4 хранятся коды длительности . используемых временных задержек, число разрядов которых определяется исходя из длительности данной задержки и величины допуска на минимальную задержку.

Старшими разрядами адреса узлов 33 и 35,1 количество которых равно га и совпадает с адресными разрядами узла 36,, определяется адрес временной задержки, равный 2 , Младшими адресными разрядаьм узлов 33 и. 35, количество которых равно N, определяется разрядность счетчика каждой временной задержки. При этом информация из ячеек памяти одноразрядных узлов 35 и 33, поступакацая на входы схемы 34 сравнения последовательно во времени в соответствии с кодом адреса Ua в каждой временной задержке, соответствует разрядам счетчика, з 1писанным в узле 33, и разрядам счетчика временной задержки, реализованного в узле 35, Разрядность счетчика временной задержки равна 2 , при зтом число разрядов

счетчика временной задержки должно быть не меньше числа разрядов кодов задержки: максимальной длительности,

В каждом коде адреса U, соответствующем определенной временной задержке, осуществляется полный двоичный п€ ребор кода адреса U, При отработке временной задержки в каждом такте работы устройства требуется циклов Запись - считыва,

кие узла 35,

Упранление устройством осуществляется сигналом с выхода 20 операционного блока. При наличии логической единицы, поступающей через выход 20 в блок 4, отрабатывается определенная временная задержка. При отсутствии логической единицы ячейки памяти, соответствующие данНОЙ временной задержке в узлах 35 и 36, обнуляются.

Код адреса определенной временной задержки с выхода 10 блока управления поступает на адресны,е

входы узла 36, на адресные входы старших разрядов узлов 33 и 35. Из всего массива ячеек памяти узлов 33 и 35 кодом адреса U выбирается часть массива ячеек памяти опреде- ленных подмассивов и поступает последовательно во времени в соответствии с кодом адреса U на входы схемы 34 сравнения.

Пусть исходное состояние данного подмассива ячеек памяти узла 35 нулевое. При нулевом коде адреса U на выходе элемента 42 формируется логическая единица. Синхроимпульсом Ua информация из узла 35 записыва- е,тся в триггер 37, а также сбрасываются в нуль триггеры 39 и 38, Сбр триггеров 38 и 39 осуществляется только при нулевом коде адреса U, При 3том на второй вход сумматора 4 поступает логическая единица. На выходе Сумма по модулю 2 сумматора 41 формируется логическая единица, а на выходе Перенос - логический нуль, которые синхроимпульсом Ug за писываются в узел 35 и триггер 38 соответственно.

В очередном коде адреса U, разряды которого поступают с первого выхода первого адресного счетчика блока управления и являются разря- даья двоичного счетчика, на триггер

37 синхроимпульсом U,

llnll

с выхода узла

35 записывается О , на выходе элемента 42 также присутствует О, а состояние триггера 38, зависящее от результата суммирования в предыдущем коде адреса U, тоже нулевое, На обоих вьпсодах сумматора 41 формируются О, которые записываются в узел 35 и триггер 38 синхроимпуль сом Uo В каждом такте работы устройства осуществляется полный двоичный перебор кода адреса U только один раз, содержимое ячеек памяти данного подмассива выглядит после первой выдачи команды данной временной задержки как О,,.0001.

При повторении команды на отработку той же временной задержки цри нулевом код е адреса U перед записью информации в узел 35 и триггер 38 1 присутствует на двух входах сумматора 41. На выходе Перенос сумматора 41 формируется 1 которая записывается в триггер 38, В узел 35 при этом в ячейку памяти данного подмассива, соответствующую нулевому коду адреса U, записывас

fO f5 с 20 25

30

290346 - 4

ется , В очередном коде адреса и с выхода узла 35 в триггер 37

35

40

45

50

55

записывается О, а из триггера 38 поступает результат суммирования в предыдущем коде адреса U - 1. Поэтому на выходе Сумма по модулю 2 сумматора 41 формируется 1, которая записывается в узел 35. В триггер 38 при этом записывается О,

B следующем коде адреса U в триггер 37 с выхода узла 35 записывается О. На все три входа сумматора поступает О, поэтому в ячейку памяти данного подмассива, соответствующую коду адреса Ug, записывается О. Содержимое ячеек памяти данного подмассива после второй выдачи команды на отработку временной задержки выглядит как О.,,0010.

Если команда на отработку временной задержки выдается в третий раз, то при нулевом коде адреса U в ячейку памяти узла 35, соответ- ствунш1ую этому коду адреса U, в данном подмассиве записывается 1, а в триггер 38 - О, В следующем коде адреса U в триггер 37 записывается 1 с выхода узла 35. 1 присутству- ет только на одном из входов сумматора 41, поэтому в узел 35 записывается 1, а в триггер 38 - О.

При дальнейшем увеличении кода адреса U, в ячейки памяти данного подмассива записывается О. Содержимое ячеек памяти данного подмассива после выдачи команды на отработку временной задержки в третий раз выглядит как О.,,0011,

Еа1а -ячейки памяти каждого подмассива узлов 35 и 33 рассматривать как разряды двоичного счетчика, то после каждой выдачи команды на отработку определенной временной задержки содержимое cooтвeтcтвyюи eгo двоичного счетчика, реализованного в узле 35, численно увеличивается на единицу.

В узле 33 записан эталонный код каждой временной задержки. Информация из ячеек памяти, определяемых кодом адреса Ug, в подмассиве, определяемом кодом адреса U,поступает на входы одноразрядной схеьи сравнения. При нулевом коде адреса Ъ д, когда на выходе элемента 42 формируется 1, и при совпадении информации, считываемой из узлов 33 и 35, на двух входах сумматора 40 присутствует 1, Синхроимпульсом и о. триггер

39сбрасывается в нулевое поэтому на третьем входе сумматора

40присутствует О. На выходе Перенос сумматора 40 формируется 1 которая синхроимпульсом U записывается в триггер 39, При этом синхроимпульс Uj подается последним из сихроимпульсов и, Uj , Ц. , чтобы операция сравнения на схеме 34 производилась, после операции суммирования на сумматоре 41. Если при всех

кодах адреса U после синхроимпульса Ug информация на входах схемы сравнения совпадает, то у триггера 30 сохраняется состояние 1, так как на первом входе сумматора 40 присутствует 1 как результат сравнения, а на третьем его входе присутствует 1 как результат предыдущего суммирования на сумматоре 40 Если хотя бы при одном коде адреса и нет совпадения информации, считываемой из узлов 33 и 35, то в тригер 39 записывается О, так как пр

- состояние

первом несовпадении.в данном подмас- 25 ступает на регистр 32 команд.

сиве 1 присутствует только на третьем входе сумматора 40 как результа предыдущего суммирования. Поэтому на выходе Перенос сумматора 40 формируется О, который записывается в триггер 39, Даже при последующих совпадениях информации на входах схемы 34 на выходе Перенос сумматора 40 сохраняется О, так как 1 поступает только в первый вход сумматора 40,

В конце каждого двоичного перебора кода адреса U, когда все разряды Ug равны 1, формируется синхроимпульс и„, которым записывается в узел 36 результат сравнения эталон ного кода, записанного в узел 33, с содержимым счетчика временной за- держки, реализованного на узле 35,

Наличие 1 в ячейке узла 36 свидетельствует о завершении отработки соответствующей временной задержки. Если операционный блок выдает сигнал на отработку временной задержки, которая уже отработана, то на.выходе

элемента И 45 формируется 1, которая, поступая через элемент НЕ 48 на первый вход элемента И 47, запрещает дальнейшее увеличение содержимого счетчика соответствующей временной задержки...

При выдаче с выхода 20 О, обнуляется соответствующий подмассив узла 35 и, так как эталонный код

6.

от

нуля, выявляется несовпадение информации на вхо- да х схемы сравнения. При этом же коде адреса U в соответствующую ячейку памяти одноразрядного узла 36 записывается О.

Генератор 28 импульсов вырабатывает импульсы напряжения стабильной частоты. По этим импульсам в делителе

частоты формируются сетка синхроимпульсов, которые служат дпя синхронизации работы всего устройства, и синхроимпульсы, поступающие на выход 12 блока управления, которые

служат Д.ПЯ синхронизации работы блока 4, Первый адресный счетчик вырабатывает код адреса Uj, которьй с выхода 13 блока управления поступает в блок 4, и тактовую частоту, поступающую на вход второго адресного счетчика, который вырабатывает коды адресов командi с выхода 11 поступающие . в блок 6 для выбора команд. Выбранная команда через вход 14 по

На коммутатор 24 через входы 15, 16 и 17 поступают сигналы с блоков 2,3 и 4, Коммутатор 25 с выходов 18, 19 и 20 выдает результаты вычислений, в блоки 2,3 и 4,

Дешиф)атор 27 кода операции по приходу кода операции расшифровывает его и выдает сигнал в узел 26 вычисления булевых функций, в который поступают также выбранный входной сигнал с коммутатора 24 и синхроимпульсы через выход 7 с блока 5 управления,,

По приходу синхроимпульсов, входных сигн;алов и расшифрованного кода операции узел 26 производит решение уравнения, определяющего условия включения блока 4, Результат рещения через коммутатор 25 поступает в блок 4 через выход 20,

Для выдачи управляющего воздействия в блок 3 временной сигнал из блока 4 через коммутатор 24 посту-, пает на вход узла 26, В узле 26 происход11т решение уравнения, представленного в виде временной булевой функции, и результат решения через комм;/татор 25 выдается в блок 3, Таким образом, решаются задачи логического управления, описываемые системой уравнений временных булевых функций.

ормула и

7

3 о

бретения

12

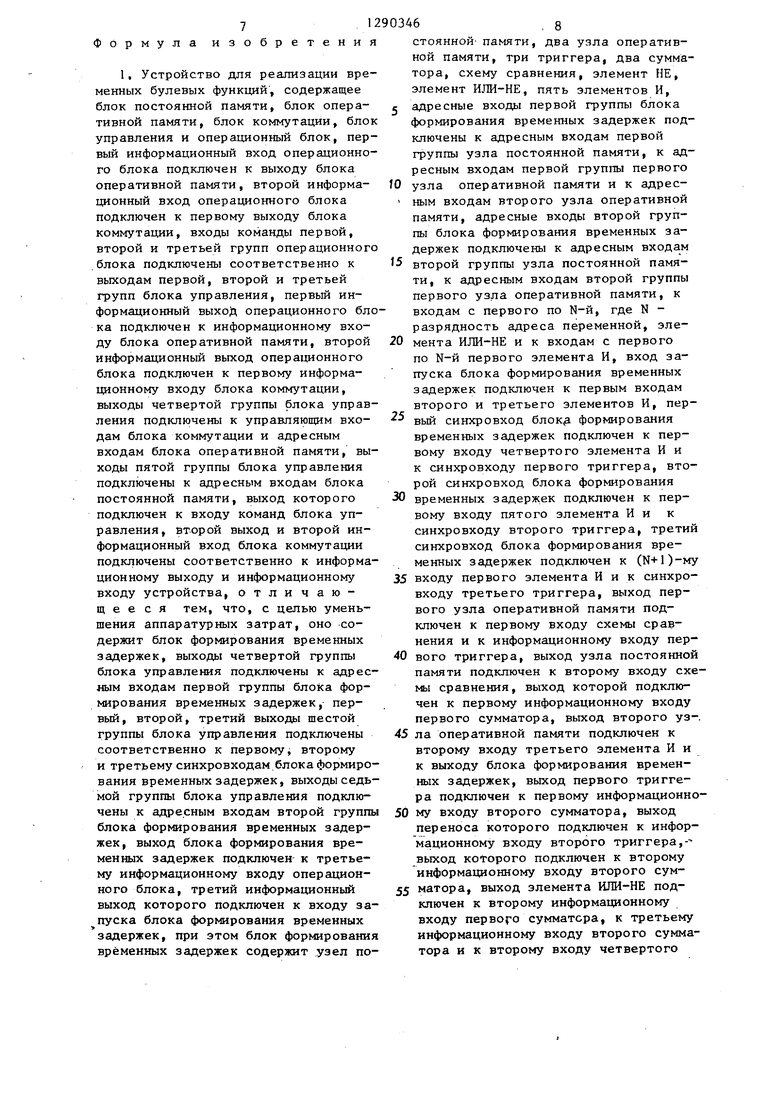

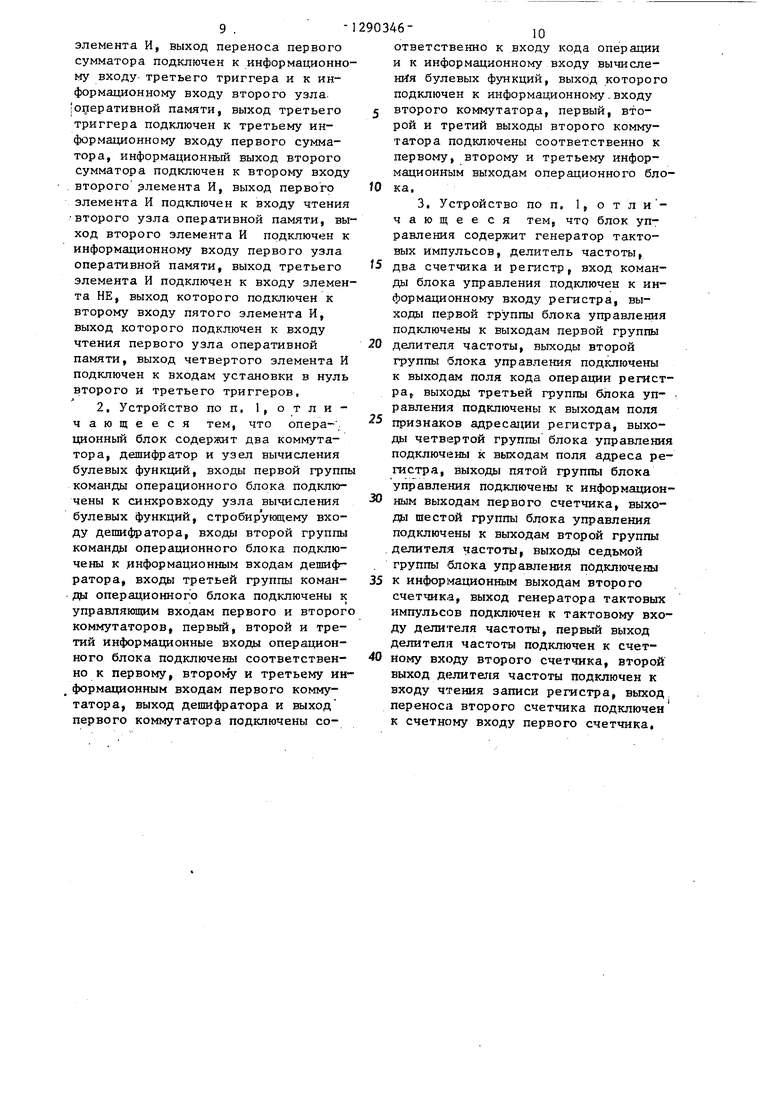

1, Устройство для реализации временных булевых функций, содержащее блок постоянной памяти, блок оперативной памяти, блок коммутации, блок управления и операционный блок, первый информационный вход операционного блока подключен к выходу блока оперативной памяти, второй информационный вход операционного блока подключен к первому выходу блока коммутации, входы команды первой, второй и третьей групп операционного .блока подключены соответственно к выходам первой, второй и третьей групп блока управления, первый информационный выход операционного блока подключен к информационному вхо- ду блока оперативной памяти, второй информационный выход операционного блока подключен к первому информационному входу блока коммутации, выходы четвертой группы блока управления подключены к управляющим входам блока коммутации и адресным входам блока оперативной памяти, выходы пятой группы блока управления подключены к адресным входам блока постоянной памяти, выход которого подключен к входу команд блока управления, второй выход и второй информационный вход блока коммутации подключены соответственно к информационному выходу и информационному входу устройства, отличающееся тем, что, с целью уменьшения аппаратурных затрат, оно содержит блок формирования временных задержек, выходы четвертой группы блока управления подключены к адресным входам первой группы блока формирования временных задержек, первый, второй, третий выходы шестой группы блока управления подключены соответственно к первому, второму и третьему синхровходам,блока формирования временных задержек, выходы седьмой группы блока управления подключены к адресным входам второй группы блока формирования временных задержек, выход блока формирования временных задержек подключен к третьему информационному входу операционного блока, третий информационный выход которого подключен к входу за- пуска блока формирования временных задержек, при этом блок формирования временных задержек содержит узел по

90346

стоянкой- памяти, два узла оперативной памяти, три триггера, два сумматора, схему сравнегшя, элемент НЕ, элемент ИЛИ-НЕ, пять элементов И,

с адресные входы первой группы блока формирования временных задержек подключены к адресным входам первой группы узла постоянной памяти, к адресным входам первой группы первого

10 узла оперативной памяти и к адрес- ным входам второго узла оперативной памяти, адресные входы второй группы блока формирования временных задержек подключены к адресным входам

15 второй группы узла постоянной памяти, к адресным входам второй группы первого узла оперативной памяти, к входам с первого по N-й, где N - разрядность адреса переменной, эле20 мента ИЛИ-НЕ и к входам с первого по N-й первого элемента И, вход запуска блока формирования временных задержек подключен к первым входам второго и третьего элементов И, пер вый синхровход блок формирования временных задержек подключен к первому входу четвертого элемента И и к синхровходу первого триггера, второй синхровход блока формирования временных задержек подключен к первому входу пятого элемента И и к синхровходу второго триггера, третий синхровход блока формирования временных задержек подключен к (N+l)-My

35 входу первого элемента Ник синхровходу третьего триггера, выход первого узла оперативной памяти подключен к первому входу схемы сравнения и к информационному входу пер-

40 вого триггера, выход узла постоянной памяти подключен к второму входу схе- MJ сравнения, выход которой подключен к первому информационному входу первого сумматора, выход второго уз-.

45 ла оперативной памяти подключен к второму входу третьего элемента И и к выходу блока формирования временных задержек, выход первого триггера подключен к первому информационно50 му входу второго сумматора, выход переноса которого подключен к информационному входу второго триггера,- выход которого подключен к второму информационному входу второго сум55 матора, выход элемента ИЛИ-НЕ подключен к второму информационному входу первого сумматора, к третьему информационному входу второго сумматора и к второму входу четвертого

30

элемента И, выход переноса первого сумматора подключен к информационному входу- третьего триггера и к информационному входу второго узла. оперативной памяти, выход третьего триггера подключен к третьему информационному входу первого сумматора, информационный выход второго сумматора подключен к второму входу второго элемента И, выход первого элемента И подключен к входу чтения второго узла оперативной памяти, выход второго элемента И подключен к информационному входу первого узла оперативной памяти, выход третьего элемента И подключен к входу элемента НЕ, выход которого подключен к второму входу пятого элемента И, выход которого подключен к входу чтения первого узла оперативной памяти, выход четвертого элемента И подключен к входам установки в нуль второго и третьего триггеров,

2. Устройство по п. 1, о т л и - чающееся тем, что опера- ционный блок содержит два коммутатора, дешифратор и узел вычисления булевых функций, входы первой групп команды операционного блока подключены к синхровходу узла вычисления булевых функций, стробирукицему входу дешифратора, входы второй группы команды операхдаонного блока подключены к 1нформационным входам дешифратора, входы третьей группы команды операционного блока подключены к управляющим входам первого и второг коммутаторов, первый, второй и третий информационные входы операционного блока подключены соответственно к первому, второму и третьему ин формационным входам первого коммутатора, выход дешифратора и выход первого коммутатора подключены со

S

ответственно к входу кода операции и к информационному входу вычисления булевых функций, выход которого подключен к информационному.входу

второго коммутатора, первый, второй и третий выходы второго коммутатора подключены соответственно к первому, второму и третьему информационным выходам операционного блока,

3, Устройство по п, 1, о т л и - чающееся тем, что блок управления содержит генератор тактовых импульсов, делитель частоты, два счетчика и регистр, вход команды блока управления подключен к информационному входу регистра, выходы первой группы блока управления подключены к выходам первой группы делителя частоты, выходы второй группы блока управления подключены к выходам поля кода операции регистра, выходы третьей группы блока уп- равления подключены к выходам поля признаков адресации регистра, выходы четвертой группы блока управления подключены к выходам поля адреса регистра, выходы пятой группы блока управле:ния подключены к информационным выходам первого счетчика, выходы шестой группы блока управления подключены к выходам второй группы делителя частоты, выходы седьмой группы блока управления подключены

5 к информационным выходам второго счетчика, выход генератора тактовых импульсов подключен к тактовому входу делителя частоты, первый выход делителя частоты подключен к счет- йому входу второго счетчика, второй выход деглителя частоты подключен к входу чтения записи регистра, выход переноса второго счетчика подключен к счетному входу первого счетчика.

0

5

0

0

IZ 23

Фиг.2

(pt/ff.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления совмещением данных | 1981 |

|

SU999066A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Устройство для поиска данных | 1989 |

|

SU1658170A2 |

| Устройство для реализации быстрого преобразования Фурье при многоканальной обработке информации | 1983 |

|

SU1124324A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для отладки программ | 1981 |

|

SU980096A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

Изобретение относится к автоматике и вычислительной технике и но- жет быть использовано для решения задач логического управления, описываемых системой временных булевых функций. Цель изобретения - уменьшение аппаратурных затрат. Поставленная цель достигается тем, что устройство содержит блок коммутации 3, операционный блок 1, блок оперативной памяти 2, блок постоянной памяти 6, блок формирования временных задержек 4 и блок управления 5. 1 з.п. ф-лы, 4 ил. а Ф i (Л ю ;о о 00 4i Од

| 0 |

|

SU189630A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения логических задач | 1974 |

|

SU531160A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 852081, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-13—Подача