Я.1

3150

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных матричных, конвейерных систолических, векторных и других п;:-оцессоров, в которых в процессе обработки информации происходит движение данных в вычислительной среде, при построении ЭВМ и вычислительных систем динамической архитектурой.

Цель изобретения - повьпиение быстродействия устройства при одновременном повышении достоверности передаваемой транзитной информации.

Сущность изобретения заключается в хранении в специальном блоке памяти набора сигнатур - отпечатков маршрутов прохождения информации по Минимальному физическому пути между двумя модулями однородной вычислительной системы. При выдаче сообщения модулем вычислительной системы сообщение дополняется из блока памяти сигнатурой, которая по мере транзитного .прохождения модифицируется идентификаторами модулей, через которые проходит маршрут формирования сообщения, и направлениями выдачи информации. При достижении модуля при- емника информации (сообщения) полученная сигнатура должна быть нулевой в противном случае сформированный маршрут будет неверным.

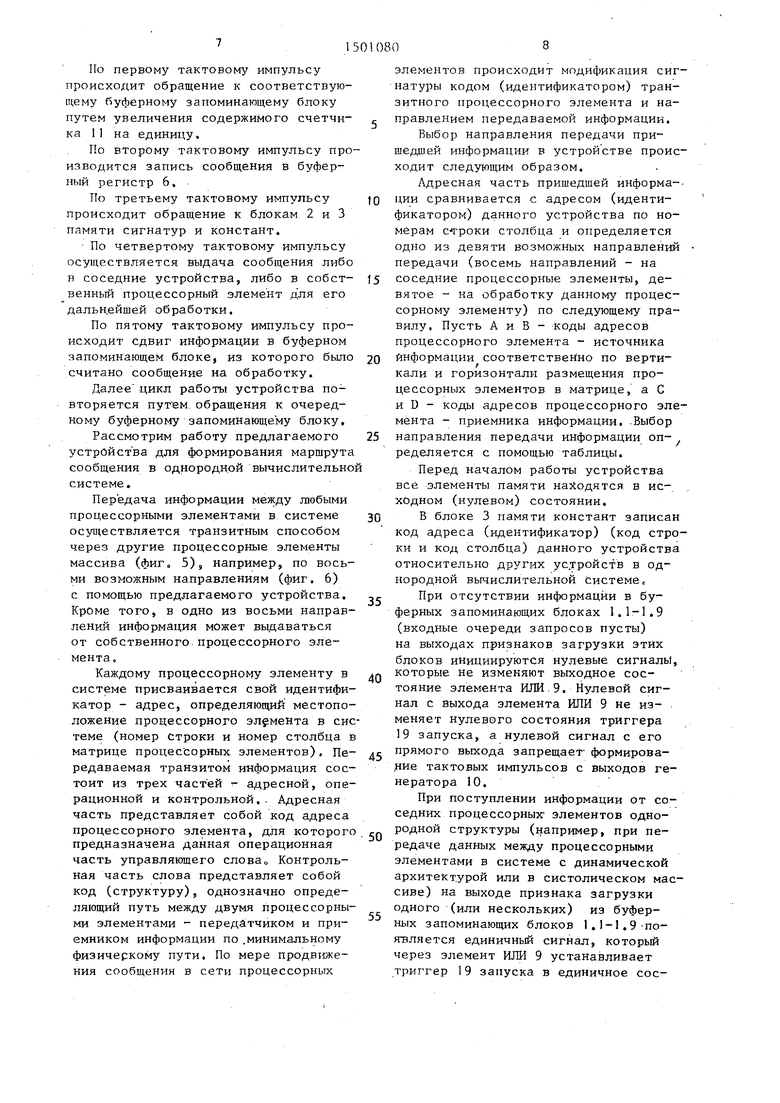

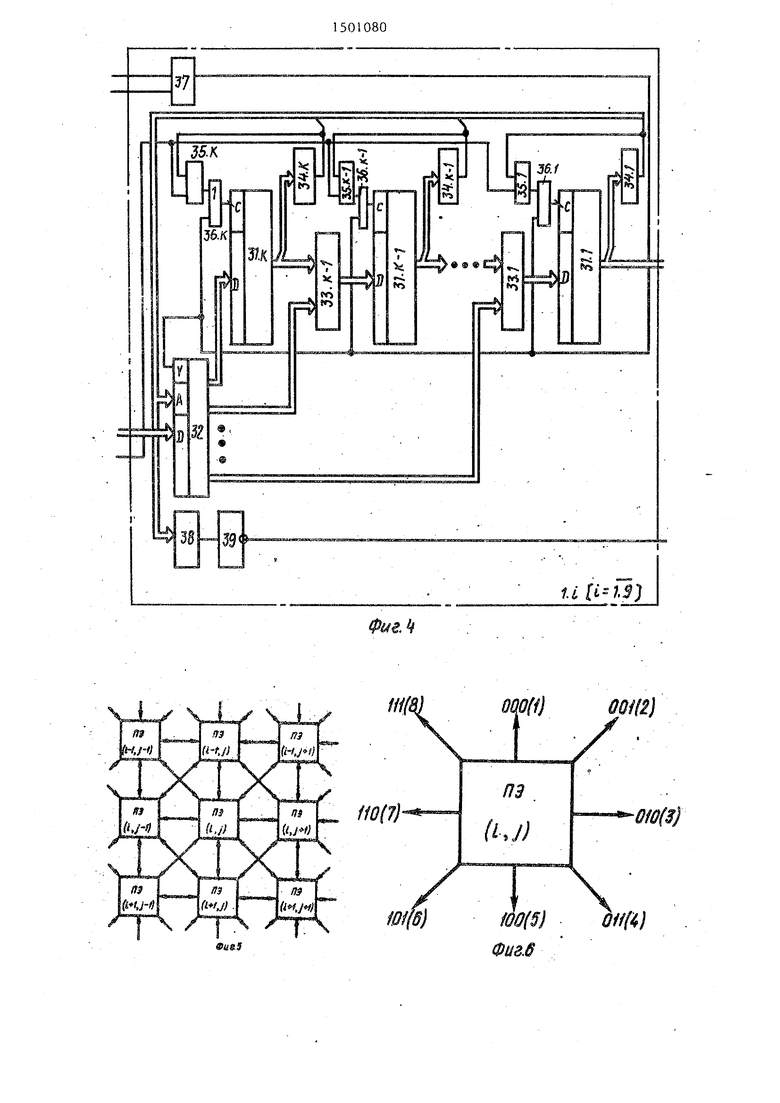

На фиг. 1 представлена функцио- нальная схема устройства для формирования маршрута сообщения в однородной вычислительной системе; на фиг„ 2 - функциональная схема блока выбора направления передачи информации; на фиг, 3 - функциональная схе ма демультиплексора; на фиг. 4 - функциональная схема i-ro (,9). буферного запоминакяцего блока; на фиГй 5 - схема, возможных путей прохождения данных между произвольными процессорными эле.ментами в вычислительной системе с использованием .предлагаемого устройства; на фиг,6 пример кодирования возможных направлений передачи сообщения от произвольного процессорного элемента; на фиг. 7 - пример кодирования матрицы процессорных элементов размерностью 3 а 3 и направлений передач сообщений от процессорного элемента 3,1 к процессорному элементу 1,3; на фиг. примеры образования кОда сигнатуры, хранимбго в специальном блоке пами

5

0

5

0

0

5

0

5

ти, и используемого при формировании маршрута передачи сообщения от процессорного элемента 3,1 к процессорному элементу 1,3 (а), модификации кода сигнатуры при правильном (8„) и неправильном (S) формировании маршрута передачи сообщения (б); на фиг. 9 - функциональная схема генератора импульсов; на фиг. 10 - временные диаграммь работы генератора импульсов и основных узлов схемы.

Устройство для формирования маршрута сообщения в однородной вычислительной системе (фиг. 1) содержит девять буферных запоминающих блоков 1.1-1.9 типа первым вошел - первым вьшзел, блок 2 памяти сигнатур, блок 3 памяти констант, блок 4 выбора направления передачи информации, Р ультиплексор 5, буферный регистр 6 с тремя полями: адресным полем 6,1, операционным полам 6,2, контрольным полем (полем сигнатур) 6,3, блок 7 суммирования по модулю два, демуль- типлексор 8, элемент ИЛИ 9, генератор 10 импульсов, счетчик 11, дешифратор 12, коммутатор 13 блок элементов И 14.1-14,8, блок 15 элементов И, элемент И 16, элемент И 17, триггер 18 управления, триггер 19 запуска, элемент И. 20 и дешифратор 21 ..

Кроме того, на фиг. 1 показаны входы 22,1-22,9 от соседник устройств и собственного процессорного элемента, выход 23 устройства к собственному процессорному элементу и выходы 24,1-24,8 устройства- к соседним устг ройствам, а также управляющий вы ход 25.. .

Блок 4 выбора направления передачи информации (фиг. 2)содержит первую 26 и вторую 27 схемы сравнения и элемент И 28.

Демультиплексор 8 (фиг, 3) образуют дешифратор 29 и группа блоков элементов И 30,1-30..8,

i-й (,9) буферный запоминающий блок ,1 включает блок регистров 31,1-31,К (К - глубина очереди сообщений), Демультиплексор 32, группу блоков элементов ИЛИ 33,1- 33,К-1, первый блок элементов И 34,1-34 о К, второй блок элементов И. 35, 1-35,К, блок элементов ИЛИ 36,1-36.К, второй элемент И 37, первый элемент И 38 и элемент НЕ 39,

5

Группа буферных запоминающих блоков 1.1-1.9 предназначена для организации очередей сообщений, поступающих от.восьми соседних устройств и собственного процессорного элемента. ..

БЛОК 2 памяти сигнатур служит для хранения кодов, определяющих првильное формирование марщрута пере дачи сообщения от данного устройства к устройствам-получателям сообщений.

Блок 3 памяти констант предназначен для хранения кода (идентификатора) , определяющего мес.тоположение устройства в матрице аналогичных устройств, осуществляющих обмен сообщениями между процессорными элементами вычислительной системы.

Блок 3 может быть выполнен в виде последовательного соединения генератора константы - фиксированного кода (тумблерного регистра и т.д.) и блока элементов И, к втopo ry входу которого подключен вход блока 3.

Блок 4 выбора направления передачи информации служит для выбора и модификации направления передачи поступившей информации в зависимос- TJ1 от кода устройства-получателя сообщения и кода (идентификатора) предлагаемого устройства.

Мультиплексор 5 предусмотрен для коммз тации входных сообщений.

Буферньй регистр 6 хранит код -сообщения на время анализа и его обработки.. . ,.

Блок 7 суммирования по модулю два предназначен для модификации поступившей контрольной информации (сигнатуры) кодом идентификатора и кодом направления передачи сообщения.

Демультиплексор 8 служит для коммутации передаваемого сообщения на один из восьми выходов устройства,

Элемент ИЛИ 9 формирует сигнал наличия хотя бы одного сообщения в одном из буферных запоминающих блоков 1.1-1.9.

Генератор 10 импульсов задает последовательность синхронизирующих импульсов.,

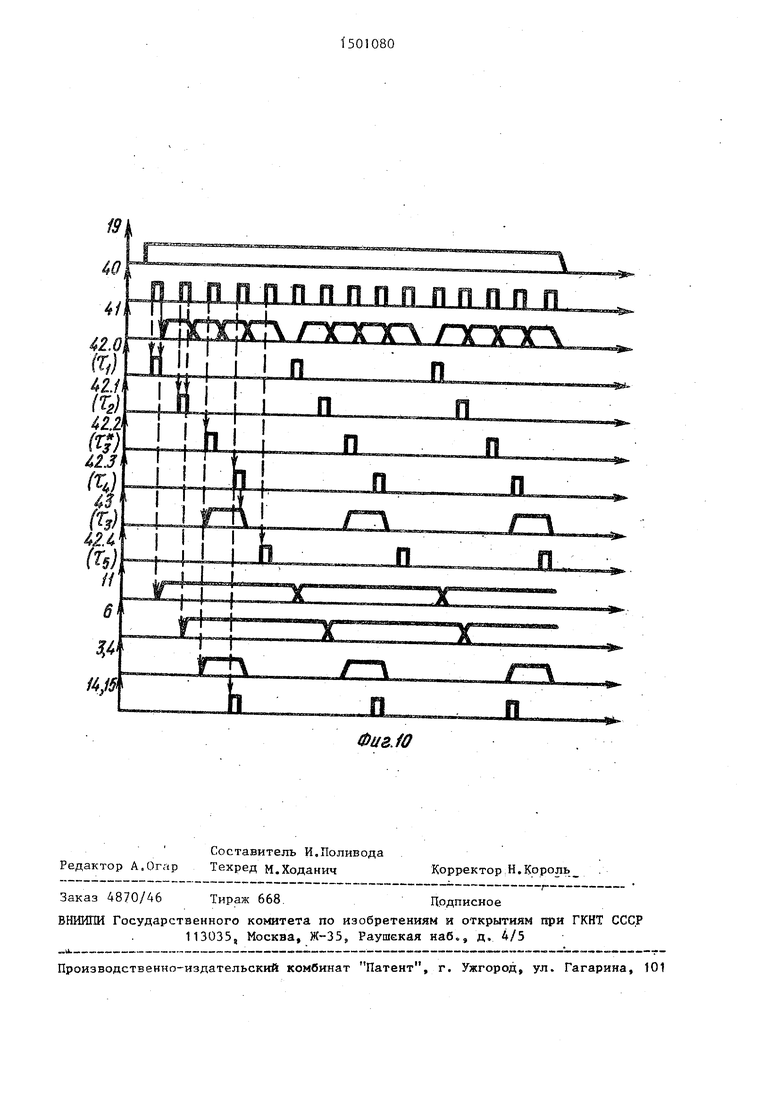

Генератор 10 импульсов . (фиг. 9) содержит управляемый генератор 40 импульсов, счетчик 41, дешифратор 42 и триггер 43 и формирует после дова- тельность синхроимпульсов . Принцип действия генератора 10 пояс-

010806

няется временными диаграммами на фиг. 10. Посредством счетчика генератора 40, который включается единичным сигналом на входе, счетчика 41 с коэффициентом пересчета 5 формируется последовательность импульсов , , 2. f ч Р гер 43 устанавливается в единичное

10 состояние импульсом S и обнуляется задним фронтом импульса i, формируя при этом удлиненный импульс 3 , который является стробирующим сигналом опроса блоков 2 и 3.

15 Счетчик 1 совместно с дешифратором 12 служит для последовательного циклического опроса буферных за- пог данающих блоков 1.1--1,9.

Коммутатор 13 предназначен для

20 коммутации либо начального кода сигнатуры (при передаче сообщения от данного устройства) либо модифицированного кода сигнатуры (при передаче транзитного сообщения).

25 Блок элементов И 14.1-14.8 совместно с дешифратором 21 служит для разрешения вьздачи тактового импульса . на соответствующий выход устройства для записи выданного сообщения сосед30 ним. устройством.

Блок 15 элементов И разрешает выдачу (передачу) поступившего сообщения собственному процессорному элементу.

35 Элемент И 16 и триггер 18 управления предназначены для формирования управляющего сигнала при ненулевой сигнатуре, полученной по окончании формирования маршрута сообщения.

40 Триггер 18 устанавливается в единичное состояние при наличии сигнала на С-входе и нулевом сигнале на . S-входе.

45 Элемент И, 20 и обусловленные им связи служат для формирования сигнала на обращение к блоку 2 памяти сигнатур при выдаче информации от данного устройства.

Q Синхронизация работы устройства происходит по импульсам, которые формируются на выходах генератора 10 импульсов и представляют собой пять импульсных последовательностей

5 (фиг, 10).Цикл работы состоит из пяти фаз. .Каждая фаза работы устройства начинается тактовым импульсом соот- ветствзпощей импульсной последовательности.

По первому тактовому импульсу происходит обращение к соответствующему буферному запоминающему блоку путем увеличения содержимого счетчи- ка 11 на единицу.

По второму тактовому импульсу производится запись сообщения в буферный регистр 6, По третьему тактовому импульсу происходит обращение к блокам 2 и 3 памяти сигнатур и констант

По четвертому тактовому импульсу осуществляется выдача сообщения либо н соседние устройства, либо в собст- венный процессорнь й элемент для его дальнейшей обработки.

По пятому тактовому импульсу происходит сдвиг информации в буферном запоминающем блоке, из которого было считано сообщение на обработку.

Далее цикл работы устройства повторяется путем обращения к очередному буферному запоминающему блоку.

Рассмотрим работу предлагаемого устройства для формирования маршрута сообщения в однородной вычислительно системе.

Передача информации между любыми процессорными элементами в системе осув;ествляется транзитным способом через другие процессорные элементы массива (фиГа 5), например, по восьми возможным направлениям (фиг, 6) с помощью предлагаемого устройства. Кроме того, в одно из восьми направлений информация может выдаваться от собственного процессорного элемента.

Каждому процессорному элементу в системе присваивается свой идентификатор - адрес, определяющий местоположение процессорного элемента в системе (номер Строки и номер столбца в матрице процессорных элементов), Пе- редаваемая транзитом информация состоит из трех частей адресной, операционной и контрольной.- Адресная часть представляет собой код адреса процессорного элемента, для которого предназначена данная операционная часть управляющего слова Контрольная часть слова представляет собой код (структуру), однозначно определяющий путь между двумя процессорными элементами - передатчиком и приемником информации по .минимальному физичеркому пути. По мере продвижения сообщения в сети процессорных

д 5 п

5

элементов происходит модификация сигнатуры кодом (идентификатором) транзитного процессорного элемента и направлением передаваемой информации.

Выбор направления передачи пришедшей информации в устройстве происходит следующим образом.

Адресная часть пришедшей информа-. ции сравнивается с адресом (идентификатором) данного устройства по номерам с-троки столбца и определяется одно из девяти возможных направлений передачи (восемь направлений - на соседние процессорные элементы, девятое - на обработку данному процессорному элементу) по следующему правилу. Пусть А и В - коды адресов процессорного элемента - источника информации соответственно по верти кали и горизонтали размещения процессорных элементов в матрице, а С и D - коды адресов процессорного элемента - приемника информации. .Выбор направления передачи информации оп- ределяется с помощью таблицы.

Перед началом работы устройства все элементы памяти на 1одятся в исходном (нулевом) состоянии.

В блоке 3 памяти констант записан код адреса (идентификатор) (код строки и код столбца) данного устройства относительно других устройств в однородной вычислительной Системе,

При отсутствии информации в буферных запоминающих блоках 1.1-1.9 (входные очереди запросов пусты) на выходах признаков загрузки этих блоков инициируются нулевые сигналы, которые не изменяют выходное состояние элемента ИЛИ.9, Нулевой сигнал с выхода элемента ИЛИ 9 не из- . меняет нулевого состояния триггера 19 запуска, а нулевой сигнал с его прямого выхода запрещает- формирование тактовых импульсов с выходов генератора 10.

При поступлении информации от соседних процессорных- элементов однородной структуры (iianpHMep, при передаче данных между процессорными элементами в системе с динамической архитектурой или в систолическом массиве) на выходе признака загрузки одного (или нескольких) из буферных запоминающих блоков 1.1-1.9-появляется единичный сигнал, который через элемент ИЛИ 9 устанавливает триггер 19 запуска в единичное сое9

тояние. Единичный сигнал на прямом выходе триггера 19 поступает на управляющий вход генератора 10 импульсов и разрешает формирование тактовых импульсов на его выходах для синхронизации работы устройства.

Тактовый импульс с выхода генератора 10 импульсов увеличивает содержимое счетчика 11 на единицу. На выходе дешифратора 12 инициируется единичный сигнал для опроса соответ- ствзлощего буферного запоминающего блока i.i (,9), Если очередь в блоке 1 буферной памяти не пуста, то код с выхода счетчика 11 поступает на управляющий вход мультиплексора 5 и разрешает по второму тактовому импульсу запись информации в буферный регистр 6,

Считываемая информация из буферных запоминающих блоков 1.1-1.9 состоит из трех частей - .адресной, операционной и контрольной, которые заносятся соответственно в поля 6.1- 6,3 буферного регистра 6 (фиг. Г),

В зависимости от вида обрабатываемой информации устройство может функционировать в двух режимах: обработки сообщения от собственного, цроцессорного элемента; обработки сообщения при передаче транзитной информации от соседних процесс орных элементов.

Отличие в функционировании устройства в режиме передачи информации от собственного процессорного элемента заключается в следующем. Так как в этом случае устройство является источником информации, то, следовательно, вместе с адресной и операционной частями сообщения должна быть выдана сигнатура маршрута прохождения информации в зависимости от кода адреса приемника информации. Все сигнатуры маршрутов прохождения информации от данного устройства записаны в блоке 2 памяти сигнатур. В поле 6,3 буферного регистра 6 находится нулевая контрольная информация

Счетчик 11 находится в состоянии, определяющем обращение к -буферному запоминающему блоку, в котором хранится информация от собственного процессорного элемента. На соответствующем выходе дешифратора 12 присутствует сигнал логической единицы, который, поступая на управляющий вхо коммутатора 13, разрешает прохожде0108010

ние через него информации с выхода блока 2 памяти сигнатур. Очередной тактовый импульс S j с выхода генера- „ тора 10 через элемент И 20 поступает на управляющий вход блока 2 памяти сигнатур и считывает из него информацию по адресу с выхода поля 6,1 буферного регистра 6,

10 Код сигнатуры с выхода блока 2

памяти сигнатур через коммутатор 13 . поступает на информационный вход де- мультиплексора 8, Кроме кода сигнатуры, на информационный вход де15 мультиплексора 8 поступает информация о коде адреса процессорного элемента - получателя информации, и непосредственно управлянлцей информации (например, начального адреса микро20 программы).

Выбор направления передачи информации от источника осуществляется блоком 4 выбора направления передачи информации (фиг. 2). Направление

25 передачи информации осзтцествляется по минимальному физическому пути между процессорным элементом - передатчиком информации и процессорным элементом - приемником на основе

30 сравнения двух кодов адресов процессорных элементов в однородной вычислительной среде. После анализа кодов адресов процессорных элементов в схемах 26 и 27 сравнения образуется

35 код направления, поступакнций на дешифратор 21 и дешифратор 29 демуль- . типлексора 8 (фиг. 3). Информация с входа- демультиплексора 8 в зависимости от кода направления передачи

40 поступает на один из выходов 24.1- 24,8 к одному из соседних процессорных элементов системы.

Очередной тактовый иь1пульс Z: с выхода генератора 10 поступает че45 рез i-й (.,8) элемент И 14.1 на соответствукнций выход 24.1 для синхронизации записи сообщения в буферный запоминающий блок соседнего уст- рбйства. Далее устройство функциони- 50 рувт аналогично описанному.

При обработке транзитной информации (сообщения) от одного из соседних процессорных элементов происхо дит обращение к соответствующему буgg ферному запоминающему блоку 1.1-1.8. Через мультиплексор 5 сообщение заносится в буферный регистр 6. При этом в поле 6.3 находится код сигнатуры маршрута прохождения между процессорными элементами вычислительной системы.

На информационный вход,демульти- плексора 8 поступает код

Апер(,)

А и А . - код адреса приемника информации соответственно по вертикали и горизонтали в матрице процессорных элементов оп операционная часть сообщения;

S - код сигнатуры; 4И - знак конкатенации (сцепления) кодов. При передаче транзитной информации код сигнатуры при прохождении устройства модифицируется кодом адреса (идентификатором) устройства и кодом направления выдачи информаци в одно из возможных направлений. Модификация кода сигнатуры, поступающего с выхода поля 6.3 буферного ре- гистр.а 6, происходит на блоке 7 суммирования по модулю два кодом направления, поступающим с выхода блока 4 выбора направления передачи информации и кодом адреса (идентификатора) с выхода блока 3 памяти констант. Полученная сигнатура (с учетом прохождения данного устройства и направления выдачи информации) с выхода блока 7 сз мирования по модулю два через коммутатор 13 поступает для дальнейшей ее передачи совместно с адресной и операционной частями в соседние аналогичные устет при поступлении импульса с выхода генератора 10 прохождение операционной части сообщения (например, кода

операции) на выход 23 устройства для дальнейшей его обработки собственным процессорным элементом. Кроме того, управляющий сигнал с выхода блока 4 выб.ора направления передачи информации поступает: на управляющий вход синхронизации триггера 18. На входы элемента И 16 с нулевых выходов поля 6,3 буферного регистра 6 поступает код сигнатуры. Ошибка в формировании

маршрута сообщения отсутствует при , в противном случа е маршрут прохождения сообщения отличен от запланированного. При нулевой сигнатуре на выходе элемента И i 6 присутс-твует сигнал логической единицы, идентифицирующий правильность прохождения маршрута сообщения. Этот сигнал поступает на инверсный вход триггера 18 управления и не изменяет

его состояния. При сигнал логического нуля с выхода эдтемента И 16 устанавливает триггер 18 в единичное состояние. На прямом выходе триггера 18 появляется сигнал логической единиць1, поступающий на выход 25 уст- ройства и идентифицирующий различия в пройденном маршруте с запланированным, т«ео признак , ошибки,

Если очереди сообщений в буферных

запоминающих блоках 1.1-1,9 пусты, то на выходе элемента ИЛИ 9 присутствует сигнал логического нуля. Этот сигнал поступает на инверсный вход элемента И 17 и разрешает при выда-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| МОДУЛЬ ДЛЯ ОБМЕНА СООБЩЕНИЯМИ | 2003 |

|

RU2249849C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ | 2000 |

|

RU2175144C1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных матричных конвейерных и других процессоров, в которых в процессе обработки информации происходит движение данных в вычислительной среде. Цель изобретения - повышение быстродействия устройства при одновременном повышении достоверности передаваемой транзитной информации. Для достижения указанной цели в устройство дополнительно введены блок 2 памяти сигнатур, блок 7 суммирования по модулю два, коммутатор 13 и триггер 18 управления. Использование сигнатур маршрутов прохождения информации по минимальному физическому пути между элементами однородной вычислительной системы, а также контроль сигнатур элементом - приемником позволяет реализовать указанные преимущества. 10 ил., 1 табл.

ройства на информационный вход демуль-40 че последнего сообщения на соседнее

типлексора 8. Далее устройство функционирует аналогично описанному. По мере продвижения сообщения в матрице от модуля (устройства) - источника информации к модулю - приемнику информации происходит модификация сигнатуры маршрутом прохождения.

При совпадении кодов адресов модуля-приемника информации.с адресной частью принятого сообщения на выходах Равно первой 26 и второй 27 схем сравнения блока 4 выбора направления передачи информации формируют- ся сигналы логической единицы. На выходе элемента И 28 также присутствует сигнал логической.единицы. Этот сигнал с выхода блока 4 выбора направления передачи информации поступает

устройство импульсом с выхода генератора 10 обнуление триггера 19 запуска. На этом устройство заверш.ает свою работу.,

45

Запись -информации от соседних устройств или собственного процессорного элемента для ее анализа и дальнейшей передачи происходит следую5Q щим образом. Сообщение от соседнего устройства поступает на информационны вход соответствующего буферного запоминающего блока (фиг, 4).С информационного входа буферного запоминающего

gg блока .сообщение поступает на информационный вход демультиплексора 32.

В.начальный момент времени элементы памяти буферного запоминающего блока

на вход блока 15 элементов И иразреша- (блок регистров 31.1-31.К) находится

устройство импульсом с выхода генератора 10 обнуление триггера 19 запуска. На этом устройство заверш.ает свою работу.,

Запись -информации от соседних устройств или собственного процессорного элемента для ее анализа и дальнейшей передачи происходит следующим образом. Сообщение от соседнего устройства поступает на информационный вход соответствующего буферного запоминающего блока (фиг, 4).С информационного входа буферного запоминающего

блока .сообщение поступает на информационный вход демультиплексора 32.

В.начальный момент времени элементы памяти буферного запоминающего блока

13I

в нулевом состоянии. На нулевых выхо- да х j-ro регистра 31 .j (j l,K) присутствуют сигналы логической единицы поэтому на выходах соответствующих элементов И 34.1-34.К присутствуют также сигналы логических единиц. Буферный запоминающий блок реализует дисциплину обслуживания типа FIFO (первым прии1ел - первым обслужен). Код, образованный выходом элементов И 34.1-.34,К, управляет процедурой записи поступающей информации в соответствующий регистр буферного запоминающего блока. Так, при коде 1 , . . 1 , поступающем на адресный вход демультиплексора 32, информация записывается в регистр 31.1, при коде 11...10 - во второй 31.2 регистр и т.д., одновременно с поступлением в буферный запоминающий блок информации на синхронизируюЪ;ий вход поступает тактовьй импульс. Этот импульс через элементы И 35,1- 35,К и элементы ИЛИ 36,1-36,К посту- пает на синхронизирующие входы блока регистров 31,1-31,К, Однако запись поступившей информации производится только в регистр 31.1, так как адресный код демультиплексора 32 разрешает прохождение информации через блок элементов ИЛИ 33,1 на информационный вход регистра 31.1, Состояние этого регистра отлично от нулевого, и на выходе элемента И 34,1 появляется сигнал логического нуля, который за- прещает поступление тактовых импульсов через элемент И 35,1 и элемент ИЛИ 36,1 на синхронизирующий вход регистра 31,К Управляющий код изменя- ется, и аналогичным образом очередное сообщение заносится во второй регистр 31,2 и Т.Д-. При изменении состояния одного из регистров 31.1- 31,К на выходе элемента И 38 появляется сигнал логического нуля и после инвертирования на элементе НЕ 39 на зшравляющем выходе буферного запоминающего блока появляется сигнал логической е : иницы, определяющий наличие сообщения в соответствующем буферном запоминающем блоке, Ло этому сигналу через элемент ИЛИ 9 (фиг,1) триггер 19 запуска устанавливается: в единичное состояние и устройство начинает функционирование аналогично- описанному, , .

После обра.ботки информации (первого сообщения) последний тактовый им

01080

пульс цикла обработки поступает на синхронизирующий вход соответствую- щего буферного запоминающего блока, на управляющий вход которого с выхода дешифратора 12 устройства поступает сигнал, разрешающий сдвиг информации в блоке регистров 3J,1-31,K буферного запоминающего блока (фиг.4)

10 Управляющий сигнал поступает на вход элемента И 37, Тактовый импульс с выхода генератора 10 импульсов через элемент И 37 и элементы ИЛИ 36,1- 36,К поступает на синхронизирующие

Ig входы блока регистров 31,1-31.К, разрешая сдвиг информации (очереди поступивших на обслуживание сообщений), Лри этом данным импульсом блокируется по инверсному управляющему

2Q входу демультиплексор 32, В результате на его выходах присутствуют только нулевые сигналы, которые исключают искажение информации на блоках элементов ИЛИ 33, Далее генера25 тор 10 импульсов формирует тактовый импульс, которьй поступает на третий вход счетчика 11, и начинается первая фаза очередного цикла обработки поступившего сообщения.

Формула изобретения

Устройство для формирования маршрута сообщения в однородной вычис лительной системе, содержащее девять буферных запоминающих блоков, мультиплексор, буферный регистр, блок памяти констант, блок выбора направления передачи информации, триггер

40 запуска, генератор импульсо.в, счетчик, два дешифратора, два блока элементов И, демультиплексор, элемент ИЛИ и три элемента И, причем информационные входы первого, второго,

4g третьего, четвертого, пятого,шестого, седьмого, восьмого и девятого буферных запоминающих блоков являются первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым

55 буферных запоминающих блоков являются первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым и девятым управляющими входами устройс 1-ьа соответственно, вторые

управляющие входы первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого буферных запоминающих блоков соединены с первым выходом генератора импульсов, третьи управляющие входы первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого буферных запоминающих блоков соединены с первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым ;зыходами первого дешифратора соответственно, управляющие выходы первого второго5третьего, четвертого, -пятого5 шестого, седьмого, восьмого и девятого буферных запоминающих блоков соединены с первым, вторым, третьим;, четвертым, пятым, шестым, седьмым, . восьмым и девятым входа.ми элемента ШШ соответственно, информационные выходы первого, второго, тре- тьего четвертого, пятого,шестого, седьмого, восьмого и девятого буферных запоминающих блоков соединены с первым, вторым, третьим, четвертым пятым, шестым, седьмым, восьмым и девятым, информационными входами мультршлексора соответственно, второ выход генератора импульсов соединен с управляющим входом буферного регисра информационный вход которого подключен к выходу мультиплексора, уп- равляющий вход которого соединен с выходом счетчика, третий выход генератора импульсов подключен к счетному входу, счетчика, выход которого соединен с входом первого дешифратора, четвертый выход генератора импульсов соединен, с прямым входом первого элемента И, первым входом первого блока элементов И и первым входом второго блока элементов И, пятый выход генератора импульсов соединен с первым входом второго элемента И и с входом синхронизации блока памяти констант, первый выход которого соединен с первым входом блока выбора направления передачи информации, уп- равляющий выход которого подключен к второму входу первого блока элементов И, вьгход элемента ИЛИ соединен с входом установки единицы триггера запуска и с инверсным входом, первого элемента И, выход которого соединен с входом установки нуля триггера за- ггуска выход которого соединен с входом генкрат ора импульсов, перв1чй

выход первого дешифратора соединен с вторым входом второго элемента И, первый выход буферного регистра соединен с третьим входом первого блока элементов И, выход которого является первым информационным выходом устройства, второй выход буферного регистра соединен с вторым входом блока выбора направления передачи информации, первый и второй выходы буферного регистра соединены с первой и второй группами разрядов входа демультиплексора соответственно,

третий выход буферного регистра соединен с входом третьего элемента И, информационный выход блока выбора направления передачи информации подключен к входу второго дешифратора

и адресному, входу демультиплексора, первьй, второй, третий, четвертый, пятьй, шестой, седьмой и восьмой выходы которого являются вторым, третьим, четвертым, пятым, шестым, седъмым, восьмым И девятым информационными выходами устройства соответственно, выход второго дешифратора соединен с вторым входом второго блока элементов И, выход которого является первым управляющим выходом устройства, о тличающее ся тем, что, с целью повьш&ния быстро- . действия устройства при одновременном поБьщ ении достоверности переда- ваемой транзитной информации, в него введены блок памяти сигнатур, блок суммирования по модулю два, коммутатор и триггер управленияj причем первый управляющий выход блока выбоpa направления передачи информации соединен с входом синхронизации триггера управления, информационный вход которого подключен к выходу третьего элемента И, выход триггера управления является вторым управляняцим цы ходом устройства, первый выход первого дешифратора соединен с управляющим входом коммутатора, выход которого подключен к третьей группе раз-рядов входа демультиплексора, второй выход блока памяти констант соединен с первым входом блока суммирования по модулю два, выход которого соединен с первым входом коммутатоpa, второй вход которого подключен к выходу блока памяти сигнатур, информационный вход которого соединен с вторым выходом буферного .регистра, третий выход которого подключен к

17150108018

первой группе разрядов второго входа выходом блока выбора направления пеблока суммирования по модулю два, вторая группа разрядов второго входа которого соединена с информационным

редачи информации, управляющий вход блока памяти сигнатур соединен с выходом второго элемента И.

Фиг. 2

выходом блока выбора направления передачи информации, управляющий вход блока памяти сигнатур соединен с выходом второго элемента И.

Si mi

8

29

Фиг.З

ffffi

OL

0(1) com}

т(7)

пз

(LJ)

Щ5) ОЩ4)

/,/

(001,001)

2J

(оюм

3J (011,001)

s«-3 000001 © OfO 010 © 000001 © OOi oil- 01100i

a

Sn oil001 © QOQQ01 $) 010010 © 00000/ © 0010//-000000 Sf 011001 © 00000/ © 0/00/0® 000010 © 0100/1 0//0//ФО

ff

Фиг.8

.2

(001,010)

1,3 (001,011)

3,Z (011,010)

3,3 (0/1,01/)

Фиг.7

Фиг.9

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1985 |

|

SU1312597A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-08—Подача