(5) УСТРОЙСТВО для ВВОДА ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь символов для устройств отображения на матричных экранах | 1981 |

|

SU1005175A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство обнаружения кодов групповой синхронизации | 1990 |

|

SU1812628A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| Устройство для обучения | 1983 |

|

SU1273974A1 |

| Устройство для ввода информации | 1983 |

|

SU1151942A1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

1

Устройство относится к автоматике и может быть использовано при построении вводных устройств.

Известно устройство для ввода информации, в котором коммутационные элементы опрашиваются cчetчикoм через дешифратор.При включении коммутационного элемента шифратор, выполненный на логических схемах, вырабатывает код IQ группы и останавливает счетчик, на выходе которого устанавливается код СПНедостатком устройства является то, что шифратор, выполненный на логических схемах, счетчик и дешифра- is тор образуют очень сложную схему.

Наиболее близким к изобретению по выполняемой функции и достигаемому результату является устройство для ввода информации, в котором с гене- 20 ратора импульсов через открытый эле|Мент И импульсы подаются на вход счетчика, с выхода которого двоичный

КОД преобразуется в десятичный дёшйф ратором, а таюхе подается на адрес- . ные входы коммутатора. Дешифратор опрашивает коммутационные элементы матрицы по вертикальным шинам, горизонтальные шины подключены к входу коммутатора. При включении коммутационного элемента коммутатор вырабатывает импульс, перебрасывающий триггер в другое состояние, запрещающий прохождение импульсов с генератора через элемент И на вход счетчика. На выходе счетчика устанавливается код соответствующего коммутационного элемента. При выключении коммутационного элемента триггер устанавливается в исходное состояние через элемент задержки, осуществляющий задержку си1- нала на время дребезга в коммутационном элементе 2..

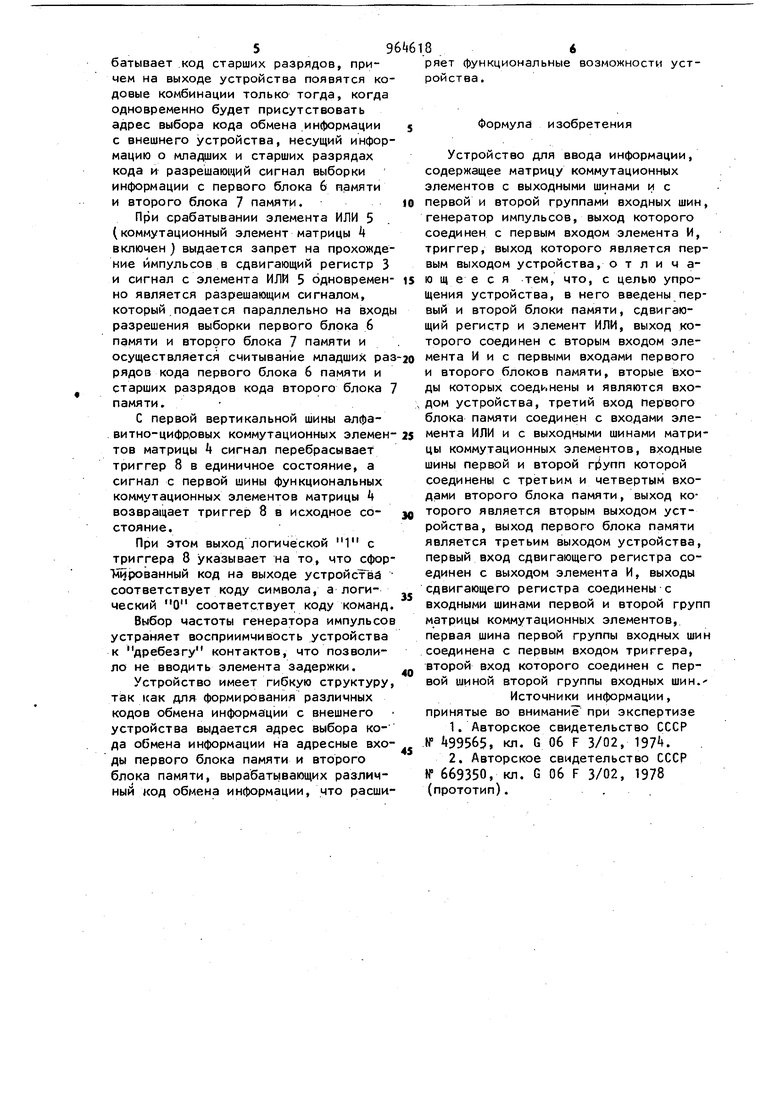

Известное устройство имеет следующие недо.статки. Формирование кода осуществляется по последовательной схеме в три этапа, когда двоичный код с выхода счетчика преобразуется в десятичный дешифратором ( этап), затем десятичный код преобразуется в последовательный код коммутатором (2 этап), сформированный сигнал запоминается триггером (3 этап ) и выдается на выход устройства. Такие преобразования при формирова нии кода увеличивают аппаратурные за траты. На выходе устройства формируются кодовые комбинации независимо от того, включен коммутационный элемент или нет. Триггер, сработав, вырабатывает сигнал, указывающий, что на выходе устройства код соответст вуёт включенному коммутационному эле менту. Поэтому необходимо стробировать выходы счетчика сигналом с триг гера, а именно вводить элементы И,, что приводит к увеличению аппаратурных затрат. Устройство имеет жесткую структуру, так как формирует только один определенный код для обмена информаци и. Для формирования другого вида кода обмена, например ИСО, КОИКОИ-8 и т.д., необходимо наращивать устройство, что увеличивает аппаратурные затраты и снижает функциональ ные возможности устройства. Целью изобретения является упрощение устройства. Указанная цель достигается тем, что в устройство для ввода информации , содержащее матрицу коммутационных элементов с выходными шинами и с первой и второй группами входных шин генератор импульсов, выход которого соединен с первым входом элемента И, триггер, выход которого является первым выходом устройства, введены первый и второй блоки памяти сдвигающий регистр и элемент ИЛИ, выход которого соединен-, с вторым входом элемента И и с первыми входами первого и второго блоков памяти, вторые входы которых соединены и являются входом устройства, третий вход первого блока памяти соединен с входами элемента ИЛИ и с выходными шинами матрицы коммутационных элементов, входные шины первой и второй групп которой соединены с тре тьим и четвертым входами второго бло ка памяти, выход которого является; вторым выходом устройства, выход пер вбго блока памяти является третьим выходом, устройства, первый вход сдви гающего регистра соединен с (5ыходом 84 элемента И, выходы сдвигающего регистра соединены с входными шинами первой и второй групп матрицы коммутационных элементов, первая шина первой группы входных шин соединена с входом триггера, йторой вход которого соединен с первой шиной второй группы входных шин. На чертеже представлена структурная ;хема устройства для ввода инфорнации. Устройство содержит генератор 1 импульсов, элемент И 2, сдвигающий регистр 3 матрицу коммутационных элементов, элемент ИЛИ 5, первый блок 6 памяти, второй блок 7 памяти и триггер 8. Устройство работает следующим о.бpai3OM. . . Тактовые импульсы с выхода генераIropa 1 импульсов поступают на один вход элемента И 2, на другой вход которого подается разрешающий сигнал с элемента ИЛИ 5, когда коммутациоиные элементы матрицы находятся в исходном состоянии (не нажаты). При включений коммутационного элемента матрицы с элемента ИЛИ 5 выдается запрещащий сигнал на прохождение им-пульсов с генератора 1 импульсов чеpeз элe eнт И 2. С поступлением разрешающего сигнала на другой вход элемента И 2 импульсы, подаваемые с генератора 1 импульсов через элемент И 2 на вход сдвигающего регистра 3 сдвигают записанную в исходном состоянии регистра логическую единицу. На выхог де сдвигающего регистра 3 тактовые импульсы опрашивают коммутационные элементы матрицы по вертикальным шинам. При включении коммутационного элемента матрицы l сигнал с соответствующего выхода сдвигающего регистра 3 через вертикальную шину матрицы k и замкнутый контакт коммутационного элемента поступает на горизонтальную шину матрицы 4, При этом вертикаль-, ная шина указывает адрес старших разрядов, а горизонтальная шина - адрес младших разрядов. С горизонтальной шины адрес младших разрядов подается на адресный вход первого блока 6 памяти, который вырабатывает код младших разрядов, а с вертикальной шины адрес старших разрядов поступает на адресный вход второго блока 7 памяти, который вырабатывает .код старших разрядов, причем на выходе устройства появятся ко довые комбинации только тогда, когда одновременно будет присутствовать адрес выбора кода обмена информации с внешнего устройства, несущий инфор мацию о младших и старших разрядах кода и разрешаю1ций сигнал выборки информации с первого блока 6 памяти и второго блока 7 памяти. При срабатывании элемента ИЛИ 5 (коммутационный элемент матрицы k включен ) выдается запрет на прохожде ние импульсов в сдвигающий регистр 3 и сигнал с элемента ИЛИ 5 одновремен но является разрешающим сигналом, который подается параллельно на вход разрешения выборки первого блока 6 памяти и второго блока 7 памяти и осуществляется считывание младший pa рядов кода первого блока 6 памяти и старших разрядов кода второго блока памяти. С первой вертикальной шины алфавитно-цифррвых коммутационных элемен тов матрицы k сигнал перебрасывает триггер 8 в единичное состояние, а сигнал с первой шины функциональных коммутационных элементов матрицы 4 возвращает триггер 8 в исходное состояние. При этом выход логической 1 с триггера 8 указывает на то, что сфор ййрованный код на выходе устройсТвй соответствует коду символа, а логический О соответствует коду команд Выбор частоты генератора импульсо устраняет восприимчивость устройства к дребезгу контактов, что позволило не вводить элемента задержки. Устройство имеет гибкую структуру так как для формирования различных кодов обмена информации с внешнего устройства выдается адрес выбора кода обмена информации на адресные вхо ды первого блока памяти и второго блсзка памяти, вырабатывающих различный код обмена информации, что расши ряет функциональные возможности устройства. Формула изобретения Устройство для ввода информации, содержащее матрицу коммутационных элементов с выходными шинами и с первой и второй группами входных шин, генератор импульсов, выход которого соединен с первым входом элемента И, триггер, выход которого является первым выходом устройства, отличающее с я тем, что, с целью упрощения устройства, в него введены первый и второй блоки памяти, сдвигающий регистр и элемент ИЛИ, выход которого соединен с вторым входом элемента И и с первыми входами первого и второго блоков памяти, вторые входы которых соединены и являются входом устройства, третий вход первого блока памяти соединен с входами элемента ИЛИ и с выходными шинами матрицы коммутационных элементов, входные шины первой и второй riiynn которой соединены с третьим и четвертым входами второго блока памяти, выход которого является вторым выходом устройства, выход первого блока памяти является третьим выходом устройства, первый вход сдвигающего регистра соединен с выходом элемента И, выходы сдвигающего регистра соединены с входными шинами первой и второй групп матрицы коммутационных элементов, первая шина первой группы входных шин соединена с первым входом триггера, второй вход которого соединен с первой шиной второй группы входных шин. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 995б5, кл. G Об F 3/02, 197t. 2.Авторское свидетельство СССР № 669350, кл. G Об F 3/02, 1978 (прототип).. . A/ фoSe//77//ffг/г/0I - / - ..I y /rgfi/ff ff AMXf |.. T A/fff/

Авторы

Даты

1982-10-07—Публикация

1980-12-16—Подача