Изобретение относится к вычисли- тельной технике и может быть использовано для статического моделирова- ния систем массового обслуживания, в частности для моделирования узлов коммутации сообщений в сетях электронных вычислительных машин (ЭВМ).

Целью изобретения является расширение функциональных возможностей за счет обеспечения загрузки-сообщений в буферный накопитель анализа признаков,.выбора выходных каналов и передачи сообщений соседнему узлу

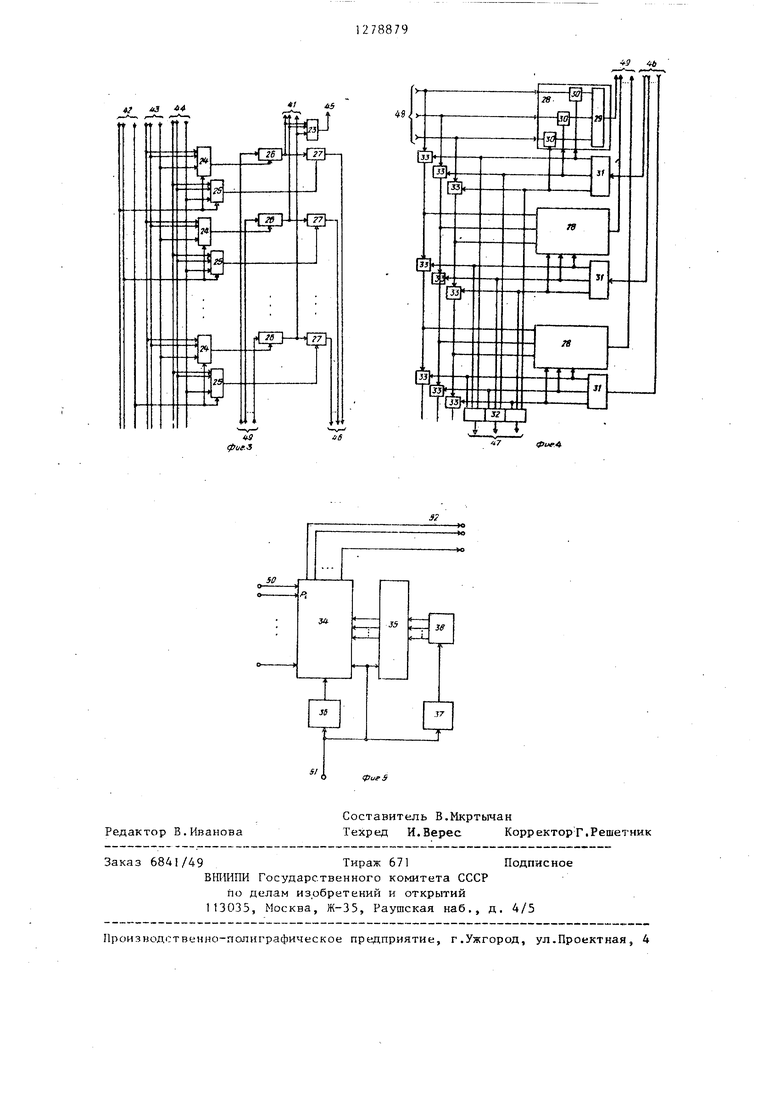

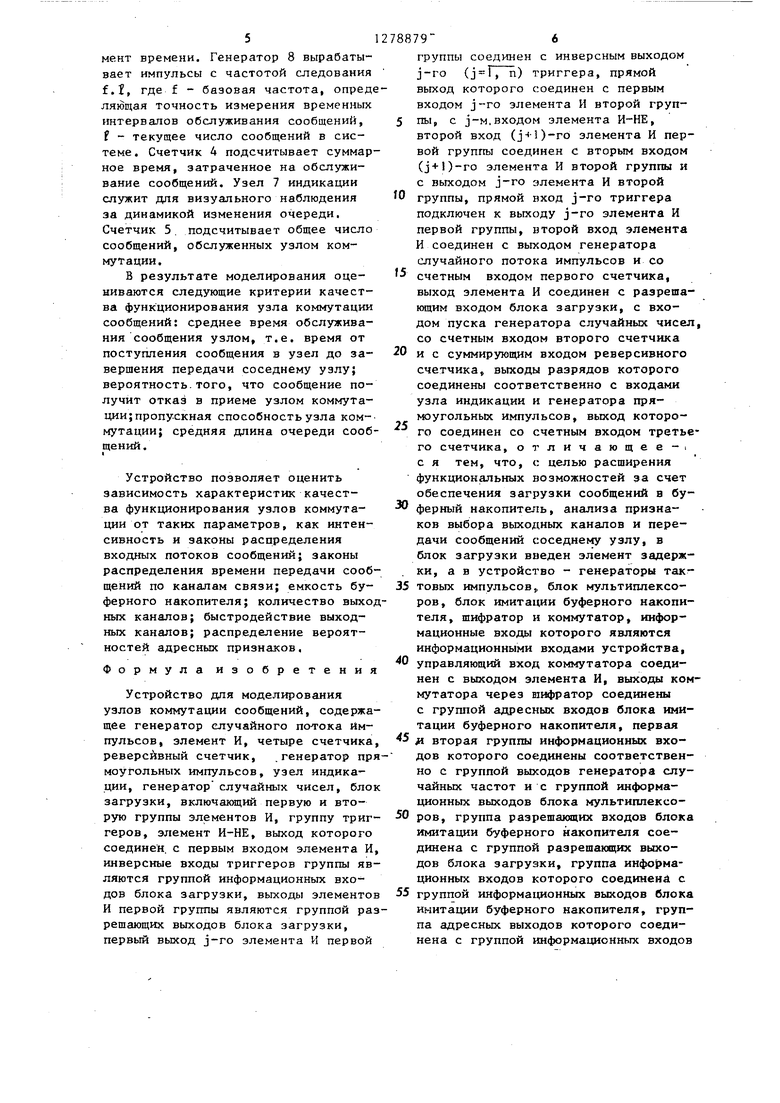

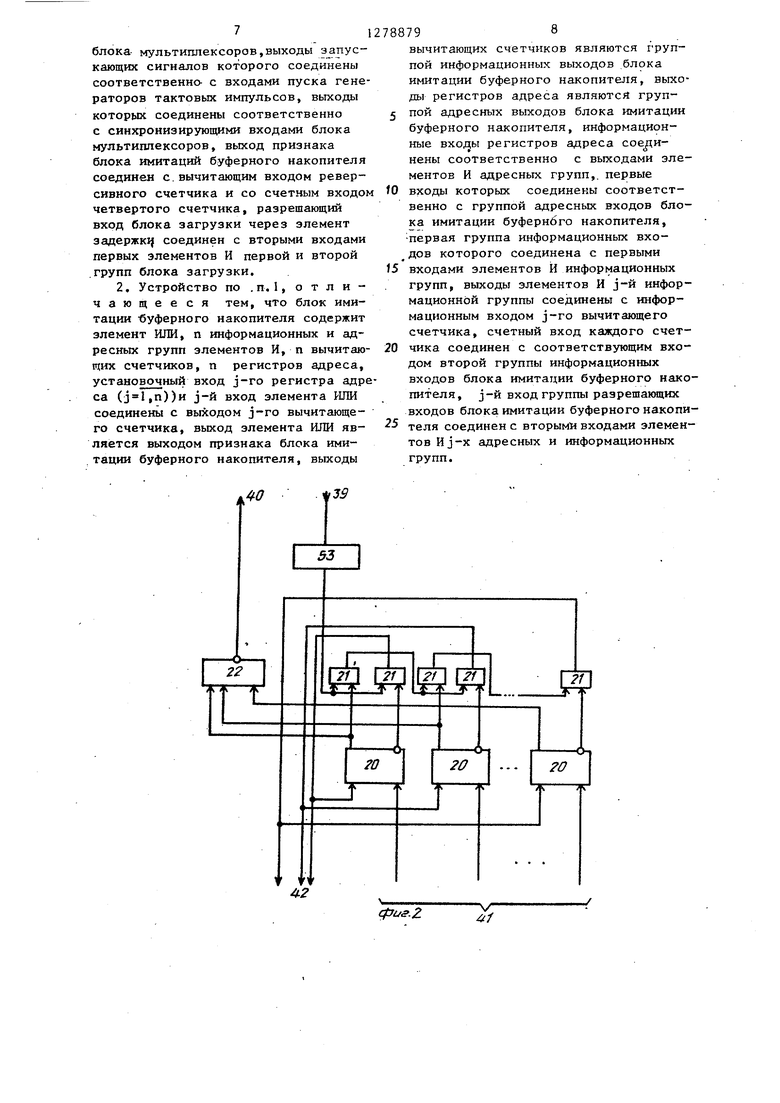

На фиг. 1 приведена блок-схем а устройства; на фиг, .2 - схемы блок загрузки; на фиг, 3 - схемы блока имитации буферного накопителя; на фиг, 4 - схема блока коммутации; на фиг, 5 - схема коммутатора.

Устройство содержит блок I обработки, включающий счетчики 2-5, реверсивный счетчик 6, узел 7 индикации, генератор 8 прямоугольных импульсов , генератор 9 случайного потока импульсов, генератор 10 случайных чисел, элемент И 11, блок 12 загрузки, коммутатор 13, шифратор 14, блок 15 имитации буферного накопителя, блок 16 коммутации, .генераторы 17-19 тактовых импульсов триггеры 20, элементы И 21, элемент И-НЕ 22, элемент ИЛИ 23, группы 24 и 25 элементов И, вычитающие счетчики 26, регистры 27 адреса, мультиплексоры 28, элемент ИЛИ 29, элементы И 30, дешифраторы 31, группы 32 элементов ИЛИ, группы 33 элементов запрета, схему 34 сравнения, регистр 35, элементы 36 и 37 задержки, генератор 38 случайных чисел, связи 39-52 и элемент 53 задержки.

Устройство работает следующим образом.

Случайный процесс поступления сообщений в узел коммутации моделируется с помощью генератора 9, который с заданной интенсивностью генерирует случайный поток импульсов, имитирующий поступление сообщений со всех приемных каналов узла коммутации. Сообщения, передаваемые в узел коммутации, могут быть приняты только при наличии свободных зон в буферном накопителе,.

Блок 12 контролирует наличие свободных зон в блоке 15 и при их

5

0

5

0

5

0

5

0

5

наличии элемент И I1 будет открыт, При поступлении очередного импульса с генератора 9 на .выходе элемента И 1 1 появляется импульс, имитирующий поступление сообщения. Импульс поступает на генератор 10 случайных чисел, который вырабатывает двоичное число, пропорциональное длине сообщения. Это число поступает на группы 24 элементов И (фиг, 3) и далее на один из свободных счетчиков 26, которые имитируют отдельные зоны буферного накопителя. Выбор счетчика обеспечивается разрешающим сигналом, которьй вырабатывается бло ком 12 и поступает по связи 42 на группы 24 и 25 элементов И, Разрешающий сигнал выдается блоком 12 при поступлении каждого очередного импульса с элемента И И, если в блоке 15 есть хотя бы одна свободная зона.

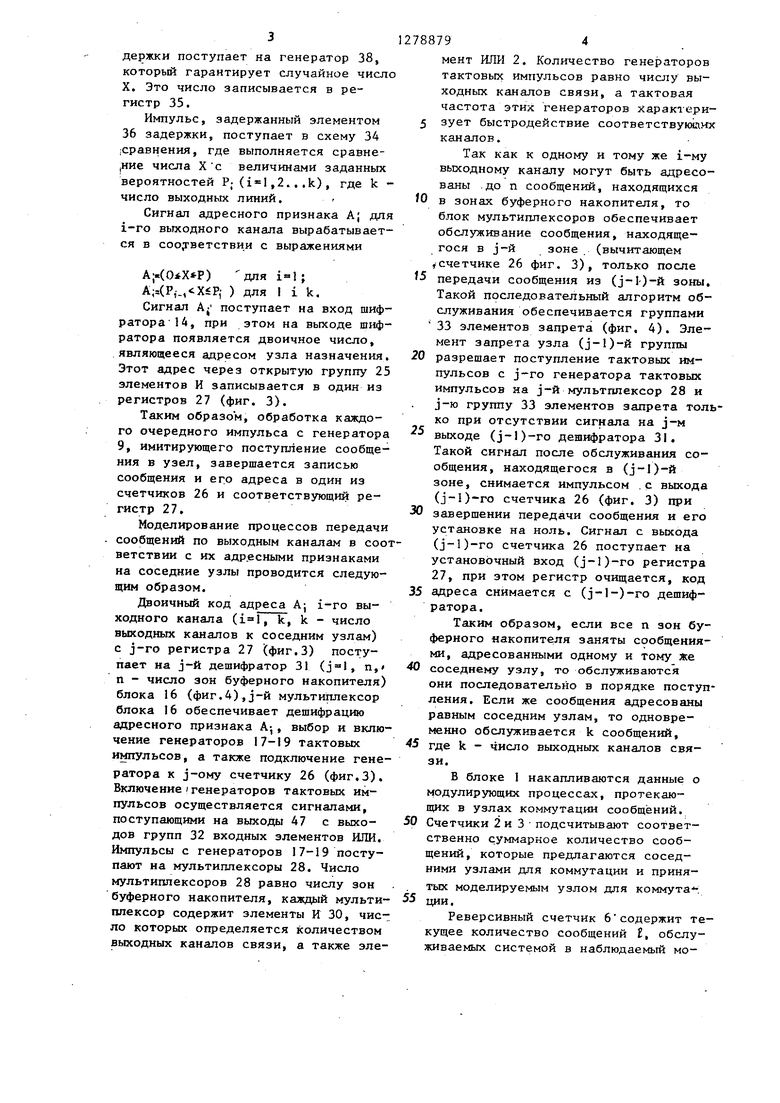

Наличие свободных зон контролируется с помощью триггеров 20 (фиг, 2), Количество триггеров равно числу зон. Если зона свободная, то соответствующий триггер находится в нулевом состоянии, импульс с вькода 39 через открытый элемент И 21 поступает в блок 15, при этом триггер устанавливается в €«диничное состояние. Блок 15 по выходу 40 выдает сигнал, вырабатываемый элементом И-НЕ 22 при наличии хотя бы одной свободной зоны.

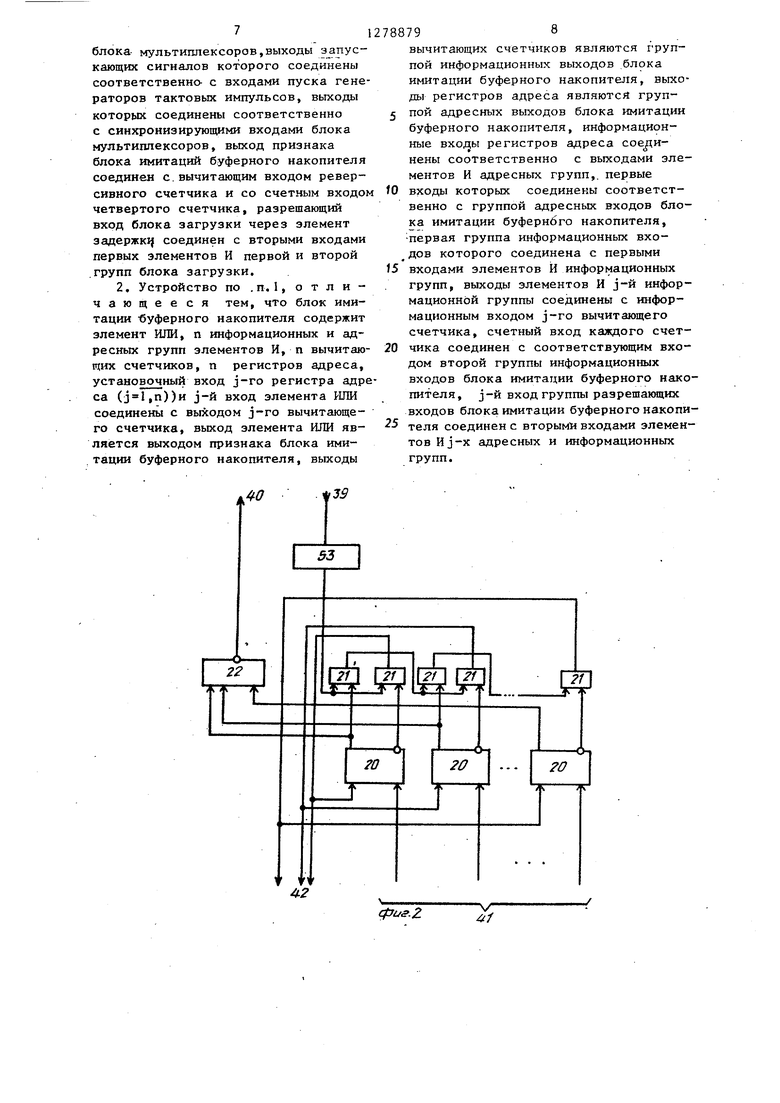

Адреса узлов назначения формируются коммутатором 13 и шифратором 14, Случайный поток импульсов, посту пающий на вход 51 коммутатора 13, разделяется- по выходам 52 в соответствии с вероятностями, задавае№ 1ми на входах 50 (фиг, 5) Количество входов коммутатора 13 равно числу выходных линий, связывающих моделируемый узел с соседними узлами. Если, например, количество выходных линий в узле три и заданные вероятности распределения сообщений по этим ли-. ниям равны ,2, ,5, ,3, то каждое очередное сообщение адресуется для передачи по первой, второй и третьей линиям с вероятностями соответственно 0,2; 0,5; 0,3. Импульс, имитирующий поступление сробщения, появляется на входе 51 коммутатора 13, устанавливает схему 34 сравнения и регистр 35 в исходное состояние и через элемент 37 задержки поступает на генератор 38, который гарантирует случайное число X. Это число записывается в регистр 35,

Импульс, задержанный элементом 36 задержки, поступает в схему 34 ;сравнения, где выполняется сравне- |Ние числа X с величинами заданных вероятностей Р; (i ,2...k), где k - число выходных линий.

Сигнал адресного признака Aj для i-ro выходного канала вырабатывается в соо ветстви.и с выражениями

А;-() для

А;(Р.,,- ) для I i k.

Сигнал Aj поступает на вход шифратора 14, при этом на выходе шифратора появляется двоичное число, являющееся адресом узла назначения. Этот адрес через открытую группу 25 элементов И записывается в один из регистров 27 (фиг. 3).

Таким образом, обработка каждого очередного импульса с генератора 9, имитирующего поступление сообщения в узел, завершается записью сообщения и его адреса в один из счетчиков 26 и соответствующий регистр 27.

Моделирование процессов передачи сообщений по выходным каналам в соответствии с их адресными признаками на соседние узлы проводится следующим образом.

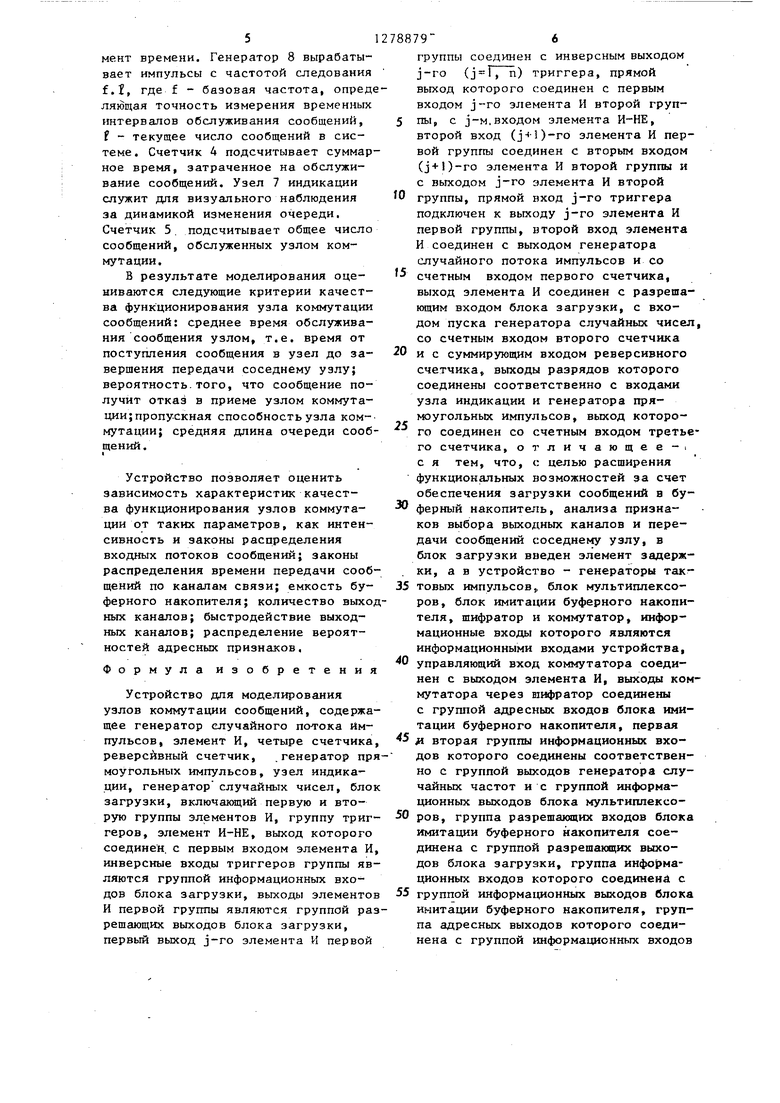

Двоичный код адреса А; выходного канала (, k, k - число выходных каналов к соседним узлам) с j-ro регистра 27 (фиг.З) поступает на j-й дешифратор 31 (j, п, п - число зон буферного накопителя) блока 16 (фиг.4),j-й мультиплексор блока 16 обеспечивает дешифрацию адресного признака А;, выбор и вклю 5

20

40

чение генераторов 17-19 тактовых импульсов, а также подключение генератора к j-ому счетчику 26 (фиг,3). Включение:генераторов тактовых импульсов осуществляется сигналами, поступающими на выходы 47 с выходов групп 32 входных элементов ИЛИ, Импульсы с генераторов 17-19 поступают на мультиплексоры 28. Число мультиплексоров 28 равно числу зон буферного накопителя, каждый мульти- 55 плексор содержит элементы И 30, число которых определяется количеством выходных каналов связи, а также эле30

35

45

50

10

788794

мент ИЛИ 2. Количество генераторов тактовых импульсов равно числу выходных каналов связи, а тактовая частота этих генераторов харакя ери- 5 зует быстродействие соответствующих каналов.

Так как к одному и тому же i-му выходному каналу могут быть адресованы .до п сообщений, находящихся в зонах буферного накопителя, то блок мультиплексоров обеспечивает обслуживание сообщения, находящегося в j-й зоне (вычитающем счетчике 26 фиг. 3), только после 5 передачи сообщения из (j-I-)-A зоны. Такой последовательный алгоритм обслуживания обеспечивается группами 33 элементов запрета (фиг, 4), Элемент запрета узла (j-l)-й группы разрешает поступление тактовых импульсов с j-ro генератора тактовых импульсов на j-й мультплексор 28 и j-ю группу 33 элементов запрета только при отсутствии сигнала на j-м выходе (j-l)-ro дешифратора 31.

Такой сигнал после обслуживания сообщения, находящегося в (j-l)-й

20

зоне , снимается импульсом .с выхода (j-l)-ro счетчика 26 (фиг, 3) при

завершении передачи сообщения и его установке на ноль. Сигнал с выхода (j-l)-ro счетчика 26 поступает на установочный вход (j-l)-ro регистра 27, при этом регистр очищается, код

адреса снимается с (j-l-)-ro дешифратора.

Таким образом, если все п зон буферного накопителя заняты сообщениями, адресованными одному и тому Ясе соседнему узлу, то обслуживаются они последовательно в порядке поступления. Если же сообщения адресованы равным соседним узлам, то одновре- h№HHo обслуживается k сообщений,

где k - число выходных каналов связи.

В блоке 1 накапливаются данные о модулирующих процессах, протекающих в узлах коммутации сообщений.

Счетчики 2 и 3подсчитывают соответственно суммарное количество сообщений, которые предлагаются соседними узлами для коммутации и принятых моделируемым узлом для коммута -: ции.

Реверсивный счетчик 6 содержит текущее количество сообщений , обслуживаемых системой в наблюдаемый мо51

мент времени. Генератор 8 вырабатывает импульсы с частотой следования f.lf где f - базовая частота, определяющая точность измерения временных интервалов обслуживания сообщений, f - текущее число сообщений в системе. Счетчик 4 подсчитывает суммарное время, затраченное на обслуживание сообщений. Узел 7 индикации служит для визуального наблюдения за динамикой изменения очереди. Счетчик 5. подсчитывает общее число сообщений, обслуженных узлом коммутации.

В результате моделирования оцениваются следующие критерии качества функционирования узла коммутации сообщений: среднее время обслуживания сообщения узлом, т.е. время от поступления сообщения в узел до завершения передачи соседнему узлу; вероятность.того, что сообщение получит отказ в приеме узлом коммутации; пропускная способность узла коммутации; средняя длина очереди сообщений .

Устройство позволяет оценить зависимость характеристик качества функционирования узлов коммутации от таких параметров, как интенсивность и законы распределения входных потоков сообщений; законы распределения времени передачи сообщений по каналам связи; емкость буферного накопителя; количество выходных каналов; быстродействие выходных каналов; распределение вероятностей адресных признаков,

Формула изобретения

Устройство для моделирования узлов коммутации сообщений, содержащее генератор случайного патока импульсов, злемент И, четыре счетчика, реверсивный счетчик, .генератор прямоугольных импульсов, узел индикации, генератор случайных чисел, блок загрузки, включающий первую и вторую группы элементов И, группу триггеров, элемент И-НЕ, выход которого соединен, с первым входом элемента И, инверсные входы триггеров группы являются группой информационных входов блока загрузки, выходы элементов И первой группы являются группой раз рещающих выходов блока загрузки, первый выход j-ro элемента И первой

группы соединен с инверсным выходом j-ro {j n n) триггера, прямой выход которого соединен с первым входом j--ro элемента И второй группы, с J-M.входом элемента И-НЕ,

второй вход (j-i-O-ro элемента И первой групггы соединен с вторым входом ()-ro элемента И второй группы и с выходом j-ro элемента И второй группы, прямой вход j-ro триггера подключен к выходу j-ro элемента И первой группы, второй вход элемента И соединен с выходом генератора случайного потока импульсов и со счетным входом первого счетчика, выход элемента И соединен с разрешающим входом блока загрузки, с входом пуска генератора случайных чисел, со счетным входом второго счетчика и с суммирующим входом реверсивного счетчика, выходы разрядов которого соединены соответственно с входами узла индикации и генератора прямоугольных импульсов, выход которого соединен со счетным входом третьего счетчика, отличающее-, с я тем, что, с целью расширения функциональных возможностей за счет обеспечения загрузки сообщений в буферный накопитель, анализа признаков выбора выходных каналов и передачи сообщений соседнему узлу, в блок загрузки введен элемент задержки, а в устройство - генераторы тактовых импульсов, блок мультиплексоров, блок имитации буферного накопителя, шифратор и коммутатор, информационные входы которого являются информационными входами устройства,

управляющий вход коммутатора соединен с выходом элемента И, выходы коммутатора через В1Ифратор соединены с группой адресных входов блока имитации буферного накопителя, первая

fi вторая группы информационных входов которого соединены соответственно с группой выходов генератора случайных частот и с группой информа- 1ДЮННЫХ выходов блока мультиплексоров, группа разрешающих входов блока имитации буферного накопителя соединена с группой разрешающих выходов блока загрузки, группа инфо| ма- ционных входов которого соединен с

группой информационных выходов блока имитации буферного накопителя, группа адресных выходов которого соединена с группой информационных входов

блока- мультиплексоров,выходы э апус- кающих сигналов которого соединены соответственно- с входами пуска генераторов тактовых импульсов, выходы которых соединены соответственно с синхронизирующими входами блока мультиплексоров, выход признака блока имитаций буферного накопителя соединен с.вычитающим входом реверсивного счетчика и со счетным входом четвертого счетчика, разрешающий вход блока загрузки через элемент задержк соединен с вторыми входами первых элементов И первой и второй групп блока загрузки.

2, Устройство по .п.1, о т л и - чающееся тем, что блок имитации буферного накопителя содержит злемент ИЛИ, п информационных и адресных групп элементов И, п вычитающих счетчиков, п регистров адреса, установочный вход j-ro регистра адреса (1,п))и j-й вход элемента ИЛИ соединень с выходом j-ro вычитающего счетчика, выход элемента ИЖ является выходом признака блока имитации буферного накопителя, выходы

вычитающргх счетчиков являются группой информационных выходов блока имитации буферного накопителя, выходы регистров адреса являются группой адресных выходов блока имитации буферного накопителя, информационные регистров адреса нены соответственно с выходами элементов И адресных групп,, первые

входы которых соединены соответственно с группой адресных входов блока имитации буфернбго накопителя, первая группа информационных входов которого соединена с первыми

входами элементов И информационных групп, выходы элементов И j-й информационной группы соединены с информационным входом j-ro вычитающего счетчика, счетный вход каждого счетчика соединен с соответствующим входом второй группы информационных входов блока имитации буферного накопителя, j-й вход группы разрещающих входов блока имитации буферного накопителя соединен с вторымм входами элементов ИJ-X адресных и информационных групп.

(pifs.Z

4f ЛЛ t-

«; лв

49 Ь

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования узлов коммутации сообщений | 1986 |

|

SU1354203A1 |

| Устройство маршрутизации сети связи | 1987 |

|

SU1499370A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Адресно-коммутационное устройство | 1987 |

|

SU1515378A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

Изобретение относится к вычислительной технике. Целью изобретения является расширение функцио.иальных возможностей за счет обеспечения загрузки сообщений в буферный накопитель, анализа признаков, выбора выходных каналов и передачи сообщений соседнему узлу. Устройство содержит блок 1 обработки, включающий счетчики 2-5, реверсивный счетчик 6, узел 7 индикации, генератор 8 прямоугольных импульсов, генератор 9 случайного потока импульсов, генератор 10 случайных чисел, элемент И 11, блок 12 загрузки, коммутатор 13, шифратор 14, блок 15 имитации буферного накопителя, блок 16 коммутации, генераторы 17-19 тактовых импульсов. 3,п.ф-лы, 5 ил. i (Л с

3

#/

Редактор В.Иванова

Заказ 6841/49Тираж 671Подписное

ВШШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Произнодственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

J5

фие5

Составитель В.Мкртычан

Техред И.ВересКорректор Г.Решетник

| Устройство для анализа кода маршрута в цифровой сети связи | 1983 |

|

SU1166130A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования систем массового обслуживания | 1980 |

|

SU922756A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-05-13—Подача