(54) УСТРОЙСТВО ПРИЕМА СИГНАЛОВ ФАЗОВОГО

ПУСКА

| название | год | авторы | номер документа |

|---|---|---|---|

| АППАРАТУРА МЕТЕОРНОЙ СВЯЗИ | 2019 |

|

RU2710286C1 |

| Устройство приема сигналов фазового пуска | 1984 |

|

SU1192150A2 |

| Устройство приема сигналов фазового пуска | 1980 |

|

SU928666A2 |

| УСТРОЙСТВО ПРИЕМА АДРЕСНОГО ВЫЗОВА | 1994 |

|

RU2097941C1 |

| Устройство для сжатия информации | 1986 |

|

SU1336080A1 |

| Устройство для регистрации индикаторных диаграмм поршневых машин | 1988 |

|

SU1597634A1 |

| Устройство приема сигналов фазового пуска | 1978 |

|

SU720764A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

| Система телемеханики | 1983 |

|

SU1149296A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯХАРАКТЕРИСТИКИ ГРУППОВОГО ВРЕМЕНИЗАПАЗДЫВАНИЯ | 1972 |

|

SU428309A1 |

Изобретение относится к технике передачи дискретных сообщений, а именно к системам синхронизации, и может быть использовано преимущественно в каналах передачи дис-/ кретной информации с переменными параметрами, а также в системах передачи, где связь осуществляется короткими сеансг1ми.

Известно устройство приема сигналов фазового пуска, содержащее бистабильный элемент и п каналов обработки сигналов, каждый из которых состоит из .последовательно соединенных формирователя импульсов фронтов и селектора, а также (п+1) ключей, причем сигнальные входы п ключей объединены с входами соответствующих формирователей импульсов фронтов, а к управляющим входам п ключей подсоединены п выходов блока управления, к п входам которрго подключены выходы селекторов, а выходы п К11ючей соединены с входами первого элемента ИЛИ, выход которого подклю- , чей к первому входу блока совпадения и через последовательно соединенные анализатор конца принимаемого сообщения и формирователь сигнала Сброс к первому входу (п+1)

ключа и (п+1) входу блока управления, (п+1) выход которого подключен к управляющему входу 1п+1) ключа , к второму входу которого подключен выход задающего генератора, а выход (п+1) ключа соединен с входом делителя частоты 1.

Однако известное устройство обладает большим временем обработки

10 сигнала при приеме дискретной информации.

Цель изобретения - сокращение времени обработки сигнала при приеме дискретной информации.

15

Поставленная цель достигается тем, что в устройство приема сигналов фазового пуска, содержащее бистабильный элемент и п каналов обра20ботки сигналов, каждый из которых состоит из последовательно соединенных формирователя импульсов фронтов и селектора, а также (п+1) ключей, причем сигнальные входы п клю25чей оСъединены с входами соответствующих формирователей импульсов фронтов, а к управляющим входам п ключей подсоединены п выходов блока управления, к п входам которого

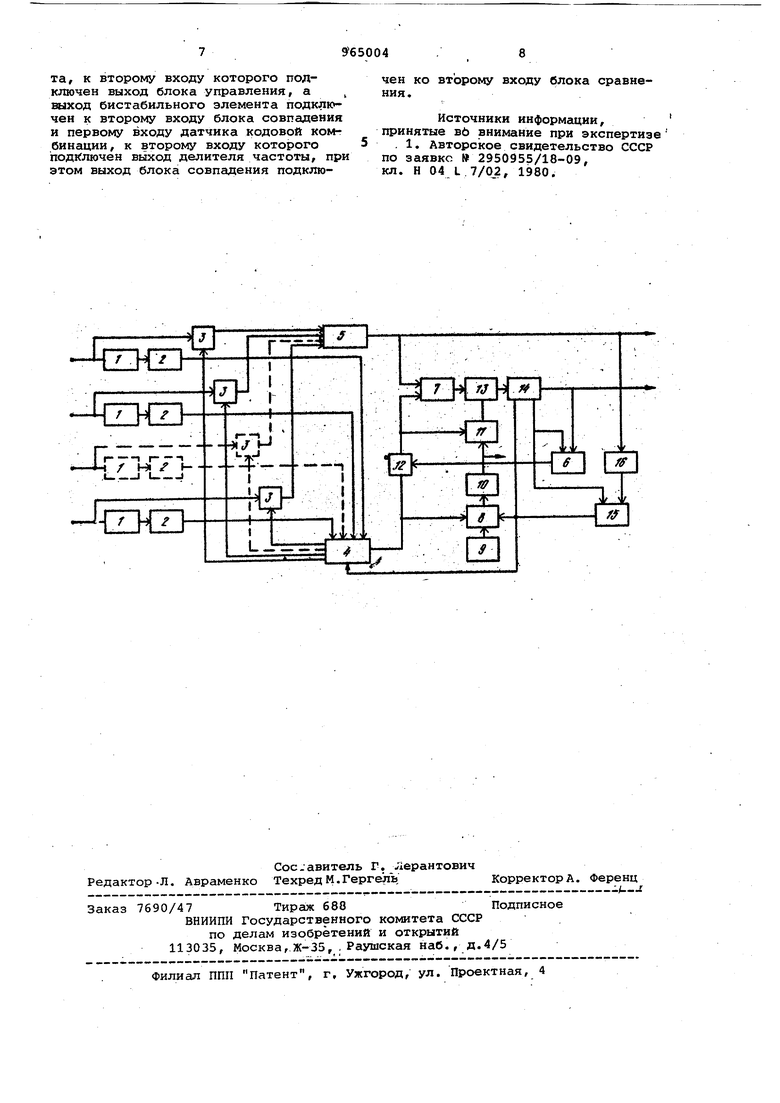

30 подключены выходы селекторов, а выходы n ключей соединены с ExoAaf m первого элемента ИЛИ, выход которого подключен к первому входу блока совпадения и через последовательно соединенные анализатор конца принимаемого сообщения и формирователь сигнала Сброс к первому входу (п+ ключа и (п+1) входу блока управления, (п+1) выход которого подключен управляющему входу (п+1) ключе, к второму входу которого подключен вы ход задающего генератора, а выход (п+1) ключа соединен с входом делит ля частоты, введены последовательно соединенные датчик кодовой комбинации, блок сравнения, интегратор и второй элемент ИЛИ, к второму вхо ду которого, а также к второму входу формирователя сигнала Сброс подключен второй выход интегратора, к второму входу которого подключен выход формирователя сигнала Сброс а выход второго элемента ИЛИ подклю чен к первому входу бистабильного элемента, к второму входу которого под ключен ВЫХОДблока управления, а вы ход бистабильного элемента подключе к второму входу блока совпадения и первому входу датчика кодовой комбинации, к второму входу которого подключен выход делителя частоты, п этом выход блока совпадения подключ к второму входу .блока сравнения. На чертеже представлена структур ная схема устройства. Устройство приема сигналов фазового пуска содержит n каналов обработки сигналов, каждый из которых состоит из. формирователя 1 импульеов фронтов, селектора 2, ключа 3, блок 4 управления, элементы ИЛИ 5 и блок 7 совпадения, п + 1 ключ 8, задающий генератор 9, делитель 10 час тоты, датчик 11 кодовой комбинаг ри, бистабильный элемент 12, блок 13 сравнения, интегратор 14, формирова тель 15 сигнала Сброс, анализатор 16 конца принимаемого сообщения Устройство работает следующим образом. С выходов анализируемых каналов сигналы в виде импульсной последовательности, содержащей синхрониз рующие импульсы для установления синхронизации по посылкам и импульсы специальной пусковой комбинации, одновременно поступают на входы n каналов обработки сигналов, каждый из которых состоит из последователь но соединенных формирователя 1 импульсов фронтов и селектора 2, причем сигнальные входы ключей 3 соответствующих каналов объединены с входами формирователей импульсов фронтов. В том случае, ,когда фронты сигнала следуют друг за другом через f , равное длительности элементарной посылки сигнала с погрешностью ±(Г, на выходе формирователя 1 импульсов фронтов появляется импульс. Если погрешность превысит величину, ff , то импульс-на его выходе не Появится. Выработанный импульс поступает на вход г-електора 2, который осуществляет счет числа поступающих на его вход импульсов на заданном временном интервале. Величину интервала счета и количество импульсов в пачке выбирают исходя из продолжительности синхроинтервала принимаемого сигнала и количества синхроимпульсов. На выходе селектора 2 импульс появляется в момент поступления на его вход последнего импульса пачки. Если количество импульсов на интервале счета оказывается меньше зачетного, селектор 2 осуществляет сброс набранного количества импульсов. Очередной счет импульсов начинается с момента поступления первого импульса после сброса. При наличии сигнала в одном из каналов на выходе селектора 2 соответствующего канала обработки появляется импульс, который поступает на бход блока 4 управления. Блок 4 ут/равления открывает ключ 3 этого же канала, разрешая прохождение сигнала через первый элемент ИЛИ 5 на вход блока 7 совпадения, при этом блок 4 управления блокируется, предотвращая тем самым одновременное включение ключей остальных каналов. Кроме того, с отдельного выхода блока 4 управления науправляющий вход (п+1) ключа 8 поступает сигнал, разрешающий прохождение импульсов от задаищего генератора 9 на вход делителя 10 частоты. На выходе делителя 10 частоты появляется периодическая последовательность импульсов, фронтй которых , совпадают с фронтами посылок принимаемого сигнала с точностью сГ. С выхода делителя 10 частоты импульсная последовательность (напряжение тактовой синхронизации; поступает на вход датчика 11 кодовой комбинации. Сигнал с отдельного выхода блока 4 управления поступает также на вход бистабильного элемента 12, под действием которрго последний переводится в одно из двух устойчивых состояний, характеризуемое вьщачей разрешающего сигнала на второй вход блока 7 совпадения, последний открывается, и принимаемый сигнал поступает на вход блока 13 сравнения. Одновременно напряжение с выхода бистабильного элемента 12 запускает датчик 11 кодовой комбинации, с выхода которого на второй вход блока 13 сравления под действием тактовой частоты начинает поступать кодовая комбинац устройства. Блок 13 сравнения осуществляет поимпульсное сравнение пусковой ком бинации сигнала с кодовой комбинацией устройства. Совпадение каждой пары импульсов фиксируется в интегр торе 14, постоянная времени которог выбирается равной длительности пусковой комбинации. Если результат сравнения пары импул сов отрицательный (т.е. пусковая комб ция не совпадает с кодовой комбинацией устройства., то со второго вых да интегратора 14 через второй элемент ИЛИ б на бистабильный элемент 12 подается импульсный сигнал, под дейст.вием которого последний перехо дит в другое устойчивое состояние, которое характеризуется подачей сиг ла запрета на блок 7 совпадения и датчик 11 кодовой комбинации. Со вт рого -выхода интегратора 14 импульсный сигнал поступает также на форми рователь 15 сигнала Сброс, который формирует сбросовый импульс, обеспечивающий перевод п+1 ключа 8, блока 4 управления и интегратора 14 в исходное положение. Анализ данного каналс;, прекращается, п устройство переходит в исходное состояние. Если результаты предварительного сравнения положительны, т.е. пус ковая комбинация сигнала начинает совпадать с кодовой комбинацией устройства, то с второго выхода интегратора 14 через второй элемент ИЛИ 6 на бистабильный элемент 12 импульсный сигнал не подается, и он остается в том устойчивом состоянии которое характеризуется подачей раз решающего сигнала на блок 7 совпадения и датчик 11 кодовой комбинации. Анализ данного канала продолжается. По истечении времени, необходимо го для полного интегрирования пусковой комбинации, на первом выходе интегратора появляется импульс, соо ветствующий началу приема информационной части сообщения, который поступает далее во внешнее устройство, осуществляющее регистрацию принимаемых сообщений. Одновременно этот же сигнал через второй . элемент ИЛИ б поступает на бистабильный элемент 12 и переводит его в состояние, характеризуемое выдачей запрещающего сигнала на блок 7 совпадения и датчик 11 кодовой ком.бинации. Сравнение прекращается, но продолжается выработка напряжения тактовой синхронизации, которое используется для работы внешнего устрой ства, осуществляющего прием сообщений . С выхода первого элемента ИЛИ 5 сигнал поступает также на внешнее устройство и анализатор 16 конца принимаемого сообщения, который после окончания сеанса связи выраба-: тывает сигнал, поступающий на вход формирователя 15 сигнала Сброс. Анализ данного канала прекр.ащается, и устройство переходит в исходное состояние.. Таким образом, в предлагаемом устройстве анализ пусковой комбинации прекращается при обнаружении в ней первой ошибки.. Использование предлагаег-юго устройства в системе, где осуществляв ется прием коротких сообщений от разных корреспондентов и регистрация их одним внешним устройством, увеличивает пропускную способность системы в целом. Формула изобретения Устройство приема сигналов фазового пуска, содержащее бистабильный длемент и и каналов обработки сигналов, каждый из которых состоит из последовательно соединенных формирователя импульсов фронтов и селектора, а также (м+1) ключей, причем сигнальные входы и ключей объединены с входами соответствующих формирователей импульсов фронтов, а к управляющим входам v ключей подсоединены и выходов блока управления, к и входам которого подключены выходы селекторов, а выходы и :ключей : соединены с входами первого элемента ИЛИ, выход которого подключен к первому входу блока совпадения и через последовательно соединенные анализатор конца принимаемого сообщения и формирователь сигнала Сброс к первому входу (м+1) ключа и (и+1) входу блока управления, (п + 1)-выход которого подключен к управляющему входу (И+1) ключа, ко второму входу которого подключен выход задающего генератора, а выход (И+1) ключа соединен с входом делителя частоты, отлич ающе е ся тем, что, с целью сокращения времени обработки сигнала при приеме дискретной информации, введены последовательно соединенные датчик кодовой комбинации, блок сравнения, интегратор и второй элемент ИЛИ, ко второму входу которого , а также к второму входу формирователя сигнала Сброс подключен второй выход интегратора, ко второму входу, которого подключен выход формирователя сигнала Сброс, а выход второго элемента ИЛИ подключен-к первому входу бистабильного элемента, к второму входу которого подключен выход блока управления, а выход бистабильного элемента подключен к второму входу блока совпадения и первому входу датчика кодовой комбинации , к второму входу которого подключен выход делителя частоты, при этом выход блока совпадения подключен ко второму входу блока сравнения.

Источники информации, принятые вб внимание при экспертизе

Авторы

Даты

1982-10-07—Публикация

1981-03-02—Подача