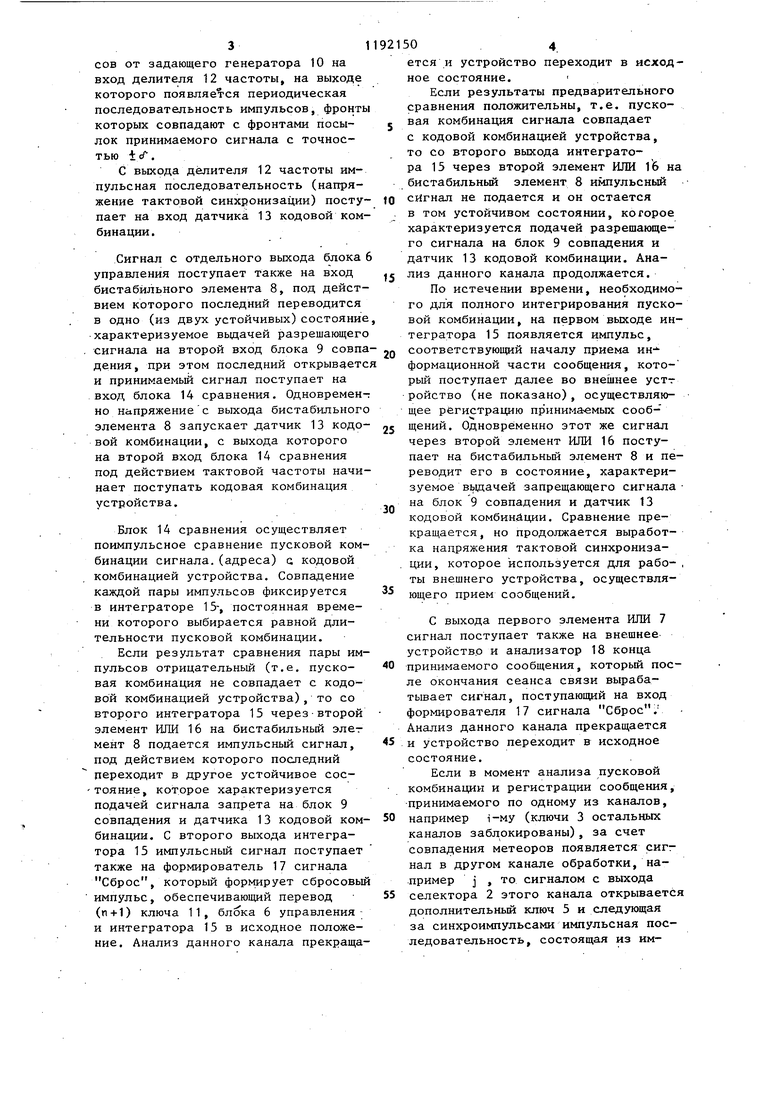

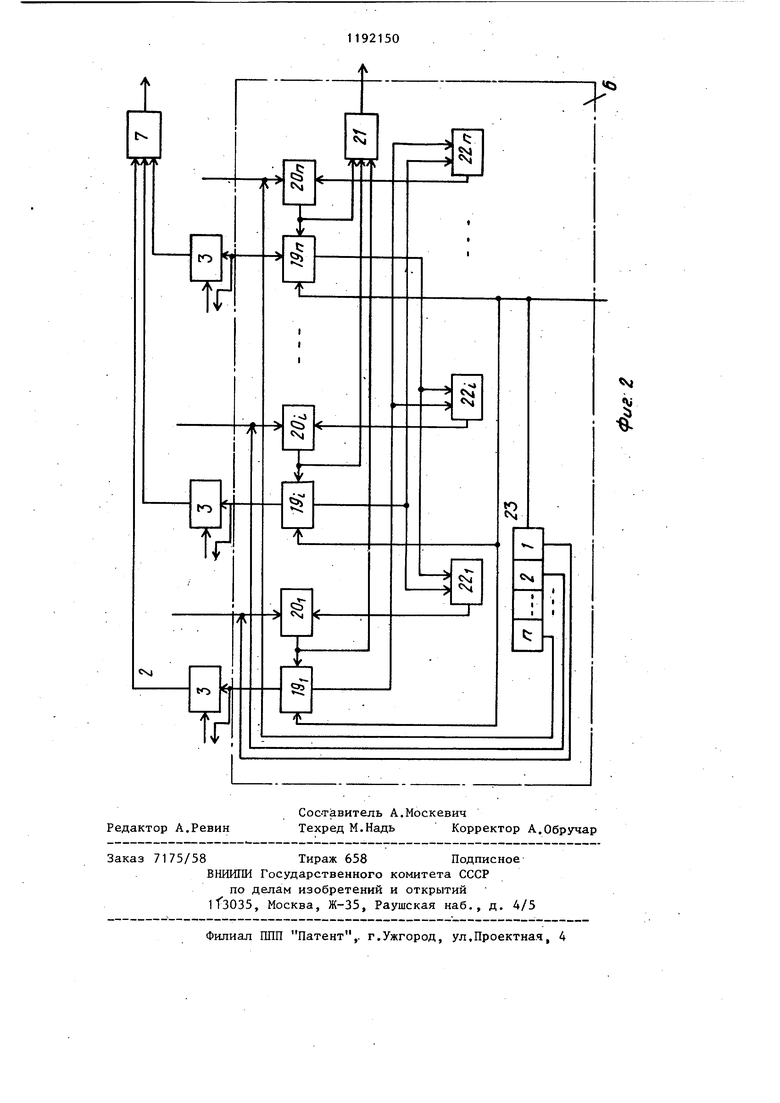

Изобретение относится к технике передачи дискретных сообщений, а именно к системам синхронизации, и можег быть использовано преимущественно в каналах передачи дискретной информации с переменньми параметрами, а также в системах передачи где связь осуществляется короткими сеан - сами. Цель изобретения - сокращение по терь информации. На фиг. 1 изображена структурная электрическая схема предлагаемого устройства-, на фиг. 2 - вариант выполнения блока управления. Устройство приема сигналов фазов го пуска содержит (фиг. 1) п канало обработки сигналов, каждый из которых состоит из формирователя .1 импульсов фронтов, селектора 2, клю-ча 3, блока 4 буферной памяти и дополнительного ключа 5, блок 6 управ ления, первый элемент ИЛИ 7, бистабильный элемент 8, блок 9 совпадения, задающий генератор 10, (п+1) ключ 11, делитель 12 частоты, датчик 13 кодовой комбинации, блок 14 сравнения, интегратор 15, второй элемент ИЛИ 16, формирователь .17 сигнала Сброс, анализатор 18 конц принимаемого сообщения. Блок управления (фиг. 2) выполне в виде п бистабильных элементов 19 19f,, п ключей 20, - .20п,. первого элемента ШШ 21, вторых элементов ИЛИ 22„, регистра 23 сдви га. Устройство работает следующим образом. С вькодов анализируемых каналов сигналы в виде имнульсной последова тельности, состоящей из синхронизирующих импульсов для установления синхронизма по посыпкам, импульсов .специальной пусковой комбинации (адрес) и информационных импульсов одновременно поступают на входы п каналов обработкисигналов, каЗДьй из которых состоит из последователь но соединенных формиров.ателя 1 импульсов фронтов и селектора 2, ключа 3, а также дополнительного ключа 5 и блока 4 буферной памяти, при .чем сигнальные входы дополнительных ключей 5 соответствующих каналов объединены с входами формирова. 1 импульсов фронтов. В том случае, когда фронты синхроимпульсов следуют друг за другом через интервал времени , равный длительности элементарной посьшки с погрешностью . ± cf , формирователь 1 импульсов фронтов вырабатывает импульс. Если погрешность превышает ± d , то импульс на его выходе не появляется. Выработанньй импульс поступает на вход селектора 2, который осуществляет счет числа поступающих на его вход синхроимпульсов, на заданном временном интервале. Величина интервала счета и количество импульсов в пачке выбирается исходя из продолжительности синхроинтервала принимаемого сигнала и количест,ва синхроимпульсов. На выходе селектора 2 импульс появляется в момент поступления на его вход последнего импульса пачки. Если количество импульсов на интервале счета оказывается меньше зачетного, то селектор 2 осуществляет сброс набранного количества импульсов. Очередной счет импульсов начинается с момента поступления первого импульса после сброса. При наличии сигнала в одном из каналов на выходе селектора 2 этого канала вырабатывается импульс, который поступает на управляющий вход дополнительного ключа 5 нормально закрытого, открывает его и разрешает тем самым прохождение информации для записи.в блок 4 буферной памяти. Одновременно импульс с выхода селектора 2 поступает на соответствующий в,ход блока 6 управления. Блок 6 управления вырабатьшает сигнал, которьй подается на управляющий вход ключа 3 и на управляющий вход блока 4 буферной памяти этого же канала.. , Ключ 3 открывается и разрешает считывание информации, записанной в блок 4 буферной памяти, на вход первого элемента ИЛИ 7. При этом блок 6 управления блокирует ключи 3 в других каналах, предотвращая тем самым одновременное считывание информации, записанной с блоков 4 буферной памяти других каналов. Кроме того, с отдельного выхода блока 6 управления на управляющий вход (п+1) ключа 11 поступает сигнал j разрешающий прохождение импуль3сов от задающего генератора 10 на вход делителя 12 частоты, на выходе которого появляется периодическая последовательность импульсов, фронт которых совпадают с фронтами посылок принимаемого сигнала с точностью i сЛ. С выхода делителя 12 частоты импульсная последовательность (напряжение тактовой синхронизации) посту пает на вход датчика 13 кодовой ком бинации . Сигнал с отдельного выхода блока управления поступает также на вход бистабйльного элемента 8, под дейст вием которого последний переводится в одно (из ДВ5 устойчивых)состояни характеризуемое выдачей разрешающег сигнала на второй вход блока 9 совп дения , при этом последний открывает и принимаемьй сигнал поступает на вход блока 14 сравнения, Одновремен но напряжение с выхода бистабйльног элемента 8 запускает датчик 13 кодо вой комбинации, с выхода которого на второй вход блока 14 сравнения под действием тактовой частоты начи нает поступать кодовая комбинация устройства. Блок 14 сравнения осуществляет поимпульсное сравнение пусковой комбинации сигнала, (адреса) с, кодовой комбинацией устройства. Совпадение каждой пары импульсов фиксируется в интеграторе 15-, постоянная времени которого выбирается равной длительности пусковой комбинации. Если результат сравнения пары импульсов отрицательный (т,е, пусковая комбинация не совпадает с кодо вой комбинацией устройства), то со второго интегратора 15 черезвторой элемент ИЛИ 16 на бистабильный элет мент 8 подается импульсный сигнал, под действием которого последний переходит в другое устойчивое состояние, которое характеризуется подачей сигнала запрета на блок 9 совпадения и датчика 13 кодовой комбинации, С второго выхода интегратора 15 импульсный сигнал поступает также на формирователь 17 сигнала Сброс, который формирует сбросовый импульс, обеспечивающий перевод (п+1) ключа 11, блока 6 управления и интегратора 15 в исходное положение. Анализ данного канала прекраща04ется и устройство переходит в исходное состояние, Если результаты предварительного сравнения положительны, т.е, пусковая комбинация сигнала совпадает с кодовой комбинацией устройства, то со второго выхода интегратора 15 через второй элемент ИЛИ 16 на бистабильньй элемент 8 импульсный сигнал не подается и он остается в том устойчивом состоянии, которое характеризуется подачей разрешающего сигнала на блок 9 совпадения и датчик 13 кодовой комбинации. АнаЛИЗ данного канала продолжается. По истечении времени, необходимого для полного интегрирования пусковой комбинации, на первом выходе интегратора 15 появляется импульс, соответствующий началу приема информационной части сообщения, который поступает далее во внешнее устт ройство (не показано), осуществляющее регистрацию принимаемых сообщений. Одновременно этот же сигнал через второй элемент ИЛИ 16 поступает на бистабильный элемент 8 и переводит его в состояние, характеризуемое вьодачей запрещающего сигнала на блок 9 совпадения и датчик 13 кодовой комбинации. Сравнение прекращается , но продолжается выработка напряжения тактовой синхронизации, которое используется для рабо- , ты внешнего устройства, осуществляющего прием сообщений. С выхода первого элемента ИЛИ 7 сигнал поступает также на внешнее устройство и анализатор 18 конца принимаемого сообщения, который после окончания сеанса связи вырабатьшает сигнал, поступающий на вход формирователя 17 сигнала Сброс. Анализ данного канала прекращается и устройство переходит в исходное состояние. Если в момент анализа пусковой комбинации и регистрации сообщения, принимаемого по одному из каналов, например i-му (ключи 3 остальных каналов заблокированы), за счет совпадения метеоров появляется сигг нал в другом канале обработки, например j , то сигналом с выхода селектора 2 этого канала открывается дополнительный ключ 5 и следующая за синхроимпульсами импульсная последовательность, состоящая из импульсов пусковой комбинации и инфо мационных импульсов, поступает в соответствующий блок 4 буферной па мяти. Считывание, информации с блоков 4 буферной памяти и ее дальне шая обработка осуществляется по сигналам блока 6 управления последовательно по мере обработки сигна .лов фазового пуска и информации в . соответствующих блоках. При приеме сигналов по i-му каналу на выходе селектора 2 этого канала вьфабатывается импульс, который поступает на i-и вход блока управления. Непосредственно в блоке 6 управления этот импульс посту-пает йа i-й ключ 2.0 i (фиг. 2), который переводит t-й, бистабильньй элемент 19- в положение, при котором на его выходе появляется импульс, открывающий соответствующий ключ 3 и,разрешающий считывание информации с 1-го блока 4 буферной памяти (фиг. 1). Одновременно импул с выхода 1-го бистабильного элемента 19. поступает на (п-1) вто-рых элементов ИЛИ 22 - 22 ,,., , на выходе которых появляются импульсы блокирующие соответствующие ключи 20 - 20f| в других (кроме i-ro) (п-1) каналах приема. Тем самым предотвращается поступление сигнало от (п-1) селекторов 2 на входы других (п-1) бистабильньк элементов 19 - 19. Кроме того, импульс вьфаботанный -ым ключем 20 поступает через первый элемент ИЛИ 21 на бистабильный элемент 8 и (п-1) ключ 11 (фиг. 1) для управления работой соответствующих блоков по определенному алгоритму. Таким образом, соответствующий ключ 3 открывается и разрешает считывание информации, записанной в блок 4 буферной памяти i-ro канала, на вход первого элемента ИЖ 7. При этом блок 6 управления блокирует другие ключи 3 в других (h-1) . каналах приема, предотвращая тем самым одновременное считывание информации, записанной в блоках 4 буферной памяти других (п-1) каналов. После окончания приема информации в i-oM, канале формирователь 17 сигнала Сброс обеспечивает перевод блока 6 управления в исходное состояние. При этом п бистабильных элементов 19 - 19 , п ключей 20 20 блока 6 управления и п ключей 3 устройства переводятся этим сигналом в исходное положение. Одновременно сигнал Сброс, поступающий с формирователя 17, подается на регистр 23 сдвига, в котором сигнал в виде 1 с тактовой частотой продвигается по п ячейкам (с первой по п-ую). Выходы п ячеек регистра 2 сдвига соединены с входами п ключей 20 - 20р. При наличии информации в одном из п блоков 4 буферной памяти, например J-OM, сигнал с j-ro выхода регистра 23 сдвига открывает j-й ключ 20.-, которьй переключает j-и бистабильный элемент 19,. По сигналу с j-ro бистабильного элемента 19; j-й ключ 3 открывается и начинается считьшание информации с j-го блока 4 буферной памяти. Далее .работа блока 6 управления происходит по алгоритму, аналогичному приему по -му каналу и т.д. Таким образом, блок 6 управления обеспечивает управление последовательной во времени обработкой информации, записанной в блоки 4 буферной памяти.

и

| название | год | авторы | номер документа |

|---|---|---|---|

| АППАРАТУРА МЕТЕОРНОЙ СВЯЗИ | 2019 |

|

RU2710286C1 |

| Устройство приема сигналов фазового пуска | 1981 |

|

SU965004A1 |

| Устройство приема сигналов фазового пуска | 1980 |

|

SU928666A2 |

| Устройство для сжатия информации | 1986 |

|

SU1336080A1 |

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1989 |

|

SU1755377A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| УСТРОЙСТВО ПРИЕМА АДРЕСНОГО ВЫЗОВА | 1994 |

|

RU2097941C1 |

УСТРОЙСТВО ПРИЕМА СИГНАЛОВ ФАЗОВОГО ПУСКА по .авт.св. № 965004, отлич а ющ ё е с я тем, что. с целью сокращения потерь информации, в каждом канале обработки сигналов вход формирователя импульсов фронтов соединен с сигнальным входом ключа через последовательно, соединенные Бвej eнныe дополнительный ключ, к управляющему входу .которого подключен выход селектора, и блок буферной памяти, управлякмций вход которого соединен с соответствующим выходом блока управления. (Л

| Авторское свидетельство СССР, 965004, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-11-15—Публикация

1984-03-11—Подача