Изобретение относится к автоматике и вычислительной технике и может найти применение, например, в качестве буферного устройства между двумя разноскоростными устройствами передачи информации.

По основному авт.св. № 913359 известно устройство для сопряжения, содержащее узел синхронизации и узел памяти, включающий группу последовательно соединенных регистров, . включающих триггера информсщионных разрядов и триггер служебного разряда, элементы И и И-НЕ по числу регистров, причем информационный вход узла памяти соединен с входом триггеров информационных разрядов первого регистра, а выходы триггеровинформационных разрядов последнего регистра являются информационным выходом узла памяти, вход триггера служебного разряда перво.го регистра является призначным входом узла памяти , а выход триггера служебного разряда последнего регистра является призначным входом памяти входы элементов И соединены с входом тактовых импульсов узла памяти и с першзш входом узла синхронизации и входом тактрвых импульсов устройства, периле входы элементов И-НЕ -подключе.ны к синхронизирующему входу узла памяти и первому выходу узла синхронизации, второй вход которого является входом чтения информации устройства, выход i-ro элемента И соединен с управляющим входом i-To регистра, а второй вход - с выходом i-ro элемента И-НЕ,

10 второй вход которого подключен к выходу триггера служебного разряда i-ro регистра, а третий вход - к выходу триггера служебного разряда (i+l)-ro егистра 1115

Иедостатком этого устройства является низкое быстродействие, так как информационные коды могут поступать на вход устройства только через такт.,

20

- Цель изобретения - повышение быстродействия устройства.

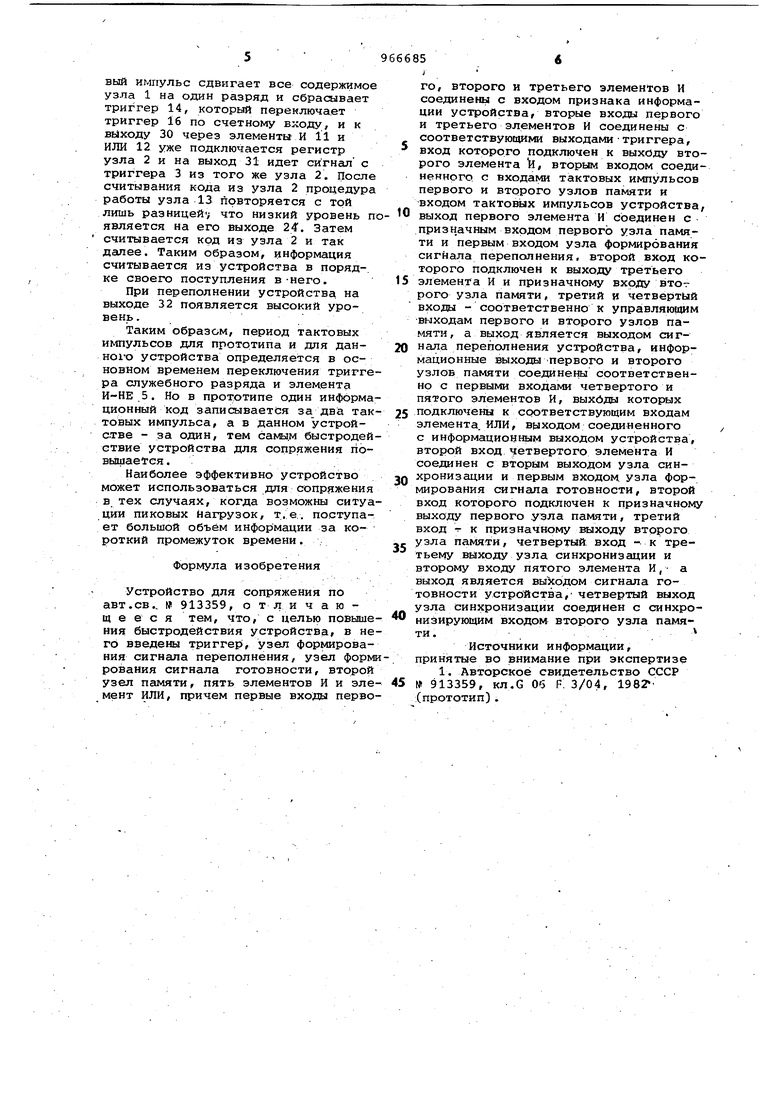

Поставленная цель достигается тем, что в устройство введены триггер, узел формирования сигнала переполне25ния, узел формирования сигнала готовности, второй узел памяти, пять элементов И и элемент ИЛИ, причем первые входы первого, второго и третьего элементов И соединены с вхо30дом признака информации устройства вторые входы первого и третьего элементов И соединены с соответствующим выходамитриггера, входкоторого под ключен к выходу второго элемента И, вторым входом соединенного с входами тактовых импульсов первого и второго узлов памяти и входом тактовых импульсов устройства, выход первого элемента И соединен с призначным вхо дом первого узла памяти и первым вхо дом узла формирования сигнала переполнения, второй вход которого подключен к выходу третьего элемента И и призначному входу второго узла памяти, третий и четвертый входы - соответственно к управляющим выходам первого и вюрого узлов памяти, а выход является выходом сигнала переполнения устройства, информационны выходы первого и второго узлов памяти соединены соответственно с пер.выми входами четвертого и -пятого эле ментов И, выходы которых подключены К соответствующим входам элемента ИЛИ, выходом соединенного с информационным выходом устройства, второй вход четвертого элемента И соединен с вторым выходом узла синхронизации и первым входом узла формирования сигнала готовности, второй вход которого подключен к призначному выходу первого узла памяти, третий вход к призначному выходу второго узла па мяти , четвертый вход - к третьему выходу узла синхронизации и второму входу пятого элемента И, а выход является выходом сигнала готовности устройства, четвертый выход узла синхронизации соединен с синхронизирующим входом второго узла памяти. На чертеже представлена блок-схема устройства, Схема содержит узлй 1 и 2 памяти, состоящие из ре1истррв с триггером 3 служебного разряда и триггерами 4 ин формационных разрядов, элементами Й-НЕ 5 и элементами И 6, элементы И 7-11, элемент ИЛИ 12, узел 13 синхронизации, состоящий из синхронного триггера 14, элементов И-НЕ 15 и аси хронных триггеров W и 17, узел 18 формирования сигнала готовности и узел 19 формирования сигнала перепол нения, состоящие из элементов ИЛИ 20 и элементов И 21, триггер 22, пер вый 23, четвертый 24, третий 25 и ззторой 26 выходы узла 13 синхронизации, вход 27 признака информации устройства, информационный вход 28 устройства, вход-29 чтения информации, информационный выход 30 устройства, выход 31 сигнала готовности устройства, выход 32 сигнала перепол нения устройства, вход 33 тактовых импульсов устройства. Устройство работает следующим образом. При включении устройства обнуляются все триггеры 3, триггеры 14 и 17, а триггеры 16 и 22 устанавливаются в одинаковое состояние (допустим единичное). На выходах всех элементов И-НЕ 5 высокий уровень, который разрешает прохождение тактовых импульсов через элементь И 6. Информационный код, поступающий в устройство, сопровождается 1 на входе 27 признака информации, которая записывается в зависимости от состояния триггера 22 в триггер 3 первого регистра узлов 1 или 2 тактовым импульсом, который, кроме того, перебрасывает и триггер 22 в противоположное состояние. Поэтому при поступлении следующего информационного кода запись 1 с входа 27 происходит в другой узел памяти. Таким образом, нечетные информационные коды сов местно с признаком записываются в узел 1, а четные информационные коды - в узел 2. Тактовые импульсы непрерывно подаются в устройство и первый занесенный код, сопровождаемый 1 в служебном разряде, последовательно через все реатистры продвигается в последний регистр, после чего-, на выходе последнего элемента И-НЕ 5 появится низкийуровень и запись новой информации в последний регистр не происходит, поскольку тактовые импульсы не проходят на синхровходы триггеров последнего регистра. Аналогичное запрещение записи в последний регистр узла 2 происходит, когда в нем окажется второй занесенный код, сопровождаемый 1 в триггере 3. Третий занесенный код, достигнув предпоследнего регистра узла 1, своим служебным разрядом запрещает запи.сь в него. Подобным образом идет заполнение всех регистров обоих узлов памяти. Триггер 16 подключает.информационный регистр 2 узла 1 к выходу 30 через элемент И 10 и элемент ИЛИ 12, а через элементы 21 .и 20 узла 18 разрешает прохождение высокого уровня с выхода триггера на выход 31 готовности устройства, что свидетельствует о наличии информации для считывания . После считывания информации, которое может происходить в любой момент времени, сигнал на входе 29 чтения информации устанавливает триггер 17 в единичное состояние. Первый пришедший после этого.тактовый импульс взводит триггер 14 в единичное состояние, что приводит к сбросу триггера 17 по второму тактовому импульсу и к появлению низкого уровня на выходе 23. Поскольку на выходе элементов И-НЕ 5 узла 1 высокий уровень, то следующий тактовьой импульс сдвигает все содержимое узла 1 на один разряд и сбрасывает триггер 14, который переключает триггер 16 по счетному входу, и к выходу 30 через элементы И 11 и ИЛИ 12 уже подключается регистр узла 2 и на выход 31 идет сигнал с триггера 3 из того же узла 2. После считывания кода из узла 2 процедура работы узла 13 повторяется с той лишь разницей; что низкий уровень пявляется на его выходе 24. Затем считывается код из узла 2 и так далее. Таким образом, информация считывается из устройства в поряд-. ке своего поступления в-него.

При переполнении устройства на выходе 32 появляется высокий уровень.

Таким образом, период тактовых импульсов для прототипа и для данHOio устройства определяется в основном временем переключения триггера служебного разряда и элемента И-НЕ 5. Но в прототипе один информационный код записывается за два тактовых импульса, а в данном устройстве - за один, тем самым быстродействие устройства для соцряжения повышаемся.

Наиболее эффективно устройство может использоваться для сопряжения в тех случаях, когда возможны ситуации пиковых Нагрузок, т.е.. поступает большой объём информации за короткий промежуток времени. .

Формула изобретения

Устройство для сопряжения по авт.св.. № 913359, о тли чающееся тем, что, с целью повышения быстродействия устройства в него введены триггер, узел формирования сигнала переполнения/ узел формрования сигнала готовности, второй узел памяти, пять элементов И и элемент ИЛИ, причем первые входы первого, второго и третьего элементов И соединены с входом признака информации устройства, вторые входы первого и третьего элементов И соединены с соответствующими выходамитриггера,

вход которого подключен к выходу второго элемента К, вторым входом соединенного с входами тактовых импульсов первого и второго узлов памяти и входом тактовых импульсов устройства,

О выход первого элемента И соединен с призначным вхрдом первого узла памяти и первым входом узла формирования сигнала переполнения, второй вход которого подключен к выходу третьего

5 элемента И и призначному входу второго узла памяти, третий и четвертый входы - соответственно к управляющим выходам первого и второго узлов памяти, а выход является выходом сигнала переполнения устройства, информационные выходы Первого и второго узлов памяти соединены соответственно с первыми входами четвертого и пятого элементов И, выхйды которых

5 подключены к соответствующим входам элемента. ИЛИ, выходом соединенного с информационным выходом устройства, второй вход четвертого элемента И соединен с вторым выходом узла синQ хронизации и первым входом, узла формирования сигнала готовности, второй вход которого подключен к призначному выходу первого узла памяти, третий вход -г к призначному выходу второго узла памяти, четвертый вход - к тре5

тьему выходу узла синхронизации и второму входу пятого элемента И, а выход является выходом сигнала готовности устройства, четвертый выход узла синхронизации соединен с синхро0низирующим входом второго узла памяти. , . .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 913359, кл.С 06 Р. 3/04, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1977 |

|

SU739516A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

| Устройство для управления вводом изображения | 1989 |

|

SU1751738A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

Авторы

Даты

1982-10-15—Публикация

1979-01-09—Подача