Изобретение относится к вычислительной технике и может быть использовано при р азработке микроЭВМ и других средств вычислительной техники на основе однокристальных микропроцессоров.

Целью изобретения является сокращение объема блока памяти, необходи-. мого для запоминания информации о вьшолнении программы. .

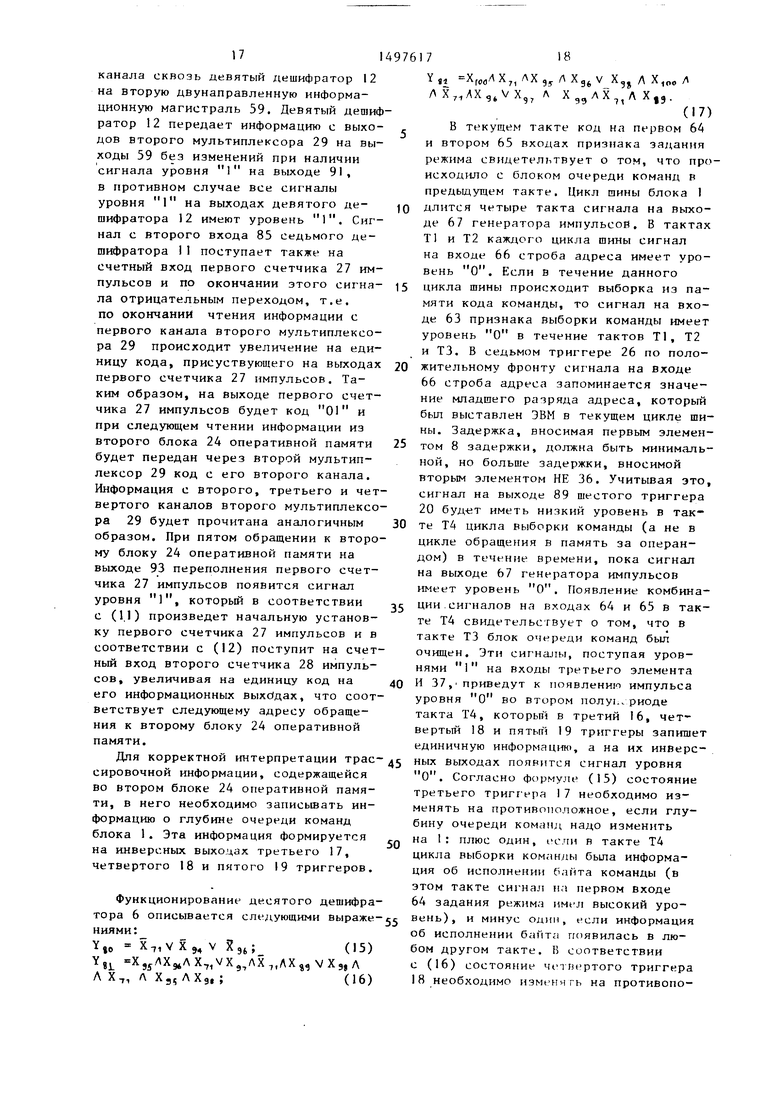

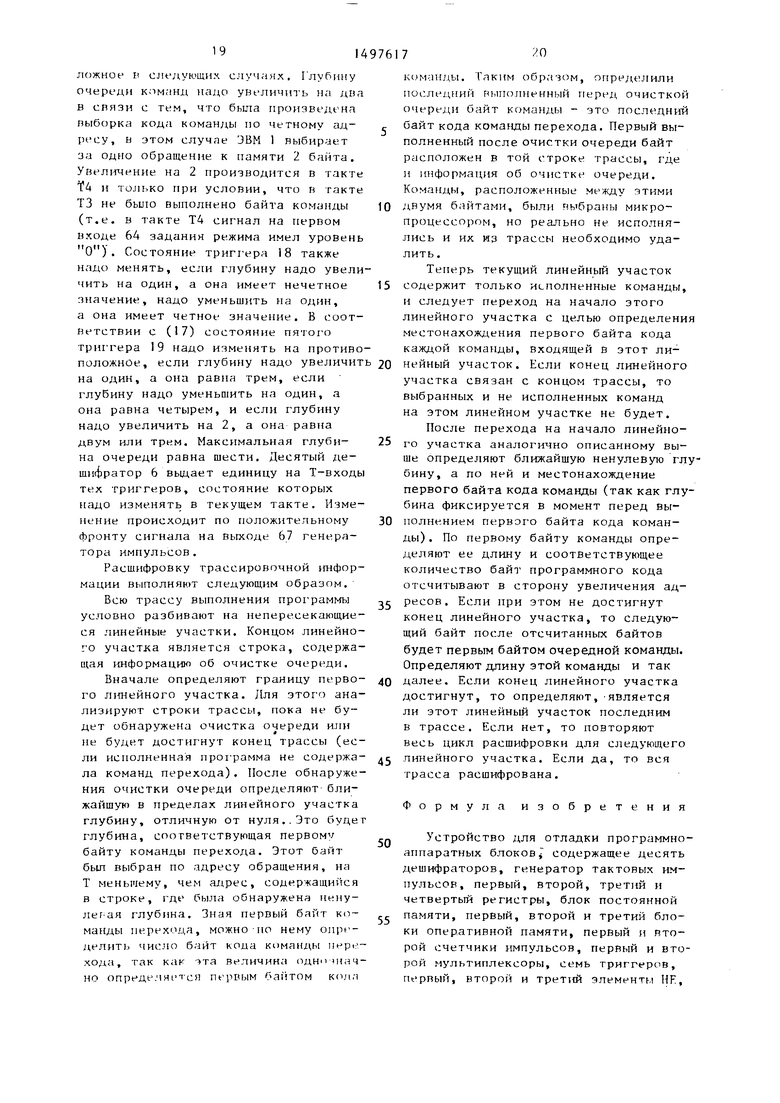

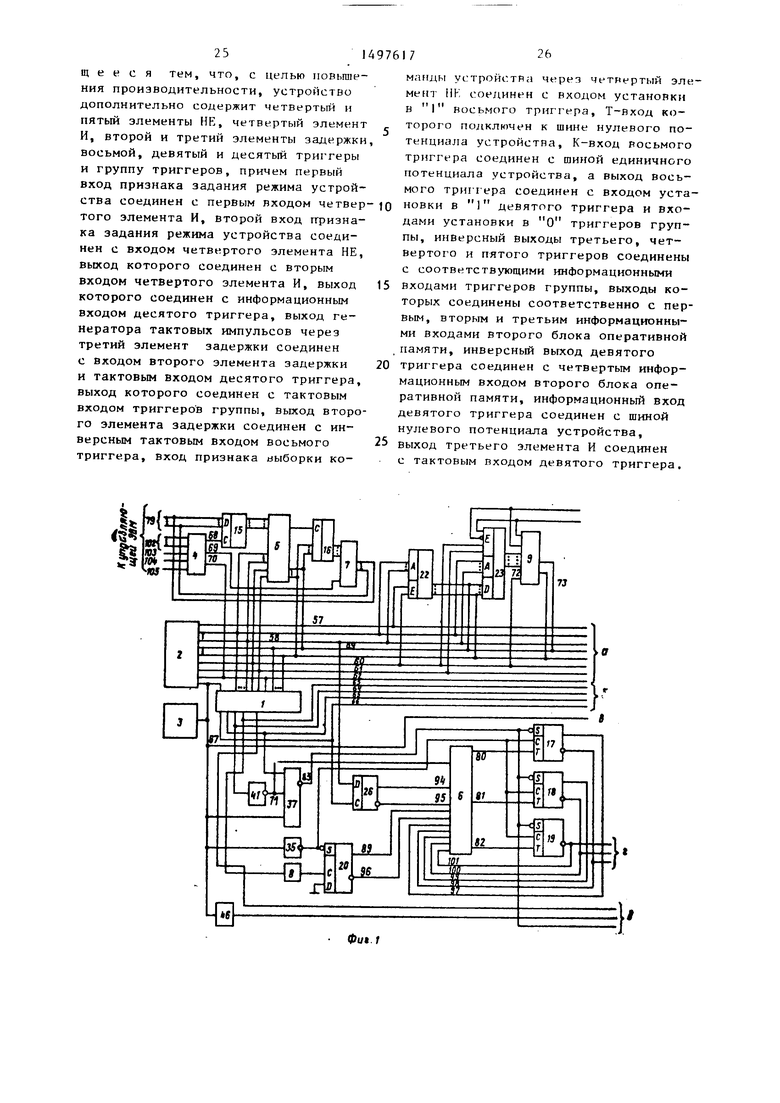

На фиг. 1 и 2 приведена схема предлагаемого устройства для отладки программно-аппаратных блоков.

Устройство содержит первый 1 и второй 2 блоки микропрограммного управления, генератор 3 импульсов, второй 4, третий 5, десятый 6 и первый 7 дешифраторы, первый элемент 8 задержки, восьмой 9, четвертый 10, седьмой 11, девятый 12, пятый 13 и шестой 14 дешифраторы, первый 15 и второй 16 регистры, третий 17, четвертый 18, пятый 19 и шестой 20 триггеры, одновибратор 21, блок 22 постоянной памяти, первый 23, второй 24 и третий 25 блокр оперативной памяти, седьмой триггер 26, первый 27 и второй 28 счетчики, второй 29 и первый 30 мультиплексоры, третий 31 и четвертый 32 регистры, первый 33 и второй 34 триггеры, второй 35 и первый 36 элементы НЕ, третий 37, первый 38 и второй 39 элементы И, схему .4J3 сравнения, третий 41, четвертый

со

sj

а

31/+9

42 и пятый 43 элементы НЕ, четрертын 3JTtMeHT И 44, второй 45 и третий 46 элементы гэадержкн, восьмой 47, девятый 48 и десятый 49 триггеры, группу трипч ров 50, первый выход 51 строба iij4peca, первый 52 и второй 53 выходы признака задания режима, выход 54 признака выборки команды, вход 55 признака готовности, второй 56 и пер вый 57 выходы признака готовности, вторые адресные входы 58, вторую двунаправленную информационную магистраль 59, вход 60 признака чтения, вход 61 признака записи, первый выход 62 признака сброса, вход 63 признака выборки команды, первый 64 и второй 65 входы признака задания режима, вход 66 строба адреса устройства, бы ход 67 -генератора импульсов, первый 68, второй 69 и третий 70 выходы второго дешифратора, первый вход 71 третьего элемента И, группу входов 72 и выходов 73 восьмого дешифратора первый 74, второй 75 и третий 76 выходы четвертого дешифратора, первый 77 и второй 78 выходы пятого дешифратора, первые информационные входы-выходы 79 устройства, первый 80, второй 8Г и третий 82 выходы де- сятого дешифратора, выход 83 третьего элемента И, первый 84, второй 85, третий 86, четвертый 87 и пятый 88 выходы седьмого дешифратора, прямой выход 89 шестого триггера, второй вх вход 90 второго элемента И, прямой выход 91 второго триггера, выходы 92 и 93 переполнения второго и первого счетчиков импульсов соответственно, второй 94,;. третий 95, пятый 96, шестой 97, седьмой 98, восьмой 99, девятый 100 и десятый 101 выходы десятого дешифратора, первые адресные входы 102, первые входы признака записи 103, признака чтения 104, приз- нака сброса 105, третьи информационные входы-выходы 106, группу адресных выходов 107, первые входы признака чтения 108, признака записи 109, второй выход 110 признака сброса УСТ ройства, информационный вход 111 и выход 112 десятого триггера 49 и выход 113 восьмого трип-ера 47.

Устройство работает под управляющей ЭВМ в качестве которой может быть использована, например, микро- ЭВМ УВС-0), и обеспечивает отладку устройств на основе микропроцессоров содержащих встроенную очередь кома)д

например К1810ВМ86 или KI810BM88. Системная шина управляющей ЭВМ подключается к входным шинам устройства для отладки программно-аппаратных блоков. Выходные шины устройства подключаются к шинам отлаживаемого устройства. Устройство может работать в одном из двух режимов: режиме управления и режиме отладки.

Рассмотрим работу предлагаемого устройства в режиме управления.

Сигнал уровня О, появляющийся на первом входе 105 признака сброса устройства при нажатии кнопки сброса на пульте управляющей ЭВМ, проходит через второй дешифратор 4 и с выхода 70 последнего воздействует на блоки I и 2, первый триггер 33 и седьмой дешифратор 11, выполняя их начальную установку. Через шестой дешифратор 14 сигнал сброса поступает также на второй выход 110 признака сброса устройства. По окончании воздействия сигнал сброса на выходе 91 режима второго триггера 34 появляется сигнал уровня О, который через второй элемент И 39 поступает на вход готовности блока ЭВМ 1 микропрограммного управления, запрещая ее работу. При этом сигнал уровня 1 с первого выхода 57 признака готовности устройства поступает на вход готовности блока 2, разрешая его работу. Блок 2 начинает отработку программы-монитора, содержащейся в блоке 22 постоянной памяти. В соответствии с этой программой блок 2 находится в цикле ожидания команд, подаваемых с управляющей ЭВМ,

Команда в виде соответствующего кода поступает от управляющей ЭВМ по первым информационным входам-выходам 79 и при определенном адресе, выставляемом на первый адресный вход 102 и при наличии сигнала на первом входе 103 записи запоминается в первом регистре 15, Блок 2 в соответствии с выполняемой программой постояи- но опрашивает этот регистр, Выставляя соответствующий код адреса на вторых адресных входах 58 и сигнал на втором входе 60 признака чтения. Прочитав код с группы выходов третьего дешифратора 5, бЛок 2 переходит к выполнению программы обработки полученной команды, В соответствии с получаемьпчи командами блок 2 производит загрузку третьего блока 25

ратнвной памяти, третьего 31 и четвертого 32 регистров и при необходимости первого блока 23 оперативной памяти. Эти операции выполняются следующим образом.

На вторых адресных входах 58 блок 2 устанавливает адрес, соответствующий одному из узлов устройства, а по второй двунаправленной информа- дионной магистрали 59 блок 2 передает необходимые коды, сопровождая их сигналом по второму входу 61 признака записи. При этом при обращении блока 2 к первому блоку 23 оператив- ной памяти на старщей адресной линии присутствует сигнал уровня О, а пр обращении к второму блоку 24 оперативной памяти, четвертому дешифратору 10, пятому дешифратору 13 и шесто му дешифратору 14 - сигнал уровня I. В третий блок 25 оперативной памяти записывается информация о том, ли при отладке использоваться память отлаживаемого устрой- ства или будет ли использоваться первый блок 23 оперативной памяти, в последнем случае ЭВМ 2 загружает в первый блок 23 оперативной памяти отлаживаемую программу. В соответст- ВИИ с информацией, записанной в третьем блоке 25 оперативной памяти, при отладке на выходе 90 будет выра- батьгоаться соответственно сигнал

разрешения работы первого блока 23

/- оперативной памяти (сигнал уровня

О) или шестого дешифратора 14 (сигнал уровня 1).

В третий 31 и четвертый 32 регистры записьшается условие оконча- ния отладки, при выполнении которого запрещается выполнение отлаживаемой программы подачей на первый выход 62 признака сброса сигнала начальной установки.

Для перехода в режим отладки блок 2, получив соответствующий код команды через первый регистр 15 и третий дешифратор 5, устанавливает на вторых адресных входах 58 код, состоя- щий из всех единиц. В этом случае на первом выходе 57 признака готовности вырабатьтается сигнал уровня О, который отключает блок 22 постоянной памяти, поступая на вход готовности блока 2, запрещает его работу, а также поступает на второй вход пятого дешифратора 13, и сигнал уровня 1. на выходе 91, которым разрешается

17

работа блока 1 и включается второй блок 24 оперативной памяти.

В режиме отладки работает блок I, выполняя Отлаживаемую программу. Бло 1 состоит из трех блоков: блока упраления канапом, блока исполнения команд и блока очереди команд. Блок управления каналом организует циклы канала, выбирает из памяти коды отлаживаемой программы и загружает их в блок очереди команд. Блок исполнения команд последовательно исполняет команды, выбирая их из блока очереди команд. Если в процессе выполнения команды необходимо обратиться к памяти, то блок исполнения команд делает заявку, блок управления каналом, закончив очередную выборку программного кода из памяти, удовлетворяет эту заявку. Объем запоминающего узла блока очереди команд ограничен, если он заполнен, то блок управления каналом работает вхолостую, если в блок очереди команд можно поместить байты программного кода, то блок управления каналом выполняет цикл выборки из памяти кода команды. Таким образом, в блоке 1 организована предварительная (заблаговременная) выборка кодов команд, а операции выборки и исполнения совмещены во времени. Поэтому последовательность выборки не соответствует последовательности их исполнения, в частности команды, которые были выбраны из памяти после выборки команды безусловного перехода, в действительности исполняться не будут. Чтобы восстановить реальную картину исполнения команд, необходимо иметь сведения о взаимодействии блока исполнения команд с блоком очереди команд. Код на выходах 64 и 65 признака задания режима свидетельствует о том, что в предыдущем такте из блока очереди команд блока 1 был выбран первый байт кода команды, либо был выбран последующий байт кода команды, либо блок очереди команд был очищен в результате выполнения команды перехода, либо в предшествующем такте блок исполнения команд не обращался к блоку очереди команд. Также необходимо знать количество команд, находящихся в блоке очереди команд в определенные моменты времени. Эту информацию вырабатывает узел, включающий десятый дешифратор 6, третий 17, четвертый 18,

пятый 19, шестой 20 и седьмой 26 триггеры, третий элемент И 37, второй 35 и третий 41 элементы НЕ и первый элемент 8 задержки.

Выполняя отлаживаемую программу, блок 1 производит обращения либо к первому блоку 23 оперативной памяти, либо к памяти отлаживаемого устройства в зависимости от информации, за- писанной в третьем блоке 25 оперативной памяти. Обмен информацией между памятью и блоком 1 производится через шестой дешифратор 14 следующим образом. В случае передачи информа- i ции от блока 1 в память отлаживаемого устройства информация на вторых адресных входах 58 и второй двунаправленной информационной магистрали 59, сопровождающаяся сигналом на втором входе 61 признака записи, передается через шестой дешифратор 14 при наличии разрешающего сигнала на выходе 90 на группу адресных выходов

107и третьи информационные входы-выходы 106 к памяти отлаживаемого устройства, сопровождаясь при этом сигналом по первому выходу 109 признака записи.

При приеме информации из памяти отлаживаемого устройства блок 1 устанавливает на втором выходе 60 признака чтения устройства сигнал чтения данных, который через шестой дешифратор 14 поступает на первый выход

108признака чтения, а на вторых адресных входах 58 - адрес ячейки,

к которой производится обращение. Ко адреса через шестой дешифратор 14 поступает на группу адресных вьсходов 107 устройства. Код адреса и сигнал на первом выходе 108 признака чтения будут сохраняться до тех пор, пока память отлаживаемого устройства не установит считанную информацию на третьих информационных входах-выходах 106, с которых через шестой дешифратор 14 она поступит на вторую двунправленную информационную магистраль 59 ЭВМ 1.

Синхронизация работы блока 1 и памяти отлаживаемого устройства выпоняется с помощью входа 55 признака готовности. При обращении к памяти последняя устанавливает на входе 55 сигнал уровня О, который через тре. тий вход второго элемента И 39 поступает на торой выход 56 признака готовности, яапрещая работу блокл 1,

Q

Q с

5

0

5

сигнал этого уровня остается до тех .пор, пока память не закончит внутренний цикл (т.е. не произведет запись или вьщачу информации). По окончании внутреннего цикла на входе 55 признака готовности память устанавливает сигнал уровня 1, который через второй элемент И 39 поступает на второй выход 56. Блок I, обратившись к памяти отлаживаемого устройства, приостанавливает свою работу на все то время, в течение которого на входе 55 признака готовности остается, сигнал уровня О.

В течение всего времени работы блока 1 включен второй блок 24 оперативной памяти, в котором по положительному фронту конъюнкции сигналов на вторых входах 60 и 61 признака чтения и признака записи запоминается информация с вторых адресных входов 58, второй двунаправленной информационной магистрали 59, информационных выходов группы триггеров, а также с инверсного выхода девятого триггера 48.

В схеме 40 сравнения в режиме отладки постоянно происходит сравнение кодов адреса с вторых адресных входов 58 с заданными в качестве условий выхода из режима отладки. При совпадении кодов адрес с заданными на выходе 91 вырабатывается сигнал уровня О, который запрещает запоминание информации во втором блоке 24 оперативной памяти и останавливает блок 1, а на выходе 57 появляется сигнал уровня 1, который разрешает работу блока 22 постоянной памяти и блока 2. Одновременно с этим одновиб- ратор 21 и первый элемент НЕ 36 формируют на линии 62 сигнал начальной установки.

Блок 2 начинает отработку программы, содержащейся в блоке 22 постоянной памяти, и остается в цикле ожидания команды от управляющей ЭВМ. Эти команды, в частности, могут инициировать передачу в управляющую ЭВМ информации, содержащейся во втором блоке 24 оперативной памяти.

Таким образом, устройство для отладки программно-аппаратных бликов позволяет моделировать отлаживаемое устройство на самых ранних этапах разработки, используя при этом пер- блок 23 оперативной памяти, и производить отладку програм шого

обеспечения, необходимого для работы отлг1живг1емог-о ycTpoiicTHa, с запоминанием информации во втором блоке 24 оперативной памяти. При отладке обеспечивается останов отлаживаемой программы по адресу, задаваемому опе тором.

На элементах 46, 45, 49, 44, 42, 37, 41, 48, 47, 50 и 43 реализован узел фиксации глубины очереди команд который работает следующим образом. Когда на входах 64 и 65 признака режима устройства появится информация об исполнении первого байта кода команды (код 10), срабатывает четвертый элемент И 44 и на его выходе 111 появится сигнал уровня 1. Это значение по положительному фронт сигнала синхронизации выхода 67, за- держанного третьим элементом 46 задержки, будет переписано на выход десятого триггера 49, где также появится сигнал уровня 1. Этот положтельный фронт на линии 112 перепи- шет значение глубины очереди команд с входов группы триггеров 50 на ее выходы. Таким образом, на выходах группы триггеров 50 будет находиться значение глубины очереди команд ЭВМ 1 перед исполнением первого байта кода команды.

Когда на входах 64 и 65 признака режима устройства появится информаци об очистке очереди (код 01), то в положительном полупериоде сигнала синхронизации с выхода 67 сработает третий элемент И 37 и на его выходе появится сигнал уровня О. По положительному фронту этого си1 нала на инверсном выходе девятого триггера 48 появится сигнал уровня 1, это свидетельствует о том, что была произведена очистка очереди команд. Запись информации во второй блок 24 оперативной памяти происходит в конце такта каждого цикла шины по отрицательному фронту сигнала синхронизации с выхода 67. Отрицательный фронт этого сигнала, задержан

ный третьим 46 и вторым 45 элементами задержки на четверть периода сигнала синхронизации с выхода 67, запишет в восьмой триггер 47 ноль и на его выходе 113 появится сигнал уровня О. По положительному фронту сигнала на входе 63 признака выборки команды, проинпгртированному и задержанному инвсртп1юм 36, восьмой

g 5 0 5 0

5 0 5

0

5

триггер 47 будет установлен в единичное состояние. Задержка, вносимая пятым элементом НЕ 43 больше задержки, вносимой элементами 45 и 46, но меньше половины периода сигнала синхронизации с выхода 67. Таким образом, на выходе 113 сразу после записи очередной строки в трассу появится импульс уровня О, который на выходах группы триггеров 50 и девятого триггера 48 установит сигналы уровня О. Если до следующей записи в трассу не будет начато выполнение команды и не будет произведена очистка очереди команд, то там сигналы уровня О так и останутся. Если до следующей записи в трассу будет начато исполнение нескольких команд, то в трассу будет записана глубина очереди команд, соответствующая последней из таких команд.

Шестой дешифратор 14 реализует следующие логические функции (индексы у переменных X соответствуют номерам входов дешифратора, индексы у переменных Y - номерам выходов дешиф- торов):

Y., Х„, ;(1)

(2) (3) (4) (5) (6) (7) (8) (9) (10)

fe ЧГР

YIOS Х„ V X

9с

108

60 90

Yj, Х,з Y ; Y, Х, V X

Y53 X

f - и

90

65 V Хоо ;

ас f

(07 5t Х9о ;

«56 Xj5 V Xgo V X j, ;

eg X,oj V V X 40 .

Из формулы () следует, что дешифратор буферизирует сигнал сброса с первого выхода 62. Сигналы 61, 62, 63, 64, 65, 66 имеют активный низкий уровень и проходят сквозь дешифратор 14 только при наличии сигнала разрешения 90 уровня 1, что свидетельствует об обращении ЭВМ 1 к памяти отлаживаемого устройства (формулы (2)-(8)). Сигналы с второй двунаправленной информационной магистрали 59 проходят в отлаживаемое устройство при наличии сигнала разрешения 90 и сигнала признака записи 61. Сигналы с третьих информационных входов-выходов 106 отлаживаемого устройства проходят на вторую двунаправленную информационную маг-истраль 59 при наличии разрешающего сигнала 90 и сигнала чтения 60, что следует из формул (9) и (10).

В третьем блоке 25 оперативной памяти содержится информация, управ- лянмцая обращением блока 1 к памяти в ре(име отладки. Подпрограмма загруз- ки третьего блока 25 оперативной па млти содержит адрес обращения к этому узлу: при этом четыре старших разряда адреса подаются на первый канал первого мультиплексора 30, остальные разряды адреса подсоединены к соот- гзетствующим входам пятого дешифратора 13, четыре старших разряда второй двунаправленной информационной магистрали 59 поступают на входы второ- I o канала первого мультиплексора 30, а младший разряд - на информационный вход третьего блока 25 оперативной памяти. Код адреса сопровождается сигналом признака записи 61. При наличии сигналов уровня О на втором входе 61 признака записи и первом выходе 57 признака готовности и наличии соответствующего кода на остальных входах пятого дешифратора I3 на первом выходе 77 последнего появляется сигнал уровня 1, разрешающий передачу информации через первый канал первога мультиплексора 30 и запись информации в третий блок 25 оперативной памяти. В то же время сигнал на втором выходе 78 имеет уровень О. Информация, записанная в третьем блоке 25 оперативной памяти, в дальнейшем будет использовать ся для определения, где будет располагаться соответствующий сегмент памяти (либо в первом блоке 23 оперативной памяти, либо в отлаживаемом устройстве). При этом младший раз- ряд второй двунаправленной информационной магистрали 59 содержит информацию о месте расположения соответствующих сегментов памяти, а четыре старших разряда содержат код соот ветствующего сегмента памяти. Если по некоторому адресу в третьем блог ке 25 оперативной памяти записан ноль, то в дальнейшем к соответствующему сегменту будут обращаться в первый блок 23 оперативной памяти, в противном случае - к памяти оглаживаемого устройства.

В режиме отладки сигнал нл первом выходе 57 признака готовности прини- мает уровеНЕз 1, при этом на первом выходе 77 пятого дешифратора 13 появляется сигнал уровня О, а на втором Pwxoju 78 - уровня I независимо от состояния сигналов на остальных входах пятого дешифратора 13. Сигнал 57 таким образом запрещает запись информации в третий блок 25 оперативной памяти и разрешает считывание информации из этого блока оперативной памяти. Теперь всякий раз, когда блок 1 выставляет на вторых адресных входах 58 новый адрес, его старшие четыре разряда будут проходить через первый канал первого мультиплексора 30 на адресные входы третьего блока 25 оперативной памяти а сигнал на выходе третьего блока 25 оперативной памяти будет указыват место нахождения сегмента памяти, задаваемого четырьмя старшими разрядами адреса.

Дешифратор 9 при наличии на его входах 60, 57 и 90 сигнала уровня О передает сигналы с входов 72 на выходы 73 без изменения, в противном случпе сигналы на выходах 73 имеют уровень 1.

Программирование третьего 31 и четвертого 32 регистров адресом останова выполнения отлаживаемой программы и сравнение адресов схемой 40 сравнения в режиме отладки осуществляется следующим образом. Сигнал инициализации, появляющийся на первом выходе 62 признака сброса, поступает на инверсный вход установки в О первого триггера 33 и через первый элемент И 38 на тактовый вход второго триггера 34, устанавливая на прямых выходах этих триггеров сигнал уровня О, а на инверсном выходе второго триггера 34 - сигнал уровня 1. Таким образом, разрешена работа блока 22 постоянной памяти и ЭВМ 2 обрабатывает программу, содержащуюся в блоке 22 постоянной памяти. Получив команду загрузки третьего 31 и четвертого 32 регистров, блок 2 выставляет соответствую - щий адрес обращения на вторых адресных входах 58, сопровождая его сигналом на втором входе 61 признака запис уровня О, причем старший разряд адреса содержит единицу. При этом в зависимости от выставленного адреса на первом выходе 74 или втором выходе 75 появится сигнал уровня 1, производящий запись информации в Третий регистр 31 или четвертый регистр 32 соответственно, при этом в регистр записывается информация с

второй двунаправленной информационной магистрали 59. Таким образом, каждому из этих регистров присвоен адрес обращения. В третий регистр 31 записывается код, который будет старшей частью адреса останова, в четвертый регистр 32 - код, который будет младшей частью адреса останова. Тогда на выходах этих регистров будет адрес останова, он подается на Входы второго сравниваемого числа схемы 40 сравнения. При работе устройства для отладки программно- аппаратных блоков в режиме отладки на вторых адресных входах 58 будут появляться коды адресов обращения блока I к первому блоку 23 оперативной памяти или памяти отлаживаемого устройства, и как только код адреса совпадет с кодом, записанным в третьем 31 и четвертом 32 регистрах, схема 40 сравнения сработает и на е выходе появится сигнал уровня I, который положительным фронтом, пода Баемым на одновибратор 21, вызовет на выходе последнего импульс уровня 1, который, пройдя через первый элемент И 38, своим положительным фронтом установит на выходе 91 низ- кий уровень. Этот же одиночный импульс, пройдя через первый элемент НЕ 36, поступит на первый выход 62 признака сброса, производя началную установку ЭВМ и других узлов. Таким образом завершен цикл работы обмен с управляющей ЭВМ - отладка. После того, как блок 2 закончит подготовку к работе всех узлов устройства для отладки программно-аппа- ратных блоков, он выполняет цикл записи по адресу, состоящему из всех единиц кода, содержащего все единицы При появлении этого адреса на вторых адресных входах 58 на третьем выходе 76 четвертого дешифратора 10 появится сигнал уровня 1. Положительным фронтом сигнала на втором входе 61 признака записи информация с информционного входа первого триггера 33 перепишется на его выход, эта I, появившаяся на выходе первого триггера 33, поступит на вход установки В 1 второго триг гера 34 и на первом выходе 57 признака готовности появится сигнал уровня О. Этот сигнал запретит работу блока 2 и блока 22 постоянной памяти, а одновременно появившийся сигнал уровня

1 на выходе 91 разрешит работу второго блока 24 оперативной памяти и блока 1. Последний начнет выполнять отлаживаемую программу.

Первый дешифратор 7 передает информацию с выходов второго регистра 16 на первые информационные входы- выходы 79 устройства при наличии сигнала уровня 1 на входе 69, в противном случае на выходах первого дешифратора 7 все сигналы имеют уровень 1. При необходимости передать информацию из управляющей ЭВМ в устройство для отладки программно- аппаратных блоков управляющая ЭВМ выставляет соответствующий код адреса обращения на первых адресных входах .102, сопровождая его сигналом на первом входе 103 признака записи. При этом на первом выходе 68 второго дешифратора 4 появится сигнал уровня 1, который стробирует загрузку ниформации в первый регистр 15 с первых информационных входов-вьосодов 79 Блок 2, обращаясь к третьему дешифратору 5, выставляет соответствующий адрес и сопровождает его сигналом на втором входе 60 признака чтения. В результате информация с выходов регистра 15 без изменений будет передана на группу выходов третьего дешифратора 5, в противном случае на этих выходах присутствуют сигналы уровня 1.

При необходимости передать информацию из устройства для отладки программно-аппаратных блоков в управляющую ЭВМ блок 2 выставляет соответствующий код адреса обращения на вторых адресных входах 58, сопровождая его сигналом на втором входе 61 признака записи. При этом на выходе третьего дешифратора 5 появляется сигнал уровня 1, который стробирует загрузку информации во второй регистр 16. Управляющая ЭВМ, обра-; щаясь к первому дешифратору 7, выставляет соответствующий адрес и сопровождает его сигналом на первом входе 104 признака чтения. В результате информация с выходов второго регистра 16 будет без изменения передана на выходы первого дешифратора 7. Сигнал на первом выходе 62 признака сброса второго дешифратора 4 всегда повторяет сигнал на первом входе 105 признака сброса.

151А9761

Дешифратор 11 реализует следующие лог ические функции:

93 61

(11)

где X д - сигнал с выхода переполнения первого счетчика импульсов 27;

(28 ,, t. 53,

где Х-, - сигнал на прямом выходе второго триггера 34;

V - Y V Y

Чт чг бг

(13)

где Xgj - сигнал с выхода переполнения второго счетчика 28 импульсов; Ygg (Xj8V X,, Хз,)ЛХ,ЛХе,.

(lA)

При выдаче сигнала инициализации на первом выходе 62 признака сброса появляется сигнал уровня О, кото- рьй в соответствии с (11) и (12), пройдя через седьмой дешифратор 11, производит начальную установку первого 27 и второго 28 счетчиков импульсов. На выходах обоих счетчиков импульсов устанавливается код, состоящий из всех нулей. При работе блока 2 по программе, содержащейся в блоке 22 постоянной памяти, запись информации во второй блок 24 опера- тивной памяти производиться не будет поскольку в этом режиме сигнал на выходе 91 принимает значение О и в соответствии с (14) на пятом выходе 88 седьмого дешифратора 11 появится пассивный сигнал уровня О который запретит запись информации во второй блок 24 оперативной памяти.

В режиме отладки сигнал на выходе 91 принима ;т значение 1. В дальнейшем, выполняя отлаживаемую программу блок 1 сопровождает адресу и данные одним из управляющих сигналов на втором входе 61 признака записи или входе 60 признака чтения, которые принимают значения О. При этом в соответствии с (14) на пятом выходе 88 седьмого дешифратора 11 появляется сигнал уровня 1, разрешающий запись во второй блок 24 оперативной памяти. По окончании действия сигнала на входе 60 или 61 в соответствии с (12) отрицательный перепад сигнала на третьем выходе 86 седьмого дешиф- ратора 11 производит увеличение кода на единицу на информационных выходах второг О счетчика 28 импульсов. Зтот код поступает на адресные входы нто-

5

0 5 0 с

о ,

0

716

рого блока 24 оперативной памяти и, следовательно, является следующим адресом, по которому будет произведена запись новой информации. При переполнении второго счетчика 28 импульсов на его выходе 92 переполнения появляется импульс, который в соответствии с (13) поступает на вход установки нуля второго счетчика 28 импульсов, И последующая информация будет записываться с нулевых адресов. По окончании режима отладки сигнал на выходе 91 принимает значение О и в соответствии с (14) запись информации во второй блок 24 оперативной памяти производиться не будет.

Блок 2, отрабатывая программу, содержащуюся В блоке 22 постоянной памяти, получает команду чтения информации из второго блока 24 оперативной памяти и переходит к выполнению соответствующих подпрограмм, выставляя при этом соответствующий адрес обращения и сопровождая его сигналом на втором входе 60 признака чтения уровня О. При этом на втором выходе 85 седьмого дешифратора 11 появляется сигнал уровня 1, который поступает на Вход чтения второго блока 24 оперативной памяти. На выходах второго блока 24 оперативной памяти, появляется записанная ранее информация, которая представлена не более, чем 64 разрядами (два байта - данные, три разряда - с выходов 98, 100 и 101, один разряд - с инверсного выхода девятого триггера 48, остальные разряды - код адреса с вторых адресных входов), все разряды разбиты на четыре равные группы и сигналы с них поступают на cootвeтcтвyющиe каналы второго мультиплексора 29. Чтение информации из второго блока 24 оперативной памяти производится по нулевому адресу, так как по окончании режима отладки узел сравнения вырабатывает сигнал начальной установки на первом выходе 62 признака сброса, который в соответствии с (11) и (13) произведет сброс первого 27 и второго 28 счетчиков импульсов, на выходах которых будет присутствовать нулевой код. Нулевой код с выходов первого счетчика 27 импульсов поступает на два управляЕощих входа второго мультиплексора 29, что соответствует передаче информации с первого.

канала сквозь девятый дешифратор 12 на вторую двунаправленную информационную магистраль 59. Девятый дешифратор 12 передает информацию с выхо- дов второго мультиплексора 29 на выходы 59 без изменений при наличии сигнала уровня 1 на выходе 91, в противном случае все сигналы уровня 1 на выходах девятого де- шифратора 12 имеют уровень 1. Сигнал с второго входа 85 седьмого дешифратора 1I поступает также на счетный вход первого счетчика 27 импульсов и по окончании этого сигна- ла отрицательным переходом, т.е. по окончаний чтения информации с первого канала второго мультиплексора 29 происходит увеличение на единицу кода, присуствующего на выходах первого счетчика 27 импульсов. Таким образом, на выходе первого счетчика 27 импульсов будет код 01 и при следующем чтении информации из второго блока 24 оперативной памяти будет передан через второй мультиплексор 29 код с его второго канала. Информация с второго, третьего и четвертого каналов второго мультиплексора 29 будет прочитана аналогичным образом. При пятом обращении к второму блоку 24 оперативной памяти на выходе 93 переполнения первого счетчика 27 импульсов появится сигнал

уровня 1, который в соответствии

с (1,1) произведет начальную установку первого счетчика 27 импульсов и в соответствии с (12) поступит на счетный вход второго счетчика 28 импульсов, увеличивая на единицу код на его информационных выхс/дах, что соответствует следующему адресу обращения к второму блоку 24 оперативной памяти.

Для корректной интерпретации трас сировочной информации, содержащейся во втором блоке 24 оперативной памяти, в него необходимо записьюать информацию о глубине очереди команд блока 1. Эта информация формируется на инверсных выходах третьего 17, четвертого 18 и пятого 19 триггеров.

Функционирование десятого дешифратора 6 описывается следующими выраже-гг ниями:

Y,o X-,,VX5, V (15)

Yg ,VX,,ЛX,,ЛX„VX5,Л

л X,, Л ,;(16)

, Q is 20 25 30

ос

О

j

Y ,1 Х,,И 7, 95 9 ,j Л Х,„о Л

0

г

л x,nx,,v х„, л х„„лх л X

9

97

99

71

(17)

в текущем такте код на первом 64 и втором 65 входах признака задания режима свидетельтвует о том, что происходило с блоком очереди команд в предьщущем такте. Цикл шины блока 1 длится четыре такта сигнала на выходе 67 генератора импульсов. В тактах Т1 и Т2 каждого цикла шины сигнал на входе 66 строба адреса имеет уровень О. Если в течение данного цикла шины происходит выборка из памяти кода команды, то сигнал на входе 63 признака выборки команды имеет уровень О в течение тактов Т1, Т2 и ТЗ. В седьмом триггере 26 по положительному фронту сигнала на входе 66 строба адреса запоминается значение младшего разряда адреса, который бьш выставлен ЭВМ в текущем цикле шины. Задержка, вносимая первым элементом 8 задержки, должна быть минимальной, но больше задержки, вносимой вторым элементом НЕ 36. Учитьшая это, сигнал на выходе 89 шестого триггера 20 буд-ет иметь низкий уровень в такте Т4 цикла выборки команды (а не в цикле обращения в память за операндом) в течение времени, пока сигнал на выходе 67 генератора импульсов имеет уровень О. Появление комбинации, сигналов на входах 64 и 65 в такте Т4 свидетельствует о том, что в такте ТЗ блок очереди команд был очищен. Эти сигналы, поступая уровнями 1 на входы третьего элемента И 37, Приведут к появлению импульса уровня о во втором полуь риоде такта Т4, которьй в третий 16, чеТ вертый 18 и 19 триггеры запишет единичную информацию, а на их инверсных выходах появится сигнал уровня О. Согласно формуле (15) состояние третьего тригг ера I 7 необходимо изменять на противоположное, если глубину очереди команд надо изменить на 1 : плюс один, 1 сли в такте Т4 цикла выборки команды была информация об исполнении байта команды (в этом такте сигнал на первом входе 64 задания режима имел высокий уровень), и минус один, если информация об исполнении байта появилась в любом другом такте. В соответствии с (16) состояние шпвертого триггера 18 необходимо изменять на противоположное Р следующих случаях. Глубину очереди команд надо увеличить на дна в спязи с тем, что была произведена выборка кода команды по четному адресу, в этом случае ЭВМ 1 выбирает за одно обращение к памяти 2 байта. Увеличение на 2 производится в такте ТА и только при условии, что в такте ТЗ не бьиш выполнено байта команды (т.е. в такте Т4 сигнал на первом входе 64 задания режима имел уровень О). Состояние триггера 18 также надо менять, если глубину надо увеличить на один, а она имеет нечетное значение, надо уменьшить на один, а она имеет четное значение. В соответствии с (17) состояние пятого триггера 19 надо изменять на противоположное, если глубину надо увеличит на один, а она равна трем, если глубину надо уменьшить на один, а она равна четырем, и если глубину надо увеличить на 2, а она равна двум или трем. Максимальная глуби- на очереди равна шести. Десятый де- ши({)ратор 6 выдает единицу на Т-входы тех триггеров, состояние которых надо изменять в текущем такте. Изменение происходит по положительному фронту сигнала на выходе 67 генератора импульсов.

Расшифровку трассировочной 1Шфор- мации выполняют следующим образом.

Всю трассу выполнения программы условно разбивают на непересекающиеся линейные участки. Концом линейного участка является строка, содержащая информацию об очистке очереди.

Вначале определяют границу перво- го линейного участка. Для этого анализируют строки трассы, пока не будет обнаружена очистка очереди или не будет достигнут конец трассы (если исполненная программа не содержа- ла команд перехода). После обнаружения очистки очереди определяют ближайшую в пределах линейного участка глубину, отличную от нуля..Это буде глубина, соответствующая nepBOMv байту команды перехода. Этот байт был выбран по адресу обращения, на Т меньшему, чем адрес, содержащийся в строке, где была обнаружена нену- леГ ая глубина. Зная первый байт ко- манды перехода, можно-по нему определить число байт кода команды перехода, так как эта величина однп)цач но определяется первым байтом кс1лл

К(.1мапды. Таким образом, определили последний Р1ипо:п1енный перед очисткой очереди байт команды - это последний байт кода команды перехода. Первый выполненный после очистки очереди байт расположен в той строке траСсы, где и информация об очистке очереди. Команды, расположенные между этими двумя байтами, были яь браны микропроцессором, но реально не исполнялись и их из трассы необходимо удалить .

Теперь текущий линейный участок содержит только исполненные команды, и следует переход на начало этого линейного участка с целью определени местонахождения первого байта кода каждой команды, входящей в этот линейный участок. Если конец линейного участка связан с концом трассы, то выбранных и не исполненных команд на этом линейном участке не будет.

После перехода на начало линейного участка аналогично описанному вы- ще определяют ближайщую ненулевую глбину, а по ней и местонахождение первого байта кода команды (так как глубина фиксируется в момент перед выполнением первого байта кода команды) . По первому байту команды определяют ее длину и соответствующее количество байт программного кода отсчитывают в сторону увеличения адресов. Если при этом не достигнут конец линейного участка, то следующий байт после отсчитанных байтов будет первым байтом очередной команды. Определяют длину этой команды и так далее. Если конец линейного участка достигнут, то определяют, является ли этот линейный участок последним в трассе. Если нет, то повторяют весь цикл расшифровки для следующего линейного участка. Если да, то вся трасса расшифрована.

Формула изобретения

Устройство для отладки программно аппаратных блоков содержащее десять дешифраторов, генератор тактовых импульсов, первый, второй, третий и четвертый регистры, блок постоянной памяти, первый, второй и третий блоки оперативно памяти, первый и второй счетчики импульсов, первый и второй мультиплексоры, семь триггеров, первый, BTOpoii и третий элементы НЕ,

одновибратор, первый, второй и третий элементы И, схемы сравнения и первый элемент задержки, причем первая группа информационных входов- выходов устройства через первую двунаправленную магистраль соединена с группой информационных входов первого регистра и группой выходов первого дешифратора, первая группа адресных входов, первые входы признака записи, признака чтения и признака сброса устройства соединены с входами второго дешифратора, первый, второй и третий выходы которого соединены соответственно с входом записи первого регистра, входом первого дешифратора и первым выходом признака сброса устройства, группа выходов первого регистра соединена с первой группой входов третьего дешифратора, выход которого соединен с входом записи второго регистра, вторая группа адресных входов устройства соединена с группой адресных входов блока постоянной памяти, первого блока оперативной памяти, первой группой входов схемы сравнения, группой входов четвертого и пятого дешифраторов, первой группой информационных входов первого мультиплексора, первой группой входов шестого дешифратора, группой входов седьмого дешифратора, первой группой информационных входов второго блока оперативной памяти и второй группой входов третьего дешифратора, группа выходов которого через вторую двунаправленную магистраль соединена с группой информационных входов первого блока оперативной памяти, группой информационных выходов блока постоянной памяти, группой выходов восьмого дешифратора, второй группой информационных входов второго блока оперативной памяти, группами информационных входов второго, третьего и четвертого регистров, второй группой информационных входов первого мультиплексора, вто- рой группой входов шестого дешифратора, группой выходов девятого дешифратора, первой группой выходов шестого дешифратора и второй группой информационных входов-выходов устройства, группа выходов второго регистра соединена с группой входов первого дешифратора, второй вход признака чтения устройства соединен с входами чтения блока постоянной памяти, первого блока оперативной памяти/ первыми входами третьего, шестого, седьмого и восьмого дешифраторов, второй вход признака записи устройства соединен с первым входом пятого дешифратора, вторыми входами третьего, шестого и седьмого дешифраторов, входом четвертого дешифратора, тактовым вхо- )0 дом первого триггера, вхол,ом записи первого блока оперативной памяти, группа информационных выходов первого блока оперативной памяти соединена с группой входов восьмого дешиф- 5 ратора, первый и второй выходы четвертого дешифратора соединены с тактовыми входами третьего и четвертого регистров, группы информационных выходов которых соединены с вто- 0 рой группой информационных входов

схемы сравнения, выход которой через одновибратор соединен с первым входом первого элемента И и через первый элемент НЕ с вторым входом пер- 5 вого элемента И, входом установки

в О первого триггера, третьими входами шестого и седьмого дешифраторов и третьим входом второго дешифратора, третий выход четвертого дешифра- 0 тора соединен с информационным входом первого триггера, выход которого соединен с входом установки в 1 второго триггера, информационный вход второго триггера соединен с шиной 5 нулевого потенциала устройства, выход первого элемента И соединен с тактовым входом второго триггера, инверсный выход которого соединен с первым входом обращения первого блока 0 оперативной памяти, входом обращения блока постоянной памяти, i: орыми входами пятого и восьмого дешифраторов и первым входом признака готовности устройства, прямой выход вто- 5 рого триггера соединен с первым входом второго элемента И и четвертым входом седьмого дешифратора, первый выход пятого дешифратора соединен с входом записи третьего блока опера- g тинной памяти и управляющим входом первого мультиплексора, группа выходов которого соединена с группой адресных входов третьего блока оперативной памяти, второй выход пятого 5 дешифратора соединен с входом чтения третьего блока оперативной памяти, выход которого соединен с третьим входом восьмого дешифрагора и вторым входом обращения nepiun o блока оперативной пг1мяти, старшин разряд информационного выхода блока постоянной памяти соединен с информационным входом третьего блока оперативной памяти, выход которого соединен с четвертым входом шестого дешифратора и вторым входом второго элемента И, Вход признака готовности устройства соединен с третьим входом второго элемента И, выход которого соединен с вторым выходом признака готовности устройства, вторая группа выходов шестого дешифратора соединена с третьей группой входов шестого дешиф ратора и является третьей группой информационных входов-выходов устройства, третья группа выходов шестого дешифратора является группой адресны выходов устройства, первый, второй, третий, четвертый, пятый, шестой и седьмой выходы шестого дешифратора являются соответственно первыми выходами признака чтения, признака записи, строба адреса устройства, вто- рым выходом признака сброса устройства, первым и вторым выходами признака задания режима устройства, выходо признака выборки команды устройства, выход генератора тактовых импульсов соединен с Входом второго.элемента И, вход признака выборки команды устройства соединен с пятым входом шестого дешифратора, первый вход признака задания режима устройства соеди ней с шестым входом шестого дешифратора, второй вход признака задания режима устройства соединен с седьмым Входом шестого дешифратора, вход строба адреса устройства соединен с восьмым входом шестого дешифратора, первый, второй, третий, четвертый и пятый выхо/4ы седьмого д/гшифратора соединены соответственно с входом установки в О первого счетчика импульсов, счетным входом первого счетчика импульсов, счетным входом . второго счетчика импульсов, входом установки в О второго счетчика импульсов и первым входом обращения второго блока оперативной памяти, второй выход седьмого дешифратора соединен с вторым входом обращения второго блока оперативной памяти и входом девятого дешифратора, выходы переполнения первого и второго счетчиков импульсов соединены соответственно с пятым и шестым входами мого дешифратора, группы информащгонных выходов первог о и второт о счетчиков импульсов соединены соответственно с группой управляюших входов второго мультиплексора и группой адресных входов второго блока оперативной памяти, первая, вторая, третья и четвертая группы выходов второго блока оперативной памяти соединены соответственно с первой, второй, третьей и четвертой группами информационных входов второго мультиплексора, группа выходов которого соединена с группой входов девятого дешифратора, выход генератора тактовых импульсов соединен с седьмым входом седьмого дешифратора, первый вход признака задания режима устройства соединен с входом третьего элемента НЕ, вьсход которого соединен с первыми входами третьего элемента И и десятого дешифратора, второй вход признака задания режима устройства соединен с вторым входом третьего элемента И, выход генератора тактовых импульсов соединен с третьим входом третьего элемента И, выход которого соединен с входами установки в 1 третьего, четвертого и пятого триггеров, вход признака выборки команды устройства через первый элемент задержки соединен с тактовым входом шестого триггера, информационный вход шестого триггера соединен с шиной нулевого потенциала устройства, выход второго элемента НЕ соединен с входом установки в 1 шестого триггера и тактовыми входами третьего, четвертого и пятого триггеров, младший разряд второй группы адресных входов устройства соединен с информационным входом седьмого триггера, вход строба адреса устройства соединен с тактовым входом седьмого триггера, первый, второй и третий выходы десятого дешифратора соединены соответственно с Т-входами третьего, четвертого и пятого триггеров, прямой и инверсный выходы седьмого и шестого триггеров соединены соответственно с вторым, третьим, чет- вертым и пятым входами десятого дешифратора, прямые Выходы третьего и четвертого триггеров соединены соответственно с шестым и седьмым рхода- ми десятого дешифратора, инверсные выходы третьего, четвертого и пятого триггеров соединены соответственно с восьмым, девятым и десятым входами десятого дешифратора, отличаюЩ е е с я тем, что, с целью повышения производительности, устройство дополнительно содержит четвертый и пятый элементы НЕ, четвертый элемент И, второй и третий элементы задержки восьмой, девятый и десятый триггеры и группу триггеров, причем первый вход признака задания режима устройства соединен с первым входом четвер того элемента И, второй вход п ризна- ка задания режима устройства соединен с входом четвертого элемента НЕ, выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с информационным входом десятого триггера, выход генератора тактовых импульсов через третий элемент задержки соединен с Входом второго элемента задержки и тактовым входом десятого триггера, выход которого соединен с тактовым входом триггеров группы, выход второго элемента задержки соединен с инверсным тактовым входом восьмого триггера, вход признака выборки команды устройства через четвертый элемент НК соединен с входом установки в 1 восьмого триггера, Т-вход которого подключен к шине нулевого по- тендиала устройства, К-вход восьмого триггера соединен с шиной единичного потенциала устройства, а выход восьмого триггера соединен с входом установки в 1 девятого триггера и входами установки в О триггеров группы, инверсный выходы третьего, четвертого и пятого триггеров соединены с соответствующими информационными входами триггеров группы, выходы которых соединены соответственно с первым, вторым и третьим информационными входами второго блока оперативной памяти, инверсный выход девятого триггера соединен с четвертьм информационным входом второго блока оперативной памяти, информационный вход девятого триггера соединен с шиной нулевого потенциала устройства, выход третьего элемента И соединен с тактовым входом девятого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для отладки программно-аппаратных блоков | 1988 |

|

SU1529228A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

Изобретение относится к вычислительной технике и может найти применение для отладки аппаратно программных средств микропроцессоров. Устройство содержит генератор импульсов, десять дешифраторов, три элемента задержки, четыре регистра, десять триггеров,одновибратор, блок постоянной памяти, три блока оперативной памяти, два счетчика, два мультиплексора, пять элементов НЕ, четыре элемента И, схему сравнения, группу триггеров. Устройство позволяет фиксировать глубину очереди команд и проводить благодаря этому расшифровку трассировочной информации на программном уровне. В результате можно сократить объем блока памяти, необходимый для запоминания информации о выполнении программы, повысить производительность отладки. 4 ил.

| Микропроцессоры | |||

| Системы программирования и отладки | |||

| /Под ред | |||

| В.А.Мясникова и др | |||

| М.: Энергоатом- издат, 1985 | |||

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-30—Публикация

1987-07-20—Подача