1

Изобретение .oтнocитqя к вычислительной и информационно-измерительной технике и может быть использовано при построении информационно-изме-j рительных систем, в которых требуется организовать обмен информацией между устройствами, работающими с р 1зной скоростью, например, измерительным устройством, передающим нерегулярно Q массивы данных, и ЦВМ.

Известны устройства для сопряжения, содержащие буферный запс шнающий блок, дешифратор, маркерный регистр, триг-.с гер, два элемента задержки, два вентиля, элемент ИЛИ-НЕ, формирователь. V Устройства осуществляют одновременно запись информации в одну ячейку буферного запоминающего блока и 2о считывание из друго.й ячейки. Эти ячейки выделяются дешифратором 1.

Недостатками таких устройств являются большое количество,связей при коммутации входных и выходных инфор- 25 мационных шин устройства с запоминающими ячейками, сложность управлякнцей схемы устройства и большие аппаратурные затраты на нее, неоднородность в структуре устройства.Известно также устройство для сопряжения, содержащее память на Мразрядных сдвиговых регистрах и узел синхронизадии, входыкоторого являются соответственно входом тактовых импульсов и входом чтения информации устройства, выходы М-го разряда сдвиговых регистров памяти являются информационными выходами устройства 2.

Недостатком этого устройства является его сложность.

Целью изобретения, является упрощение конструкции устройства.

Поставленная цель достигается тем, что в устройство введены дополнительный М-разрядный сдвиговый регистр, М-элементов И и М элементов ИМПЛИКАЦИЯ, причем первые разряды сдвиговых регистров памяти являются информационными входами устройства, первый разряд дополнительного.сдвигового регистра является входом признака наличия информации, йходы сдвига i-го разряда сдвиговых регистров Пс1мяти и дополнительного сдвигового регистра подключены к выходу i-ro элемента И, первый вход которого соединен с входом тактовых импульсов

устройства, а второй вход - с прямым входом -i - 1-го элемента ИМПЛИКАЦИЯ выходом 1-го элемента ИМПЛИКАЦИЯ, инверсный вход которого соединен с выходом i-ro разряда дополнительного сдвигового регистра, прямой вход элемент& ИМПЛИКАЦИЯ м-го разряда соединен с выходом узла синхронизации, выход М-горазряда дополнительного сдвигового регистра является выходом готовности устройства, выход переполнения которого соединен с выходом первого элемента ИМПЛИКАЦИЯ.

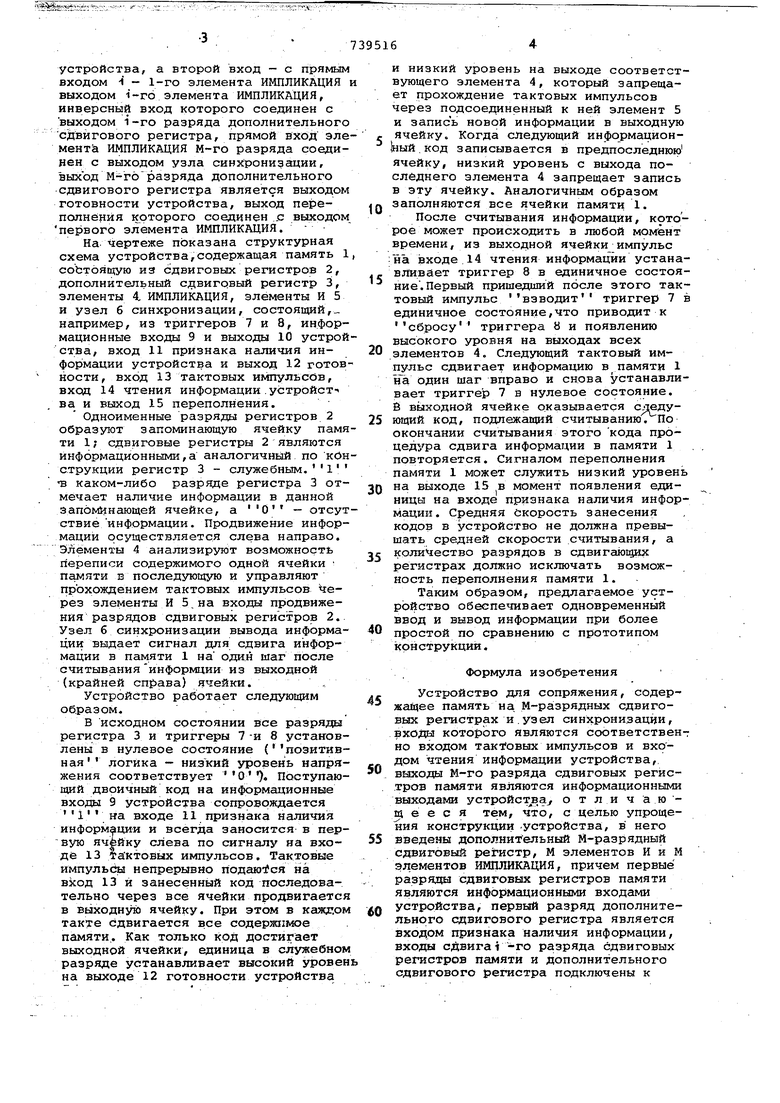

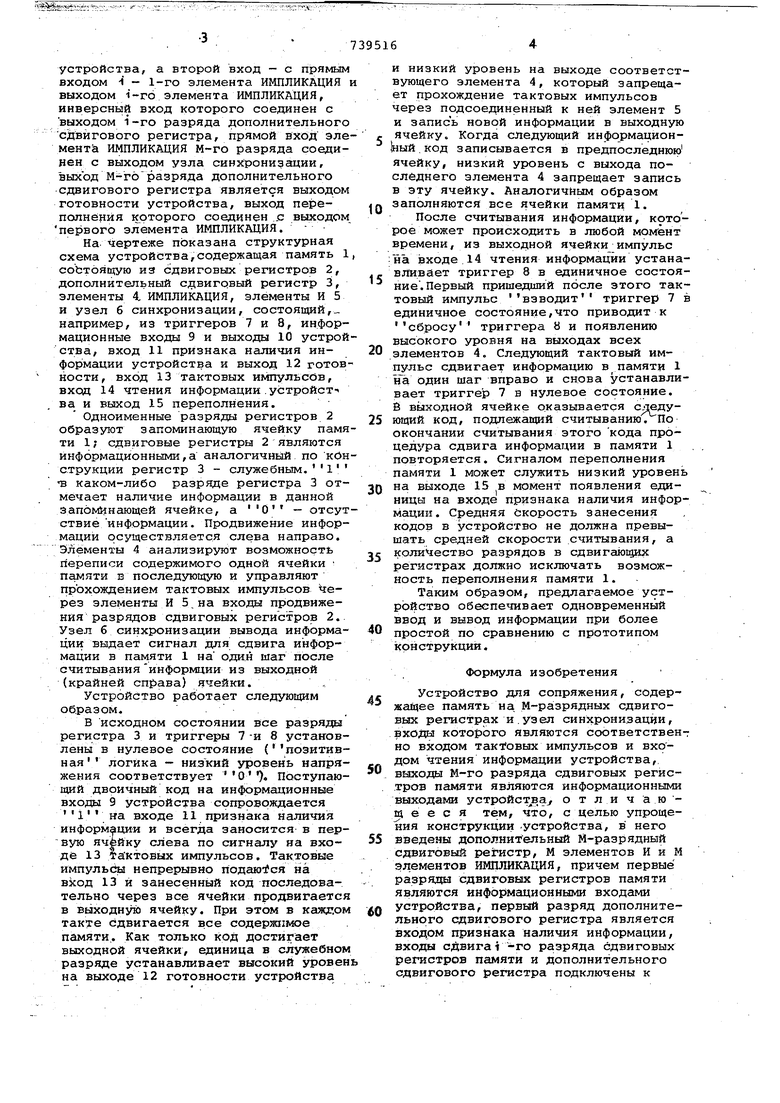

На чертеже показана структурная схема устройства,содержащая память 1 соЪтоящую из сдвиговых регистров 2, дополнительный сдвиговый регистр 3, элементы 4. ИМПЛИКАЦИЯ, элементы И 5 и узел б синхронизации, состоящий, например, из триггеров 7 и 8, информационные входы 9 и выходы 10 устройства, вход 11 признака наличия инфор мации устройства и выход 12 готовности, вход 13 тактовых импульсов, вхся 14 чтения информации . устройства и выход 15 переполнения.

Одноименные разряды регистров 2 образуют запоминающую ячейку памяти 1; сдвиговые регистры 2 являются информационными,а аналогичный по конструкции регистр 3 служебным.Ч -в каком-либо разряде регистра 3 отмечает наличие информации в данной запоминающей ячейке, а О - отсутствие информации. Продвижение информации осуществляется слева направо. Элементы 4 анализируют возможность переписи содержимого одной ячейки памяти в последующую и управляют прохождением тактовых импульсов через элементы И 5.на входы продвижения разрядов сдвиговых регистров 2. Узел б синхронизации вывода информации выдает сигнал для сдвига информации в памяти 1 на один шаг после считыванияинформции из выходной (крайней справа) ячейки. ,

Устройство работает следующим образом.

В исходном состоянии все разряды регистра 3 и триггеры 7-и 8 установлены в нулевое состояние (позитивная логика - низкий уровень напряжения соответствует О). Поступающий двоичный код на информационные входы 9 устройства сопровождается 1 на входе 11 признака наличия информации и всегда заносится- в первую ячейку слева по сигналу на входе 13 тактовых импульсов. Тактовые импульйы непрерывно подаются на вkoд 13 и занесенный код последовательно через все ячейки продвигается в выходную ячейку. При этом в каждом такте сдвигается все содержимое памяти. Как только код достигает выходной ячейки, единица в служебном разряде устанавливает высокий уровен на выходе 12 готовности устройства

и низкий уровень на выходе соответствующего элемента 4, который запрещает прохождение тактовых импульсов через подсоединенный к ней элемент 5 и запись новой информации в выходную , ячейку. Когда следующий информацион ный , код записывается в предпоследнюю ячейку, низкий уровень с выхода последнего элемента 4 запрещает запись в эту ячейку. Аналогичным образом

Q заполняются все ячейки памяти 1.

После считывания информации, К9торое может происходить в любой момент времени, из выходной ячейки импульс :на входе 14 чтения информации устанавливает триггер 8 в единичное состояние. Первый пришедший после этого тактовый импульс взводит триггер 7 в единичное состояние,что приводит к сбросу триггера в и появлению высокого уровня на выходах всех

0 элементов 4. Следующий тактовый импульс сдвигает информацию в памяти 1 а один шаг вправо и снова устанавливает триггер 7 в нулевое состояние. S выкодной ячейке оказывается сдеду5 ющий код, подлежащий считыванию. По окончании считывания этого кода процедура сдвига информации в памяти 1 повторяется. Сигналом переполнения памяти 1 может служить низкий уровень

Q на выходе 15 в момент появления единицы на входе признака наличия информации. Средняя Скорость занесения кодов в устройство не должна превышать средней скорости считывания, а

с количество разрядов в сдвигающих регистрах должно исключать возможность переполнения памяти 1.

Таким образом, предлагаемое устройство обеспечивает одновременный ввод и вывод информации при более

0 простой по сравнению с прототипом конструкции.

Формула изобретения

Устройство для сопряжения, содержащее память на. М-разрядных сдвиговых регистрах и.узел синхронизации, входы которого являются соответственно входом тактовых импульсов и входом чтения информации устройства,,

выходы М-го разряда сдвиговых регистров памяти являются информационными выходами устройст в.а о т ли ч а ю щ е е с я тем, что, с целью упрощения конструкции .устройства, в него

введены дополнительный М-разрядный сдвиговый регистр, М элементов И и М

элементов ИМПЛИКАЦИЯ, причем первые разряды сдвиговых регистров памяти являются информационными входами

устройства, первый разряд дополнительного сдвигового регистра является входом признака наличия информации, входы сдвига i -го разряда сдвиговых регистров памяти и дополнительного сдвигового регистра подключены к

вшсоду ч-го элемента И, первый вход которого соединен с входом тактовых импульсов устройства, а второй входс прямымвходом 1- 1-го элемента ИМПЛИКАЦИЯ и выходом -i-го элемента ИМПЛИКАЦИЯ, инверсный вход которого соединен с выходом i-го разряда дополнительного сдвигового регистра, прямой вход элемента ИМПЛИКАЦИЯ М-го разряда соединен с выходом узла синхройизации, выход м-го разряда дополt t-t-.t-tt- t-ff

нительного сдвигового регистра является выходом готовности устройтсва, выход переполнения которого соединен с выходом первого элемента ИМПЛИКАЦИЯ,

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 488202, кл. G Об F 3/04, 1973.

2.Авторское свидетельство СССР 401999, кл. G 06 F 13/02, 1971 (прототип).

j Sr-HfwU.nvrt ijieii.-svvAfrbfe. ,iiii.-;:; Wi-i2i G 4

/tf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1983 |

|

SU1124276A1 |

| Устройство для сопряжения | 1979 |

|

SU966685A2 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Буферное устройство для передачи данных | 1987 |

|

SU1418725A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Фотоэлектрическое считывающее устройство | 1988 |

|

SU1674181A1 |

| Ячейка однородной структуры | 1990 |

|

SU1789977A1 |

| Многоканальное устройство для обработки первичной информации | 1984 |

|

SU1234851A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

Авторы

Даты

1980-06-05—Публикация

1977-12-26—Подача