(5) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ УЗЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Генератор псевдослучайных последовательностей | 1983 |

|

SU1127079A1 |

| Генератор псевдослучайных последовательностей | 1987 |

|

SU1443141A1 |

| Устройство для контроля генератора М-последовательностей | 1985 |

|

SU1278850A1 |

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Генератор двоичной последовательности | 1990 |

|

SU1709505A1 |

случайные коды могут вызвать неопределенность поведения контролируемого логического блока из-за критических состояний фронтов входных сигналов ло гического блока, возникающих вследст- s

вие одновременного изменения состояний на нескольких емходах генератора псевдослучайных кодов. При этом выходные реакции контролируемого логического блока на заданный псевдослучайный тест оказываются неопределенными, что приводит к невозможности достоверного контроля правильности функционирования этого блока.

Цель изобретения - повышение достоверности контроля логических узлов.

Поставленная цель достигается тем, что в устройство для контроля логических узлов, содержащее блок формирования контрольного числа, генератор 20 .псевдослучайных последовательностей, блок управления, причем первый выход блока управления соединен с синхровхо дом блока формирования контрольного, числа, информационные входы которого соединены соответственно с контактами проверяемого узла, второй выход блока управления соединен с управляющим вхо дом генератора псевдослучайных последовательностей, вход запуска блока уп равления является входом запуска устройства, введен блок сравнения, блок приоритетов, регистр, причем входы проверяемого узла соединены соответст венно с первой группой входов блока сравнения, с выходами регистра, управ ляющий вход которого соединен с треть им выходом блока управления, первый выход первой группы выходов поразрядного сравнения блока сравнения соединен с первым информационным входом регистра, информационные входы с второго по п-й (где п - число входов проверяемого -узла) регистра соединены со ответственно с выходами блока приоритетов, выходы с второго по п-й первой группы выходов поразрядного сравнения блока сравнения соединены соответственно с первой группой входов блока приоритетов,-вторая группа входов которого соединена соответственна с вы ходами с первого по (п-1)-й второй группы выходов поразрядного сравнения блока сравнения, выход общего сравнения которого соединен с тактовым входом блока управления, выходы генера- 5S го

тора псевдослучайных последовательностей соединены соответственно с второй группой входов блока сравнения.

При этом блок сравнения содержит п сумматоров по модулю два, элемент И, выход которого является выходом общего сравнения блока, первый выход

сравнения которого соединен с прямым выходом первого сумматора по модулю два, прямые выходы сумматоров по модулю два с второго по п-й являются

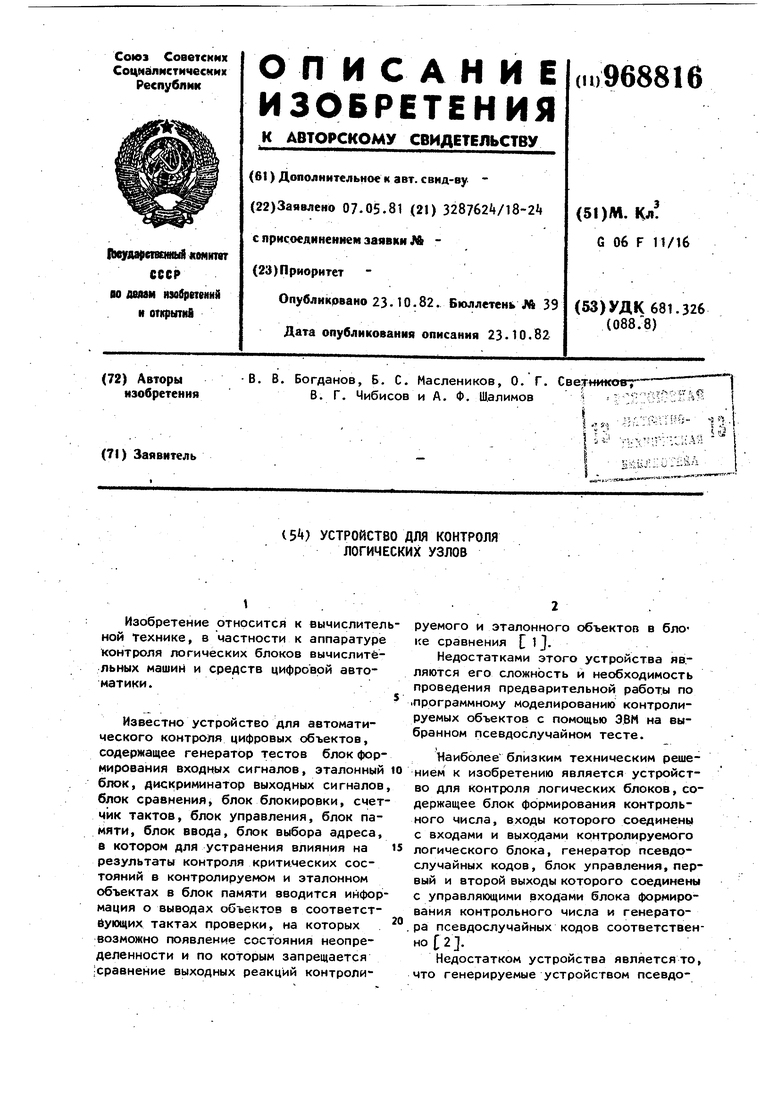

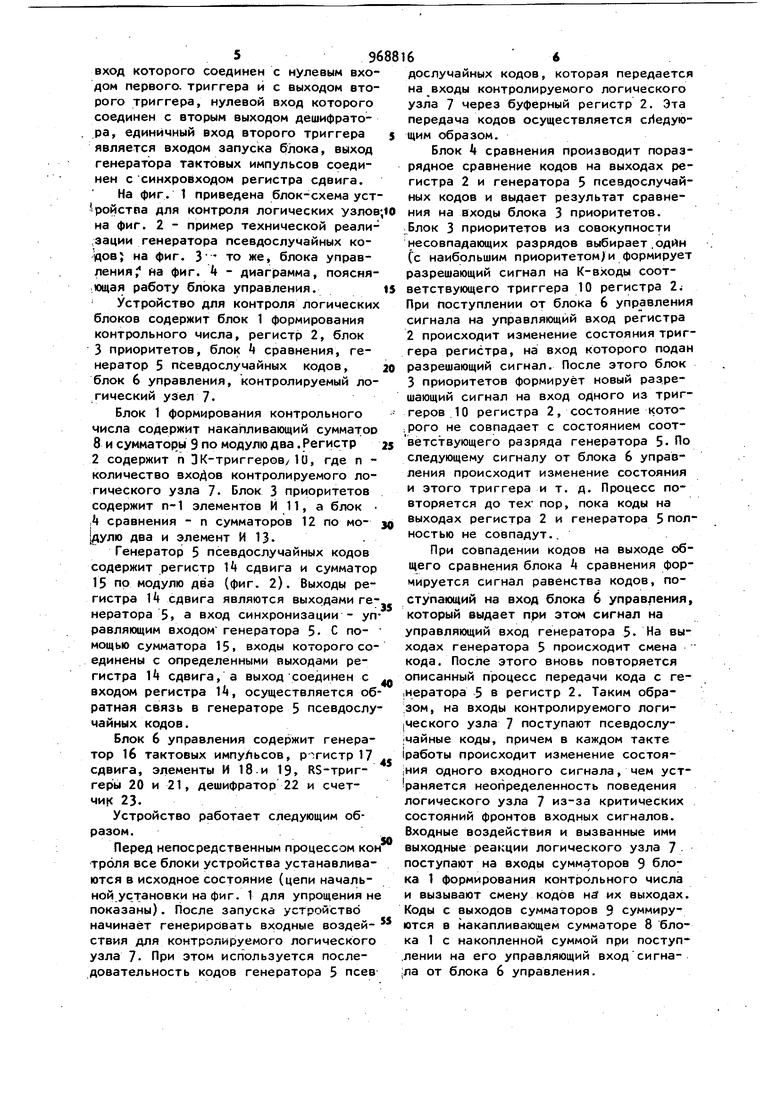

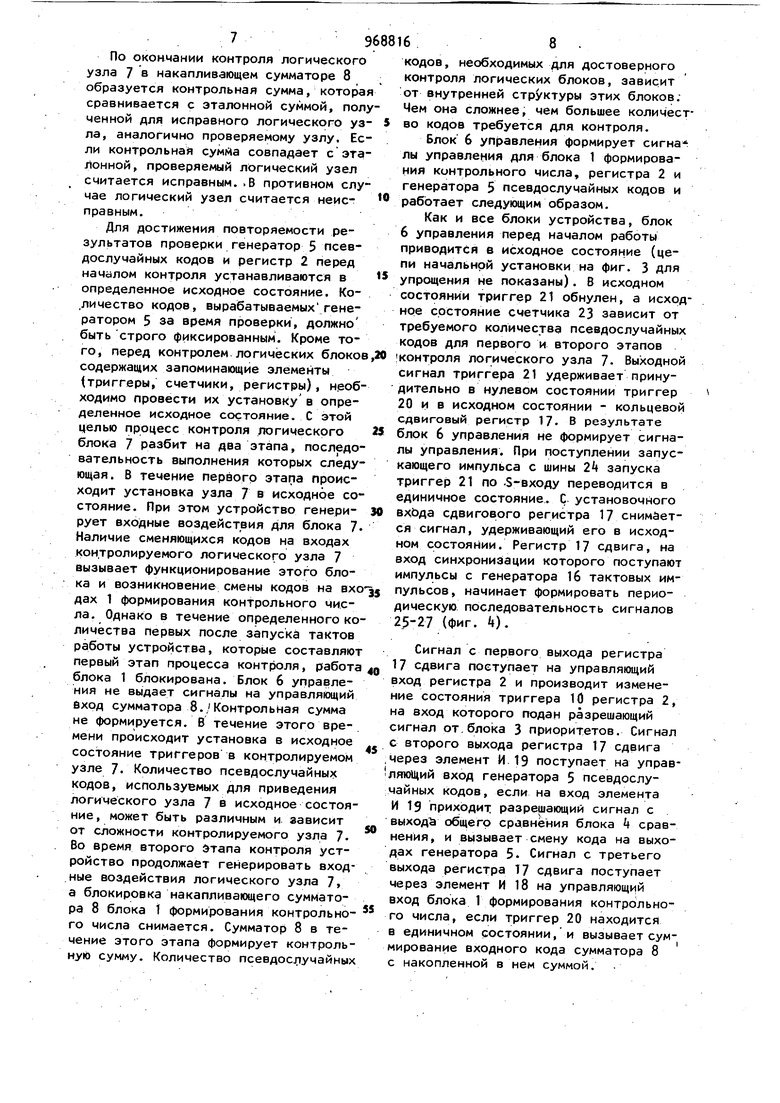

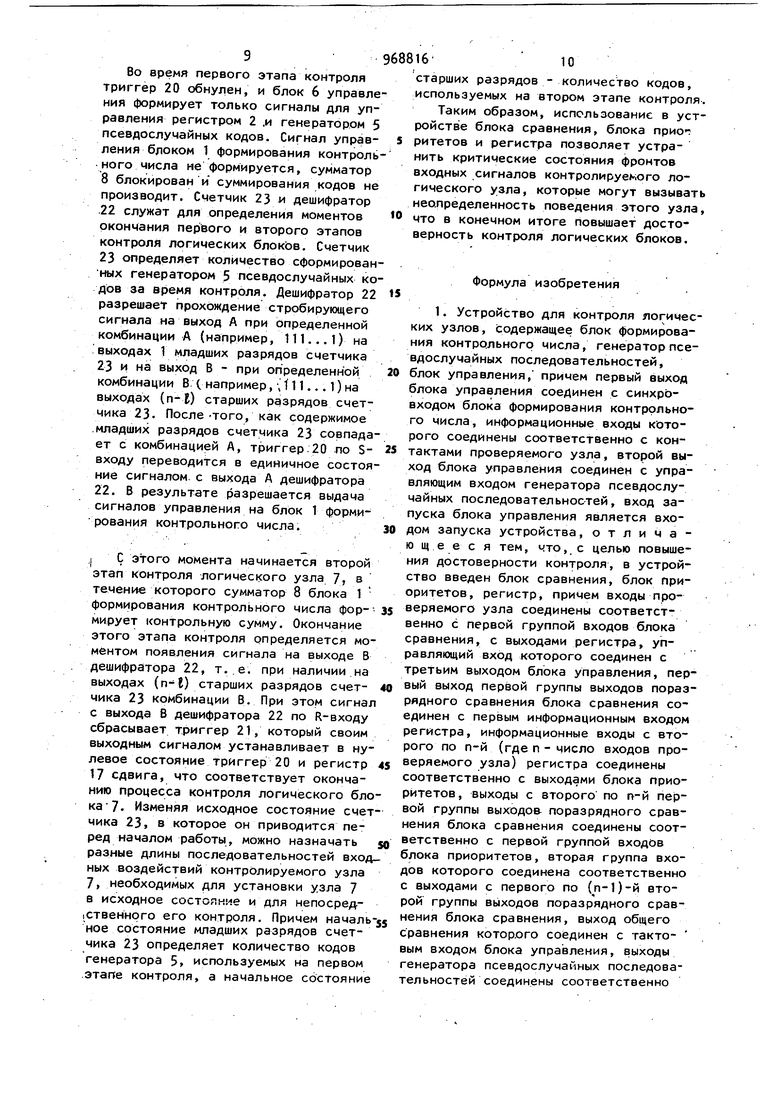

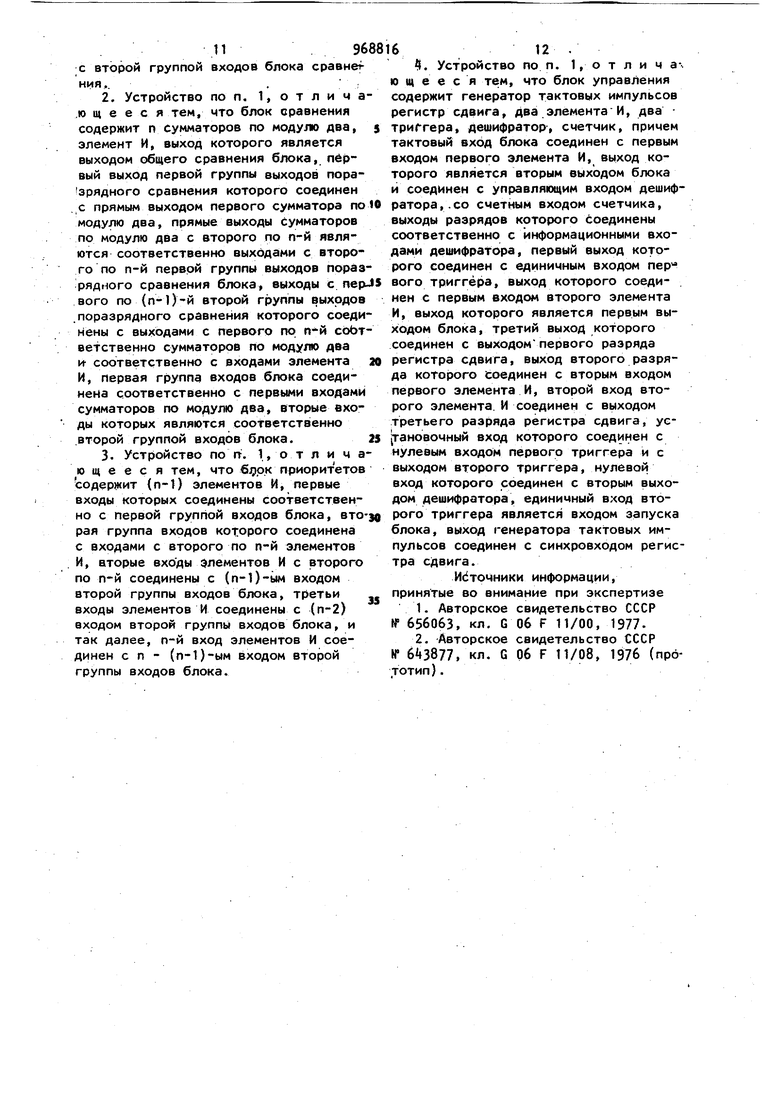

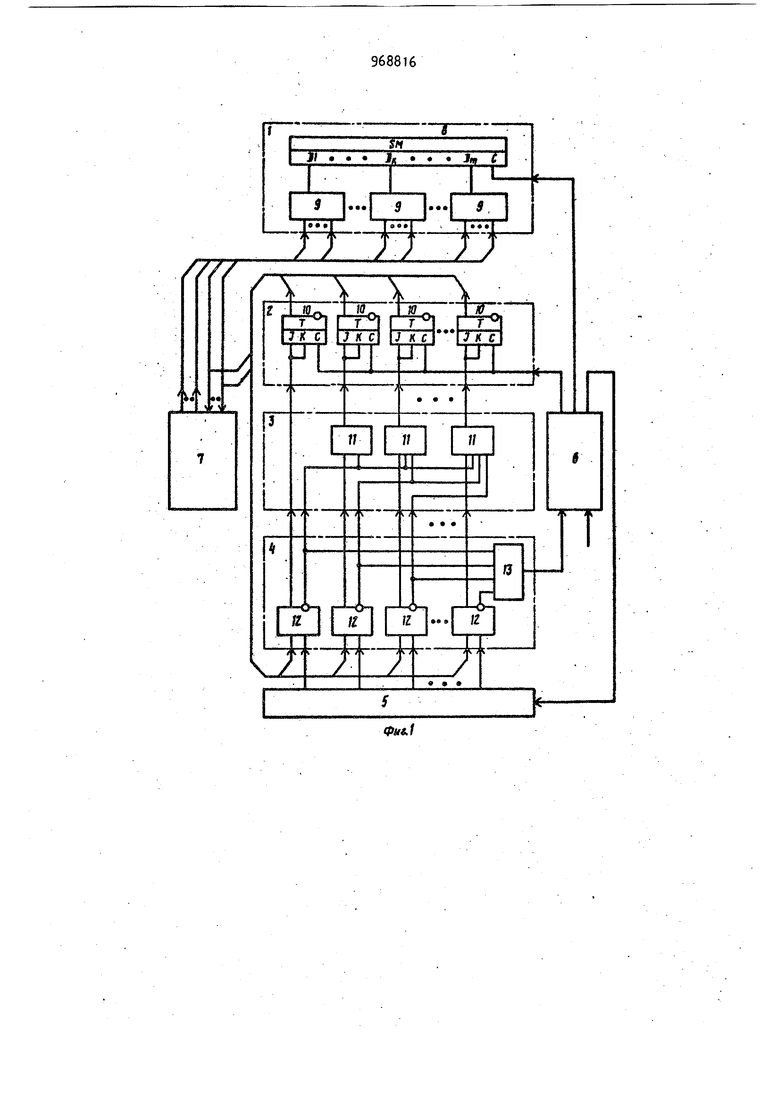

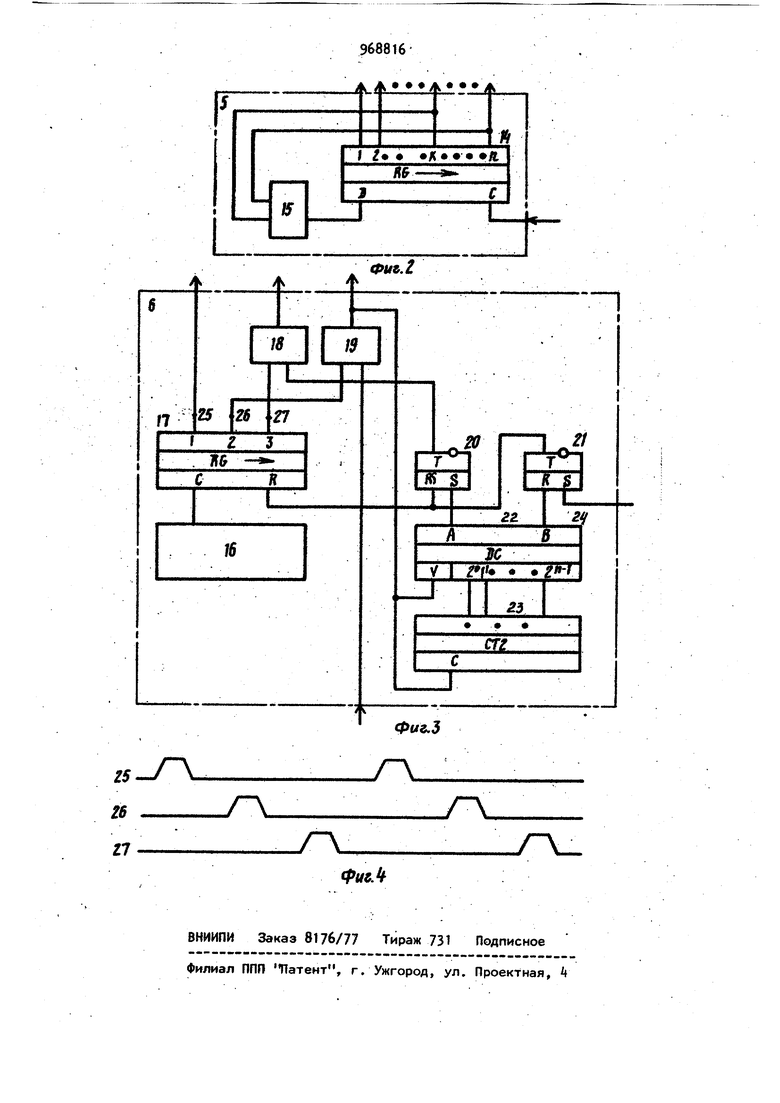

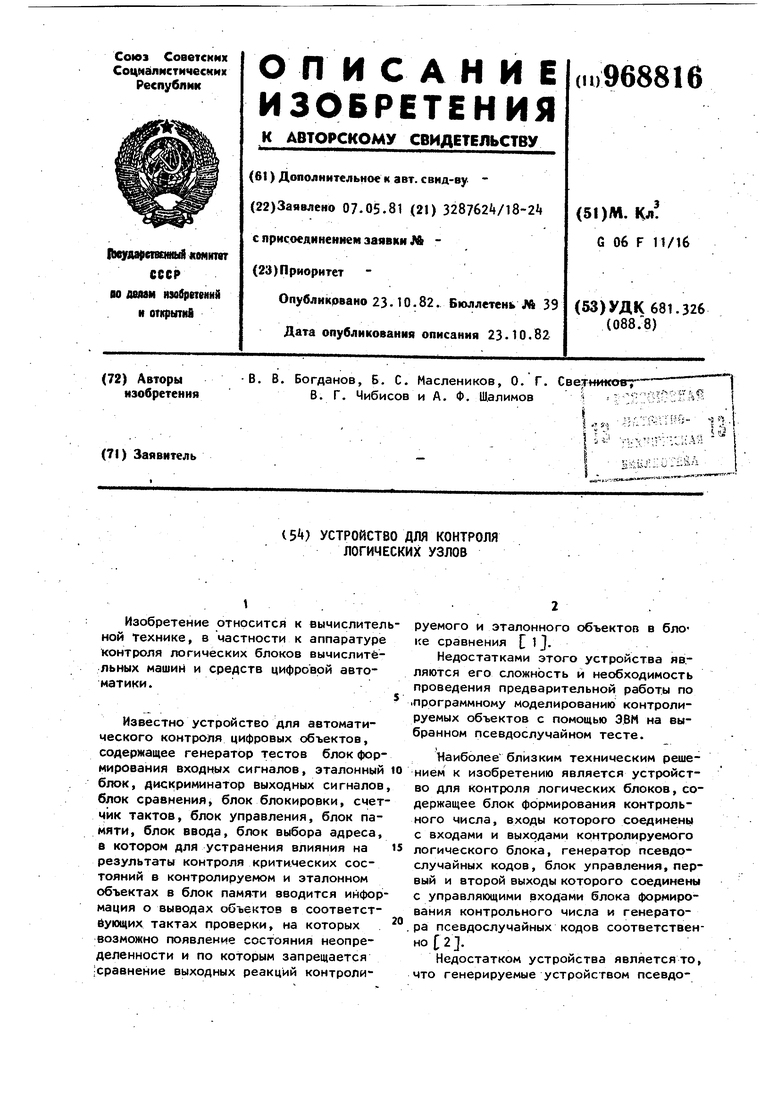

соответственно выходами с второго по п-й первой группы, выходов поразрядного сравнения блока, выходы с первого по (п-1)-й второй группы выходов поразрядного сравнения которого соедииены с выходами с первого по п-й соответственно сумматоров по модулю два и соответственно с входами элемента И, первая группа входов блока соединена соответственно с первыми входами элемента И, второй вход второго элемента И соединен с выходом третьего разряда регистра сдвига, установочный первой группы выходов поразрядного сумматоров по модулю два, вторые входы которых являются соответственно второй группой входов блока. Кроме того, блок приоритетов содержит (n-l) элементов И, первые входы которых соединены соответственно с первой группой входов блока, вторая группа входов которого соединена с входами с второго по п-й элементов И, вторые входы элементов И с второго по п-й соединены с (п-1)-ым входом второй группы входов блока, третьи входы элементов И.соединены с (п-2) входом второй группы входов блока, и так далее, п-й вход элементов И соединен СП- (п-1)-ым входом второй группы входов блока. Блок управления содержит генератор тактовых импульсов, регистр сдвига, два элемента И, два триггера, дешифратор, счетчик, причем тактовый вход блока соединен с первым входом первого элемента И, выход которого является вторым выходом блока и соединен с управляющим входом дешифратора, со счетным входом счетчика, выходы разрядов которого соединены соответственно с информационными входами де(Шифратора, первый выход которого соединен с единичным входом первого триггера, выход которого соединен с первым входом второго элемента И, выход которого является первым выходом блока, третий выход которого соединен с выходом первого разряда регистра сдвига, выход второго разряда которосоединен с вторым входом первого 596 вход которого соединен с нулевым входом первого, триггера и с выходом второго триггера, нулевой вход которого соединен с вторым выходом дешифратора, единичный вход второго триггера является входом запуска блока, выход генератора тактовых импульсов соединен с синхровходом регистра сдвига. На фиг. 1 приведена блок-схема устфоистпа для контроля логических узлов на фиг. 2 - пример технической реали.зации генератора псевдослучайных кодов} на фиг. З- то же, блока управления на фиг. k - диаграмма, поясняющая работу блока управления. Устройство для контроля логических блоков содержит блок 1 формирования контрольного числа, регистр 2, блок 3 приоритетов, блок i сравнения, генератор 5 псевдослучайных кодов, блок 6 управления, контролируемый логический узел 7. Блок 1 формирования контрольного числа содержит накапливающий сумматор 8 и сумматоры 9 по модулю два. Регистр 2 содержит п ЗК-триггеров/10, где п количество вхоДов контролируемого логического узла 7. Блок 3 приоритетов содержит п-1 элементов И 11, а блок Л сравнения - п сумматоров 12 по мо|дулю два и элемент И 13. Генератор 5 псевдослучайных кодов содержит регистр Т сдвига и сумматор 15 по модулю два (фиг. 2). Выходы регистра Ц сдвига являются выходами генератора 5, а вход синхронизации - уп равляющим входом генератора 5. С помощью сумматора 151 входы которого соединены с определенными выходами регистра 14 сдвига, а выход соединен с входом регистра 1А, осуществляется об ратная связь в генераторе 5 псевдослу чайных кодов. Блок 6 управления содержит генератор 16 тактовых импуЛьсов, р- гистр 17 сдвига, элементы И 18 и 19, RS-триггер ы 20 и 21, дешифратор 22 и счетчик 23. Устройство работает следующим образом. Перед непосредственным процессом ко троля все блоки устройства устанавливаются в исходное состояние (цепи начальной установки на фиг. 1 для упрощения н показаны). После запуска устройство начинает генерировать входные воздействия для контролируемого логического узла 7. При этом используется последовательность кодов генератора 5 псев 6 дослучайных кодов, которая передается на входы контролируемого логического узла 7 через буферный регистр 2. Эта передача кодов осуществляется с;1едующим образом. Блок k сравнения производит поразрядное сравнение кодов на выходах регистра 2 и генератора 5 псевдослучайных кодов и выдает результат сраанения на входы блока 3 приоритетов. ;Блок 3 приоритетов из совокупности несовпадающих разрядов выбирает.один (с наибольшим приоритетом/и формирует разрешающий сигнал на К-входы соответствующего триггера 10 регистра 2; При поступлении от блока 6 упр авления сигнала на управляющий вход регистра 2происходит изменение состояния триггера регистра, на вход которого подан разрешающий сигнал. После этого блок 3приоритетов формирует новый разрешающий сигнал на вход одного из триггеров 10 регистра 2, состояние кото;рого не совпадает с состоянием соответствующего разряда генератора S- По следующему сигналу от блока 6 управления происходит изменение состояния и этого триггера и т. д. Процесс повторяется до тех пор, пока коды на выходах регистра 2 и генератора 5 полностью не совпадут.. При совпадении кодов на выходе общего сравнения блока 4 сравнения формируется сигнал равенства кодов, поступающий на вход блока 6 управления, который выдает при этом сигнал на управляющий вход генератора 5- На выходах генератора 5 происходит смена кода. После этого вновь повторяется описанный процесс передачи кода с ге Нератора 5 в регистр 2. Таким обра;зом, на входы контролируемого логи Ческого узла 7 поступают псевдослу чайные коды, причем в каждом такте (работы происходит изменение состоя|ния одного входного сигнала, чем уст раняется неопределенность поведения логического узла 7 из-за критических состояний фронтов входных сигналов. Входные воздействия и вызванные ими выходные реакции логического узла 7 поступают на входы сумматоров 9 блока 1 формирования контрольного числа и вызывают смену кодов НсГ их выходах. Коды с выходов сумматоров 9 суммируются в накапливающем сумматоре 8 блока 1 с накопленной суммой при поступ.лении на его управляющий вход сигна;ла от блока 6 управления. По окончании контроля логического узла 7 в накапливающем сумматоре 8 образуется контрольная сумма, которая сравнивается с эталонной суммой, полу ченной для исправного логического узла, аналогично проверяемому узлу. Если контрольная сумма совпадает сэталонной, проверяемый логический узел считается исправным..В противном случае логический узел считается неисправным. Для достижения повторяемости результатов проверки генератор 5 псевдослучайных кодов и регистр 2 перед началом контроля устанавливаются в определенное исходное состояние. Ко.личество кодов, вырабатываемыхгенератором 5 за время проверки, должно быть строго Фиксированным. Кроме того, перед контролем логических блоков содержащих запоминающие элементы триггеры, счетчики, регистры), необходимо провести их установку в определенное исходное состояние. С этой целью процесс контроля логического блока 7 разбит на два этапа, последовательность выполнения которых следующая. В течение первого этапа происходит установка узла 7 в исходное состояние. При этом устройство генерирует входные воздействия для блока 7. Наличие сменяющихся кодов на входах контролируемого логического узла 7 вызывает функционирование этого блока и возникновение смены кодов на BXO дах 1 формирования контрольного числа. Однако в течение определенного количества первых после запуска тактов работы устройства, которые составляют первый этап процесса контроля, работа блока 1 блокирована. Блок 6 управления не выдает сигналы на управляющий вход сумматора В.,/Контрольная сумма не формируется. В течение этого времени происходит установка в исходное состояние триггеров в контролируемом узле 7. Количество псевдослучайных кодов, используемых для приведения логического узла 7 в исходное состояние, может быть различным и зависит от сложности контролируемого узла 7. Во время второго дтапа контроля устройство продолжает генерировать входные воздействия логического узла 7, а блокировка накапливающего сумматора 8 блока i формирования контрольного числа снимается. Сумматор 8 в течение этого этапа формирует контрольную сумму. Количество псевдослучайных 9 6 - 8 . кодов, необходимых для достоверного контроля логических блоков, зависит от внутренней структуры этих блоков; Чем она сложнее, чем большее количество кодов требуется для контроля. Блок 6 управления формирует сигна лы управления для блока 1 формирования контрольного числа, регистра 2 и генератора 5 псевдослучайных кодов и работает следующим образом. Как и все блоки устройства, блок 6 управления перед началом работы приводится в исходное состояние (цепи начальной установки на фиг. 3 Для упрощения не показаны). В исходном состоянии триггер 21 обнулен, а исходное состояние счетчика 23 зависит от требуемого количества псевдослучайных кодов для первого и второго этапов 1контроля логического узла 7. Выходной сигнал триггера 21 удерживает принудительно в нулевом состоянии триггер 20 и в исходном состоянии - кольцевой сдвиговый регистр 17. В результате блок 6 управления не формирует сигналы управления. При поступлении запускающего импульса с шины 2k запуска триггер 21 по -З-входу переводится в единичное состояние. С установочного вхЬда сдвигового регистра 17 снимается сигнал, удерживающий его в исходном состоянии. Регистр 17 сдвига, на вход синхронизации которого поступают импульсы с генератора 16 тактовых импульсов, начинает формировать периодическую последовательность сигналов (фиг. if). Сигнал с первого выхода регистра сдвига поступает на управляющий вход регистра 2 и производит изменение состояния триггера 10 регистра 2, на вход которого подан разрешающий сигнал от,блока 3 приоритетов. Сигнал с второго выхода регистра 17 сдвига через элемент И.19 поступает на управляю1Дий вход генератора 5 псевдослучайных кодов, если на вход элемента И 19 приходит; разрешающий сигнал с выхода общего сравнения блока t сравнения, и вызывает смену кода на выходах генератора 5. Сигнал с третьего выхода регистра 17 сдвига поступает через элемент И 18 на управляющий вход блока 1 формирования контрольного числа, если триггер 20 находится в единичном состоянии, и вызывает суммирование входного кода сумматора 8 с накопленной в нем суммой. .

Во время первого этапа контроля триггер 20 обнулен, и блок 6 управления формирует только сигналы для управления регистром 2 .и генератором 5 псевдослучайных кодов. Сигнал управления блоком 1 формирования контрольного числа не формируется, сумматор 8 блокирован и суммирования кодов не производит. Счетчик 23 и дешифратор

22служат для определения моментов окончания первого и второго этапов контроля логических блоков. Счетчик

23определяет количество сформированных генератором 5 псевдослучайных кодов за время контроля. Дешифратор 22 разрешает прохождение стробирующего сигнала на выход А при определенной комбинации А {например, П1...1) на выходах 1 младших разрядов счетчика

23 и на выход В - при определенной комбинации В (например,t11...1)на выходах (п-1) старших разрядов счетчика 23. После-того, как содержимое .младших разрядов счетчика 23 совпадает с комбинацией А, триггер.20 по Sвходу переводится в единичное состояние сигналом с выхода А дешифратора 22. В результате разрешается выдача сигналов управления на блок 1 формирования контрольного числа.

С этого момента начинается второй этап контроля логического узла 7, в течение которого сумматор 8 блока 1 формирования контрольного числа формирует контрольную сумму. Окончание этого этапа контроля определяется моментом появления сигнала на выходе В дешифратора 22, т..е. при наличии на выходах (п-1) старших разрядов счетчика 23 комбинации В. При этом сигнал с выхода 8 дешифратора 22 по R-входу сбрасывает триггер 21, который своим выходным сигналом устанавливает в нулевое состояние триггер 20 и регистр 17 сдвига, что соответствует окончанию процесса контроля логического блока 7. Изменяя исходное состояние счетчика 23, в которое он приводится перед началом работы, можно назначать разные длины последовательностей входных воздействий контролируемого узла 7 необходимых для установки узла 7 в исходное состояние и для непосред.ственного его контроля. Причем началь ное состояние младших разрядов счетчика 23 определяет количество кодов генератора 5, используемых на первом .этапе контроля, а начальное состояние

старших разрядов - количество кодов, используемых на втором этапе контроля. Таким образом, использование в устройстве блока сравнения, блока приог ритетов и регистра позволяет устранить критические состояния фронтов входных сигналов контролируемого логического узла, которые могут вызывать неопределенность поведения этого узла, что в конечном итоге повышает достоверность контроля логических блоков.

Формула изобретения

ji

J

TTjJ

fn 3m С

-ГП

/777

iLEr ЛЗТ

.J

t

У

J

h

On

и

и

A ; с

А

) I «Д «ft

tftut.t

Авторы

Даты

1982-10-23—Публикация

1981-05-07—Подача