Изобретение относится к вычислительной технике и может быть использовано для формирования тестовых воздействий при контроле функционирования и диагностирований неисправностей цифровых узлов автоматики и вычислительной техники.

Цель изобретения - повышение быстродействия устройства.

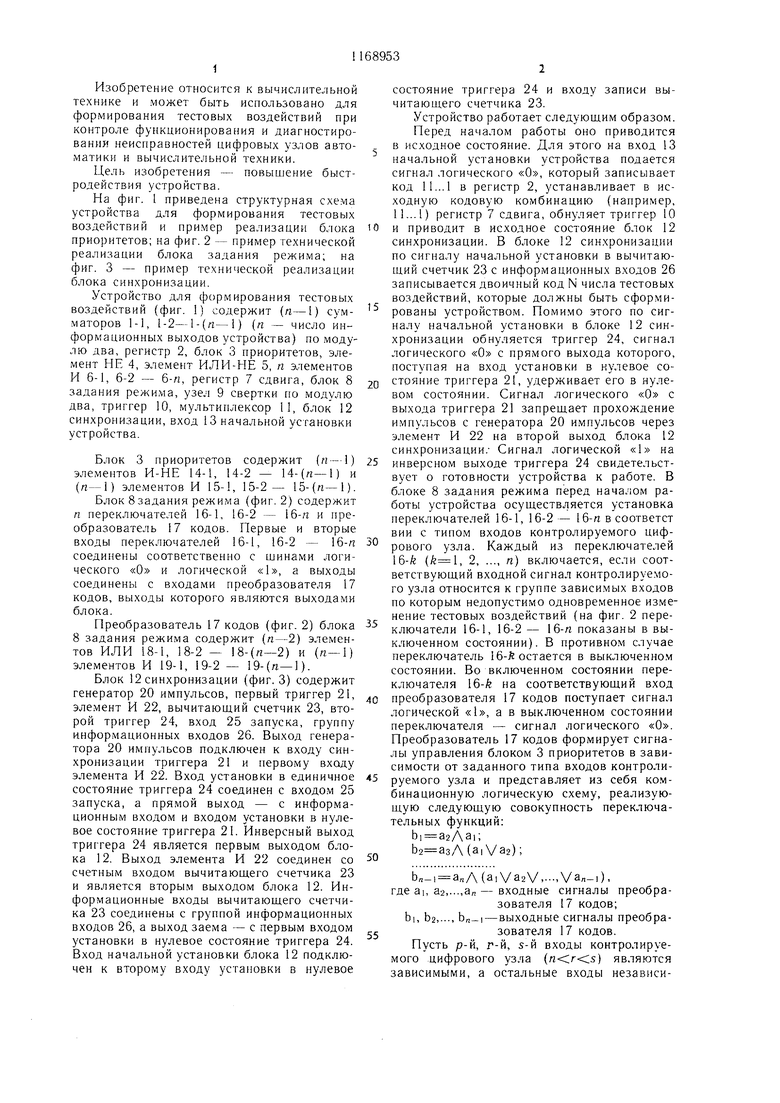

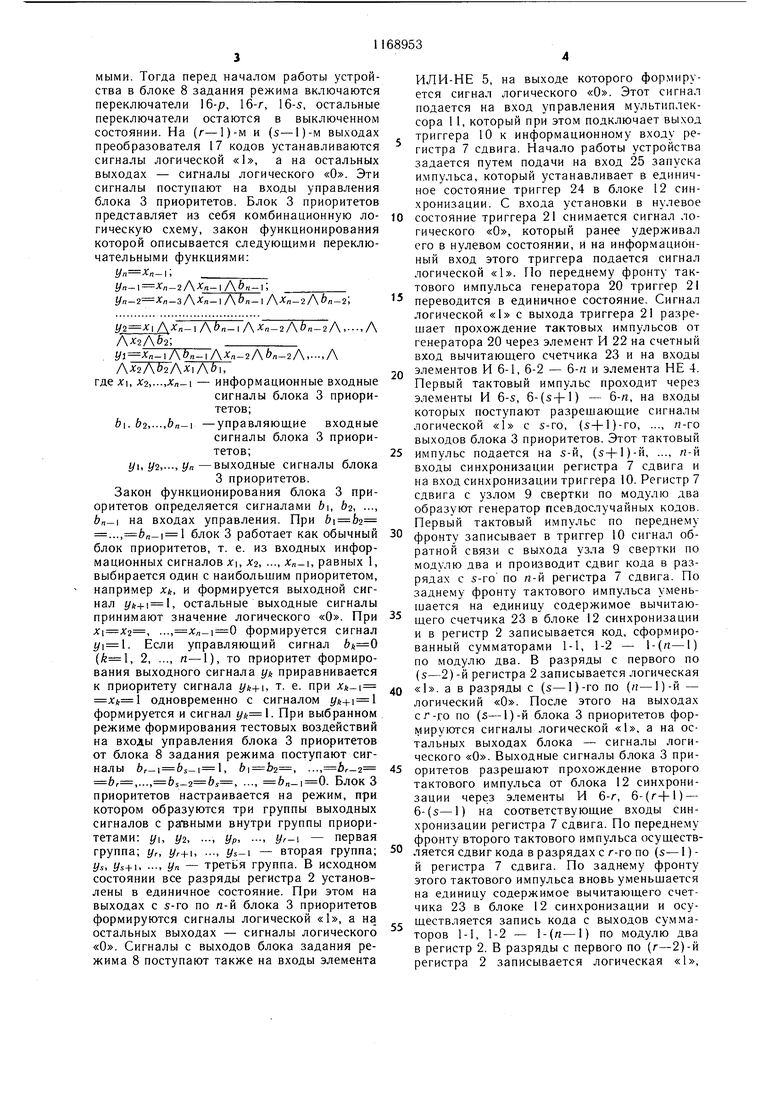

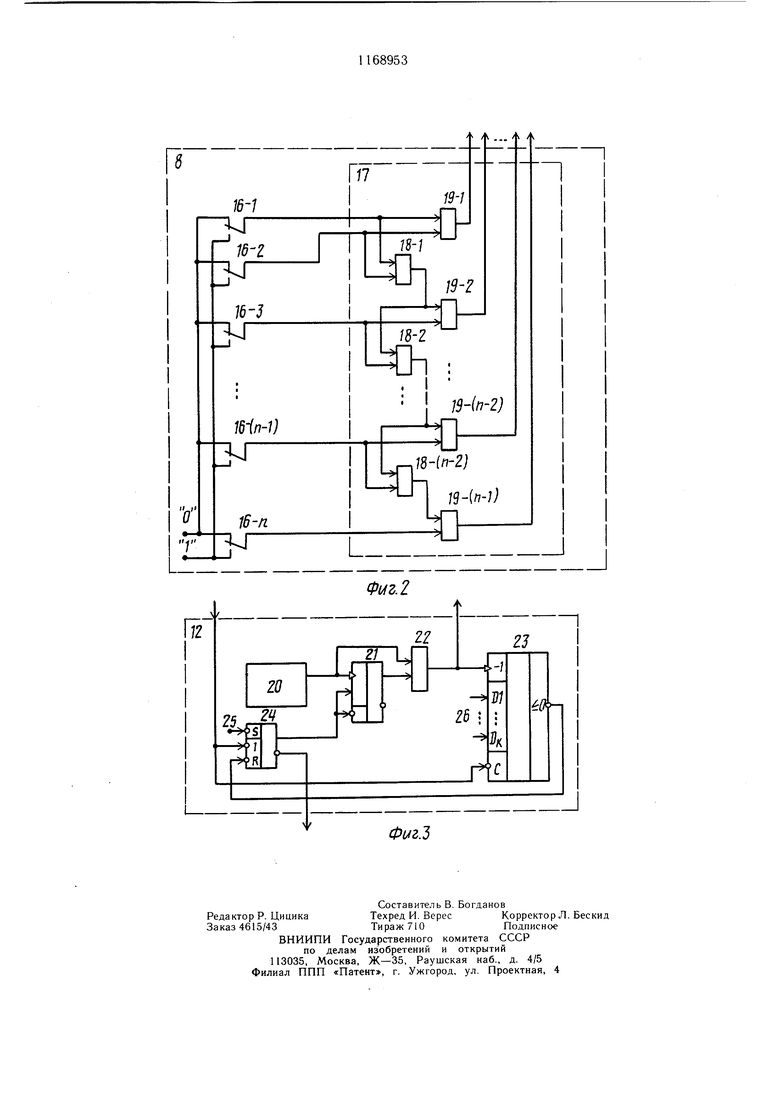

На фиг. 1 приведена структурная схема устройства для формирования тестовых воздействий и пример реализации блока приоритетов; на фиг. 2 - пример технической реализации блока задания режима; на фиг. 3 - пример технической реализации блока синхронизации.

Устройство для формирования тестовых воздействий (фиг. 1) содержит (п-1) сумматоров 1-1, 1-2-1-(л-1) (п - число информационных выходов устройства) по модулю два, регистр 2, блок 3 приоритетов, элемент НЕ 4, элемент ИЛИ-НЕ 5, п элементов И 6-1, 6-2 - 6-п, регистр 7 сдвига, блок 8 задания режима, узел 9 свертки по модулю два, триггер 10, мультиплексор 11, блок 12 синхронизации, вход 13 начальной установки устройства.

Блок 3 приоритетов содержит («--1) элементов И-НЕ 14-1, 14-2 - 14-() и (л-1) элементов И 15-1, 15-2- 15-(п-1).

Блок 8задания режи.ма (фиг. 2) содержит п переключателей 16-1, 16-2 - &-п и преобразователь 17 кодов. Нервые и вторые входы переключателей 16-1, 16-2 - 16-п соединены соответственно с шинами логического «О и логической «1, а выходы соединены с входами преобразователя 17 кодов, выходы которого являются выходами блока.

Преобразователь 17 кодов (фиг. 2) блока 8 задания режима содержит (п-2) элементов ИЛИ 18-1, 18-2 - 18-(«-2) и (и-1) элементов И 19-1, 19-2 - 19-(п-1).

Блок 12 синхронизации (фиг. 3) содержит генератор 20 импульсов, первый триггер 21, эле.мент И 22, вычитающий счетчик 23, второй триггер 24, вход 25 запуска, группу информационных входов 26. Выход генератора 20 импульсов подключен к входу синхронизации триггера 21 и первому входу элемента И 22. Вход установки в единичное состояние триггера 24 соединен с входо.м 25 запуска, а прямой выход - с информационным входом и входом установки в нулевое состояние триггера 21. Инверсный выход триггера 24 является первым выходом блока 12. Выход элемента И 22 соединен со счетным входом вычитающего счетчика 23 и является вторым выходом блока 12. Информационные входы вычитающего счетчика 23 соединены с группой информационных входов 26, а выход заема - с первым входом установки в нулевое состояние триггера 24. Вход начальной установки блока 12 подключен к второму входу установки в нулевое

состояние триггера 24 и входу записи вычитающего счетчика 23.

Устройство работает следующим образом. Перед началом работы оно приводится в исходное состояние. Для этого на вход 13 начальной установки устройства подается сигнал логического «О, который записывает код 11... 1 в регистр 2, устанавливает в исходную кодовую комбинацию (например, 11...1) регистр 7 сдвига, обнуляет триггер 10

0 и приводит в исходное состояние блок 12 синхронизации. В блоке 12 синхронизации по сигналу начальной установки в вычитающий счетчик 23 с информационных входов 26 записывается двоичный код N числа тестовых воздействий, которые должны быть сформированы устройством. Помимо этого по сигналу начальной установки в блоке 12 синхронизации обнуляется триггер 24, сигнал логического «О с прямого выхода которого, поступая на вход установки в нулевое состояние триггера 21, удерживает его в нулевом состоянии. Сигнал логического «О с выхода триггера 21 запрещает прохождение импульсов с генератора 20 импульсов через элемент И 22 на второй выход блока 12 синхронизации.- Сигнал v oгичecкoй «1 на

5 инверсном выходе триггера 24 свидетельствует о готовности устройства к работе. В блоке 8 задания режима перед началом работы устройства осуществляется установка переключателей 16-1, 16-2 - 16-п в соответст ВИИ с типом входов контролируемого цифрового узла. Каждый из переключателей 16-fe (k, 2, ..., п) включается, если соответствующий входной сигнал контролируе.мого узла относится к группе зависимых входов по которым недопустимо одновременное изменение тестовых воздействий (на фиг. 2 переключатели 16-1, 16-2 - 16-п показаны в выключенном состоянии). В противном случае переключатель 16-А остается в выключенном состоянии. Во включенном состоянии переключателя Q-k на соответствующий вход

0 преобразователя 17 кодов поступает сигнал логической «1, а в выключенном состоянии переключателя - сигнал логического «О. Преобразователь 17 кодов формирует сигналы управления блоком 3 приоритетов в зависимости от заданного типа входов контроли5 руемого узла и представляет из себя ко.мбинационную логическую схему, реализующую следующую совокупность переключательных функций: bi a2Aai;

0 (aiVa2);

a,,A(aiVa2V,---.Va«-i), где ai, а2,...,а„-входные сигналы преобразователя 17 кодов;

bi, bg,..., bn i-выходные сигналы преобразователя 17 кодов.

Пусть р-н, г-й, 5-й входы контролируемого цифрового узла () являются зависимыми, а остальные входы независимыми. Тогда перед началом работы устройства в блоке 8 задания режима включаются переключатели 16-р, 16-г, 16-5, остальные переключатели остаются в выключенном состоянии. На (г-1)-м и (s-1)-м выходах преобразователя 17 кодов устанавливаются сигналы логической «1, а на остальных выходах - сигналы логического «О. Эти сигналы поступают на входы управления блока 3 приоритетов. Блок 3 приоритетов представляет из себя комбинационную логическую схему, закон функционирования которой описывается следующими переключательными функциями:

y„- Xn-2/ Xn- / bn-i;

.з/ Хп- / bn-i/ Хп-2/ 1)п-2;

J TTI/XO A , - - -, л

Л 2ЛЙ2;

1/ Ь„- / х„-2/ Ь„-2/,...,Л ,

гдех:, хч,...,Хп- - информационные входные сигналы блока 3 приоритетов;

Ь. Ь2,---,Ь„- -управляющие входные сигналы блока 3 приоритетов;УЬ У2,..., г/„-выходные сигналы блока

3 приоритетов.

Закон функционирования блока 3 приоритетов определяется сигналами Ь, Ь, ..., &„ на входах управления. При bi b2 ..., блок 3 работает как обычный блок приоритетов, т. е. из входных информационных сигналов х, Х2, ..., Хп-, равных 1, выбирается один с наибольшим приоритетом, например х, и формируется выходной сигнал y/t+i l, остальные выходные сигналы принимают значение логического «О. При , ..., формируется сигнал (. Если управляющий сигнал (1, 2, ..., п-1), то приоритет формирования выходного сигнала г/ приравнивается к приоритету сигнала , т. е. при Xk-i одновременно с сигналом yk+i формируется и сигнал (/. При выбранном режиме формирования тестовых воздействий на входы управления блока 3 приоритетов от блока 8 задания режима поступают сигналы 6г-1 , , ...,Ьг-2

6r,...,fts-2 &s, ..., . Блок 3 приоритетов настраивается на режим, при котором образуются три группы выходных сигналов с равными внутри группы приоритетами: /1, г/2, .-., Ур, --., УГ- - первая группа; у, Уг+, , /s-i - вторая группа; t/i, 1/S+1, .... Уп - третья группа. В исходном состоянии все разряды регистра 2 установлены в единичное состояние. При этом на выходах с s-ro по п-й блока 3 приоритетов формируются сигналы логической «1, а на остальных выходах - сигналы логического «О. Сигналы с выходов блока задания режима 8 поступают также на входы элемента

ИЛИ-НЕ 5, на выходе которого формируется сигнал логического «О. Этот сигнал подается на вход управления мультиплексора 1 1, который при этом подключает выход триггера 10 к информационному входу регистра 7 сдвига. Начало работы устройства задается путем подачи на вход 25 запуска импульса, который устанавливает в единичное состояние триггер 24 в блоке 12 синхронизации. С входа установки в нулевое

0 состояние триггера 21 снимается сигнал логического «О, который ранее удерживал его в нулевом состоянии, и на информационный вход этого триггера подается сигнал логической «1. По переднему фронту тактового импульса генератора 20 триггер 21

переводится в единичное состояние. Сигнал логической «1 с выхода триггера 21 разрешает прохождение тактовых импульсов от генератора 20 через элемент И 22 на счетный вход вычитающего счетчика 23 и на входы

Q элементов И 6-1, 6-2 - 6-п и элемента НЕ 4. Первый тактовый импульс проходит через элементы И 6-s, 6-(s+l) - 6-n, на входы которых поступают разрешающие сигналы логической «1 с s-ro, (s+l)-ro, ..., п-го выходов блока 3 приоритетов. Этот тактовый

5 импульс подается на s-й, (5+1)-й, ..., п-И входы синхронизации регистра 7 сдвига и на вход синхронизации триггера 10. Регистр 7 сдвига с узлом 9 свертки по модулю два образуют генератор псевдослучайных кодов. Первый тактовый импульс по переднему

0 фронту записывает в триггер 10 сигнал обратной связи с выхода узла 9 свертки по модулю два и производит сдвиг кода в разрядах с .s-ro по п-й регистра 7 сдвига. По заднему фронту тактового импульса уменьшается на единицу содержимое вычитающего счетчика 23 в блоке 12 синхронизации и в регистр 2 записывается код, сформированный сумматорами 1-1, 1-2 - -(п-I) по модулю два. В разряды с первого по (s-2) -и регистра 2 записывается логическая

0 «1. а в разряды с (s-1)-го по (п-1)-й - логический «О. После этого на выходах с г-го по (s-1)-и блока 3 приоритетов формирукзтся сигналы логической «1, а на остальных выходах блока - сигналы логического «О. Выходные сигналы блока 3 приоритетов разрешают прохождение второго тактового импульса от блока 12 синхронизации через элементы И 6-г, 6-(/+1) - 6-(s-1) на соответствующие входы синхронизации регистра 7 сдвига. По переднему фронту второго тактового импульса осуществляется сдвиг кода в разрядах с г-го по (s- 1) и регистра 7 сдвига. По заднему фронту этого тактового импульса вновь уменьшается на единицу содержимое вычитающего счетчика 23 в блоке 12 синхронизации и осус ществляется запись кода с выходов сумматоров 1-1, 1-2 - 1-(п-1) по модулю два в регистр 2. В разряды с первого по (г-2)-и регистра 2 записывается логическая «1,

а в разряды с (г-1)-го по (п-1)-й - логический «О. На выходах с первого по (г-1)-й блок 3 приоритетов устанавливаются сигналы логической «1, а на остальных выходах - сигналы логического «О. При этом по переднему фронту третьего тактового импульса от блока 12 синхронизации в регистре 7 сдвига производится сдвиг кода в разрядах с первого по (г- 1) -и. По заднему фронту этого тактового импульса уменьшается на единицу содержимое вычитающего счетчика 23 в блоке 12 синхронизации, а во все разряды регистра 2 записывается логическая «1 с выходов сумматоров 1-1, .2-1-(й - 1) по модулю два. Таким образом за три такта работы (вместо + 1 тактов у известного устройства) на информационные выходы устройства передается один псевдослучайный код, причем состояния на/-м,г-м, J--M информационных выходах устройства изменяются поочередно. Далее процесс передачи псевдослучайных кодов на информационные выходы устройства повторяется аналоги чным образом. Формирование тестовых воздействий продолжается до тех пор, пока в блоке 12 синхронизации не станет равным нулю содержимое вычитающего счетчика 23. При этом на его выходе заема формируется импульс, который обнуляет триггер 24. Сигнал логического «О с выхода этого триггера устанавливает в нулевое состояние триггер 21 сигнал логического «О с прямого выхода которого запрещает прохождение тактовых импульсов от генератора 20 импульсов через элемент И 22. Сигнал логической «1 с инверсного выхода триггера 24 свидетельствует о том, что устройство закончило формирование заданного числа N тестовых воздействий. При тестировании комбинационных цифровых узлов, все входы которых являются независимыми, в блоке 8 задания режима переключатели 16-1, 16-2 - 16-п выключаются. На всех выходах блока 8 задания режима устанавливаются сигналы логического «О. При этом на выходе элемента ИЛИ-НЕ 5 формируется сигнал логической «1, который поступает на вход управления мультиплексора 1 1. Мультиплексор 1 1 подключает выход узла 9 свертки по модулю два к информационному входу регистра 7

0 сдвига. При работе устройства в этом режиме на всех выходах блока 3 приоритетов формируются сигналы логической «1. которые разрещают сдвиг кода одновременно во всех разрядах регистра 7 сдвига. Регистр 7 сдвига с узлом 9 свертки по модулю два

функционирует в этом случае как обычный генератор псевдослучайных кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Генератор псевдослучайных последовательностей | 1987 |

|

SU1443141A1 |

| Генератор псевдослучайных последовательностей | 1983 |

|

SU1127079A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU993444A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Устройство для контроля генератора М-последовательностей | 1985 |

|

SU1278850A1 |

1. УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕСТОВЫХ ВОЗДЕЙСТВИЙ, содержащее регистр, регистр сдвига, выходы которого являются информациоииыми выходами устройства, узел свертки по модулю два, входы которого соединены с группой выходов регистра сдвига, триггер, информационный вход которого соединен с выходом узла свертки по модулю два, и блок синхронизации, первый выход которого является выходом готовности устройства, а вход начальной установки соединен с входаминачальной установки регистра, регистра сдвига, триггера и с входом начальной установки устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок приоритетов, блок задания режима, элемент ИЛИ-НЕ, мультиплексор, (п-1) сумматоров по модулю два (где п- число информационных выходов устройства), п элементов И и элемент НЕ, причем разрядные выходы регистра соединены с соответствующими информационными входами блока приоритетов и первыми входами соответствующих сумматоров по модулю два, первый выход блока приоритетов соединен с первым входом первого элемента И и с вторыми входами сумматоров по модулю два с первого по (п-1)-й, выходы с второго по «-Й блока Я.-- т-,.-...,„ а. БЙБЛйа., приоритетов соединены соответственно с первыми входами с второго по п-к элементов И и с третьими входами сумматоров по модулю два с первого по (п-1)-й, выходы которых соединены с соответствующими информационными входами регистра, выходы блока задания режима соединены с управляющими входами блока приоритетов и входами элемента ИЛИ-НЕ, выход которого соединен с управляющим входом мультиплексора, первый и второй информационные входы мультиплексора соединены соответственно с выходом свертки по модулю два и выходом триггера, вход синхронизации которого соединен с выходом п-го элемента И, выход мультиплексора соединен с информационным входом регистра сдвига, входы синхронизации которого с первого по п-й соединены с выхо дами соответствующих п элементов И, второй (Л выход блока синхронизации соединен с вторыми входами п элементов И и входом элемента НЕ, выход которого соединен с входом синхронизации регистра. 2. Устройство по п. 1, отличающееся тем, что блок приоритетов содержит (п-I) элементов И-НЕ и (п-1) элементов И, причем выход каждого г-го элемента И-НЕ (i 1,2,... п-1) соединен с (п-/)-ми входами элемен05 тов И с первого по t-й, каждый/-и инфорсх со сд мационный вход блока (, 2, ..., п-2) соединен с первым входом /-го элемента И-НЕ и с (п-/)-м входом (/+1)-го элемента И, выходы элементов И с первого по (п-1)-й 00 являются выходами блока с первого по (п-1)-й, (п-1)-й информационный вход блока соединен с первым входом (п-1)-го элемента И-НЕ и с п-м выходом блока, управляющие входы которого соединены с вторыми входами элементов И-НЕ.

| Устройство для контроля логических блоков | 1979 |

|

SU792256A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования тестовых воздействий | 1980 |

|

SU911533A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-04-29—Подача