Изобретение относится к импульсной технике и может быть использовано для генерации двоичных последовательностей оперативно перестраиваемых по составу и очередности формирования составляющих их кодовых наборов в зависимости от нужд контроля (диагностики) цифровых объектов.

Известен генератор псевдослучайных чисел, содержащий последовательно соединенные генератор сйнхротактов, регистр сдвига и блок линейных обратных связей.

Недостатком известного устройства является невозможность с его помощью осуществлять целенаправленный синтез сложных составных двоичных последовательностей, обеспечивающих одновременно полноту тестирования цифровых объектов и селекцию и исключение запрещенных кодов, анализ генерируемых двоичных последовательностей.

Наиболее близким по технической сущности и достигаемому эффекту является устройство, содержащее последовательно связанные сумматор по модулю два и регистр сдвига, последовательно соединенные триггер и элемент И, выход которого соединен со входом управления сдвигами регистра сдвига, а также генератор сйнхротактов.

Недостатком этого технического решения является неизменная .для всех прове-ряемых объектов очередность следования двоичных кодов, что приводит к невозможности возбуждения некоторых последовательных (содержащих элементы памяти)

, цифровых объектов. Кроме того, известное техническое решение не позволяет осуществлять целенаправленный синтез тестовых

воздействий и анализ потока генерируемых двоичных кодов (определять число различных двоичных кодов генерации или длину пакета генерации, определять, содержится ли в пакете генерируемых кодов любой конкретный код и на каком такте он формируется, определять очередность следования кодов), что необходимо делать при синтезе тестов и оценка эффективности тестирования определенных цифровых объектов при нестандартн1 х ситуациях.

Указанные недостатки известных технических решений приводят к низкой эффективности контроля и диагностике цифровых объектов с использованием псевдослучайных кодов.

Целью изобретения является расширение функциональных возможностей генератора путем изменения структуры генерируемых последовательностей.

Поставленная цель достигается тем, что в генератор двоичной, последовательности, содержащий последовательно соединен ные сумматор по модулю два и п-разрядный регистр сдвига) последовательно соединенные триггер и элемент И. выход которого соединен с входом управления сдвигами регистра сдвигов, а также генератор синхротактрв, причем вход сумматора по модулю два соединен с шиной прстоянной логической единицы, введены регистр выдачи, группа элементов И, счетчик адреса, первый, второй, третий ичетвертый элементы задержки, группа элементов сравнения, ПЗУ, элемент сравнения, первый и второй элементы ИЛИ, второй и третий элементы И, счетчик пакета, элемент НЕ, формирователь одиночного импульса и адаптер.

За счет введенных указанных элементов в цепях обратных связей сдвигового регистра осуществляется оперативная перестройка генератора двоичной последовательности таким образом, что на выходе генератора образуются двоичные последовательности, отличающиеся друг от друга по составу и/или очередности следования Двоичных кодов,ЧТО обеспечивает управление ИЗ состава двоичной последовательности запрещенных кодов при сохранении Г1олноты тестирования объекта контроля, генерацию составных двоичных последовательностей для повышения полноты тестирования на нёскольки,х различных полиномах кодирования (многочленах обратныу (Связей) при автоматической перестройке генератора в. единой процедуре генерации.

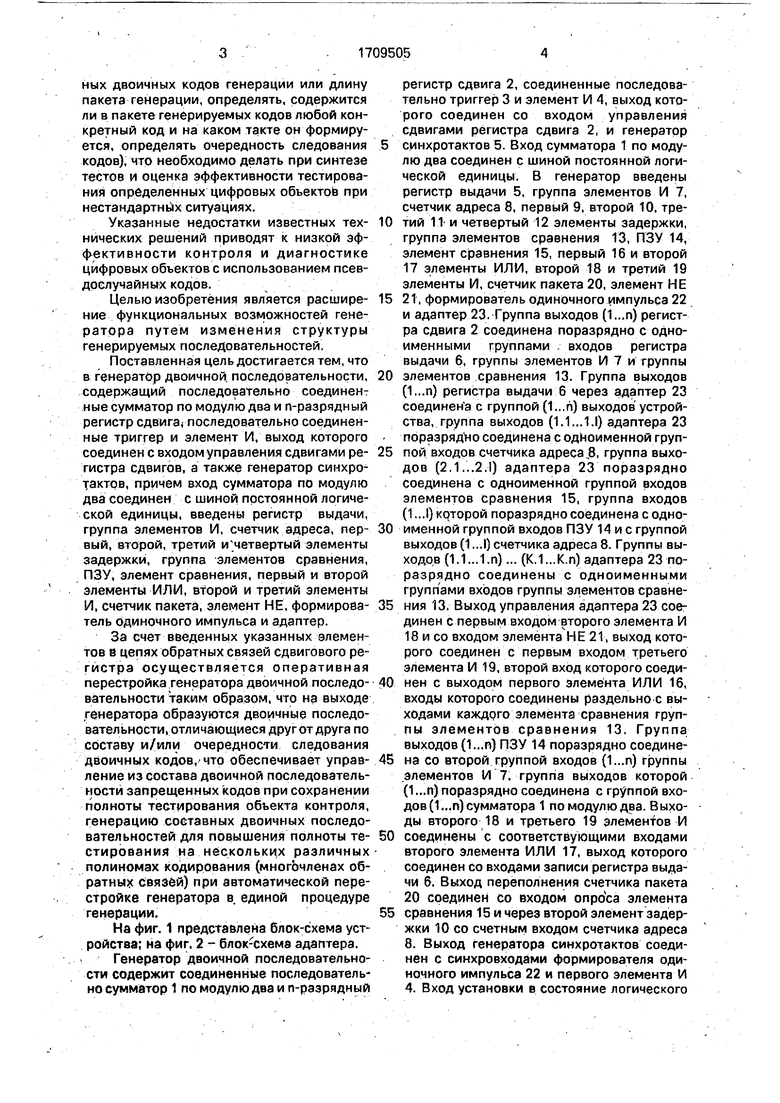

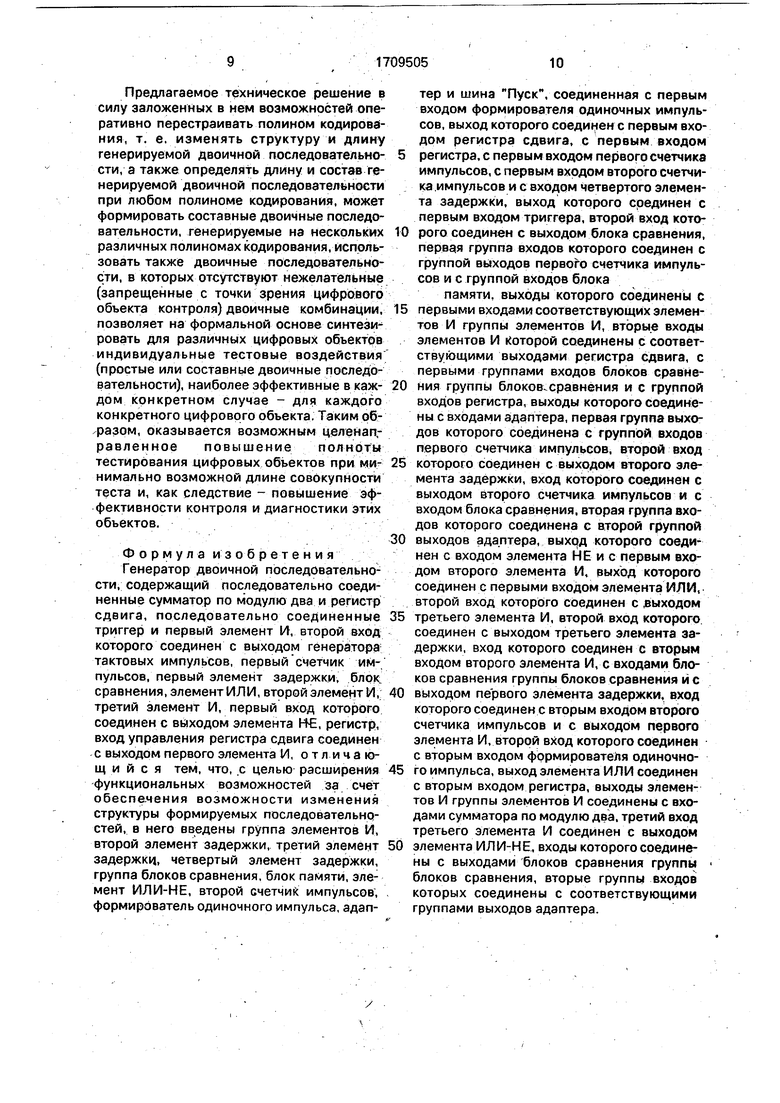

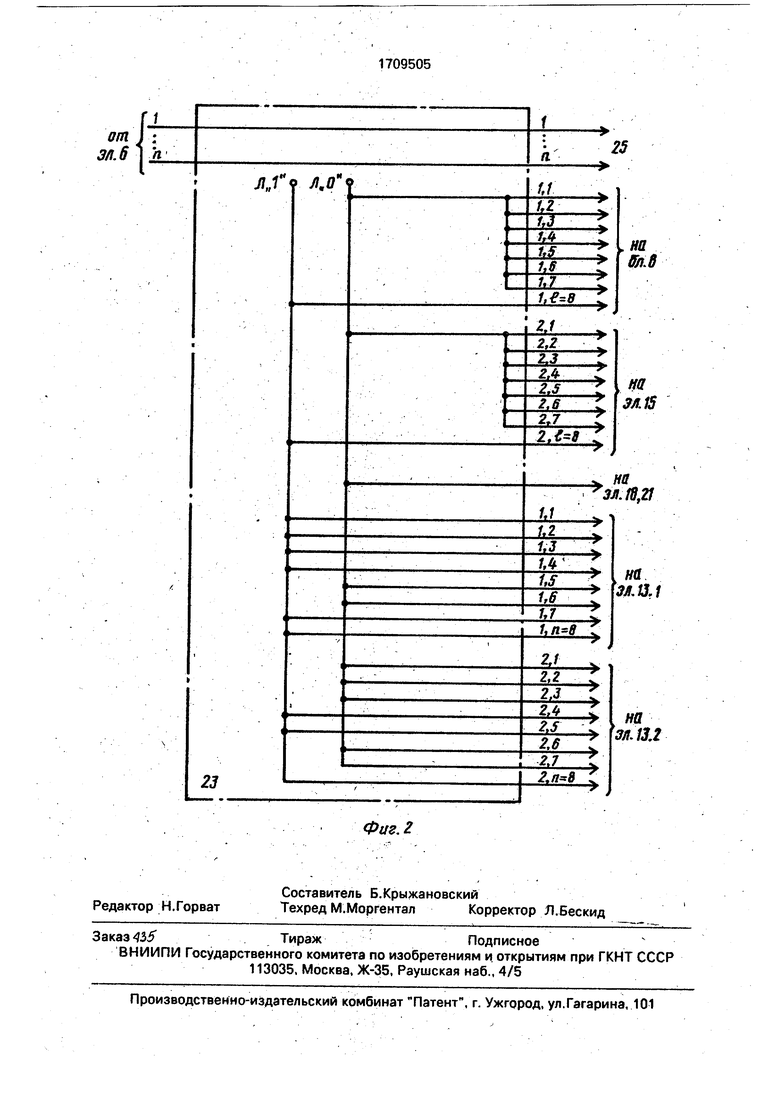

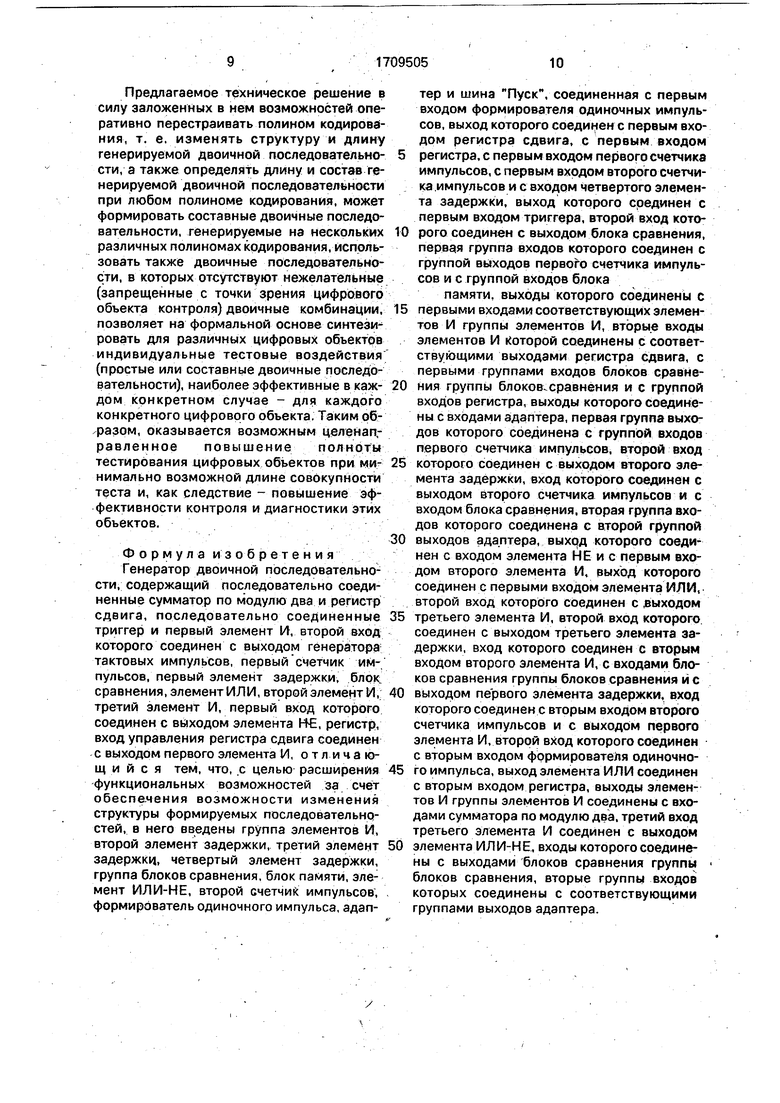

На фиг, 1 представлена блок-схема устройства; на фиг, 2 - блок-схема адаптера.

Генератор двоичной последовательности содержит соединенные последовательно сумматор 1 по модулю два и п-разрядный

регистр сдвига 2, соединенные последовательно триггер 3 и элемент И 4, выход которого соединен со входом управления сдвигами регистра сдвига 2, и генератор

синхротактов 5. Вход сумматора 1 по модулю два соединен с шиной постоянной логической единицы. В генератор введены регистр выдачи 5, группа элементов И 7, счетчик адреса 8, первый 9, второй 10, третий IT и четвертый 12 элементы задержки, группа элементов сравнения 13, ПЗУ 14, элемент сравнения 15, первый 16 и второй

17элементы ИЛИ, второй 18 и третий 19 элементы И, счетчик пакета 20, элемент НЕ

21, формирователь одиночного импульса 22 и адаптер 23. Группа выходов (1...п) регистра сдвига 2 соединена поразрядно с одноименными группами , входов регистра выдачи 6, группы элементов И 7 и группы

элементов сравнения 13. Группа выходов (1...П) регистра выдачи 6 через адаптер 23 соединена с группой (1...п) выходов устройства, группа выходов (1.1...1.1) адаптера 23 поразрядно соединена с одноименной группой входов счетчика адреса JB, группа выходов (2,1...2.1) адаптера 23 поразрядно соединена с одноименной группой входов элементов сравнения 15, группа входов (1 ...I) которой поразрядно соединена с одноименной группой входов ПЗУ 14 и с группой выходов (1 ...I) счетчика адреса 8. Группы выходов (1.1...1.п) ... (К. 1...К,п) адаптера 23 поразрядно соединены с одноименными группами входов группы элементов сравнения 13. Выход управления адаптера 23 соединен с первым входом второго элемента И

18и со входом элемента НЕ 21, выход кото рого соединен с первым входом третьего элемента И 19, второй вход которого соединен с выходом первого элемента ИЛИ 16, входы которого соединены раздельно с выходами каждого элемента сравнения группы элементов сравнения 13. Группа выходов (1...П) ПЗУ 14 поразрядно соединена со второй группой входов (1...п) группы .элементов И 7. группа выходов которой (1 ...п) поразрядно соединена с группой входов (1...п) сумматора 1 помодулюдва. Выходы второго 18 и третьего 19 элeмeнfoв И

соединены с соответствующими входами второго элемента ИЛИ 17, выход которого соединен со входами записи регистра выдачи 6. Выход переполнения счетчика пакета 20 соединен со входом опроса элемента

сравнения 15 и через второй элемент задержки 10 со счетным входом счетчика адреса 8. Выход генератора синхротактов соединен с синхровходами формирователя одиночного импульса 22 и первого элемента И 4. Вход установки в состояние логического

нуля триггера 3 соединен с выходом элемента сравнения 15, Вход установки в состояние логической единицы триггера- 3 соединен через четвертый элемент эадержки 12 с выходом формирователя одиночного импульса 22 и с входами установки в ноль регистра сдвига 2, регистра выдачи iS, счетчиков адреса 8 и пакета 20, а также с выходом установки в ноль устройства. Выход первого элемента И 4 соединен со счетным входом счетчика пакета 20 через первый элемент задержки 9 со входом опроса группы элементов сравнения 13, вторым входом второго элемента И 18 и через третий элемент задержки 11 с третьим входом третьего элемента И 19, а также с выходом синхронизации устройства. Вход Hyck устройства соединен с одноименным входом формирователя одиночного импульса 22;

Генератор двоичной последовательности работает следующим образом.

После подключения Объекта (например, объекта контроля) к выходам адаптера 23 ло сигналу ПУСК открывается формирователь одиночного импульса 22 и пропускает на свой выход из серии синхроимпульсов генератора 5 одиночный импул1 с, который устанавливает в исходное состояние регистр 2 сдвиге, регистр 6 выдачи, счетчика адреса 8 (записывается, код адреса начала) счетчик пакета 20 и через выход устройства установки в ноль объект (при нёобходимрсти). Затем через элемент 12 задержки устанавливает в единичное логическое состояние триггер 3. Исходное состояние счетчика адреса 8 определяется адресом начала (АН), защитным в адаптере 23. Записанный код, например, при п k 8 АИ 00000001 с выходов (1...I) счетчика 8 адреса поступает на ПЗУ 14, на выходах(1...п) которого устанавливается: информация, представляющая собой двоичный полином обратных связей регистра 2 сдвига. По каждому синхроимпульсу, поступающему с выхода элемента И 4, регистр 2 сдвига формирует на своих выходах (1...п) двоич ный код, представляющий собой сдвиг на один разряд в сторону старших разрядов содержимого регистра.2 сдвига с одновременной записью в его младший разряд (первый) суммы по модулю два 1 и битов замкнутых, т. е. открытых через элементы И 7.1 ...7.П обратных связей регистра 2 сдвига, соединяющих соответствующие выходы (1...П) регистра 2 сдвига с одноименными входами (1...П) суМматора 1 по модулю два. Замкнутые обратные связи определяются полиномом обратных связей - двоичным кодом на выходах (1...п) ПЗУ 14.

Одновременно по каждому синхроимпульсу осуществляется прибавление 1 на счетчике 20 пакета. Через время задержки элемента 9 происходит опрос группы элементов сравнения 13, каждая из которых сравнивает сформированный на выходе регистра 2 сдвига на данном синхротакте двоичный код с кодом, заданным адаптером 23 на выходах(1,..п)...(К.1...К.п), который является запрещенным для объекта коДом. Каждый запрещенный п-разрядный код поступает на группу входов элементов сравнения 13.1... 13.п с соответствующей группы выходов запрещенных кодов адаптера 23.

5 Элемент 9 задержки выбирается таким, чтобы опрос элементов сравнения 13.1...13.k осуществляется после завершения формирования очередного кода на выходах (1...п) регистра 2 сдвига.

0 Если объект не имеет запрещенных кодов, то на выходе управления адаптера 23 имеет место уровень 1, который через элемент НЕ 21 запирает элемент И 19 и непосредственно открывает элемент И Ш. В

5 результате независимо от работы группы элементов сравнения 13 по каждому синхроимпульсу через злемент задержки 9. элемент И 18 и элемент ИЛИ 17 формируется Импульс записи на соответствующем входе

0 регистра б выдачи, осуществляющий запись очередного сформированного двоичного кода на выходах (1 ...п) регистра 2 сдвига через одноименные входы (1...П) регистра выдачи б в этот регистр, с выходов которого через

5 адаптер 23 очередной код поступает на объ-, ект.

Если объект имеет запрещенные коды, например, коды 11110011 и 00011001, то на выходе управления адаптера 23 имеет мес0 То уровень О, который через элемент21 НЕ открывает элемент И 19 и запирает элемент И 18. В результате при появлении на выходах (1 ...п) регистра 2 сдвига одного из запрещенных кодов (любого в любой

5 очередности) на выходе сравнения соответствующего элемента сравнения 13.1...13.k вырабатывается сигнал сравнения, который через элемент ИЛИ 16 закрывает элемент И 19 для прохождения через

0 него импульса с выхода элемента задержки 11. При этом запрещенный код не записы- , вается на регистр б выдачи и не выдается на объект. Все остальные, кроме запрещенных, коды не формируют сигналов сравнения на одном из элементов сравнения . 13.1...13.k и не изменяют на выходе элемента ИЛИ 16 уровня 1, который открывает элемент И 19, пропускающий соответствующие синхроимпульсы с выхода элемента задержки 9 на вход записи регистра выдачи 6

через элемент задержки 11 и злементы И 19 и ИЛИ 17. Таким образом, все остальные коды поступают на выходы устройства.

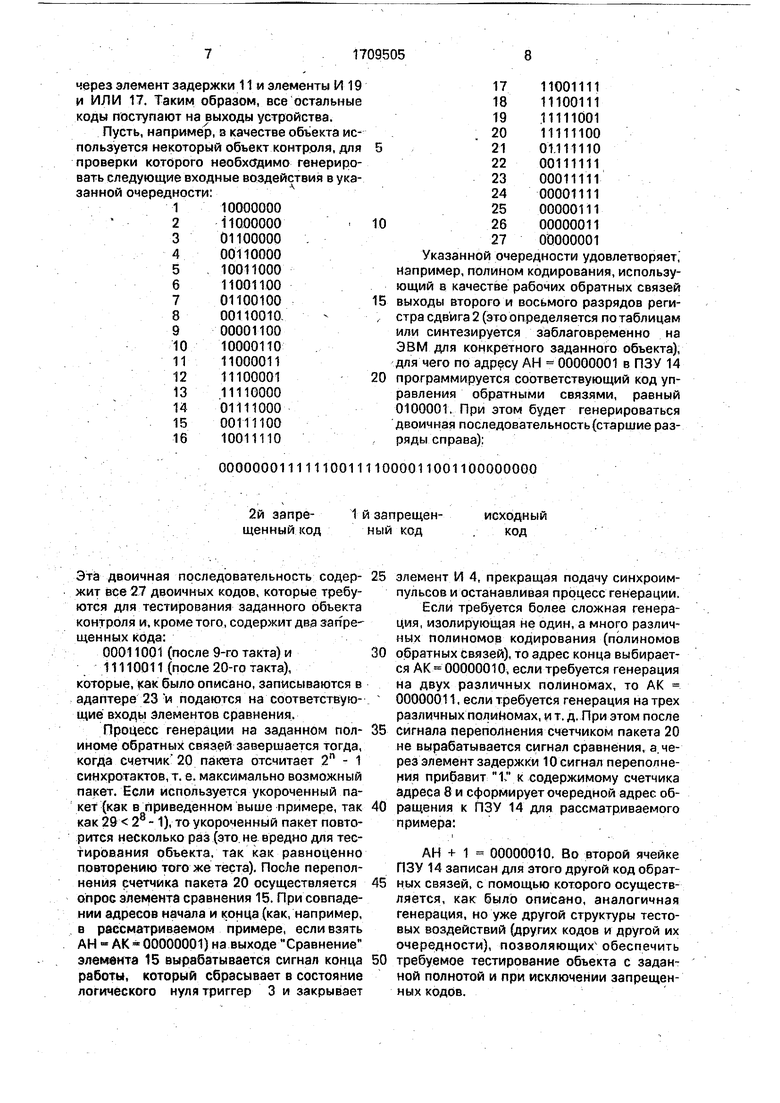

Пусть, например, в качестве объекта используется некоторый объект контроля, для проверки которого необходимо генерировать следующие входные воздействия в указанной очередности:

I10000000 2 11000000

301100000 .

400110000

5, 10011000

611001100

701100100

800110010/

900001100

1010000110

II11000011

1211100001

1311110000

14 01111000

1500111100

1610011110

0000000111111001111000011001100000000

2й запрещенный код

Эта двоичная последовательность содержит все 27 двоичных кодов, которые требуются для тестирования заданного объекта контроля и, кроме того, содержит дв.а загтре-щенных кода:

00011001 (после 9-го такта) и

11110011 (после 20-го такта), которые, как было описано, записываются в адаптере 23и подаются на соответствующиё входы Элементов сравнения.

Процесс генерации на заданном полиноме обратных связей завершается тогда, когда счетчик20 пакета отсчитает 2 - 1 синхротактов,т. е. максимально возможный пакет. Если используется укороченный пакет (как в приведенном выше примере, так как 29 2® - 1), то укороченный пакет повторится несколько раз (это. не вредно для тестирования объекта, так как равноценно повторению того же теста). ПосЛе переполнения счетчика пакета 20 осуществляется опрос элемента сравнения 15. При совпадении адресов начала и конца (как, например, в рассматриваемом примере, если взять АН АК « 00000001) на выходе Сравнение элемента 15 вырабатывается сигнал конца работы, который сбрасывает в состояние логического нуля триггер 3 и закрывает

Указанной очередности удовлетворяет, например, полином кодирования, использующий в качестве рабочих обратных связей 15 выходы второго и восьмого разрядов региf стра сдвига 2 (зто определяется по таблицам или синтезируется заблаговременно на ЭВМ для конкретного заданного объекта), для чего по адресу АН 00000001 в ПЗУ 14 20 программируется соответствующий код управления обратными связями, равный 0100001. При этом будет генерироваться двоичная последовательность (старшие разряды справа):

1 и запрещенисходныйный код код

элемент И 4, прекращая подачу синхроимпульсов и останавливая процесс генерации. Если требуется более сложная генерация, изолирующая не один, а много различных полиномов кодирования (полиномов о15ратных связей), то адрес конца выбирается АК 00000010, если требуется генерация на двух различных полиномах, то АК 00000011, если требуется генерация на трех различных полийомах, и т. д, При этом после сигнала переполнения счетчиком пакета 20 не вырабатывается сигнал сравнения, а, через элемент задержки 10 сигнал переполнения прибавит 1, к содержимому счетчика адреса 8 и сформирует очередной адрес обращения к ПЗУ 14 для рассматриваемого примера:

1-....

АН + 1 00000010. Во второй ячейке ПЗУ 14 записан для этого другой код обратных связей, с помощью которого осуществляется, как было описано, аналогичная генерация, но уже другой структуры тестовых воздействий (других кодов и другой их очередности), позволяющих обеспечить требуемое тестирование объекта с заданной полнотой и при исключении запрещенных кодов.

Предлагаемое техническое решение в силу заложенных в нем возможностей оперативно перестраивать полином кодирования, т. е. изменять структуру и длину генерируемой двоичной последовательности, а также определять длину и состав генерируемой двоичной последовательности при любом полиноме кодирования, может формировать составные двоичные последовательности, генерируемые на нескольких различных полиномах кодирования, использовать также двоичные последовательности, в которых отсутствуют нежелательные (запрещенные с точки зрения цифрового объекта контроля) двоичные комбинации, позволяет на формальной основе синтезировать для различных цифровых объектов индивидуальные тестовые воздействия; (простые или составные двоичные последовательности), наиболее эффективные вкаждом конкретном случае - для каждого конкретного цифрового объекта. Таким рб.разом, оказывается возможным целенап,равленное повышение полноты тестирования цифровых объектов при минимально возможной длине совокупности теста и, как следствие - повышение эффективности контроля и диагностики этих объектов.

Формула изобретения Генератор двоичной последовательности, содержащий последовательно соединенные сумматор по модулю два и регистр сдвига, последовательно соединенные триггер и первый элемент И, второй вход которого соединен с выходом генератора тактовых импульсов, первый счетчик импульсов, первый элемент задержки, блок: сравнения, элемент ИЛИ, второй элемент И, третий элемент И, первый вкод которого соединен с выходом элемента Н€, регистр, вход управления регистра сдвига соединен с выходом первого элемента И, отличающийся тем, что, .с целью расширения функциональных возможностей за счет обеспе-чения возможности изменения структуры формируемых последовательностей, в него введены группа элементов И, второй элемент задержки, третий элемент задержки, четвертый элемент задержки, группа блоков сравнения, блок памяти, элемент ИЛИ-НЕ, второй счетчий импульсов, формирователь одиночного импульса, адаптер и шина Пуск, соединенная с первым входом формирователя одиночных импульсов, выход которого соединен с первым входом регистра сдвига, с первым входом регистра, с первым входом первого счетчика импульсов, с первым входом второго счетчика .импульсов и с входом четвертого элемента задержки, выход которого срединен с первым входом триггера, второй вход которого соединен с выходом блока сравнения, первая группа входов которого соединен с группой выходов первого счетчика импульсов и с группой входов блока

памяти, выходы которого соединены с первыми входами соответствующих элементов И группы элементов И, вторые входы элементов И Которой соединены с соответствующими выходами регистра сдвига, с первыми группами входов блоков сравнения группы блоков сравнёния и с группой входов регистра, выходы которого соединены с входами адаптера, первая группа выходов которого соединена с группой входов первого счетчика импульсов, второй вход которого соединен с выходом второго элемента задержки, вход которого соединен с выходом второго счетчика импульсов и с входом блока сравнения, вторая группа входов которого соединена с второй группой выходов адаптера, выход которого соединен с входом элемента НЕ и с первым входом второго элемента И, выход которого соединен с первыми входом элемента ИЛИ, второй вход которого соединен с эыходом третьего элемента И, второй вход которого. соединен с выходом третьего элемента задержки, вход которого соединен с вторым входом второго элемента И, с входами блоков сравнения группы блоков сравнения и с выходом первого элемента задержки, вход которого соединен с вторым входом второго счетчика импульсов и с выходом первого элемента И, второй вход которого соединен с вторым входом формировате)1я одиночного импульса, выход элемента ИЛИ соединен с вторым входом регистра, выходы элементов И группы элементов И соединены с входами сумматора по модулю два, третий вход третьего элемента И соединен с выходом элемента ИЛИ-НЕ, входы которого соединены с выходами блоков сравнения группы блоков сравнения, вторые группы входов которых соединены с соответствующими группами выходов адаптера.

ШМЗ-си- Н2

Т .

от

ЗЛ.6

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| Генератор тестовой псевдослучайной двоичной последовательности | 1987 |

|

SU1640699A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2039365C1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Генератор М-последовательностей | 1988 |

|

SU1596440A2 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1984 |

|

SU1241177A1 |

| СИСТЕМА ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1994 |

|

RU2103744C1 |

| Устройство формирования модифицированных М-последовательностей | 2023 |

|

RU2801743C1 |

Изобретение относится к импульсйой[ технике и может использоваться в контрольно-измерительной технике. Цель изобретения - расширение функциональныхвозможностей за счет обеспечения возможности изменения структуры формируемых последовательностей - достигается введением в генератор двоичной последовательности группы элементов И 7.1-7.п. элементов 10-12 задержки, группы блоков 13.1-13.k сравнения, блока 14 памяти, элемента ИЛИ-НЕ 16, счетчика 20 импульсов, формирователя 22 одиночного импульса, .адаптера 23, шины 24 "Пуск" и образованием новых функциональных связей. На чертеже также показаны: сумматор 1 по модулю два, регистр 2 сдвига, триггерЗ, элементы И 4, 18 и 19, генератор 5 тактовых импульсов, ре^гистр 6. счетчик 8 импульсов, элемент 9 задержки, блок 15 сравнения, элемент ИЛИ 17, элемент НЕ 21. 2 ил.

на Сл.6

на MJS

на 3Ji.f8,2f

на

3,13.1

на ж 13.2

| Варакин Л.Е | |||

| Теория сложных сигналов | |||

| М.: Советское радио, 1970 | |||

| с | |||

| Вагонетка для кабельной висячей дороги, переносной радиально вокруг центральной опоры | 1920 |

|

SU243A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-01-30—Публикация

1990-01-05—Подача