Изобретение относится к импульсной технике и может найти применение в системах для контроля последовательности импульсов по периоду следования и скважности.

Известно устройство для сравнения периода следования импульсов с заданной нормой, содержащее вентиль, три элемента задержки, три триггера, резисторный делитель напряжения, конденсатор, блок совпадения ij.

Однако это устройство имеет большое количество оборудования и, осуществляя контроль периода следования импульсов, не позволяет контролировать скважность импульсной последовательности .

Наиболее близким к предлагаемому является устройство для контроля последовательности импульсов, содержащее элемент задержв:и, два триггера, два элемента И, элемент ИЛИ СООднако в известном устройстве отсутствует возмох ность контроля скважности периодической последовательности импульсов.

Цель изобретения - расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в устройство для контроля после довательности импульсов, содержащее .два триггера, два элемента И, элемент задержки и элемент ИЛИ, входы которого подключены к выходам первого и второго элементов И, первые входы которых соединены соответственно с прямым и инверсным входами первого

10 триггера, а вторые входы подключены соответственно к прямому и инверсному выходам второго триггера, введены формирователь импульсов и инвертор, выход которого соединен с

15 третьим входом второго элемента И, а вход инвертора подключен к третьему входу первого элемента И и вуоду формирователя импульсов выход которого соединен с входом элемента за20держки, первый и второй выходы которого подключены к входам установки в единицу соответственно первого и второго триггера, а третий и четвертый выходы элемента задержки соеди25нены с входами установки в ноль соответственно первого и второго триггеров .

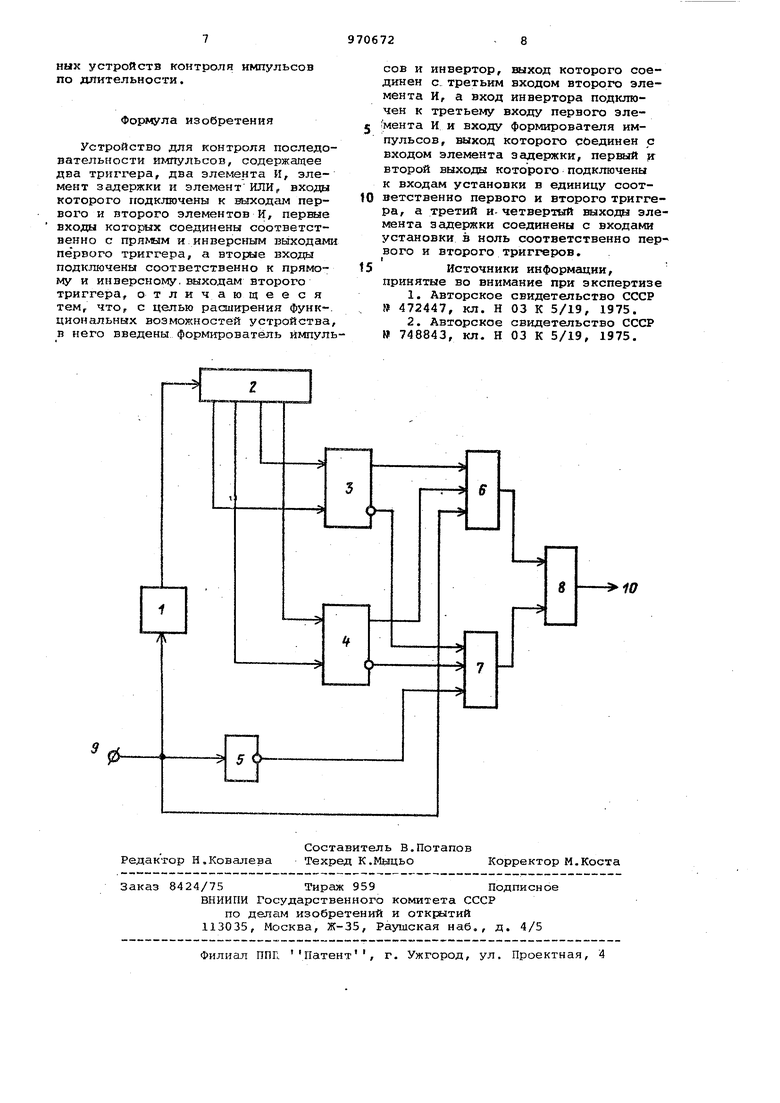

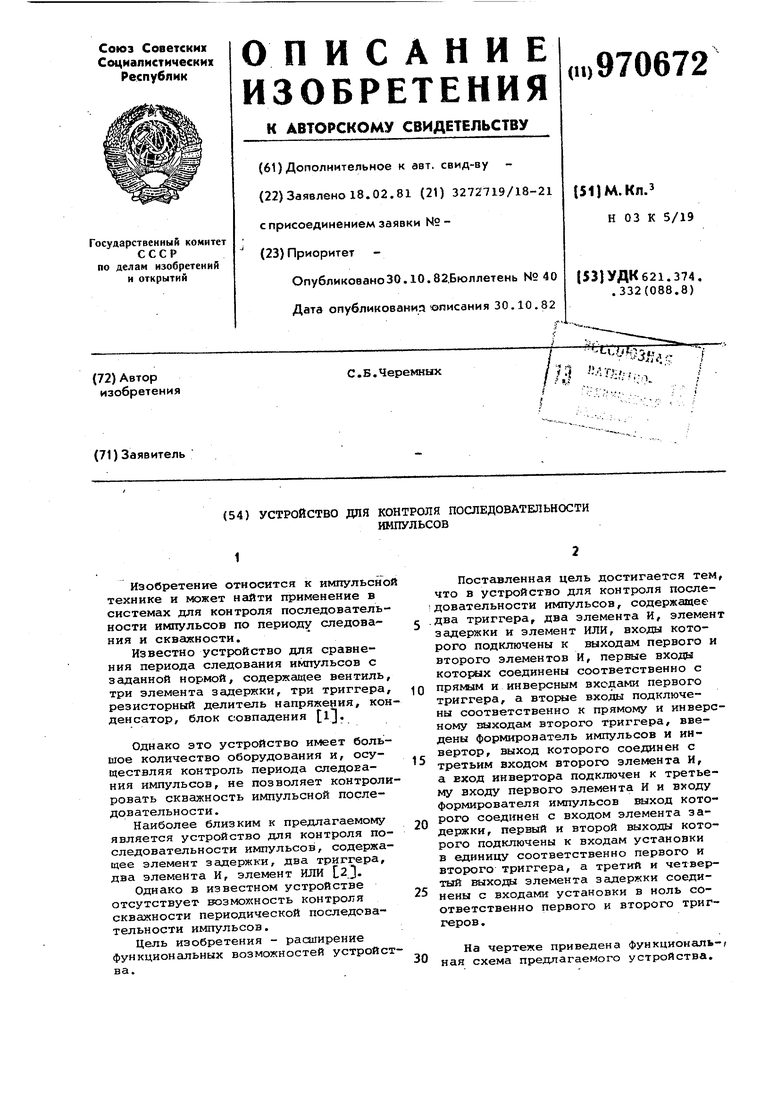

На чертеже приведена функциональ-г

30 ная схема предлагаемого устройства. Устройство содержит фор№1рователь 1 импульсов, элемент 2 задержки, триггеры 3 и 4, инвертор 5, элементы И 6 и 7, элемент ИЛИ 8, входная шина 9, выходная шина 10. Устройство работает следующим образом. Формирователь 1 для формирования короткого импульса по фрон ту импульсов контролируемой последовательности. Элемент 2 задержки пред назначен для выделения стробнмпульсоЕ начала и конца временных допусков на контролируемую последовательвость импульсов, причем время задержки стробимпульсов первого и второго выходов элемента 2 задержки соответствует началу и концу допустимого временного интервала на длительность и Шyльcoв, а время задержки стробимпульсов с третьего и четвертого выходов элемента 2 задержки соответствует начаяу и концу допустимого временного интервала на период следования контролируемой пocлeдoвaтJeльнocти импульсов, В исходном состоянии на входной шине 9 устройства присутствует низ.кий уровень напряжения, а на выходной шине 10 высокий уровень напряжения. На прямых выходах триггеров 3 и 4 присутствуют низкие уровни напр жения, а на их инверсных выходах высокие уровни напряжения. На выходе инвертора 5 присутствует высокий уровень напряжения. На шлходах элементов И б и И 7 - соответ ственно низкий и высокий уроиень на ряжения. При поступлении первого импульса на входную шину 9 устройства на тре тий вход элемента И 7 через инверто 5 поступает низкий уровень напряжения и на выходе элемента И 7 устано вится ниэкий уровень напряжения, ко торый совместно с низким уровнем на пряжения с выхода элемента И б (на входах элемента И б присутствуют ни кие уровни напряжения, поступающие триггеров 3 и 4) установят на выходе элемента ИЛИ 8 низкий уровень напряжения. Кроме того, по фронту входного импульса формирователь 1 выдает короткий импульс на вход эле мента 2 задержки. В Момент времени, когда с первого выхода .элемента 2 задержки посту пает стробимпульс, триггер 3 переключается, и с его инверсного выхода низкий уровень напряжения поступает на первый вход элемента. И 7, а с прямого выхода триггера 3 высокий уровень напряжения поступает на пер вый вход элемента И 6, но так как на втором входе элемента И б низкий уровень напряженил, снимаемый 6 три гера 4, то на выходе элемента И б сохраняется низкий уровень напряжения, а значит сохраняется и низкий уровень напряжения на выходной шине 10 устройства. По окончании входного импульса ниэкий уровень напряжения поступает на третцй вход элемента И 6, а с инвертора 5 высокий уровень напряжения поступает на третий вход элемента И 7, но так как на первом входе этого эл-емента низкий уровень напряжения, снимаемый с инверсного выхода триггера 3, то как на выходе элемента И 7, так и на входной шине 10 устройства сохраняются низкие уровни напряжения. В момент времени, когда со второго выхода элемента 2 задержки поступает стробимпульс, триггер 4 переключается и с его инверсного выхода низкий уровень напряжения поступает на второй вход элемента И 7, а с прямого выхода - высокий уровень напряжения на второй вход И б, но так как на третьем входе элемента И б низкий уровень напряжения, поступающий с входной шины 9 устройства, то как на выходе элемента И 6, так и на выходной шине 10 устройства сохраняются низкие уровни напряжения. В момент времени/ когда с третьего выхода элемента 2 задержки поступает стробимпульс, триггер 3 переключается в исходное состояние и с его прямого выхода низкий уровень напряжения поступает на первый вход элемента И б, а с его инверсного выхода высокий уровень напряжения поступает на первый вход элемента И 7, но так Как на втором входе элемента И 7 присутствует низкий уровень напряжения, снимаемый с инверсного выхода триггера 4, то низкий уровень напряжения сохраняется как на выходе элемента И 7, так и выходной шина 10 устройства. Низкие уровни напряжения на выходах элементов И б и И 7 сохраняются и при появление; очередного входного импульса, по фронту которого формирователь 1 выдает очередной короткий импульс на вход элемента 2, а на входе инверсного элемента 5 установится низкий уровень напряжения. В Момент времени, когда с четвертого выхода элемента 2 задержки поступает стробимпульс, триггер 4 переключается в исходное состояние, и с его инверсного выхода высокий уровень напряжения поступает на второй вход элемента И 7, но на выходе элемента И 7 сохраняется низкий уровень напряжения за счет того, что на третьем входе этого элемента присутствует низкий уровень напряжения, снимаелйлй с инвертора 5.

Очередные стробимпульсы с первог и второго выходов элемента 2 задерж ки вырабатывают допуск на длительность очередного входного импульса, а стробимпульсы с третьего и четвертого выходов элемента задержки вырабатывают допуск на временной интервал для следующего входного импульса. Так будет повторяться до тех пор, пока на входную шину 9 устройства будут поступать импульсы контролируемой последовательности. Причем, если длительность импульсов контролируемой последовательности и интервал времени между импульсами этой последовательности будут в эа данных до пусках, то на выходной шине 10 устройства установится и буде сохраняться уровень низкого напряжения.

Если же длительность импульсов или интервал времени между импульсами контролируемой последовательности выйдут за пределы допустимого, то это будет проявляться наличием импульсов отказа на выходной шине 10 устройства. Так, если длительность импульсов и контролируемой последовательности меныие заданного допуска, то, прежде чем придет стробимпульс с первого выхода элемента 2 задержки и перебросит триггер 3, на всех трех входах элемента И 7 будут присутствовать высокие уровни напряжения, а значит как на выходе элемента И 7, так и на выходе элемента ИЛИ 8 появятся высокие уровни напряжения. Если же длительность импульсов в контролируемой последовательности больше заданного допуска, то после прихода стробимпульса со второго выхода элемента 2 задержки, когда триггеры 3 и 4 установятся в состояние, противоположное исходному, на всех трех входах элемента И 6 будут присутствовать высокие уровни напряжения, а значит как на выходе элемента И 6, так и на выходе элемента ИЛИ 8 появятся высокие уровни напряжения. Если интервал между импульсами в контролируемой последовательности будет меньше допустимого, т.е. очередной импульс контролируемой последовательности импульсов поступит до прихода стробимпульса с третьего выхода элемента 2 задержки, то высокий уровень напряжения с входной шины 9 устройства поступит на третий вход элемента И б тогда, когда на прямых выходах триггеров 3 и 4 сохранятся еще высокие уровни напряжения, а значит высоки уровни напряжения будут на выходах элемента И б и элемента ИЛИ 8. Если интервал между импульсами контролируемой последовательности будет болше допустимого, т.е. очередной импульс контролируемой последовательности импульсов не поступит к моменту появления стробимпульса с четвертого выхода элемента 2 задержки, то на всех трех входах элемента И 7 установятся высокие уровни напряже-. ния, а значит высокие уровни напряжения будут на выходе элемента ИЛИ 8. Т.е. любое отклонение временных

0 параметров контролируемой последовательности импульсов (как по периоду следования, так и по скважности) приведет к тому, что на выходной шине 10 устройства будут появляться им5пульсы отказа.

К формирователю 1 жестких требований не предъявляется, достаточно, чтобы он формировал импульсы по длительности в пределах диапазона, М1№и0мальное значение которого определяется только быстродействием элементов устройства, а максимальное значение определяется выражением

C:,,(1)

5

где т; - задержка сигнала на первом

выходе элемента 2 задержки; .

Чдлительность импульса на выходе формирователя 1;

т период следования контроли0pyeivgjx импульсов.

Выражение (1) по.пучается, исходя из того, что в противном случае, когда на третьем выходе элемента 2 задержки появится импульс, то на пер5вом и тем более на втором выходах элемента 2 задержки имщльс еще не закончится, а значит на прямых выходах триггеров 3 и 4 сохранятся высокие уровни напряжений, и появление

0 в этот момент очередного контролируемого импульса приводит к появлению ложного отказа, так как на всех трех входах элемента И 6 одновременно будут высокие уровни напряжения.

Исходя из того, что период Т в

5 пределе принимает минимальное значение, равное t - время задержки сигнала на третьем выходе элемента 2 задержки, получается

(2)

ПС + t(,5. -С

или (3)

tcpJ-c -T;,.

Из выражения (3) следует, что.если

55 длительность контролируемых импульсов меньше разности С,,- Т то предлагаемое устройство работает без формирователя .

Таким образом, предлагаемое устройство позволяет расширить функциональные возможности, так как позволяет производить контроль последовательности импульсов не только по периоду следования, но и по скважности

65 без включения для этого дополнитель-t

ных устройств контроля импульсов по длительности,

Формула изобретения

Устройство для контроля последовательности импульсов, содержащее два триггера, два элемента И, элемент задержки и элемент ИЛИ,, входы которого подключены к выходгил первого и второго элементов И, первые входы которых соединены соответственно с прямым и инверсным выходами первого триггера, а вторые входы подключены соответственно к прямому и инверсному, выходам второго триггера, отличающееся тем, что, с целью расширения функ-. цнональннх возможностей устройства, в него введены формирователь Импульсов и инвертор, выход которого соединен с третьим входом второго элемента И, а вход инвертора подключен к третьему входу первого эле мента И и входу формирователя импульсов, выход которогхэ соединен с входом элемента задержки, первый второй выходы которого подключены к входам установки в единицу соответственно первого и второго триггера, а третий И- четвертый выходы элемента задержки соединены с входами установки в ноль соответственно первого и второго триггеров.

5 Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 472447, кл. Н 03 К 5/19, 1975.

2.Авторское свидетельство СССР № 748843, кл. Н 03 К 5/19, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по длительности | 1980 |

|

SU936413A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Устройство для обнаружения потери импульса | 1989 |

|

SU1647870A1 |

| Устройство для контроля периода импульсной последовательности | 1988 |

|

SU1511855A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU687578A1 |

| Устройство для контроля последовательности импульсов | 1987 |

|

SU1457159A1 |

| Устройство для допускового контроля пиковых значений напряжения | 1985 |

|

SU1269044A1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Двоичный счетчик | 1984 |

|

SU1282321A1 |

| Устройство синхронизации | 1988 |

|

SU1529426A1 |

Авторы

Даты

1982-10-30—Публикация

1981-02-18—Подача