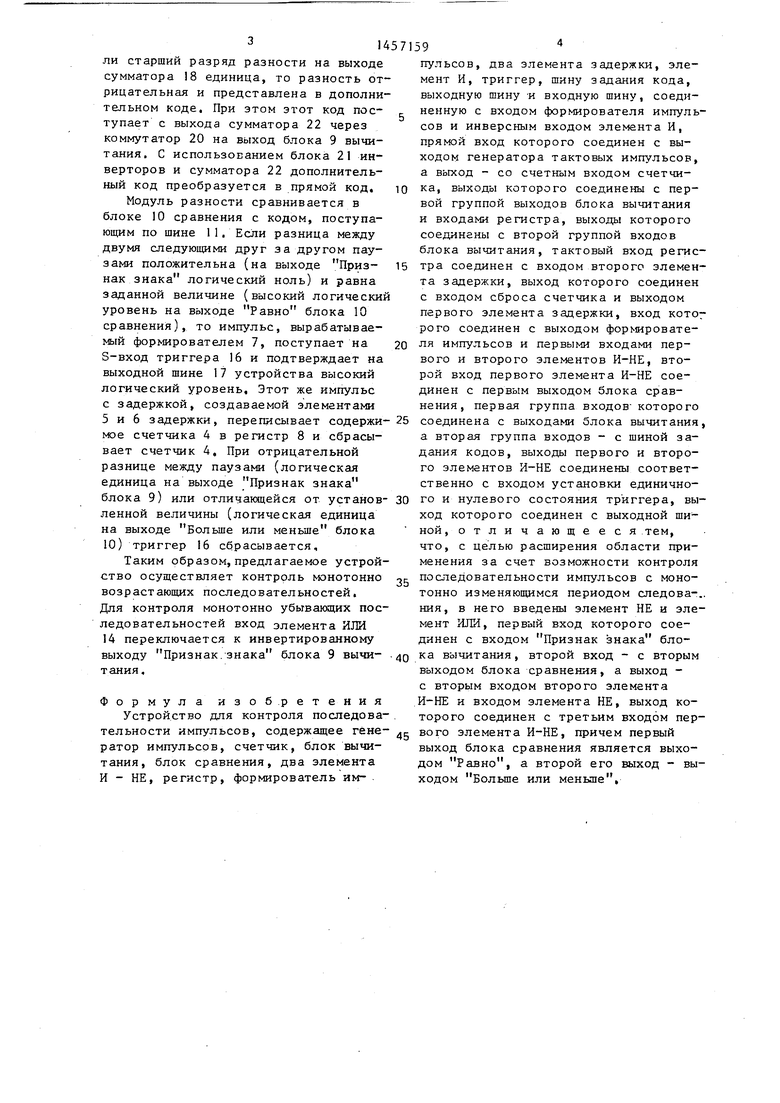

Ц)иг.1

Изобретение относится к импульсной технике и может быть использовано в автоматике и для контроля узлов цифровых вычислительных устройств,

Цель изобретения - расширение области применения за счет возможности контроля последовательности импульсов с монотонно изменяющимся периодом следования.

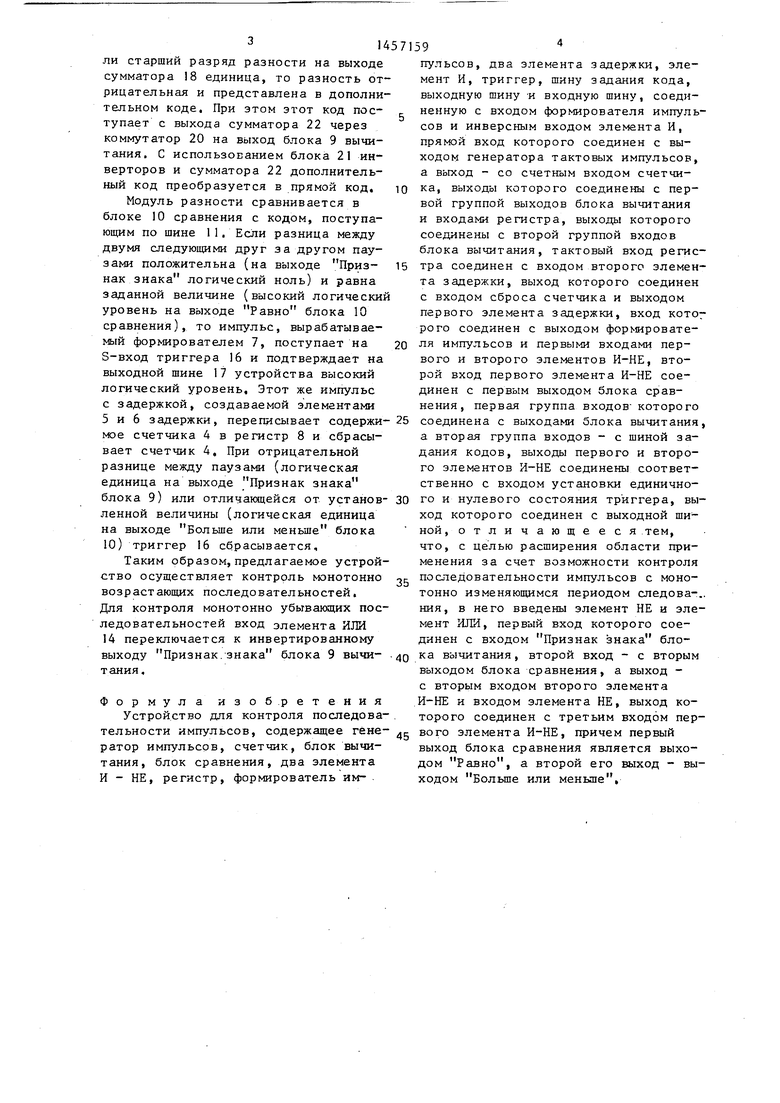

На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блока вычитания.

Устрейство для контроля последовательности импульсов (фиг.1) содержит входйую шину 1, элемент И 2, генератор 3 импульсов, с етчик 4, элементы 5 и 6 задержки, формирователь 7 импульсов, регистр 8, блок 9 вычитания блок 10 сравнения,-шину 11 задания кода, элементы И-НЕ 12 и 13, элемент ИЛИ 14, элемент НЕ 15, триггер 16 и выходную шину 17.

Выход элемента И-НЕ 13 соединен с входом установки в единицу триггер 16, выходкоторого соединен с выходной шиной 17, входная шина I соединена с входом формирователя 7, первая группа входов блока 9 вычитания соединена с выходами счетчика 4, с информационными входами регистра 8, выходы которого соединены с второй группой входов блока 9. вычитания, выходы которого соединены с первой группой входов блока 10 сравнения, вторая группа входов которого соединена с шинами 11 задания кода, выход формирователя 7 соединен с входом элемента 5 задержки и с первыми входами элементов И-НЕ 13 и 12, вторые входы которых соединены соответственно с выходами Равно блока 10 сравнения и выходом элемента ИЛИ 14, который соединен через элемент НЕ 15 с третьим входом элемента И-НЕ 13.

Выход Больше или меньше блока 10 сравнения соединен с первым входом элемента ИЛИ -14, второй вход которого подключен к выходу Признак знака блока 9 вычитания,.выход эле- мента И-НЕ 12 соединен с входом установки нуля триггера 16, выход элемента 5 задержки соединен с тактовым входом регистра 8 и с входом элемента 6 задержки, выход которого соеди- иен с входом сброса счетчика 4, счетный вход которого соединен с выхЪдом элемента И 2, прямой и инверсный входы которого соединены соотвественно

с выходом генератора 3 импульсов и с входной шиной 1.

Блок 9 вычитания (фиг.2) содержит первый сумматор 18, первый блок 19 инверторов, коммутатор 20, второй блок 21 инверторов и второй сумматор 22. Первая группа входов блока 9 вычитания (вход уменьшаемого) подключена к входам А сумматора 18, вторая группа входов блока 9 вычитания (вход вычитаемого) подключена к входам блока 19 инверторов, а выход подключен к выходу коммутатора 20, Старший разряд С J. cyMNb:, формируемой сумматором 18, образует выход Признак знака блока 9 вычитания.

Устройство работает следукяцим образом,

Контролируемая последовательность импульсов поступает на инверсный вход элемента И 2 и вход формирователя 7 импульсов. На вторую группу входов блока 10 сравнения поступает задающий код по шинам 11, определяющий точность контроля периода следования импульсов. Элемент И 2 открывается при появлении на его инверсном входе нулевого логического уровня. Таким образом, пауза между двумя импульсами последовательности заполняется импульсами генератора 3. Образовавшийся на выходах счетчика 4 код и код, установленный на выходах регистра 8, поступают соответственно на первую и вторую группы входов блока 9 вычитания.

Первый сумматор 18 и блок 19 инверторов формируют разность кодов, поступающих на первый и второй входы блока 9. Для этого код, поступающий на второй вход блока 9, преобразуется блоком 19 инверторов в инверсный а подача на вход переноса Р сумматора 18 единицы преобразует его в дополнительный. При этом на вход старшег разряда первого кода сумматора 18 подается логический ноль, а на вход старшего разряда второго кода - логическая единица, что обеспечивает вычитание второго кода из первого. Старший разряд суммы показывает, какой знак имеет разность, сформирования сумматором 18. Если старший разряд разности (знаковый С р) ноль, то разность положительная и через коммутатор 20 на выход блока 9 поступает модуль разности кодов, т.е. все разряды разности, кроме старшего. Ее10

15

20

1457159

ли старший разряд разности на выходе сумматора 18 единица, то разность отрицательная и представлена в дополнительном коде. При этом этот код поступает с выхода сумматора 22 через коммутатор 20 на выход блока 9 вычитания. С использованием блока 21 инверторов и сумматора 22 дополнительный код преобразуется в прямой код.

Модуль разности сравнивается в блоке 10 сравнения с кодом, поступающим по шине 11. Если разница между двумя следующими друг за другом паузами положительна (на выходе Признак знака логический ноль) и равна заданной величине (высокий логический уровень на выходе Равно блока 10 сравнения), то импульс, вырабатываемый формирователем 7, поступает на S-вход триггера 16 и подтверждает на выходной шине 17 устройства высокий логический уровень. Этот же импульс с задержкой, создаваемой элементами 5 и

мое счетчика 4 в регистр 8 и сбрасывает счетчик 4, При отрицательной разнице между паузами (логическая единица на выходе Признак знака блока 9) или отличающейся от установленной величины (логическая единица на выходе Больше или меньше блока 10) триггер 16 сбрасывается.

Таким образом,предлагаемое устройство осуществляет контроль монотонно возрастающих последовательностей. Для контроля монотонно убывающих последовательностей вход элемента ИЛИ 4 переключается к инвертированному выходу Признак.знака блока 9 вычитания.

пульсов, два элемента задержки, элемент И, триггер, шину задания кода, выходную шину -и входную шину, соединенную с входом формирователя импульсов и инверсным входом элемента И, прямой вход которого соединен с выходом генератора тактовых импульсов, а выход - со счетным входом счетчика, выходы которого соединены с первой группой выходов блока вычитания и входами регистра, выходы которого соединены с второй группой входов блока вычитания, тактовый вход регистра соединен с входом второго элемента задержки, выход которого соединен с входом сброса счетчика и выходом первого элемента задержки, вход котог рого соединен с выходом формирователя импульсов и первыми входами первого и второго элементов И-НЕ, второй вход первого элемента И-НЕ соединен с первым выходом блока срав30

35

нения, первая группа входов- которого

6 задержки, переписывает содержи- 25 соединена с выходами блока вычитания,

а вторая группа входов - с шиной задания кодов, выходы первого и второго элементов И-НЕ соединены соответственно с входом установки единичного и нулевого состояния триггера, выход которого соединен с выходной шиной, отличающееся тем, что, с целью расширения области применения за счет возможности контроля последовательности импульсов с монотонно изменяющимся периодом следова-.. ния, в него введены элемент НЕ и элемент ИЛИ, первый вход которого соединен с входом Признак знака блока вычитания, второй вход - с вторым выходом блока сравнения, а выход - с вторым входом второго элемента И-НЕ и входом элемента НЕ, выход которого соединен с третьим входом пер- 45 вого элемента И-НЕ, причем первый выход блока сравнения является выходом Равно, а второй его выход - выходом Больше или меньше.

40

Формула изобретения

Устройство для контроля последовательности импульсов, содержащее генератор импульсов, счетчик, блок вычитания, блок сравнения, два элемента И-НЕ, регистр, формирователь им0

5

0

пульсов, два элемента задержки, элемент И, триггер, шину задания кода, выходную шину -и входную шину, соединенную с входом формирователя импульсов и инверсным входом элемента И, прямой вход которого соединен с выходом генератора тактовых импульсов, а выход - со счетным входом счетчика, выходы которого соединены с первой группой выходов блока вычитания и входами регистра, выходы которого соединены с второй группой входов блока вычитания, тактовый вход регистра соединен с входом второго элемента задержки, выход которого соединен с входом сброса счетчика и выходом первого элемента задержки, вход котог рого соединен с выходом формирователя импульсов и первыми входами первого и второго элементов И-НЕ, второй вход первого элемента И-НЕ соединен с первым выходом блока срав30

45

35

45

45

40

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1981 |

|

SU1024933A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2444123C1 |

| Адаптивное цифровое устройство для определения амплитуды и длительности случайных сигналов | 1983 |

|

SU1233170A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

Изобретение может быть использовано в автоматике и для контроля узлов цифровых вычислительных устройств. Цель изобретения - расширение области применения за счет возможности контроля последовательности импульсов с монотонно изменяюпщ- мся периодом следования - достигается путем введения в состав устройства элемента ИЛИ 14, элемента НЕ 15 и новых связей, В состав устройства входят также входная шина 1, элемент И 2, генератор 3 импульсов, счетчик 4, элементы 5 и 6 задержки, формирователь 7 импульсов, регистр 8, блок 9 вычитания, блок 10 сравнения, шина 11 задания кода, элементы И-НЕ 12 и 13, триггер 16, выходная шина 17. Введенные отличия обеспечивают возможность индикации появления в априорно неизвестной входной последовательности импульсов с монотонно изменяющимся периодом следования. 2 ил. п s ел сд | ел со

«0 tY

Y

.i .

«tf

TT

«SI

«0 tY

.i .

| Устройство для контроля последовательности импульсов | 1983 |

|

SU1102042A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Устройство для контроля последовательности импульсов | 1985 |

|

SU1307581A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-02-07—Публикация

1987-03-31—Подача