(ЗО УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ ЛИНЕАРИЗАЦИИ

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для вычисления функций линеаризации выходных характеристик первичных измерительных преобразователей и для Дискретной записи с минимальной избыточностью информации сигналов, характеризующих физические процессы в различных автоматизированных системах управления технологическими процессами.

Известно устройство для формирования функции линеаризации, содер ; а1дее генератбр опорной частоты, смесители и полосовые фильтры 1 .

Недостатком устройства является ограниченная область применения, так как это устройство позволяет определять функцию линеаризации только частотных датчиков с дифференциальным выходом.

Известно также устройство для вычисления функции линеаризации, содержащее аналого-цифровой преобразователь, цифроаналоговые преобразователи, реверсивные счетчики, генератор импульсов, блок памяти, элементы задержки и Элементы И, триггер и компаратор 21 ,

Heдocтaткo д данного устройства является ограниченная область применения, так как оно может быть использовано только для перв ичных измерительных преобразователей с регу

10 лируемыми коэффициентами передачи.

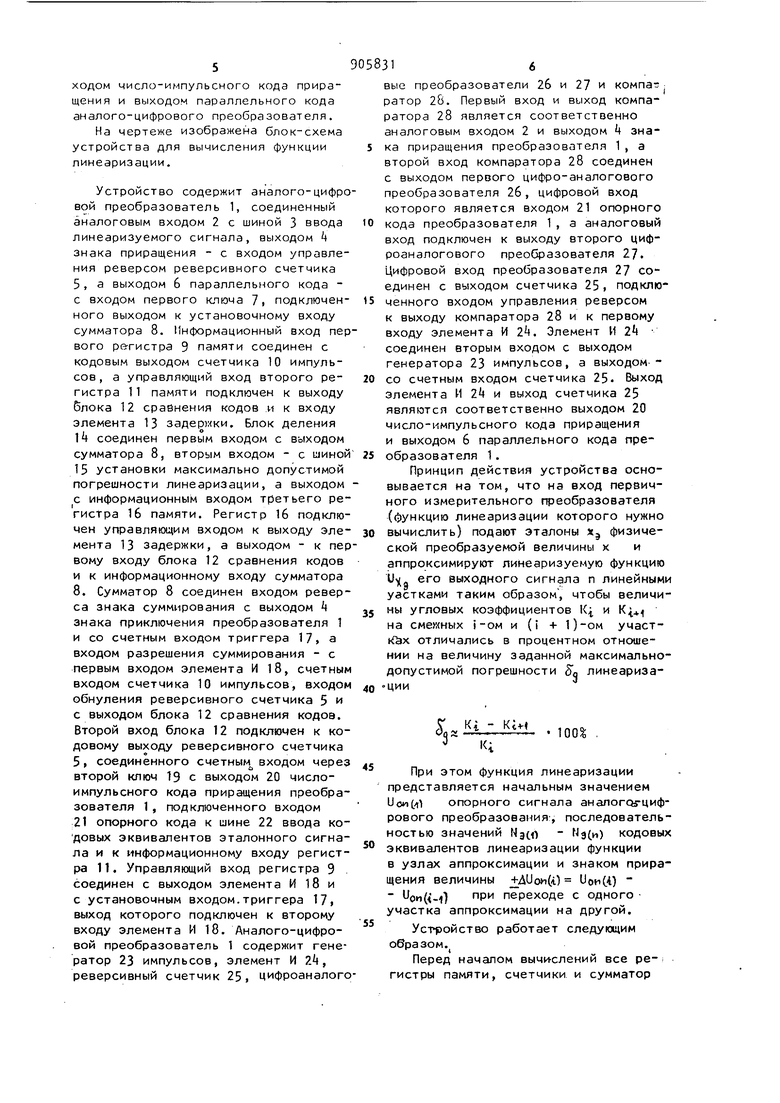

Наиболее близким к изобретению является устройство для вычисления функции линеаризации, содержащее регистры памяти, ключи и аналого15цифровой преобразователь, соединенный аналоговым входом с шиной ввода линеаризации сигнала, выходом знака приращения - с входом управления реверсом реверсивного счетчика, а вы20ходом параллельно кода - с входом первого ключа, подключенного выходом к установочному входусумматора, причем информационный вход первого регистра памяти соединен с кодовым выходом счетчика импульсов, а управЛЯЮ1ЧИЙ вход второго регистра памяти подключен к еы-ходу блока сравнения кодов, входу элемента задержки, управляющим входам двух коммутаторов, соединенных информационными входами через соответствующие ключи с выходами первого и второго регистров памяти, выходом реверсивного счетчика и выходом счетчика импульсов, подклю ченного входом общения к входу обнуления реверсивного счетчика и к выхо ду элемента задержки, а счетным входом к выходу генератора импульсов и входу делителя частоты, соединенного управляющими входами с выходами коммутаторов, а выходом - со счетным вхо дом дополнительного реверсивного сче чика, подключенного выходом к входу цифроаналогового преобразователя и к информационному входу сумматора, соединенного выходом с первым входом блока сравнения кодов, подключенного вторым входом к шине установки максимально-допустимой погрешности линеаризации, причем выход число-импульсного кода приращения аналогоцифрового преобразователя соединен со счетным входом реверсивного счетчика, а выход параллельного кода преобразователя подключен к информационному входу второго регистра и через первь|й ключ к установочному входу дополнительного реверсивного счетчика СЗЗ. Недостатком этого устройства является сложность технической реализации вычисления функции линеаризаци характеристик первичных измерительны Преобразователей. Целью изС5бретения является упрощение устройства. С этой целью устройство для вычисления функции линеаризации, включающее регистры памяти, ключи и аналого-цифровой преобразователь, соеди ненный аналоговым входом с шиной вво да линеаризуемого сигнала, выходом знака приращения - с входом управления реверсом реверсивного счетчика, а выходы параллельного кода - с входом первого ключа, подключенного выходом к установочному входу сумматора, причем информационный вход первого регистра памяти соединен с коде вым выходом счетчика импульсов, а управляющий вход второго регистра па мяти подключен к выходу блока сравне ния кодов и к входу элемента задержки, содео) триггер, элемент И и блок деления, соединенный первым входом с выходом сумматора, вторым входом - с шиной установки максимально допустимой погрешности линеаризации, а выходом - информационным входом третьего регистра памяти, подключенного управляющим входом к выходу элемента задержки, а выходом - к первому входу блока сравнения кодов и к информационному входу сумматора, соединенного входом реверса знака суммирования с выходом знака приращения аналого-цифрового преобразователя и со счетным входом триггера, а входом разрешения суммирования - с первым входом элемента И, счетным входом счетчика импульсов, входом обнуления реверсивного счетчика и с выходом блока сравнения кодов, второй вход которого подключен к кодовому выходу реверсивного счетчика, соединенного счетным входом через второй ключ с выходом число-импульсного кода приращения аналого-цифрового преобразо.вателя, подключенного входом опорного :кода к шине ввода кодовых эквивалентов эталонного сигнала и к информационному входу второго регистра памяти, а управляющий вход первого регистра памяти соединен с выходом элемента И и с установочным входом три|- гера И. Кроме этого, аналого-цифровой преобразователь содержит генератор импульсов, элемент И, реверсивный счетчик, цифроаналоговые преобразователи и компаратор, пераы вход и выход которого являются соответственно аналоговым входом и выходом знака приращения аналого-цифрового преобразователя, а второй вход соединен с выходом первого -цифроаналогового; преобразователя, цифровой вход которого является входом опорного кода аналого-цифрового преобразователя, а аналоговый вход подключен к выходу второго .цифроаналогового преобразователя, соединенного цифровым входом с выходом реверсивного счетчика, подключенного входом управления реверсом к выходу компаратора и к первому входу элемента И, соединенного вторым входом с выходом генератора импульсов, а выходом - со счетным входом реверсивного счетчика, причем выход элемента И и. выход реверсивного счетчика являются соответственно выходом число-импульсного кода приращения и выходом параллельного кода аналого-цифрового преобразователя. На чертеже изображена блок-схема устройства для вычисления функции линеаризации. Устройство содержит аналого-цифро вой преобразователь 1, соединенный аналоговым входом 2 с шиной 3 ввода линеаризуемого сигнала, выходом 4 знака приращения - с входом управления реверсом реверсивного счетчика 5, а выходом 6 параллельного кода с входом первого ключа 7i подключенного выходом к установочному входу сумматора 8. Информационный вход пер вого регистра 9 памяти соединен с кодовым выходом счетчика 10 импульсов , а управляющий вход второго регистра 11 памяти подключен к выходу блока 12 сравнения кодов и к входу элемента 13 задержки. Блок деления k соединен первым входом с выходом сумматора 8, вторым входом - с шиной 15 установки максимально допустимой погрешности линеаризации, а выходом с информационным входом третьего регистра 16 памяти. Регистр 16 подключен управляющим входом к выходу элемента 13 задержки, а выходом - к пер вому входу блока 12 сравнения кодов и к информационному входу сумматора 8. Сумматор 8 соединен входом реверса знака суммирования с выходом Ц знака приключения преобразователя 1 и со счетным входом триггера 17, а входом разрешения суммирования - с первым входом элемента И 18, счетным входом счетчика 10 импульсов, входом обнуления реверсивного счетчика 5 и с выходом блока 12 сравнения кодов. Второй вход блока 12 подключен к кодовому выходу реверсивного счетчика 5 , соединенного счетным. входом через второй ключ 19 с выходо м 20 числоимпульсного кода приращения преобразователя 1, подключенного входом 21 опорного кода к шине 22 ввода кодовых эквивалентов эталонного сигнала и к информационному входу регистра 11. Управляющий вход регистра 9 соединен с выходом элемента И 18 и с установочным входом.триггера 17, выход которого подключен к второму входу элемента И 18. Аналого-цифровой преобразователь 1 содержит генератор 23 импульсов, элемент И .k, реверсивный счетчик 25, цифроаналого 16 вые преобразователи 2б и 27 и компат: ратор 28. Первый вход и выход компа ратора 28 является соответственно аналоговым входом 2 и выходом знака приращения преобразователя 1, а второй вход компаратора 28 соединен с выходом первого цифро-аналогового преобразователя 26, цифровой вход которого является входом 21 опорного кода преобразователя 1, а аналоговый вход подключен к выходу второго цифроаналогового преобразователя 27. Цифровой вход преобразователя 27 соединен с выходом счетчика 25, подклю ценного входом управления реверсом к выходу компаратора 28 и к первому входу элемента И . Элемент И 2 соединен вторым входом с выходом генератора 23 импульсов, а выходом со счетным входом счетчика 25. Выход элемента И 2k и выход счетчика 25 являются соответственно выходом 20 число-импульсного кода приращения и выходом 6 параллельного кода преобразователя 1. Принцип действия устройства основывается на том, что на вход первичного измерительного преобразователя (функцию линеаризации которого нужно вычислить) подают эталоны х физической преобразуемой величины к и аппроксимируют линеаризуемую функцию Uy его выходного сигнала п линейными уастками таким образом , чтобы величины угловых коэффициентов К| и К на смежных i-ом и (i + 1)-ом участkex отличались в процентном отношении на величину заданной максимальнодопустимой погрешности Sq линеариза4ии .Г . Kt - KUl к; При этом функция линеаризации представляется начальным значением onifl} опорного сигнала аналого5-цифрового преобразования:, последовательностью значений NjCO эС) кодовых эквивалентов линеаризации функции в узлах аппроксимации и знаком приращения величины +/iUon(t) ЧоиС) - Uon(-i) Р переходе с одного участка аппроксимации на другой. Устройство работает следующим образом. Перед началом вычислений все ре-; гистры памяти, счетчики и сумматор обнуляютсЯс Вычисленные функции линеаризации начинают с определения начального значения NQ;(.J опорного сигнала NQVJ на участке Хэ(о) ) для чего нажатием пусковой кнопки (на чертеже на изображена) кратковременно размыкают ключ 19 и замыкают ключ 7. Соответственно с этим обрывается связь счетного входа сче чика 5 с выходом 20 число-импульсного кода приращения преобразовател 1 , а установочный вход сумматора 8 подключается к выходу 6 параллельно го кода, преобразователя 1 (на врем удержания кнопки в нажатом состоянии). Одновременно с этим подают на вход первичного измерительного преобразователя эталон y(,} и на шину 22 устройство соответствуюидий этому эталону кодовый эквивалент ) , Выходной сигнал Uy3(-i) измерительного преобразователя с шины 3 устройства поступает на аналоговый вход 2 аналого-цифрового преоб разователя 1, В результате появивше гося на выходе компаратора 28 сигна ла, вызванного разбалансом на его входах сигналов U,3(i) и U (где и выходное напряжение преобразо вателя 26), счетчик 25 начинает заполняться импульсами с выхода генер тора -23 до совпадения сигналов на входах компаратора 28, при этом величина кода на выходе 6 преобразова теля 1 (т,е„ код счетчика 25) станет равной опорное напряжение на ана логовом входе преобразователя 27; NV и Njv|- количество дискретных уров ней, формируемых преобразо вателями 2б и 27Показание NOM счетчика 25 заносится в сумматор 8 и представляет собой первое слагаемое, неизменяющееся в течение всего процесса вычислений. При этом в регистр 16 через блок деления 1 { запишется первое значение приращения ANonti) S oq- величина максимально-допус погрешности линеаризации, вво в делитель 1 с шины 15. Поспе отпускания пусковой кнопки ключ 7 размыкается, а ключ 19 замыкается и далее на вход измерительного преобразователя и на шину 22 начинают подавать последовательно в порядке нарастания значений эталоны , ..., Xз(,) и соответствующие им кодовые эквиваленты N эСг) ,,., Мэ(и-) , Если при подаче каждой пары значений х.2.} э(г) .-. уравновешивание сигналов э(г) 3(0 , . .. Uxsti) , N9(0 . поступающих на входы 2 и 21 аналогоцифрового преобразователя 1, достигается в результате изменения кода в счетчике 25 на величину ANo ТО считают линеаризуемой выходной сигнал первичного измерительного преобразователя линейным на участке 5(5(1) UisaU) в пределах допустимой погрешности On линеаризации. При этом сравнение текущего значения приращения Д Мц, , формируемого в счетчике 5 , с максимально допустимым значением ДМйу,(л) для первого участка Ux3(i) Ux3(4l линеаризации, хранимым в регистре 16, осуществляется блоком 12 сравнения кодов. Если при каком-то (i + 1)-ом значении пары эталонов Хз(4Я ) счетчике 5 сформируется число, равное максимально допустимому приращению оиС) ° сработает блок 12, сигнал на выходе которого зафиксирует конец первого линейного (в пределах Su) участка выходной характеристики По сигналу с выхода блопроизоидет запись в регистр узлового значения N.) ; поступление одного счетного импульса в счетчик 10; обнуление счетчика 5; формирование в сумматоре 8 нового результата о(г) ) +AHo«(i) ; запись в регистр 16 через делитель 1 нового максимально допустимого для второго участка приращения (эта запись проANoh(2.) изводится через временной интервал, определяемый элементом 13 задерх ки) ; поступление сигнала на один вход элемента И 18. Однако сигнал разрешения записи в регистр 9 на выходе элемента И 18 появится в том случае. если перед поступлением импульса с выхода блока 12 знак приращения ANiovn на последуюо ем участке смен1-1тся ча противоположный по отношению к знаку приращения на предыдущем участ ке. Каждая омена знака на выходе 4 преобразователя 1 вызывает переключение триггера 171 а появление сигнала на выходе элемента И 18 возвращает триггер 17 в исходное нулевое состояние. При дальнейшем формировании пар значений эталонов Хэ(1+з.) - зСг-а) э(и) bin) устройство работает аналогично описанному. Таким образом, после окончания вычисления функции линеаризации полная функция линеаризации задана значениями функции N в узла-х линеаризации (записанными в регистр 11) и порядковыми номерами линейных участков, на которых необходимо сменить знак приращения ДМсц (э начале градуированной шкалы приращение Nonf/i) О во всех случаях, так как определение начального значения ) производят с нуля). Порядковые номера К записываются в регистр Для получения истинного значения преобразуемой физической величины х при эксплуатации первичного измерительного преобразователя с нелинейной выходной характеристикой Ux f (х) подключают его выход к входу пре образователя 1, устанавливают начальн значение Мд„() опорного сигнала (коэффициент аналого-цифрового прео разователя) и по мере получения на выходе 6 преобразователя 1 узловых значений N изменяют величину опорного сигнала на входе 21 преобразователя 1 . Таким образом, предлагаемое устро ство по сравнению с известным позвб ляет упростить техническует реализацию вычисления функции линеаризации что, в частности, объясняется умень .шением количества формируемых и хра нимых параметров функции линеаризации, так как в известном функция линеаризации задается большей совокупностью параметров таких координа узлов аппроксимации, как значения линеаризуемой функции, значения вре менных интервалов между узлами, вел чины и знаки приражения линеаризуемой функции. Указанное обстоятельство и обуславливает возможную технико-экономическую эффективность устройства. Формула изобретения 1. Устройство для вычисления функции линеаризации,-содержащее регистры памяти, ключи и аналого-цифровой преобразователь, соединенный аналоговым входом с шиной ввода линеаризуемого сигнала,выходом знака приращения - с входом управления реверсом реверсивного счетчика, а выходы параллельного кода - с входом первого ключа, подключенного выходом к установочному входу сумматора, причем информационный вход первого регистра памяти соединен с кодовым выходом счетчика импульсов, а управляющий вход второго регистра памяти подключен к выходу блока сравнения кодов и к входу элемента задержки, отличающееся тем, что, с целью упрощения устройства, оно содержит триггер, элемент И и блок деления, соединенный первым входом с выходом сумматора, вторым входом с шиной установки максимально допустимой погрешности линеаризации, а выходом - информационным входом трртьего регистра памяти, подключенного управляющим входом к выходу элемента задержки, а выходом - к первому входу блока сравнения кодов и к информационному входу сумматора, соединенного входом реверса знака суммирования с выходом знака приращения аналого-цифрового преобразователя и со счетным входом триггера. а входом разрешения суммирования с первым входом элемента И, счетным входом счетчика импульсов, входом обнуления реверсивного счетчика и с выходом блока сравнения кодов, второй вход которого подключен к кодовому выходу реверсивного счетчика, соединенного счетным входом через второй ключ с выходом число-импульсного кода приращения аналого-цифрового преобразователя, подключенного входом опорно го кода к шине ввода кодовых эквивалентов эталонного сигнала и к информационному входу второго регистра памятиj а управляющий вход первого регистра памяти соединен с выходом элементами и с установочным входом триггера, выход которого подключен к второму входу элемента И. 2. Устройство по п. 1, , о т л и чающееся тем, что аналогоцифровой преобразователь содержит генератор импульсов, элемент И, реверсивный счетчик, цифроаналоговые преобразователи и компаратор, первый вход и выход которсу-о являются соответственно аналоговым входом и выходом знака приращения аналого-цифрового преобразователя, а второй вход соединен с выходом первого цифроаналогового преобразователя, цифровой вход которого является входом опорного кода аналого-цифрового преобразователя, а аналоговый вход подключен к выходу второго цифроаналогового преобразователя, соединенного цифровым входом с выходом реверсивного счетчика, подключенного входом управления реверсом к выходу компа1 2ратора и к первому входу элемента И, соединенного вторым входом с выходом генератора импульсов, а выходом со счетным входом реверсивного счетчика, причем выход элемента И и выход реверсивного счетчика являются соответственно выходом число-импульсного кода приращения и выходом параллельного кода аналого-цифрового преобразователя., Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР ff , кл. G 06 G 7/26, Г978 , 2.Авторское свидетельство СССР по заявке № 27866418/1 8-2, кл. G Об J 3/00, 1979. 3.Авторское свидетельство СССР № , кл. G Об F 3/00, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Устройство для коррекции характеристик измерительных преобразователей | 1982 |

|

SU1100630A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1019465A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1070575A1 |

| Логарифмирующее устройство | 1979 |

|

SU858011A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

IS -0

Авторы

Даты

1982-02-15—Публикация

1980-05-12—Подача