(54) АДАПТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU875622A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU864552A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1084852A1 |

| Способ для измерения частоты и устройство для его осуществления | 1980 |

|

SU883779A1 |

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1051703A1 |

| Адаптивный аналого-цифровой преобразователь | 1983 |

|

SU1109899A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU942257A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1056246A1 |

| Система для передачи телеизмерительной информации | 1982 |

|

SU1113832A1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1976 |

|

SU738158A1 |

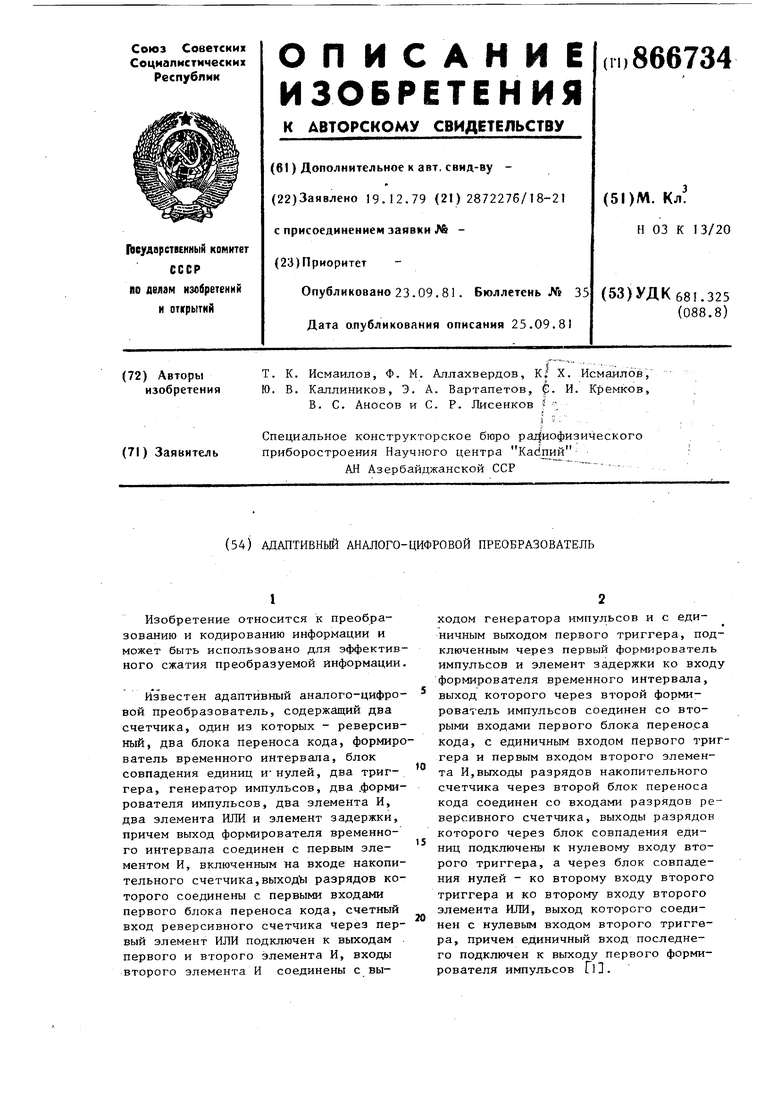

Изобретение относится к преобразованию и кодированию информации и может быть использовано для эффектив ного сжатия преобразуемой информации Известен адаптивный аналого-цифровой преобразователь, содержащий два счетчика, один из которых - реверсивный, два блока переноса кода, формиро ватель временного интервала, блок совпадения единиц и нулей, два триггера, генератор импульсов, два .формирователя импульсов, два элемента И, два элемента ИЛИ и элемент задержки, причем выход формирователя временного интервала соединен с первым элементом И, включенным на входе накопительного счетчика,выходЪ разрядов которого соединены с первыми входами первого блока переноса кода, счетный вход реверсивного счетчика через первый элемент ИЛИ подключен к выходам первого и второго элемента И, входы второго элемента И соединены с выходом генератора импульсов и с единичным выходом первого триггера, подключенным через первый формирователь импульсов и элемент задержки ко входу формирователя временного интервала, выход которого через второй формирователь импульсов соединен со вторыми входами первого блока переноса кода, с единичным входом первого триггера и первым входом второго элемента И,выходы разрядов накопительного счетчика через второй блок переноса кода соединен со входами разрядов реверсивного счетчика, выходы разрядов которого через блок совпадения единиц подключены к нулевому входу второго триггера, а через блок совпадения нулей - ко второму входу второго триггера и ко второму входу второго элемента ИЛИ, выход которого соединен с нулевым входом второго триггера, причем единичный вход последнего подключен к выходу первого формирователя импульсов Г). Недостатком данного устройства является низкая точность преобразования за счет динамических погрешностей и низкая эффективность сжатия преобра- зуемой информации. Цель изобретения - повышение точности преобразования и эффективности сжатия преобразуемой информации. Поставленная цель достигается тем, что в адаптивный аналого-цифровой пре образователь, содержащий первый блок переноса кода, генератор эталонной частоты, выход которого соединен с первьп входом первого элемента И, выход которого соединен с первым входом второго элемента И и с первым входом первого счетчика, выходы которого соединены с первыми входами второго блока переноса кода, выходы которого соединены с информационными вы ходными клеммами, выход второго элемента И соединен со входом сложения второго счетчика, вход Еычитания кото рого соединен с выходом элемента задержки, а выход старшего разряда подключен ко счетным входам первого триг гера, выход которого соединен со знаковыми выходными Клеммами, второй триггер, вход установки в нуль которо го соединен с выходом элемента ИЛИ, дополнительно введены третий Ьчетчик регистр памяти, блок цифрового задания апертуры, цифровой компаратор, преобразователь обратного кода в прямой, третий элемент И и блок управления, при этом вход элемента задержки соединен со счетным входом третьего счетчика и подключен к выходу тре тьего элемента И, первый вход которого соединен с выходом генератора эталонной частоты, выходы разрядов второ го счетчика подключены к; первым инфор мационным входам преобразователя обратного кода в прямой, вторые управляющие входы которого подключены к вы ходам первого триггера,выходы npeo6tt разователя обратного кода в прямой .подключены К первым входам цифрового комйаратора, вторые входы которого подключены к выходам блока цифрового задания апертуры, выходы второго блока 50 и к

переноса кода подключены ко входам разрядов регистра памяти, выходы разрядов которого подключены к первым входам первого блока переноса кода, выходы которого подключены ко входам раз-рядов третьего счетчика, выход старшего разряда которого подключен к первому входу элемента ИЛИ, еди1тчвторой вход которого соединен с первым входом второго элемента ШШ и третьим входом блока управления, второй вход которого соединен со вторыми 55 входами второго, третьего и пятого элемента ИЛИ, с нулевыми входами первого и пятого триггеров, единичный выход пятого триггера соединен с четверный выход второго триггера подключен ко второму входу третьего элемента И,. входная клемма устройства подключена к первому входу блока управления, второй вход которого подключен к клемме Пуск, третий вход - к выходу старшего разряда третьего счетчика, четвертый вход - к выходу цифрового компаратора и к сигнальной выходной , первый выход блока управления клемме подключен ко вторым входам первого . блока переноса кода и ко входам установки в нуль первого и второго счетчиков и первого триггера, второй выход блока управления подключен к единичному входу второго триггера, третий выход - ко второму входу первого элемента И, четвертый выход - ко второму входу второго элемента И, пятый выХОД - ко -входу установки в нуль третьего счетчика и ко второму входу элемента ИЛИ шестой выход - ко входу установки в нуль регистра памяти, седьмой выход - ко вторым входам второго блока переноса кода, восьмой выход ко входу установки в нуль первого счетчика. БЛОК управления, входящий в устройство, выполнен на пяти-триггерах, трех формирователях импульсов, двух элементах И, пяти элементах ИЛИ и четырех элементах задержки, причем первый вход блока управления соединен со счетным входом первого триггера, единичный выход которого через первый формирователь импульсов подключен ко входу первого элемента задержки, выход которого подключен к единичному входу второго триггера, нулевым входам третьего и четвертого триггеров и ко второму выходу блока управления, первый выход которого соединен с выходом первого формирователя импульсов, нулевой выход первого триггера подключен ко входу второго формирователя импульсов, выход которого соединен со входом второго элемента задержки, выход второго элемента задержки подключен к единичному входу пятого триггера, нулевому входу второго триггера первому входу первого элемента ИЛИ тым выходом блока управления, третий выход которого соединен с единичным выходом второго триггера, выход первого элемента ШШ подключен к первому входу первого элемента И и к едияичному входу третьего триггера, еди ничный выход которого подключен к пе вому входу второго элемента И, второ вход которого соединен с четвертым вхо дом блока управления, пятый выход ко торого соединен с выходом второго элемента ИЛИ, выход второго элемента И подключен к единичному входу че вертого триггера, единичный выход ко торого подключен ко второму входу первого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, через третий элемент з держки - к первому входу четвертого элемента ИЛИ, а через четвертый элемент задержки - к первому входу пято го элемента ИЛИ, выход которого соединен с восьмым выходом блока управ ления , седьмой выход которого соединен с выходом четвертого элемента ИЛИ, второй вход которого через третий формирователь импульсов соеди нен с единичным выходом пятого триггера, а шестой выход блока управлени соединен с выходом третьего элемента ИЛИ. На чертеже изображена блок-схема устройства. Устройство содержит счетчики 1-3, регистр 4 памяти, блок 5 цифрового задания апертуры, цифровой компаратор 6, преобразователь 7 обратного кода в прямой, два блока 8 и 9 перен са кода, генератор 10 эталонной част ты, триггеры 11 и 12, элементы И 13элемент ИЛИ 16, элемент 17 задержки и блок 18 управления. Блок 18 управления содержит триггеры 19-23, формирователи 24-26 импульсов, элементы И 27 и 28, элементы ИЛИ 29-33, элементы 34-37 задержки. Входная клем ма 38 устройства подключена к первому входу блока 18 управления, второй вход которого подключен к клемме 39 устройства. Информационные выходные клеммы 40 устройства подключены к выходам разрядов блока 9 переноса кода, сигнальная выходная клемма 4 устройства соединена с четвертым входом блока 18 управления и подключена к выходу цифрового компаратора 6, а знаковые выходные клеммы 42 устройства подключе 1ы к выходам триггера 12, соединенным со вторыми управляющими входами преобразователя 7 обратного кода в прямой. Третий вход блока 18 управления подключен к выходу старшего разряда счетчика 2 и к первому входу элемента ИЛИ 16. Первый выход блока управления 18 подключен ко вторым управляющим входам первого блока 8 переноса кода и ко входам обнуления счетчика 3, счетчика и триггера 12, второй выход блока управления подключен к единичному входу триггера 11, третий выход блока управления подключен ко второму входу элемента И 14, четвертьш выход блока управления подключен ко второму входу элемента И 15, пятый выхОд блока управления подключен ко входу обнуления счетчика 2 и ко второму входу элемента ИЛИ 16, шестой выход блока управления подключен ко входу обнуления регистра 4 памяти, седьмой выход блока управления подключен ко вторым управляющим входам второго блока 9 переноса кода, восьмой выход блока управления подключен ковходу обнуления счетчика 3. Вы ход генератора 10 эталонной частотыподключен к первым входам элементов И 13 и 14, выход последнего подключен к первому входу элемента И 15 и ко счетному входу счетчика 3, выходы разрядов которого подключены к первым информационным входам второго блока 9 переноса кода, выходы которого подключены ко входам разрядов регистра 4 памяти, выходы разрядов которого подключены к первым информационным входам первого блока 8 переноса кода, выходы коТ,орого подключены ко входам разрядов счетчика 2, счетный вход которого соединен через элемент 17 задержки со счетным входом вычитания счетчика 1 и подключен к выходу элемента И 13, второй вход которого подключен к единичному выходу триггера 11, нулевой вход которого подключен к выходу элемента ИШ. 16. Выход элемента И 15 подключен к счетному входу сложения реверсивного счетчика 1, выход старшего разряда которого подключен к счетному входу триггера 12, а выходы разрядов его подключены к первым информационным входам преобразователя 7 обратного кода в рямой, выходы которого подключены первым входам цифрового компаратоа 6, вторые, входы которого подключеы к выходам блока 5 цифрового задаия апертуры. В блоке 1В управления первый вход соединен со счетным входом триггера 19, единичный и нулевой выходы которого соответственно через формирова тели импульсов 24 и 25 подключены ко входам элементов 36 и 37 задержки, причём выход формирователя 24 импульсов соединен также с первым выходом блока 18 управления. Выход элемента 36 задержки подключен к единичному входу триггера 20, к нулевым входам триггеров 22 и 23, а также ко вто рому выходу блока 18 управления Выход элемента 37 задержки подключен к единичному входу триггера 21, к нулевому входу триггера 20 и к первому входу элемента ИЛИ 33, второй вход которого соединен с третьим входом блока 18 управления и первым входом элемента ИЛИ 29, выход которого соединен с пятым выходом блока 18 управления. Выход элемента ИЛИ 33 подключен к первому входу элемента И 28 и к единичному входу триггера 22, единичный выход которого подключен к первому входу элемента И 27, выход .которой подключен к единичному входу триггера 23, единичный выход которого подключен ко второму входу элемента И 28, выход которого подключен к первому входу элемента ИЛИ 30/ через элемент 34 задержки - ко второму входу элемента ИЛИ 31 и через элемент 35 задержки - к первому входу элемента ИЛИ 32, выход которого соеди нен с ВОСЫФ1М выходом блока 18 управ ления, седьмой выход которого соединен с выходом элемента ИЛИ 31, первы вход которого через формирователь 26 импульсов подключен к единичному выходу триггера 21 и к четвертому выхо ду блока 18 управления, четвертый вход которого соединен со вторым вхо дом элемента И 27. Второй вход блока 18 управления соединен со вторыми входами элементов ИЛИ 29, 30 и 32, а также с нулевьми входами триггеров 1 и 21. Выход элемента ИЛИ 30 соединен с шестым выходом блока 18 управления третий выход которого соединен с еди ничным выходом триггера 20. Устройство работает следукяцим образом. На входную клемму 38 поступает по следовательность импульсов, период следования (t) которых функциональ но связан со входным сигналом. По си налу на пусковой клемме 39 устанавли ваются в нулевое положение триггеры и 21 в блоке 18 управления, через элемент ИЛИ 29 счетчик 2 обнуляется, а триггер 11 через элемент ИЛИ 16 устанавливается в нулевое положение, через элемент ИЖ 30 обнуляется регистр 4 памяти и через элемент ИЛИ 32 обнуляется счетчик 3. При этом элементы И 13-15 закрыты и через них не проходят импульсы эталонной частоты f с выхода генератора 10 на входы счетчиков 1-3. При поступлении первого импульса входной последовательности Tx(t) на первый вход 38 блока 18 управления триггер 19 перебрасывается в единичное положение. Формирователь 24 импульсов преобразует передний фронт сигнала с единичного выхода триггера 19 в импульс, по которому открывается первый блок 8 переноса кода и обнуляются счетчик 3, счетчик I и триггер 12. При этом сигналом с нулевого выхода триггера 12 к преобразователю 7 кода подключаются прямые выходы разрядов счетчика 1. Затем импульс с выхода формирователя 24, задержанный в элементе 36 на-время, необходимое для установки счетчика 1 и триггера 12 в нулевое положение, устанавливает триггеры 11 и 20 в единичное положение, а триггеры 22 и 23 - в нулевое полЪжение. При этом сигналами с единичных выходов триггеров 11 и 20 открываются соответственно элементы И 13 и 14. В счетчи,ке 2 записан полный код 2 -1 (где п - число разрядов счетчика), так как в момент открытия блока 8 переноса кода в регистре 4 памяти на инверсных выходах разрядов, подключенных к информационным входам блока 8 переноса кода, имеется код 2 -1 обнуленного регистра. Сигналом со старшего разряда счетчика 2 через элемент ИЛИ 16 триггер 11 перебрасывается в нулевое состояние, при котором элемент И З закрывается. Импульсы эталонной частоты f, с выхода генератора 10 через открытый элемент И 14 начинают поступать на счетный вход счетчика 3, где суммируются в течение интервала времени, на который открыт элемент И 14. Вторым импульсом входной последовательности TX(t) триггер -19 перебрасывается в нулевое положение, при этом передний фронт сигнала с нулевого выхода триггера 19 преобразуется в формирователе 25 в имульс, который, задержавшись в элемене 37 на время задержки элемента 36, .устанавливает триггер 21 в единичное положение, а триггер 20 - в нулевое положение. При этом элемент И 14 закрывается, а элемент И 15 открывается и остается в открьутом состоянии до окончания измерения и появления повторного сигнала на пусковой клемме 3 устройства. Поскольку интервал между первым и вторым импульсами входной последовательности T;(t), на который открывается элемент И 14, равен периоду следования входного сигнала, за это время в счетчике 3 образуется числовой эквивалент входного сигнала, равный NyCt) foTx(t-i) где T(t) - первый период входного сигнала, отнесенный к моменту времени t. Передний фронт сигнала с единичного выхода триггера 21, появляющийся в момент окончания первого после пуска периода входного сигнала, преобразуется в формирователе 26 в им пульс, который через элемент ИЛИ 31 открывает второй блок 9 переноса кода через которую код N)((t-j) первого пери ода переписывается в регистр 4 памяти. Код Nj((t-,) поступает также на выход 40 устройства и является начальным существенным отсчетом N((t ) . По импульсу начала следующего пери ода входного сигнала импульсом с выхода формирователя 24 обнуляется ре|Версивный счетчик 1 и триггер 12 значка, а также открывается первый блок 8 (переноса кода, через который в счетчик 2 переписывается обратный код N j.( t ) начального существенного от-, счета. Затем, после задержки в элементе 36, импульс устанавливает триггеры П и 20 в единичное положение, а триггеры 22 и 23 - в нулевое положение. При этом открываются элементы И 13 и 14. Через элемент И 13 импульсы ffl с выхода генератора 10 начинают поступать на счетный вход счет чика 2 и после задержки в элементе 17 на счетный вход вычитания реверсивного счетчика 1. Через открытые элемен;ты И 14 и 15 импульсы частоты fg начи нают поступать соответственно на счет ный вход счетчика 3 и счетный вход суммирования счетчика 1. Задержка элемента 17 выбирается равной половине периода частоты f, поэтому импуль сы на входы сложения и вычитания приходят не совпадая во времени. Поскольку в счетчике 2 записан обратный код ) начального существенного отсчета, то после поступления на вход счетчика 2 числа импульсов, соответствующего начальному существенному отсчету, счетчик переполнится и на выходе его старщего разряда появится сигнал, который через элемент ИЖ 16 перебросит триггер 11 в нулевое положение, при котором элемент И 13 закрывается . Сигналом с выхода счетчика 2 через элемент ИЛИ 29 обнуляется этот, счетчик. Следовательно, элемент И 13 открывается на время, равное периоду начального существенного отсчета Tx(t.), за которое на вход вычитания счетчика 1 поступит число импульсов, соответствующее этому периоду. Элемент И 14 открывается.на время, равное текущему периоду T() входного сигнала, за которое на вход сложения счетчика 1 поступит число импульсов, соответствующее этому периоду. В счетчике 1, после окончания большего из периодов образуется, число импульсов, равное разности между числами импульсов, соответствующих существенному и текущему отсчетам. В зависимости от знака числа на выходах разрядов счетчика 1 образуется прямой или обратный код приращения д N x( Nx(ti) - Na(ti). Преобразователь 7 обратного кода в прямой,управляемый сигналами с триггера 12, формирует на своих выходах модуль uNxCt.) в прямом коде числа в счетчике 1. Этот код, непрерывно изменяющийся во времени, сравнивается с кодом апертуры N, поступающим из блока 5 цифрового задания апертуры, в цифровом компараторе, на выходе которого формируется сигнал в момент Мо,фМх(1НнИ Если приращение текущего периода входного сигнала относительно периода предыдущего существенного отсчета достигло заданной величины апертуры, формируется на выходе цифрового компаратора 6 сигнал нового существенного отсчета, по которому код текущего периода, определенного как сзпдественный, из счетчика 3 передается на выход 40 устройства и переписывается в регистр 4 памяти. С приходом слеующего импульса входной последовательности Т(t) начинается новый цикл равнения текущего периода с сущестенным отсчетом, хранимым в регисте 4. Если же в результате сравнения кажется, что приращение меньше аперуры, на выходе компаратора 6 сигнал е формируется, код в регистре 4 не Обновляется и на выход 40 устройства теку1ций отсчет, признанный несутцественным, не передается. В зависимости от знака приращения, сигнал существенного отсчета может формироваться до или после окончания момента окончания текущего периода. Начало сравниваемых периодор существенного и текущего отсчётов совмещены при сравнении во времени, образование приращения начинается в момент окончания текущего периода и заканчивается в момент окончания существенного периода в случае Tx(t4 Tc( и в случае Тх(Ц+) Tc(t-,) образование приращения начинается в момент окончания существенного пер ода и заканчивается в момент окончания текущего периода. Устройство обеспечивает сравнение каждого периода входного сигнала с существенным отсчетом,при этом сравнен производится непрерывно точным цифровым способом. Это уменьшает динамическую погрешность самого преобразования входного сигнала (измеряет ся мгновенное значение входного сигнала) и повышает точность определения .момента существенного отсчета бл годаря непрерывности цифрового сравнения приращения с заданной апертурой. На вьгход устройства не передаются отсчеты при отсутствии изменения вхо ного сигнала или малой их величине, что повьш1ает коэффициент сжатия устройства. Высокая точность определения моментов существенных отсчетов позволя ет дополнительно существенно сжать: передаваемую информацию за счет пере дачи на выход 40 только начального полного кода входного сигнала, а затем передачи на выход 41 только сигн лов моментов существенных отсчетов и сигналов знака приращения на выходы 42. Все это повьшает точность и эффективность адаптивного преобразо|вания входной функции. Формула изобретения 1. Адаптивный аналого-цифровой пр образователь, содержащий первый блок переноса кода, генератор эталонной частоты, выход которого соединен с п .вым входом первого элемента И, выход которого соединен с первым входом вт рого элемента И и с первым входом первого счетчика, выхо;д 1 которого соединены с первыми входами второго блока переноса кода, выходы которого соединены с информационными выходными клеммами, выход второго элемента И соединен со входом сложения второго счетчика, вход вычитания которого соединен с выходом элемента задержки, а выход старшего разряда подключен к счетным входам первого триггера, выход которого соединен со знаковыми выходными клеммами, второй триггер, вход установки в нуль которого соединен с выходом элемента ИЛИ, отличающийся тем, что, с целью повьппения точности преобразования и эффективности сжатия преобразуемой информации, в него введены третий счетчик, регистр памяти, блок цифрового задания апертуры, цифровой компаратор, преобразователь обратного кода в прямой, третий элемент И и блок управления, при этом вход элемента задержки соединен со счетным входом третьего счетчика и подключен к выходу третьего элемента И, первый вход которого соединен с выходом генера-. тора эталонной частоты, выходы разрядов второго счетчика подключены к первым информационным входам преобразователя обратного кода в прямой, вторые управлягацие входы которого подключены к выходам первого триггера, выходы преобразователя обратного кода в прямой подключены к первым входам цифрового компаратора, вторые входы которого подключены к выходам блока цифрового задания апертуры, выходы второго блока переноса кода подключены ко входам разрядов регистра памяти, выходы разрядов которого подключены к первым входам первого блока переноса кода, выходы которого подключены ко входам разрядов третьего счетчика, вьгход старшего разряда которого подключен к первому входу элемента ИЛИ, единичный выход второго триггера подключен ко второму входу третьего элемента И, входная клемма подключена к первому входу блока управления, второй вход которого подключен к клемме 1Пуск, третий вход - к выходу старшего разряда третьего счетчика, четвертый вход - к выходу цифрового , компаратора и к сигнальной выходной клемме, первый выход блока управле.ния подключен ко вторым входам первого блока переноса кода и ко входам установки в нуль первого счетчика, второго счетчика и первого триггера, второй выход блока управления подключен к единичному входу второго триггера, третий выход - ко второму входу первого элемента И, четвертый выход - КС второму входу второго:элемента И, пятый выход - ко входу установки в нуль третьего счетчика и ко второму входу элемента JfflH, шестой выход - ко входу установки в нуль регистра памяти, седьмой выход - ко вто рым входам второго блока переноса кода, восьмой выход - ко входу установки в нуль первого счетчика. 2. Адаптивный преобразователь по п.1,о тличающийся тем,что, блок управления выполнен на пяти триг герах, трех формирователях импульсов, двух элементах И,пяти элементах ИЛИ и четырех элементах задержки,причем пер вый вход блока управления соединен со счетным входом первого триггера, единичный выход которого через первый Iформирователь импульсов подключен ко входу первого элемента задержки, выход которого подключен к единичному входу второго триггера, нулевым входам третьего и четвертого триггеров и ко второму выходу блока управления, первый выход которого соединен с выхо дом первого формирователя импульсов, нулевой выход первого триггера подключен ко входу второго формирователя импульсов, выход которого соединен со входом второго элемента задержки, .выход второго элемента задержки подключен к единичному входу пятого триг гера, нулевому входу второго триггера и к первому входу первого элемента ИЛИ, второй вход которого соединен с первым входом второго элемента ШТИ и третьим входом блока управления, второй вход которого соединен со вторыми входами второго, третьего и пятого элементов ИЖ, с нулевыми входами первого и пятого триггеров, единичный выход пятого триггера соединен с четвертым выходом блока управления , третий выход которого соединен с единичным выходом второго триггера, выход первого элемента ШШ подключен к первому входу первого элемента И и к единичному входу третьего триггера, единичный выход которого подключен к первому входу второго элемента И, второй вход которой соединен с четвертым входом блока управления, пятый выход которого соединен с выходом второго элемента ШШ, выход второго элемента И подключен к единичному входу четвертого триггера, единичный выход которого подключен ко второму входу первого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, через третий элемент задержки - к первому входу четвертого элемента ИЛИ, а через четвертьй элемент задержки - к первому входу пятого элемента ИЛИ, выход которого соединен с восьмым выходом блока управления, седьмой выход которого соединен с выходом четвертого элемента ИЛИ, второй вход которого через третий формирователь импульсов соединен с единичным выходом пятого триггера, а шестой выход блока управления соединен с вькодом третьего элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 443479, кл, Н 03 К 13/20, 1974 (прототип).

Авторы

Даты

1981-09-23—Публикация

1979-12-19—Подача