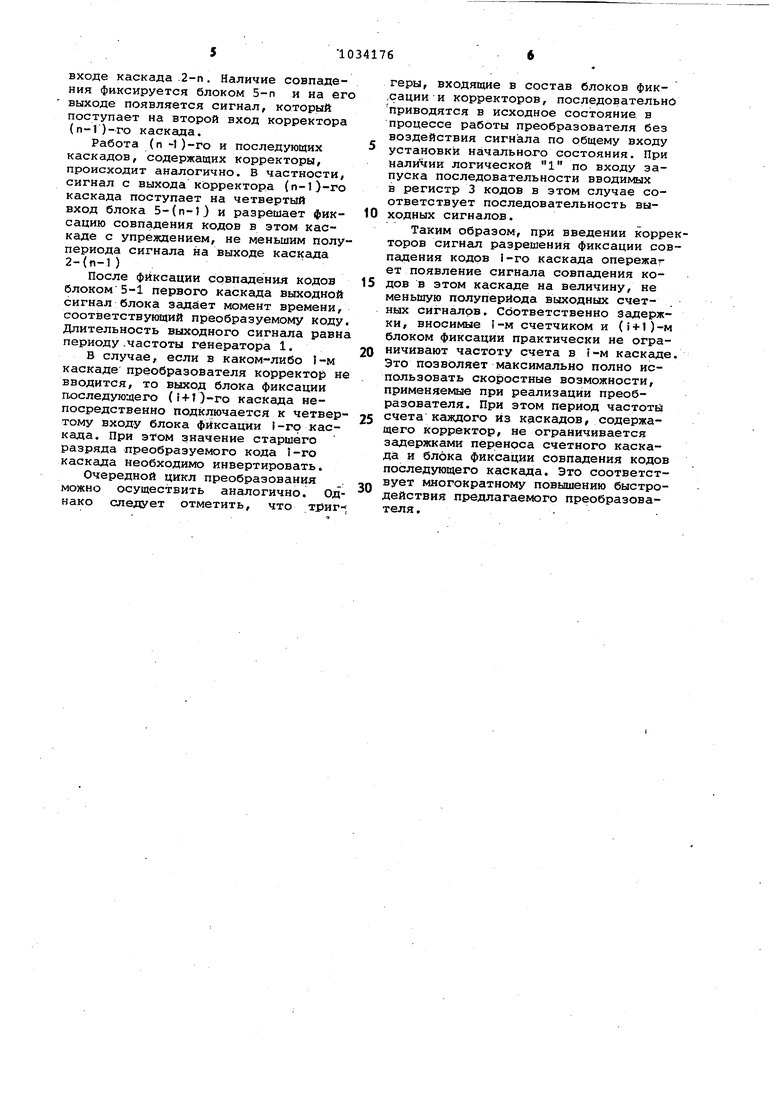

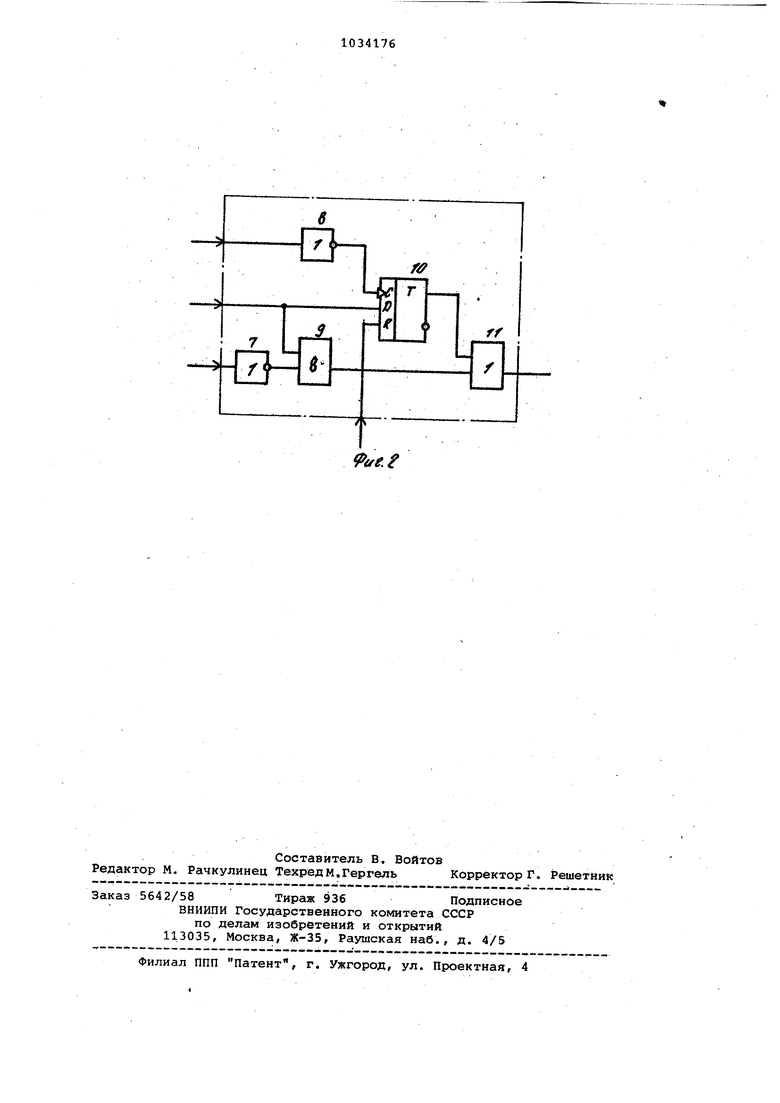

Изобретение относится к импульсной технике, а именно к преобразователям кода в непрерывную величину, и может ть использовано, в частности, при обработке сигналов на измерительных системах импульсной локацич и дальнометр ии. Известен преобразователь код временной интервал, содержащий генератор эталонной частоты, счетчик единичных приращений, регистр преобразуемого кода и кодовый компаратор, входы которого подключены к выходам указанных счетчика и регистра ИЗ.: Однако данный преобразователь имеет низкую надежность работы при широкодиапазонных преобразованиях кодов большой разрядности, что србусловлено тем, что момент времени соответствующий концу формируемого интервала, выделяется путем одновременного во всех разрядах сравнения текущего кода с заданным. Для исключения возможности появления на выходе кодового компаратора ложных сиг налов счетчик единичных приращений должен быть выполнен полностью синхронным, что сопряжено со значительным усложнением счетчика и возрастанием объема его оборудования. Это в свою очередь, повышает вероятность отказа какого-либо его элемента и сбоев в работе. Известен также преобразователь код-момент времени, содержащийгенератор эталонной частоты, п-каскадный счетчик единичных приращений, регист кода, кодовый компаратор, выпапненный на п блоках сравнения, и п блоков фиксации совпадения кодов, выход генератора эталонной частоты соеди.нен с входом- первого счетного каскада счетчика единичных приращений к первым входом первого блока фиксации совпадения кодов, первые входы остальных блоков фиксации совпадения кодов соединены с входами соответствующих каскадов счетчика единичных приращений, вторые входы блоков фиксации совпадени я кодов подключены к выходам соответствующих блоков сравнения кодового компаратора, входы кодового компаратора соединены соответственно с выходами счетчика единичных приращений и регистра кода 23. , Недостатком указанного преобразователя является низкое быстродейст вие, что обусловлено тем, что период частоты счета в каждом из п счетных каскадов должен быть не менее удвоен ной суммы задержки переноса этого каскада-и задержки блока фиксации совпадения кодов последующего каскада. Это, в свою очередь, ограничи ;вает частоту счета единичных приращений для устройства в целом. Цель изобретения - повышение быстродействия преобразователя. Поставленная цель достигается тем,.что в преобразователь код-момент времени, содержащий счетчик единичных приращений, выполненный на п последовательно соединенных каскадах, п-каскадный регистр кода, кодовый компаратор, выполненный на п блоках сравнения, п блоков фиксации совпадения кодов и генератор , эталонной частоты, вькод которого соединен с- входом первого каскада счетчика единичных приращений и первым входом первого блока фиксации совпадения кодов, выход которого ПОДКЛЮчен к выходной шине, первые вх(5ды остальных блоков фиксации совпадения кодов соединены с входами соответствующих каскадов счетчика единичных приращений, вторые входы блоков фиксации совпадения кодов подключены к шине установки нуля, а третьи вхо№3 - к выходам.соответствующих блоков сравнения кодового компаратора, входы которых соединены с выходами соответствующих каскадов А:;четчика единичных приращений и регистра кода соответственно,- введены m корректоров,где m«n, причем первый вход каждого 1-го корректора соединен с выходом старшего разряда соответствующего i-ro каскада счетчика единичного приращения, второй вход каждого -го, кроме последнего, корректора - с выт ходом каждого последующего (i + O-ro блока фиксации совпадения кодов, третий вход каждого f-ro корректора с выходом старшего разряда соответствующего i-ro каскада регистра кода, четвертый вход - с шиной установки нуля, а выход - с четвертым входом соответствующего 1-го блока фиксации совпадения кодов, при этом второй вход последнего т-го корректора подключен к шине запуска. Кроме того, корректор выполнен на двух инверторах, триггере, элементе И и элементе ИЛИ, причем первый вход корректора соединен через первый инвертор q С-входом триггера, второй вход корректора - с D-входом триггера и первым входом элемента И, второй вход которого через второй инвертор подключен к третьему входу корректора; а выход - к первому входу элемента шта, второй вход которого соединен с выходом триггера, а выход - с выходом корректора, четвертый вход которого подключен к R-входу триггера. На фиг. 1 представлена структурная схема предлагаемого преобразователя; на фиг. 2 - функциональная схема корректора. ; Преобразователь содержит генератор 1 эталонной частоты, счетчик 2 , единичных приращений, состоящий из

каскадов 2-1 - 2-n, регистр 3 преобЕ)азуемого кода, состоящий из каскадОв 3-1 - З-п, кодовый компаратор 4 из блоков 4-1 - 4-п, п блоков 5-1 5-п фиксации совпадения- кодов и m корректоров 6-1 - 6-т. В целом пре- 5 образователь имеет покаскадную структуру, где каждый i.-й.каскад () содержит счетчик 2-, регистр 3- i кода блок 4-J сравнения и блок 5-1 фиксации, ..10

Выход генератора 1 эталонной частоты соедданен с входом первого каскада 2-1 счетчика 2 я перв входом первого блока 5-1 фиксациисовпадения кодов. Первые входы блоков 5-2 - |5 5-п фиксации совпадения кодов сое-динёиы соответственно с входами каскадов 2-2 - 2-п счетчика 2. Вторле г входы блоков 5-1 - 5-п фиксации совпадения краов подключены к шине ус-.. ,. та:новки нуля, а третьи входы - к вы- ходам блоков 4-1 - 4гп сравнения кодового компаратора 4. Выходы каскадов 2-1 - 2-п счетчика 2 соединены с входами соответствующих блоков 4-1 - 4-п кодового компаратора 4, к 25 другим входам которых подключены выходи каскадов 3-1 - 3-п регистра 3. пре;образуемогс кода.

Число корректоров может быть равноили меньше п. Корректоры включаются 30 в структуру тех каскадов, быстродействие которых необходимо повысить, т;ё. где требуется наиболее полно использовать скоростные возможности элемектов, применяемых при реализа- 35 ции преобразователя. При наличии корректоров в п-м каскаде второй вход корректора является входом запуска преобразователя.

Для определенности на фиг. 1 по- хп казан пример выполнения преобразователя, где каждый из п каскадов содержит корректор (men).

Первые входа кор ректоров 6-1 бтт соединены соответственно с вы- ходами старших разрядо в с 1етных касКадов 2-1 - 2-п счетчика 2, вторые входы корректоров 6-1 - б-{)п-1) соединены соответственно с выходами блоков 5-2 - 5-п фиксации-совпадения кодов, выход блока 5-1 фиксации 50 совпадения тсодов соединен с выходом преобразователя, второй вход корректора 6-т соединен с входом запуска преобразователя, третьи входы корректоров 6-1 - б-т соединены соответ- 55 ственно с выходами старшего разряда каскадов 3-1 - 3-п регистра 3 преобразуемого кода, выходы корректоров 6-1 - б-т соединены соответственно с четвертыми входами блоков 5-1 Q 5-п фиксации совпадения ксэдов.

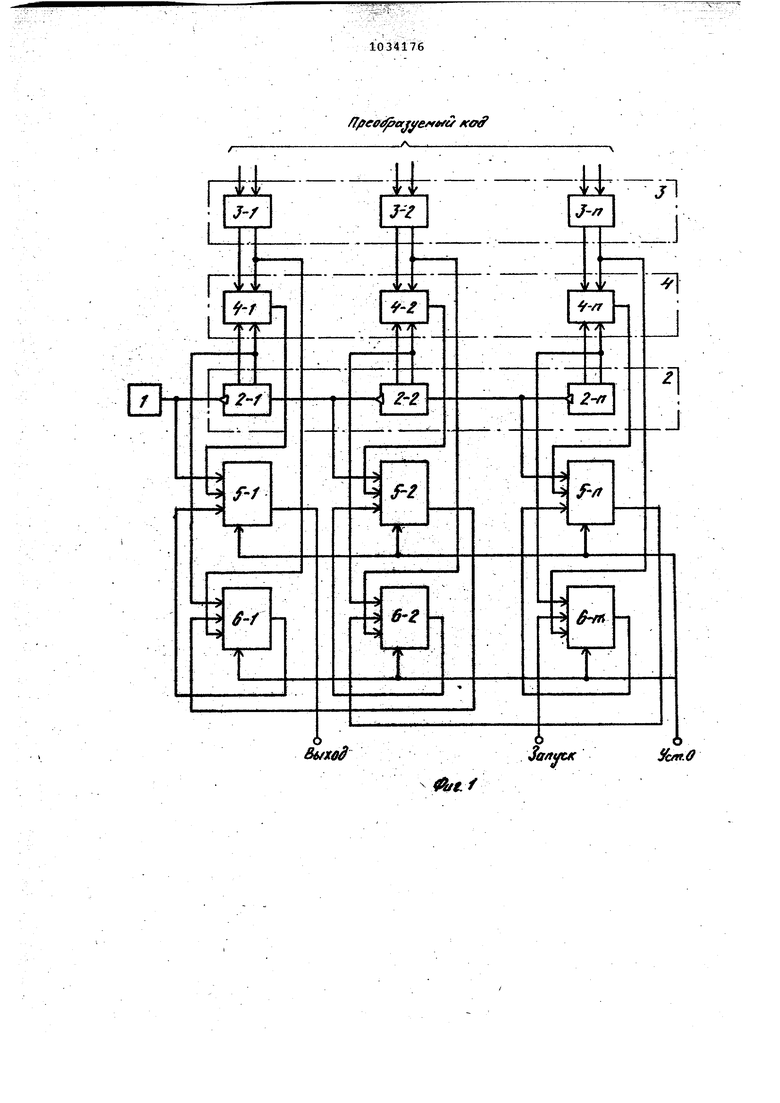

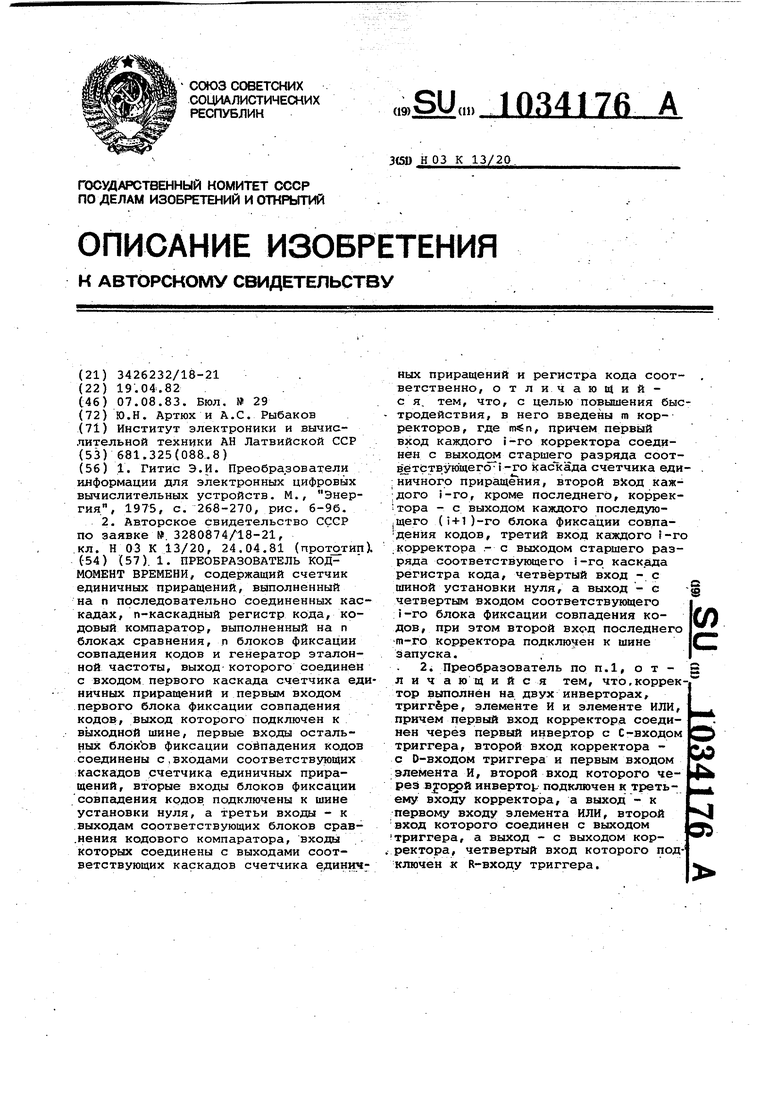

каждый из корректоров (фиг. 2) содержит логические элементы 7 и 8 , типа НЕ, логический элемент 9 типа И,; триггер 10 с С-входом синхронизации, 65

информационным D-входом и R-входом установки нулевого состояния, а также логический элемент 11 типа,ИЛИ.

Первый вход корректора соединен с входом элемента 8 типа НЕ, выход.которого соединен с С-входом тригг а 10. Второй вход корректора соединен с 0-входом триггера 10.и первым входом элемента 9 типа И, второй вход которого соединен с выходом элемента 7 типа НЕ. Третий вход корректора соединен с входом элемента 7 типа НЕ,, выхода триггера 10 и элемента 9 типа И соединены с входами элемента 11 типа ИЛИ, выход которого соединен с выходом корректора.

Преобразователь работает следующим образом.

В исходном состоянии сигналы с выхода генератора 1 непрерывно подсчитыв.аются счетчиком 2, причем в каждом из его каскадов осуществляется синхронный (квазисинхронный) счет а связь между каскадами асинхронная. В результате счета на выходах счетчика 2 формируется шкала текущего времени, заданная, например, в натуральном двоичном коде, i Началу преобразования предшест вует установка в исходное нулевое состояние триггеров блоков фиксации совпадения кодов и корректоров. В регистр 3 вводится код, соответствующий требуемому моменту появления выходного сигнала преобразователя.

Преобразование начинается при подаче на вход запуска корректора п-го каскада логической 1. После подачи сигнала запуска момент появления сигнала на выходе.корректора зависит от значения старшего разряда кода каскада 3-п. Если это значение нулевое, то входной сигнал запуска через элементы 9 и 11 непосредственно проходит на выход корректора. Если значение старшего разряда лода единичное, то сигнал на выходе корректора появляется после переключения триггера 10 сигналом по его С-входу. В обоих случаях обеспечивается то, что сигнал с выхода корректора, разрешающий фиксацию совпадения кодов в блоке 5-п, появляется на четвертом входе блока 5-п относительно сигнала совпадения кодов на третьем входе с упреждением не меньшим полупериода сигнала на выходе счетного каскада 2-п. При этом независимо от введенного в регистр 3 кода преобразование всегда происходит однозначно, в очередном цикле шкалы, начиная с ее нулевого состояния.

В момент совпадения кодов каскада З-п и каскада 2-п на выходе блока 4-п сравнения появляется сигнал совпадения, длительность которог соответствует периоду сигнала на

входе каскада .2-п, Наличие совпадения фи-ксируется блоком 5-п и на его выходе появляется сигнал, который поступает на второй вход корректора (п-Г)-го каскада.

Работа (п -1 )-го и последующих каскадов, содержащих корректоры, происходит аналогично. В частности, сигнал с выхода корректора (n-l)-ro каскада поступает на четвертый вход блока 5-(п-О и разрешает фиксацию совпадения кодов в этом каскаде с упреждением, не меньшим полупериода сигнала на выходе каскада 2-(п-1)

После фиксации совпадения кодов блоком 5-1 первого каскада выходной сигнал блока задает момент времени, соответствугадий преобразуемому коду. Длительность выходного сигнала равна периоду .частоты генератора 1.

В случае, если в каком-либо 1-м каскаде преобразователя корректор не вводится, то выход блока фиксации последующего (i -f-1 )-го каскада непосредственно подключается к четвертому входу блока фиксации i-го каскада. При этом значение старшего разряда преобразуемого кода f-ro каскада необходимо инвертировать.

Очередной цикл преобразования можно осуществить аналогично. Однако следует отметить, что Т1)иггеры, входящие в состав блоков фик.сации и корректоров, последовательно приводятся в исходное состояние в процессе работы преобразователя без воздействия сигнала по общему входу

установки начального состояния. При наличии логической 1 по входу запуска последовательности вводимых в регистр 3 кодов в этом случае соответствует последовательность выходных сигналов.

Таким образом, при введении корректоров сигнал разрешения фиксации совпадения кодов 1-го каскада опережаг ет появление сигнала совпадения кодов в этом каскаде на величину, не меньшую полуперйода выходных счетных сигналов. Соответственно задержки, вносимые 1-м счетчиком и (ч-1)-м блоком фиксации практически не ограничивают частоту счета в -м каскаде. Это позволяет максимально полно использовать скоростные возможности, применяемые при реализации преобразователя. При этом Период частотй счета каждого из кэскадов, содержащего корректор, не ограничивается задержками переноса счетного каскада и блока фиксации совпадения кодов последующего каскада. Это соответствует многократному повышению быстродействия предлагаемого преобразователя.

fcfff

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-момент времени | 1981 |

|

SU970685A1 |

| Преобразователь моментов времени в код | 1979 |

|

SU855995A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU677097A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU866734A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Преобразователь код-напряжение с широтноимпульсной модуляцией | 1978 |

|

SU790283A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1349005A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НАНРЯЖЕНИЕ — КОД | 1967 |

|

SU193154A1 |

. 1. ПРЕОБРАЗОВАТЕЛЬ КОДМОМЕНТ ВРЕМЕНИ, содержащий счетчик единичных приращений, выполненный на п последовательно соединенных каскадах, п-каскадный регистр кода, кодовый компаратор, выполненный на п блоках сравнения, .п блоков фиксации совпадения кодов и генератор эталонной частоты, выход-которого соединен с входом первого каскада счетчика единичных приращений и первым входом первого блока фиксации совпадения кодов, выход которого подключен к выходной шине, первые входы остальных блокЬв фиксации совпадения кодов соединены с,входами соответствующих каскадов счетчика единичных приращений, вторые входы блоков фиксации совпадения кодов, подключены к шине установки нуля, а третьи входы - к .выходам соответствующих блоков срав.нения кодового компаратора, входы которых соединены с выходами соответствующих каскадов счетчика едини ных приращений и регистра кода соответственно, отличающийся, тем, что, с целью повышения быс- тродействия, в него введены m кор-ректоров, где , причем первый вход каждого i-ro корректора соединен с выходом старшего разряда соответствующего- i-ro счетчика еди;ничногр приращения, второй вХод каждого i-ro, кроме последнего, коррекi тора - с выходом каждого последую,щего (i+1)-ro блока фиксации совдаденйя кодов, третий вход каждого -го .корректора .- с выходом старшего разряда соответствующего 1-го каскада регистра кода, четвёртый вход - с а S шиной установки нуля, а выход - с четвертым входом соответствукицего (Л i-го блока Фиксации совпадения кодов, при этом второй вход последнего гп-го корректора подключен к шине Запуска. , 2. Преобразователь по п.1, о т л и ч а ющ и и с я тем, что,корректор выполнен на двух инверторах, триггере, элементе И и элементе ИЛИ, причем первый вход корректора соединен через первый инвертор с С-входом триггера, второй вход корректора с с D-входом триггера и первым входом 4;: элемента И, второй вход которого через инвертор подключен к третьему входу корректора, а выход - к si первому входу элемента ИЛИ, второй № вход которого соединен с выходом триггера, а выход - с выходом кор. ректора, четвертый вход которого подключен к R-входу триггера.

tf

tff.e

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М., Энергия, 1975, с | |||

| Способ изготовления гибких труб для проведения жидкостей (пожарных рукавов и т.п.) | 1921 |

|

SU268A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке | |||

| 3280874/18-21, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-08-07—Публикация

1982-04-19—Подача