Изобретение относится к измерительл ной технике и может быть использовано в измерительно-вычислительных комплексах при цифровом измерении частотновременных параметров сигнапа. Известно устройство для преобразования моментов текущего времени в цифровой код, содержащее reHepaTqa этало: ной частоты, счетчик приращений текущего момента вретлени, синхронизатор и регистр фиксации кода счетчика Ш. Недостаток этого устройства - невысо кая точность. Наиболее близким по технической сущ ности и достигаемому результату к предпагаемому является измеритель серии временных интервалов, содернсащий генератор импульсов эталонной частоты, каскадный счетчик единичных прщэащений времени, синхронизатор, выполненный на основе элемента И, пороговой схемы и расширителя импупьсов, регистр фиксации кода счетчика, а также запоминающее устройство Сз}. Недостаток такого устройства - огрв ниченная точность преобразования, обусловленная возможными врач енными соотношен1етми между входным сигналом и тактовым импульсом генератора, а также рассогласованием суммарной и каскадов счетчика и компенсирую:Щ1гх. задержек. Цель изобретения - повышение точности чреобразования. Поставленная цель достигается тем, что в преобразователь моментов времени в коа, содержащий генератор эталонной частоты, п последовательно соедин енных счетчиков единичных приращений, основной синхронизатор и п регистров фиксации кодов, первые входы которых соединены с выходами соответствующих разрядов . счетчиков единичных приращений, выход генератора эталонной частоты соединен с первым входом основного синхронизатора и входом счет чика единичных приращений первого кап. каца, входная шина устройства соеJ

дииена с третьим входом основного синхронизатора, дополнительно введены реп-гстр фиксации кодов и п - 1 синхронизаторов, первый и второй вхоцы каждого иа которых поцключены к вы ходам старших разрядов соответс-пзенно счетчика и регистра фиксации кодов соответствующего каскада, а третьи входы каждого иа п - 1 синхронизаторов подключены к выходу синхронизатора предшествующего каскада, выходы синхронизаторсв соединены с входами считывания соответствующих регистров фиксации кодов, выхода фаз генератора под ключены к входам дополнительного регистра фиксации кодов, вход считываН1та которого соединен с входной шиной устройства, третий вход основного синхронизатора соединен с выxoдo f старшего разряда дополнительного регистра фиксации кодов.

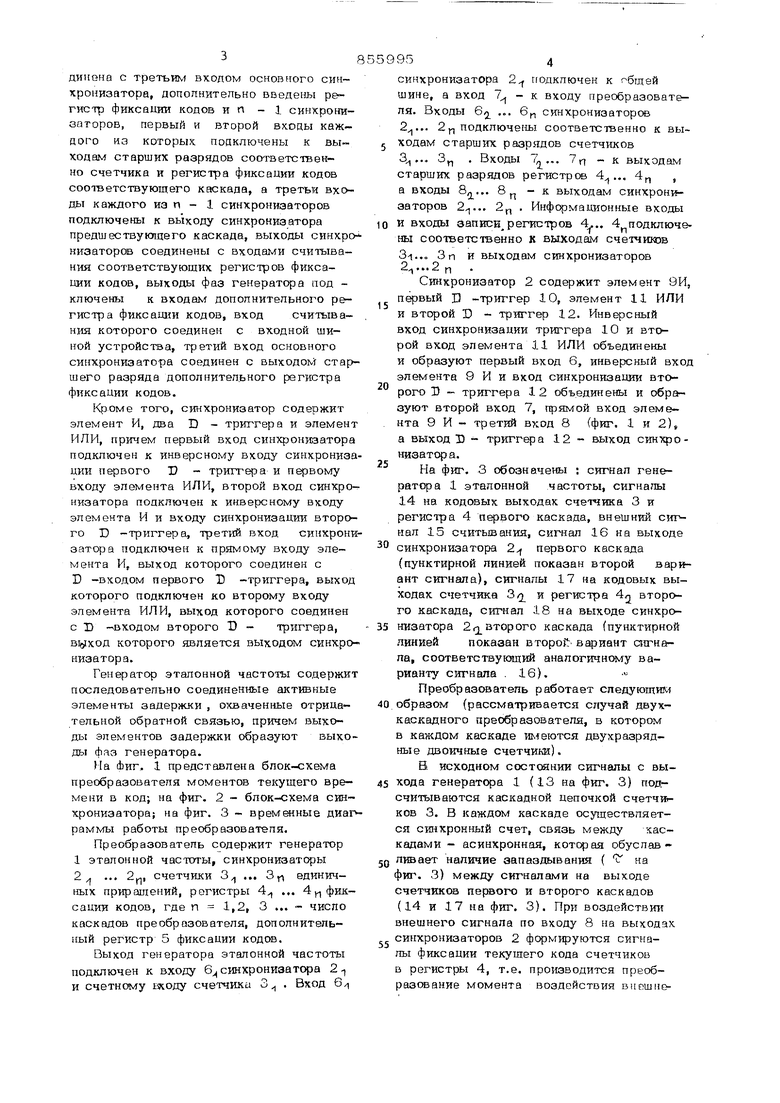

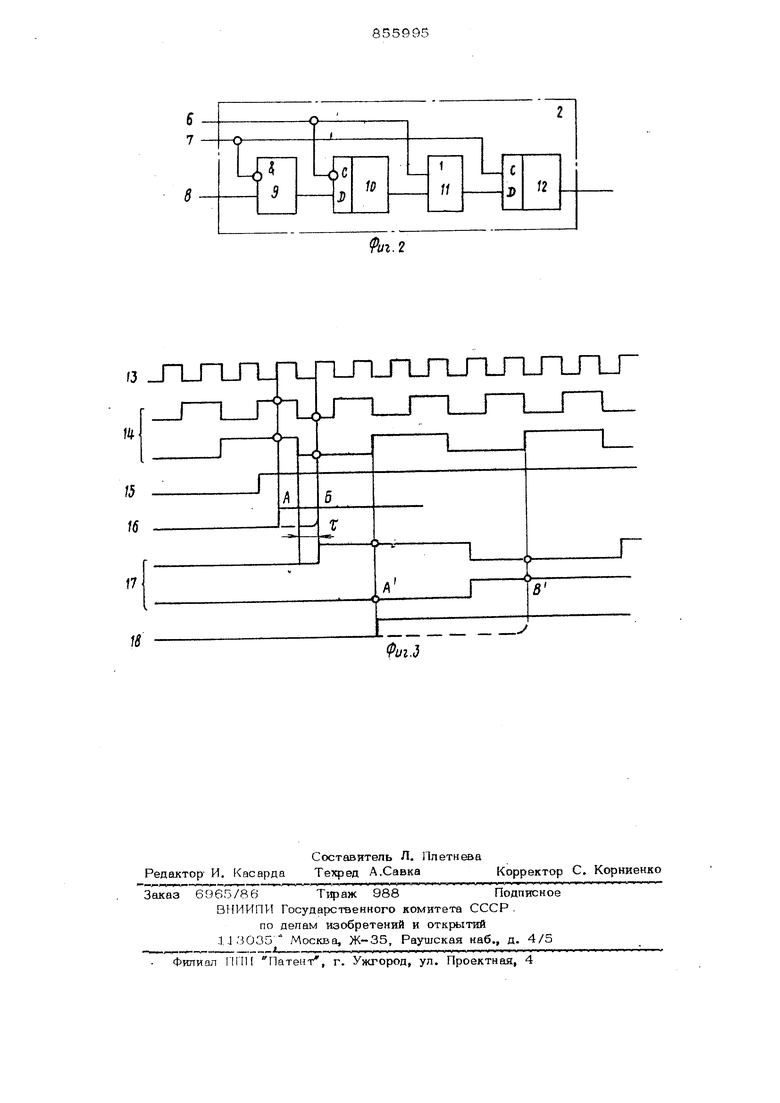

Кроме того, синхронизатор содержит элемент И, два D - триггера и элемент ИЛИ, причем первый вход синхрони:затора подключен к инверсному входу синхронизации первого Б - триггера и первому входу элемента ИЛИ, второй вход синхронизатора подключен к инверсному входу элемента И и входу синхронизации второго D -триггера, третий вход синхронизатора подключен к прямому входу элемента И, выход которого соединен с D -входом первого D -триггера, выход которого подключен ко второму входу элемента ИЛИ, выход которого соединен с Б --входом второго Т - триггера, вуход которого является выходом синхронизатора.

Генератор эталонной частоты содержит последовательно соединенные активные элементы задержки , охваченные отрицательной обратной связью, причем выходы элементов задержки образуют выходы фаз генератора.

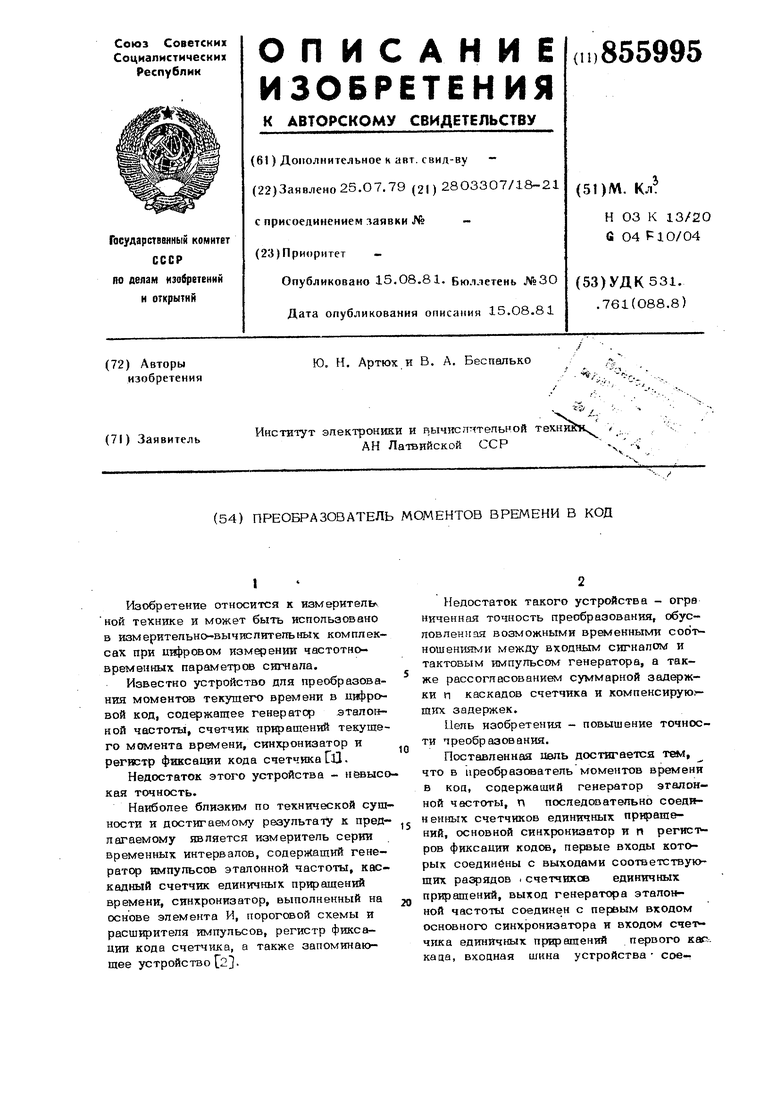

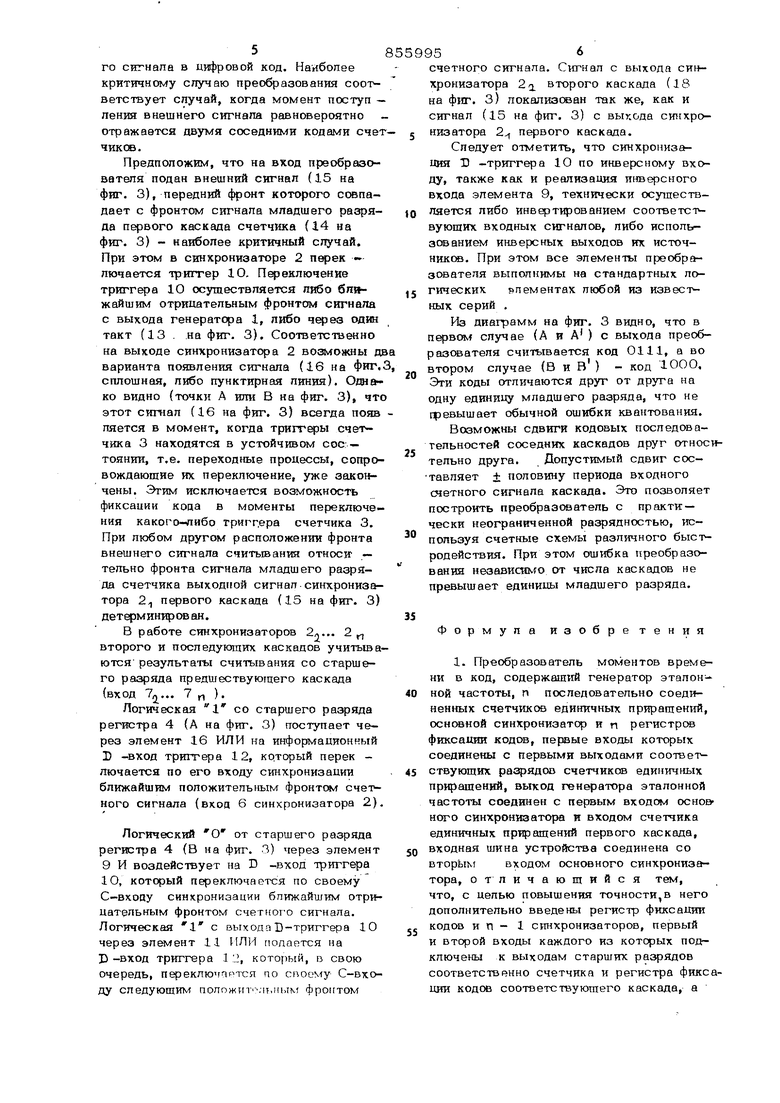

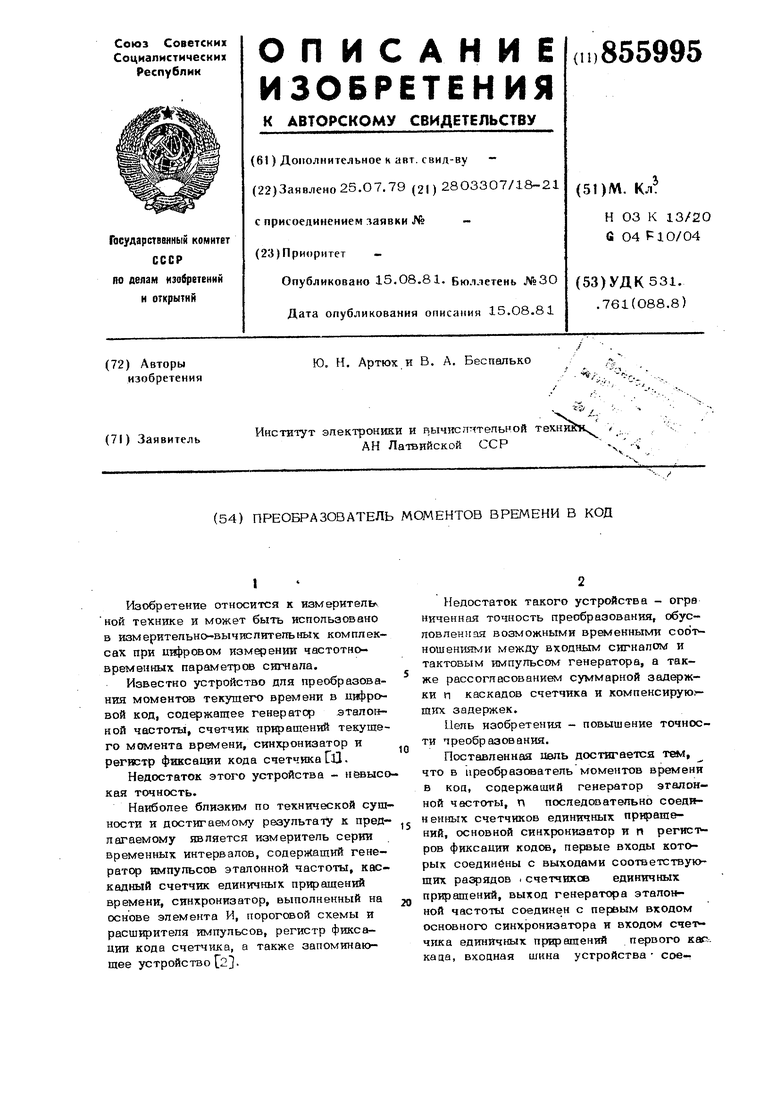

На фиг. 1 представлена блок-схема преобразователя моментов текущего времени в код; на фиг. 2 - блок-схема синхронизатора; на фиг. 3 - временные диапраммы работы преобразователя.

Преобразователь содержит генератор 1 эталонной частоты, cинxpoнизaтof)Ы 2 ... 2, счетчики 3 ... 3, единичных приращений, регистры 4 ... 4 фиксации кодов, где п 1,2, 3 ... - число каскадов преобразователя, дополнительный регистр 5 фиксации кодов.

Выход генератора ЭТЕШОННОЙ частоты подключен к входу 6 синхронизатора 2 и счетному таоду счетчика 3 . Вход б/,

59954

синхронизатора 2 ггодключен к шине, а вход 7 - к входу преобразователя. Входы 6/j ... 6f синхронизаторов 2.., 2 подключе 1ы соответственно к вы5 ходам старших разрядов счетчиков

3... 3 . Входы 7f,,. 7п - к выходам старших разрядов регистров 4... 4, , а входы 8,j... 8 - к выходам синхронизаторов 2,,... 2р . Информационные входы 10 и входы записи, регистров 4... 4 подключены соответственно к выходам счетчимэв

3t..o Зп и выходам синхронизаторов 2,...2п .

Синхронизатор 2 содержит элемент 9И,

первый D -триггер 10, элемент 11 ИЛИ и второй Б - триггер 12. Инверсный вход синхронизации триггера 10 и второй вход элемента 11 ИЛИ объединены и образуют первый вход 6, инверсный вход элемента 9 И и вход синхрониза1ши второго Б триггера 12 объединены и образуют второй вход 7, прямой вход элемента 9 И - третий вход 8 (фиг. 1 и 2), а выход D - триггера 12 - выход синхронизатора.

На фиг. 3 обозначены ; сигнал генератора 1 эталонной частоты, сигналы 14 иа кодовых выходах счетчика 3 и регистра 4 первого каскада, внешний сигнал 15 считывания, сигнал 16 на выходе

0 синхронизатора 2 первого каскада

{пунктирной пинией показан второй вариант сигнала), сигналы 17 на кодовых выходах счетчика 3/ и регистра 4 второго каскада, сигнал 18 на выходе синхро35 низатора 2Q второго каскада (пунктирной линией показан второй : вариант агнала, соответствующий аналогичному варианту сигнала .16).

Преобразователь работает следующим

40 образом (рассматривается случай двухкаскадного преобразователя, в котором в каждом каскаде и eютcя двухразрядные двоичные счетчики).

В исходном состоянии сигналы с выхода генератора 1 (13 на фиг. 3) подсчитываются каскадной цепочкой счетчиков 3. В каждом каскаде осуществляется синкронный счет, связь между каскадами - асинхронная, которая обуслав5Q Л1ша8т наличие запаздывания { на фиг. 3) между сигналами на выходе счетчиков первого и второго каскадов (14 и 17 на фиг. 3). При воздействии внешнего сигнала по входу 8 на выходах синхронизаторов 2 формируются сигналы фиксации текущего кода счетчиков в регистры 4, т.е. производится преобразование момента воздействия виешнего сигнала в цифровой код. Наиболее критичному случаю преобразования соответствует случай, когда момент поступ - Ленин внешнего сигнала равновероятно отражается двумя соседними кодами сче чиков. Предположим, что на вход преобразователя подан внешний сигнал (15 на фиг. 3), передний фронт которого совпадает с фронтом сигнала младшего разряда первого каскада счетчика (14 на фиг. 3) - наиболее критичный случай. При этом в синкронизаторе 2 перек - лючается триггер 1О. Переключение триггера 10 осуществляется либо бпйжайшим отрицательным фронтом сигнала с выхода генератора 1, либо через один такт (13 . .на фиг. 3), Соответственно на выходе синхронизатора 2 возможны да варианта появления сигнала (16 на фиг. сплошная, либо пунктирная линия). Одаако видно (точки А или В на фиг. 3), чт этот сигчал (16 на фиг. 3) всегда появ ляется в момент, когда триггфы счетчика 3 находятся в устойчивом состоянии, т.е. переходные процессы, сопро вождающие их переключение, уже закончены. Этим исключается возможность фиксации кода в моменты переключения какого-либо тригг,ера счетчика 3. При любом другом расположении фронта внешнего сигнала считьюания относи - тельно фронта сигнала младшего разряда счетчика выходной сигнал-синхронизатора 2 первого каскада (15 на фиг. 3) детермннщ)ован. В работе синхронизаторов 2,,... 2 второго и последующих каскадов учитыва ются результаты считывания со старшего р 13ряда предшествующего каскада (вход If,.. 7 и ). Логическая 1 со старшего разряда регистра 4 (А на фиг. 3) поступает через элемент 16 ИЛИ на информационный D -вход триггера 12, который перек лючается по его входу синхронизации ближайшим положительным фронтом счетного сигнала (вкод 6 синхронизатора 2) Логический О от старшего разряда регистра 4 (В на фиг. 3) через элемент 9 И воздействует на С -вход триггера Ю, который переключается по своему С-вхоцу синхронизации бпижайшим отрицательным фронтом счелсого сигнала. Логическая с выхода Б-триггера 10 через элемент 11 ИЛИ полается на D -вход триггера 1 2, который, в свою очередь, переключартсл по своему С-входу следующим положит:;11, фронтом 56 счетного сигнала. Сигнал с выхода синхронизатора 2i второго каскада (18 на фиг. З) покализсеан так же, как и сигнал (15 на фиг. 3) с выхода синхронизатора 2 первого каскада. Следует отметить, что синхронизация D -триггера 10 по инверсному входу, также как и реализация инверсного входа элемента 9, технически осутяествляется либо инвертированием соответствующих входных сигналов, либо использованием инверсных выходов их источнике. При этом все элементы преобразователя выполнимы на стандартных логических рпементах любой из извест ных серий . Из диаграмм на фиг. 3 видно, что в первок случае (А и А ) с выхода преобразс«ателя считывается код 0111, а во втором случае (В и в ) - код ЮОО, Эти коды отличаются друг от друга на одну единицу младшего разряда, что не сревышает обычной ошибки квантования. Возможны сдвиги кодовых последовательностей соседних каскадов друг относительно друга. Допустимый сдвиг составляет ± половину периода входного сметного сигнала каскада. Это позволяет построить преобразователь с практически неограниченной разрядностью, используя счетные схемы различного бысрродействия. При этом ошибка преобразования независимо от числа каскадов не превышает единицы младшего разряда. Формула изобретения 1. Преобразователь моментов времени в код, содержащий генератор эталонной частоты, п последовательно соединенных счетчиков единичных приращений, основной синхронизатор и п регистре фиксации код1ж, первые входы которых соединены с первыми выход 1ми соответ ствующих разрядов счетчиков еди1гичных приращений, выход генератора эталонной частоты соединен с первым входом основного синхрон1юатора и входом счетчика единичных приращений первого каскада, входная шина устройства соединена со BTOpbiM входом основного синхронизатора, отличающийся тем, что, с целью повышения точности,в него дополнительно введены регистр фиксации кодов и п - 1 синхронизаторов, первый и второй входы каждого из которых подключены к выходам старших разрядов соответственно счетчика и регистра фиксации кодов соответствующего каскада, а

третьи входы каждого из п - 1 синхрон заторов подключены к выходу синхронизатора предшествующего каскаца, выходы синхронизаторов соединены с входами считывания соответствующих регистров фиксации кодов, выходы фаз генератора подключены к входам дополнительного регистра фиксации кодов, вход считывания которого соединен с входной шиной устройства, третий вход основного синхронизатора соединен с выходедл старшего разряда дополнительного регистра фиксации кодов.

2. Преобразователь по п. 1, о т п ичающийся тем, что синхрониэа тор содержит элемент И, два 1) -irpmreра и элемент ИЛИ, причем первый вход синхронвэатора подключен к инверснаму входу синхронизации первого 1) - триггера и первому входу элемента ИЛИ второй вход синхронизатора подключен к инверсному входу элемента И и входу синхронизации второго -триггера, третий вход синхронизатора подключен к прямому входу элемента И, выход которого соединен с D - входом первого D -триггера, выход которого подключен КО второму входу элемента ИЛИ, выход которого соединен cD -входом второго D -триггера, выход которого является выходом синхронизатора.

3. Преобразователь по п. 1, о т л ичающийся тем, что генератор эталонной частоты содержит последова тельно соединенные активные элементы задержки, охваченные отрицательной обратной связью, причем выходы эле-

ментсе задержки образуют выходы фаз генератора,

№;точники информации, принятые во внимание при экспертизе Приборы для научных исследований , 1968, № 10, с. 85-87,

2. Авторское свидетельство СССР № 369542, кл,ео4Т: 10/О4 , 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-момент времени | 1981 |

|

SU970685A1 |

| Преобразователь код-момент времени | 1982 |

|

SU1034176A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Преобразователь код-временной интервал | 1979 |

|

SU822348A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2014 |

|

RU2570116C1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Устройство для передачи геофизической информации | 1987 |

|

SU1564579A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

Авторы

Даты

1981-08-15—Публикация

1979-07-25—Подача