Изобретение относится к электронике, может найти применение в системах и приборах автоматического контроля и регулирования и вычислительной технике для согласования цифровых устройств с исполнительными органами шагового типа, для формирования сиг налов, распределенных по нескольким каналам управления.

По основному авт.св. 663108 известен реверсивный преобразовательраспределитель импульсов, содержащий первый и второй триггеры основного и первый и второй триггеры вспомогательного {Регистра, элементы И и элементы ИЛИ, причем единичные выходы первого и второго триггеров основного регистра соединены с первыми входами первых элементов И, выходы которых связаны с нулевыми входсили соответствующего первого и второго триггера вспомогательного регистра, единичные входы первого и второго триггеров основного регистра соединены с выходами соответственно первого и В1 орого элементов ИЛИ, а выходы первых и вторых элементов И связаны с входами третьего элемента ИЛИ, а также третий, четвертый, пятый, шестой, седьмой, вос

мой, де в ятый, -де ся тый, одинн адцатый и двенадцатый элементы И, четвертый и пятый элементы ИЛИ, два инвертора, дополнительный триггер и блоки управления тактами и сийхронизации, причем выходы триггеров основного регистра соединены с входами блока синхронизации, первые входы вторых элементов И связаны с нулевы10ми выходами триггеров основного регистра ,. нулевые входы которых соединены соответственно с выходами четвертого и пятого элементов ИЛИ, вторые входы первых и вторых эле15ментов И связаны с выходом первого инвертора, выходы элементов И соединены соответственно с единичными входами первого и второго триггеров вспомогательного регистра,

20 выход третьего элемента ИЛИ связан с входом блока управления тактами и входом второго инверторар Еыход которого соединен с первыми входами одиннадцатого и двенадцатого

25 элементов И, единичный выход первого триггера вспомогательного регистра связан с первыми выходами четвертого, пятого, девятого и десятого элементов И, нулевой выход

30 первого триггера вспомогательного

регистра соединен с первыми входами третьего, шестого, седьмого и восьмого элементов И, единичный выход второго триггера вспомогательного регистра связан с входами третьего, четвертого, седьмого и десятого элементов И, нулевой выход второго триггера вспомогательного регистра соединен с вторими входами Пятого, шестого, восьмого и девятого элементов И , третьи входы третьего, четвертого, пятого и шес.того элементов И связаны с выходом одиннадцатого элемента И, третьи входы седьмого, восьмого, девятого и: десятого элементов И соединены с выходом двенадцатого элемента И, выход третьего элемента И связан с пер вым входом первого элемента ИЛИ второй вход которого соединен с выходом восьмого элемента И и входом блока управления тактами, выход четвертого элемента И связан с входом яблока управления тактами и первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента И, выход пятого элемента И связан с входом блока управления тактами и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом десятого элемента И, выход шестого элемента И связан с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом девятого элемента И и входом блока управления тактами, третьи входы первого и второго, а такхсе четвертого и пятого элементов ИЛИ соединены с соответствующими входами блока управления тактами, вторые входы одиннадцатого и двенадцатого элементов И связаны с входом первого инвертора и выходом блоке управления тактами, третьи входы одиннадцатого и двенадцатого элементов И соединены соответственно с нулевым и единичным выходами дополнительного триггера, а также с соответствующими входами блока управления тактами, а входы дополнительного триггера связаны с соответствующими выходами блока управления тактами l

Недостатками этого распределителя является то, что при работе в широком диапазоне температур и при разбросах временных характеристик элементов схемы в нем может возникнуть ложная отработка информации в момент прохождения заднего фронта входного импульса, а именно: первый инвертор разрешает перезапись информации через элементы И перезаписи на триггеры вспомогат€ льного регистра в тот момент, когда импульс на любом из выходов первого, второго четвертого и пятого элементов ИЛИ еще не закончился. В этом случае

триггеры вспомогательного регистра устанавливаются в следующее положение до окончания импульса на входах триггеров основного регистра, и устройство отрабатывает ложную информацию, которая затем опять переписывается на вспомогательный .регистр. Это снижает надехшость и требует подбора элементов по временным характеристикам.

Цель изобретения - повышение надежности работы.

Поставленная цель достигается тем что в устройство по авт.св. № 663108 дополнительно введен восьмивходоврй элемент ИЛИ, входы которого соответственно соединены с выходами третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого элементов И, а выход - с дополнительным входом первого инвертора.

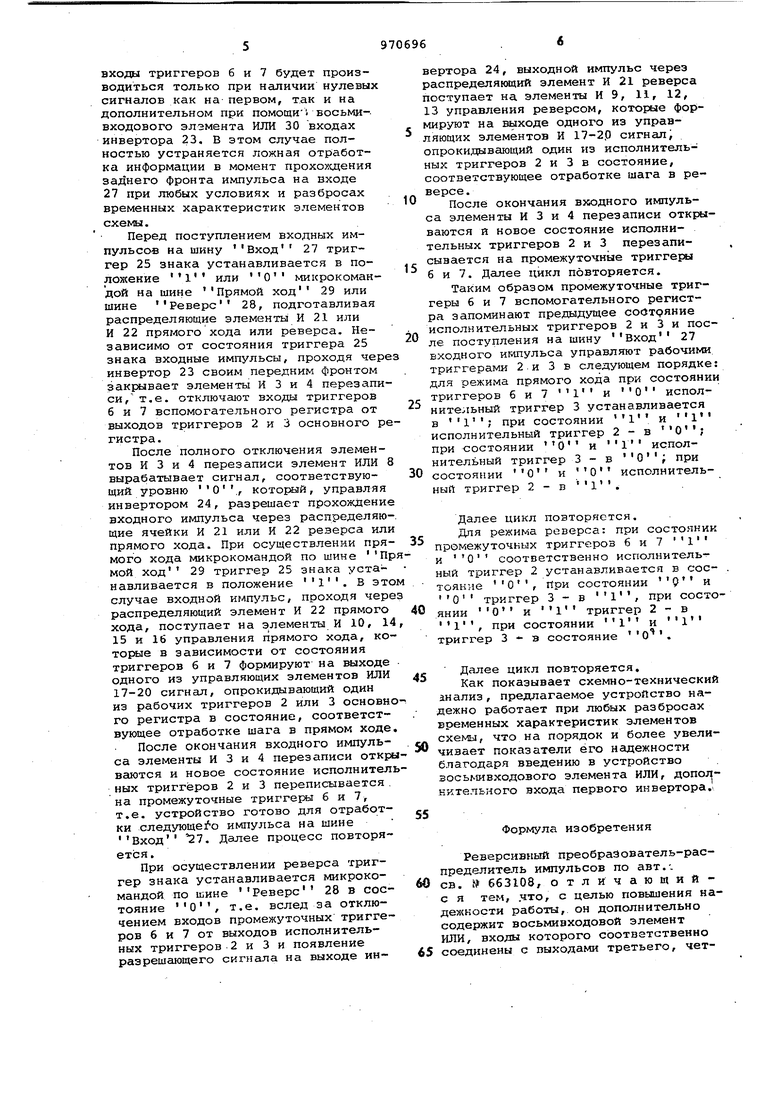

На чертеже показана функциональная схема предлагаемого реверсивного преобразователя-распределителя импульсов.

Реверсивный преобразователь-распределитель содержит блок 1 синхронизации/ построенный на переключателях и элементах И-Ш1И-НЕ и представляющий собой дешифратор;, первый и второй триггеры 2 и 3 основного регистра, первые элементы И 4, вторые элементы И 5, первый и второй триггеры 6 и 7 вспомогательного регистра, первый элемзнт ИЛИ 8, третий четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый элементы И 9-16, второй, третий, четвертый и пятый элементы ИЛИ 17-20, одиннадцатый и двенадцатый элементы И 21 и 22, первый инвертор 23 с до-, полнительным входом, второй инвертор 24, дополнительный триггер 25 знака, блок 26 управления тактами построенный на триггере со счетным входом и переключателях и представляющий собой управляемый делитель частоты, шину Вход 27, шину Реверс 28, шину Прямой вход 29 и восьмивходовой элемент 30 ИЛИ.

Устройство работает следующим iобразом.

При отсутствии импульсов на входной шине 27 через первый инвертор, 23 разрешается прохождение сигналов через элементы И 4 и 5 перезаписи только в том случае, когда на выходах элементов И 9-16 будут низкие потенциаль, т.е. входы триггеров 2 и 3 основного регистра -полностью отключатся от выходов триггеров 6 и 7 вспомогательного регистра. В этом случае разрешение переза,писи информации через элементы И 4 и 5с выходов триггеров 2 и 3 на

входы триггеров 6 и 7 будет производиться только при наличии нулевых сигналов как на первом, так и на дополнительном при помощи восьми-входового элзманта ИЛИ 30 входах инвертора 23. В этом случае полностью устраняется локная отработка информации в момент прохохсдения заднего фронта импульса на входе 27 при любых условиях и разбросах временных характеристик элементов схекы.

Перед поступлением входных импульсов на шину Вход 27 триггер 25 знака устанавливается в положение 1 или О микрокомандой на шине Прямой ход 29 или шине Реверс 28, подготавливая распределяющие элементь И 2.1 или И 22 прямого хода или реверса. Независимо от состояния триггера 25 знака входные импульсы, проходя чере инвертор 23 своим передним фронтом закрывает элементы И 3 и 4 перезаписи, т.е. отключают входы триггеров 6 и 7 вспомогательного регистра от выходов триггеров 2 и 3 основного регистра.

После полного отключения элементов И 3 и 4 перезаписи элемент ИЛИ 8 вырабатывает сигнал, соответствующий уровню О,, , управляя инвертором 24, разрешает прохождение входного импульса через распределяющие ячейки И 21 или И 22 реверса или прямого хода. При осуществлении прямого хода микрокомандой по шине Прмой ход 29 триггер 25 знака устанавливается в положение . В это случае входной импульс, проходя чере распределяющий элемент И 22 прямого хода, поступает на элементы И 10, 14 15 и 16 управления прямого хода, которые в зависимости от состояния триггеров 6 и 7 формируют на выходе одного из управляющих элементов ИЛИ 17-20 сигнал, опрокидывающий один из рабочих триггеров 2 или 3 основного регистра в состояние, соответствующее отработке шага в прямом ходе.

После окончания входного импульса элементы И 3 и 4 перезаписи открывгиотся и новое состояние исполнительных триггеров 2 и 3 переписывается . на промежуточные триггеры 6 и 7, т.е. устройство готово для отработки следующез о импульса на шине Вход 27. Далее процесс повторяется.

При осуществлении реверса триггер знака устанавливается микрокомандой по шине Реверс 28 в состояние О, т.е. вслед за отключением входов промежуточных триггеров 6 и 7 от выходов исполнительных триггеров 2 и 3 и появление разрешающего сигнала на выходе ин-

вертора 24, выходной импульс через распределяющий элемент И 21 реверса поступает на. элементы И 9, 11, 12, 13 управления реверсом, которые формируют на выходе одного из управляющих элементов И 17-2,0 сигнал i опрокидывающий один из исполнительных триггеров 2 и 3 в состояние, соответствующее отработке шага в реверсе.

После окончания вхюдного импульса элементы И 3 и 4 перезаписи открываются и новое состояние исполнительных триггеров 2 и 3 перезапи- , сывается на промежуточные триггеры 6 и 7. Далее цикл повторяется.

Таким образом промежуточные триггеры 6 и 7 вспомогательного регистра запоминают предыдущее соотряние исполнительных триггеров 2 и 3 и после поступления на шину Вход 27 входного импульса управляют рабочими триггерами 2 и 3 в следующем порядке: для режима прямого хода при состоянии

О исполтриггеров 6 и 7 1

и

нительный триггер 3 устанавливается

и

; при состоянии

исполнительный триггер 2 - в О; при состоянии О и исполнительный триггер 3 - в О ; при

30 состоянии О и О ный триггер 2 - в 1

Далее цикл поэторяется.

Для режима реверса: при состоянии

5 промежуточных триггеров 6 и 7 1 и О соответственно исполнитель ный триггер 2 устанавливается в сое- . О , состоянии 9 и

, При состоянии

тояиие

О триггер 3 - в , при состо3 -

0 1 триггер 2 - в янии О и

, при состоянии 1 и триггер 3 - в состояние

Далее цикл повторяется.

Как показывает схемно-технический анализ, предлагаемое устройство надежно работает при любых разбросах временных характеристик элементов схемы, что на порядок и более увеличивает показатели его надежности благодаря введению в устройство зосьмивходового элемента ИЛИ, дополнительного входа первого инвертора..

55

Формула изобретения

Реверсивный преобразователь-распределитель импульсов по авт...

60 св. 663108, отличающий с я тем, .что, с целью повышения надежности работы, он дополнительно содержит восьми входовой элемент ИЛИ, входы которого соответственно

65 соединены с выходами третьего, чет

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь распределитель импульсов | 1971 |

|

SU663108A1 |

| Реверсивный преобразователь-распределитель импульсов | 1982 |

|

SU1078617A2 |

| Измеритель временных интервалов | 1982 |

|

SU1034012A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР С ЗАПОМИНАЮЩИМ УСТРОЙСТВОМ НА МАГНИТНОМ БАРАБАНЕ | 1966 |

|

SU182414A1 |

| Устройство для отображения инфор-МАции HA эКРАНЕ элЕКТРОННО-лучЕВОйТРубКи | 1979 |

|

SU807364A1 |

| Адаптивный эхокомпенсатор | 1989 |

|

SU1665520A1 |

| Устройство для управления маркером на экране электронно-лучевой трубки | 1988 |

|

SU1689982A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Система динамической синхронизации и корректировки рангов объектов в АСУ | 1985 |

|

SU1305630A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-10—Подача