(54) РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ-РАСПРЕДЕЛЖЕЛЬ ИМПУЛЬСОВ

элементов ИЛИ, входы элементов И соединены с входами третьего элемента ИЛИ, дополнительно введены третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый элементы И, четвертый и пятый : элементы ИЛИ, два инвертора, дополнительный .триггер, блоки синхронизации и управления тактами, причем выходы триггеров основного регистра соединены с входами блока синхронизации, первы1г входы вторых элементов.И соединены с . нулевыми выходами триггеров основного регистра, нулевые входы которых соединены соответстВЙ1НО с выходами четвер1ого и пятого элементов ИЛИ, вторые входы первых и вторь1х элементов И соединены с выходом первого инвертора, выходы вторых элемейтов И соединены соответственно с единичными входами первбго и второго триггеров вспомогательного регистра, выход третьего элемента ИЛИ соединен с входом блока управления тактами и входом второго инвертора, выход которого соединен с первыми входами одиннадцатого и двенадцатого элементов И, единичный выход первого триггера вспомогательного регистра соединен с первыми выходами четвертого, пятого, девятого и десятого элементов И, нулевой . выход первого триггера вспомогательного регистра соединен с первыми входами третьего, шестого, седьмого и восьмого- элементов И, единичный «ыход второго триггера вcпoмoгaтeльнof 6 регистра соединен с вторыми входами третьего, четвертого, седьмого и десятого элементов И, нулевой выход второго триггера вспомогательного регистра соединен с вторыми входами пятого, шестого, восьмого и девятого элементов И-, третьи входы третьего, четвертого, пя±ого и шестого элементов И соединены с выходом одиннадцатого элемента И, третьи входы седьмого, вос1.мого, девятого и десятого элементов И соеданены с выходом двенадцатого элемента И, вьОсод третьего элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходов восьмого элемента И и входом блока управления тактами, выход четвертого элемента И соединен с выходом блока управления тактами и первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента И, выход пятого элемента И соединен с входом блока управления тактами и с первым входом чет вертого элемента ИЛИ, второй вход которого соединен с выходом десятого элемента И, выход шее того элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом девятого элементу И и входом блока управления тактами, третьи входы первого и втр.рого, а также четвертого и пятого элементов ИЛИ ШеДиненыс сЬбТветствуюицши входами блока управления тактами, вторые входы одиннадцатого и двенадцатого элементов И соединены с входом

первого инвертора и выходом блока управления тактами, третьи входы одиннадцатого и двенадца того элементов И соединены соответственно с нулевым и единичным выходами дополнительного триггера, а также с соответствующими входами блока управления тактами, входы дополнительного триггера соединены с соответствуюшими выходами блока управления тактами,

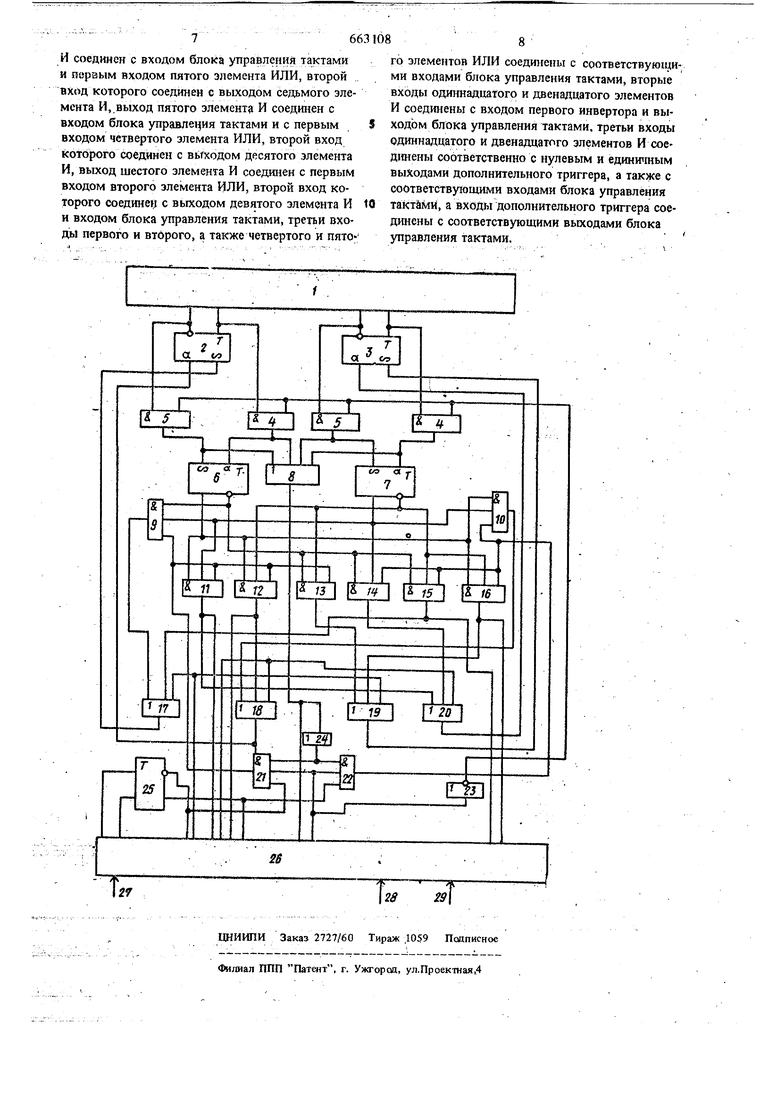

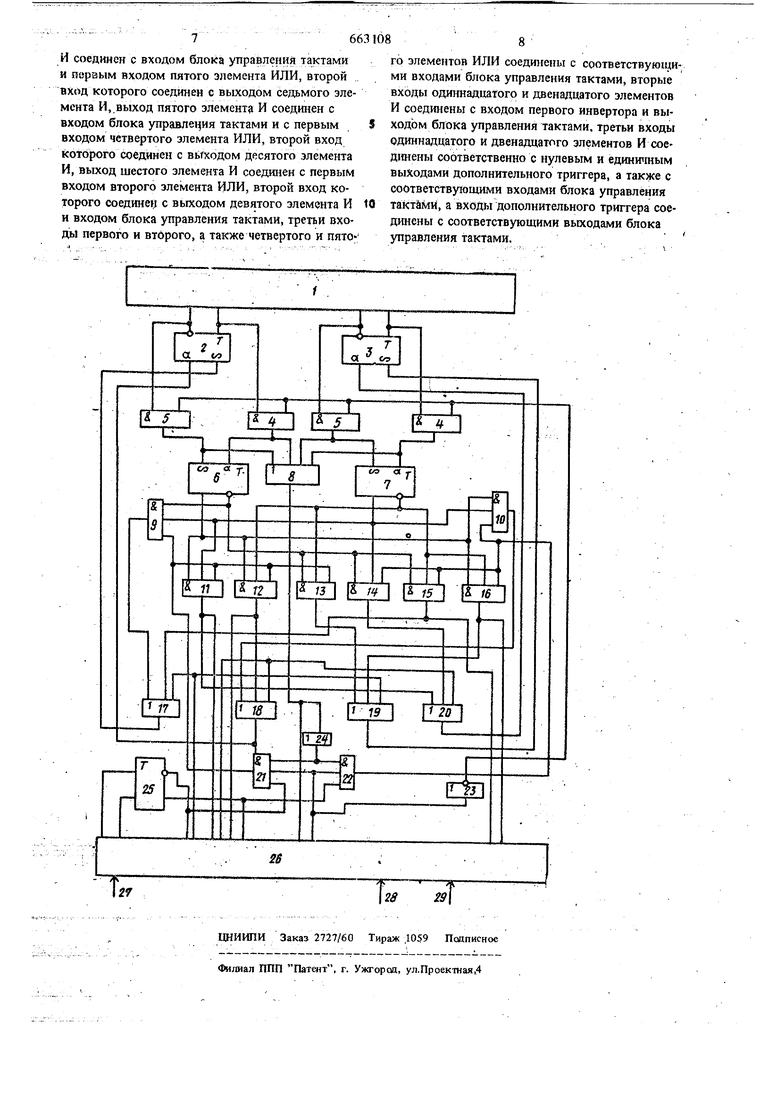

На чертеже представлена блок-схема предлагаемого реверсивного преобразователя-распределителя

Реверсивный преобразователь-распределитель содержит блок 1 синхронизации, первый и второй (триггеры 2,3 основного регистра, первые элементы 4 И, вторые элементы 5 И, первый и триггеры 6, 7 вспомогательного регистра, третий элемент 8 ИЛИ, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, и десятый элементы 9, 10, 11, 12, 13, 14, 15, 16 И, первый, второй, четвертый и пятый элементы 17, 18, 19, 20 ИЛИ, одиннадцатый и двенадцатый элементы 21, 22 И, первый и второй инверторы 23, 24, дополнитель;ный триггер 25 знака, блок 26 управления тактами, шину 27 Вход, шину 28 Реверс, шину 29 Прямой код.

Устройство работает следуюшим образом.

При отсутствии импульсов на шине 27 Вход через первый инвертор 23 разрешается прохождение сигналов через элементы 4, 5 И перезаписи, и информация с выходов исполнительных тригге- ров 2, 3 основного регистра переписывается на промежуточные триггеры 6, 7 вспомогательного регистра.

Перед поступлением входных импульсов на шину 27 Вход триггер 25 знака устанавливается в соответствующее положение 1 или О микрокомандой на шине 29 Прямой вход или шине 28 Реверс, подготавливая соответственно распределяющие элементы 21 И или 22 И прямого хода или реверса. Неэависимо от состояния триггера 25 знака входные импульсы, проходя через инвертор 23 своим передним фронтомзакрывают элементы 3, 4 И перезаписи, то есть отключают входы триггеров 6, 7 вспомогательного регистра от выходов триггеров 2, 3 основного регистра. ; После полного отключения элементов 3, 4 И перезаписи собирательный элемент 8 ИЛИ вырабатывает сигнал, соответствующий уровню О, который управляя инвертором 24 рафешает прохождение входного импульса через распределяюшие ячейки 21 И или 22 И реверса или прямого хода.

При осуществлении прямого хода микрокомандой по шине 29 Прямой ход триггер 25 знака устанавливается в положение 1. В этом случае входной импульс, проходя через распределяющий элемент 22 И прямого хода, поступает на элементы 10, 14, 15, 16 И управления прямого хода, которые в зависимости от состояния триггеров 6, 7 формируют на выходе одного из управляющих элементов 17, 18, 19, 20 ИЛИ сигнал, опрокадывающий один из рабочих триггеров 2 или 3 осно ного регистра в состояние, соответствующее отр ботке шага в прямом ходе. После окончания входного импульса элементы 3, 4 И перезаписи открываются и новое состояни исполнительных триггеров 2, 3 переписывается н промеясуточные триггеры 6, 7, то есть устройство готово для отработки следующего импульса на шине 27 Вход. Далее процесс повторяется. При осуществлении реверса триггер 25 знака устанавливается микрокомандой по шине 28 Реверс в состояние О, то есть вслед за отклю чением входов промезкуточных триггеров 6, 7 от выходов исполнительных триггеров 2, 3 и появле ния разрешающего сигнала на выходе инвертора 24, выходной импульс через распределяющий зле мент 21 И реверса поступает на элементы 9, 11, 12, 13 И управления реверсом, которые формируют на выходе одного из управляющих элемен тов 17, 18, 19, 20 ИЛИ сигнал, опрокидывающий один из исполнительных триггеров 2, 3 в состояние, соответствующее отработке шага в реверсе После окончания входного импульса злементы 3, 4 И п езаписи открываются и новде состояние исполнительных триггеров 2, 3 переписывается на промежуточные триггеры 6, 7. Далее цикл повторяется. Таким образом промежуточные триггеры 6, 7 вспомогательного регистра запоминают предыдущие состояния исполнительных триггеров 2, 3 и после поступления на ашну 27 Вход входаого импульса управляют рабочими триггерами 2, 3 в следующем порядке: для режима прямого хода: при состоянии триггеров 6, 7 1 и О соответ ственно исполнительный триггер 3 устанавливается в состояние 1, при состоянии промежуточных триггеров 6, 7 1 и 1 исполнительный триггер 2 устанавливается в О, при состоянии промежуточных триггеров 6, 7 О и 1 исполнительный триггер 3 устанавливается в О, при состоянии промежуточных триггеров 6, 7 О и О исполнительный триггер 2 устанавливается в Г . Далее цикл повторяется. Для режима реверса: при состоянии про- i межуточных триггеров 6, 7 1 и О соответственно исполнительный триггер 2 устанавливается в состояние при состоянии триггеров 6, 7 р триггер 3 устанавливается в состояние .1, при состоянии промежуточных триггеров 6, 7 О и Г исполнительный триггер 2 устанавливается в состояние 1, при состоянии промежуточных триггеров 6, 7 1 и 1 исполнительный григгер 3 устанавливается в состояние О. Далее цикл повторяется. Формула изобретения ..Iч Реверсивный преобразователь-распределитель импульсов, содержащ1 й первьш и второй триггеры основного и первый и второй триггеры вспомогательного регистров, элементы И и элементы ИЛИ, причем единичные выходы первого и второго триггеров основного регистра соединены с первыми входами первых элементов И, выходы которых соединены с нулевьши вводами соответственно первого и второго триггера вспомогательного регистра, единивдые входы первого и вюрого триггеров основного регистра соединены с выходами соответственно первого и второго элементов ИЛИ, а BbixojQ(bi первых и вторых элементов И соединены с входами третьего элемента ИЛИ, отличающийся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый элементы И, четвертый и пятый элементы ИЛИ, даа инвертора, дополнительный триггер и блоки управления тактами и синхронизации, причем выходь триггеров основного регистра соединены с входами блока синхронизации, первые входа вторых элементов И соединень с нулевыми выхоДаМй триггерой основного регистра, нулевые вхоДй kotojpbix соединены соответственно с выходами четвертого и пятого элементов ИЛИ, вторые входы первых и вторых элементов И соединены с выходом первого инвертора, выходы вторых элементов И соединены соответственно с единичными входами первого и второго триггеров вспомогательного регистра, выход третьего элемента ИЛИ соединен с входом блока управления тактами и входом второго инвертора, выход которого соединен с первыми входами одиннадцатого и двенаддагого зяементов И, единичный выход первого триггера вспомогательного регистра соединен с первыми выходами четвертого, пятого, девятого и десятого элементов И, нулевой выход первого триггера вспомогательного регистра соединен с первыми входами третьего, шестого, седьмого и восьмого элементов И, единичный выход второго триггера вспомогательного регистра соединен с вторыми входами третьего, четвертого, седьмого и десятого элементов И, нулевой выход второго триггера вспомогательного регистра соединен с вторыми входами пятого, шестого, восьмого и девятого элементов И, третьи ходы третьего, четвертого, пятого и шестого элеентов И соединены с выходом одиннадцатого лемента И, третьи входы седьмого, восьмого, евятого и десятого элементов И соединены с выодом двенадцатого элемента И, выход третьего лемента И соединен с первым входом первого лемента ИЛИ, второй вход которого соединен с ыходом восьмого элемента И и входом блока правления тактами, выход четвертого элемента

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь-распределитель импульсов | 1981 |

|

SU970696A2 |

| Реверсивный преобразователь-распределитель импульсов | 1982 |

|

SU1078617A2 |

| Адаптивный эхокомпенсатор | 1989 |

|

SU1665520A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Устройство определения конца блока циклического кода | 1982 |

|

SU1061279A1 |

| Система записи и воспроизведения видеосигнала | 1990 |

|

SU1783635A1 |

| Устройство для отображения инфор-МАции HA эКРАНЕ элЕКТРОННО-лучЕВОйТРубКи | 1979 |

|

SU807364A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Устройство кодирования информации для записи на магнитный носитель | 1982 |

|

SU1045382A1 |

Авторы

Даты

1979-05-15—Публикация

1971-07-05—Подача