Изобретение относится к цифровой вычислительной технике и предназнач ется для использования в составе цифровых вычислительных машин (ЦВМ).

Известны арифметические устройства (АУ) параллельного действия, содержащие основной и вспомогательный триггерные регистры сумматора, схемы формирования переносов, основной и вспомогательный триггерные регистры множителя (частного) и логические элементы И, ИЛИ, обеспечивающие прием и пересылку кодов между регистрами Г ..

Недостатками их являются сложност

и низкое быстродействие.

Наиболее близким к предлагаемому устройству является арифметическое устройство, содержащее регистр множи теля, накапливающий регистр, сумматор и регистр множимого со схемой парафазного приема кода, содержащей логические элементы И, ИЛИ, НЕ Г2 Известные арифметические устройства обеспечивают выполнение операции умножения только двух сомножителей одновременно. Это приводит к тому, что на каждое умножение требуется затратить время для приема одно

го из сомножителей и выполнения не посредственно операции умножения, т.е. в известном АУ не обеспечивается одновременное выполнение операции умножения нескольких множимых на один множитель.

Цель изобретения - упрощение устройства и повыщение быстродействия.

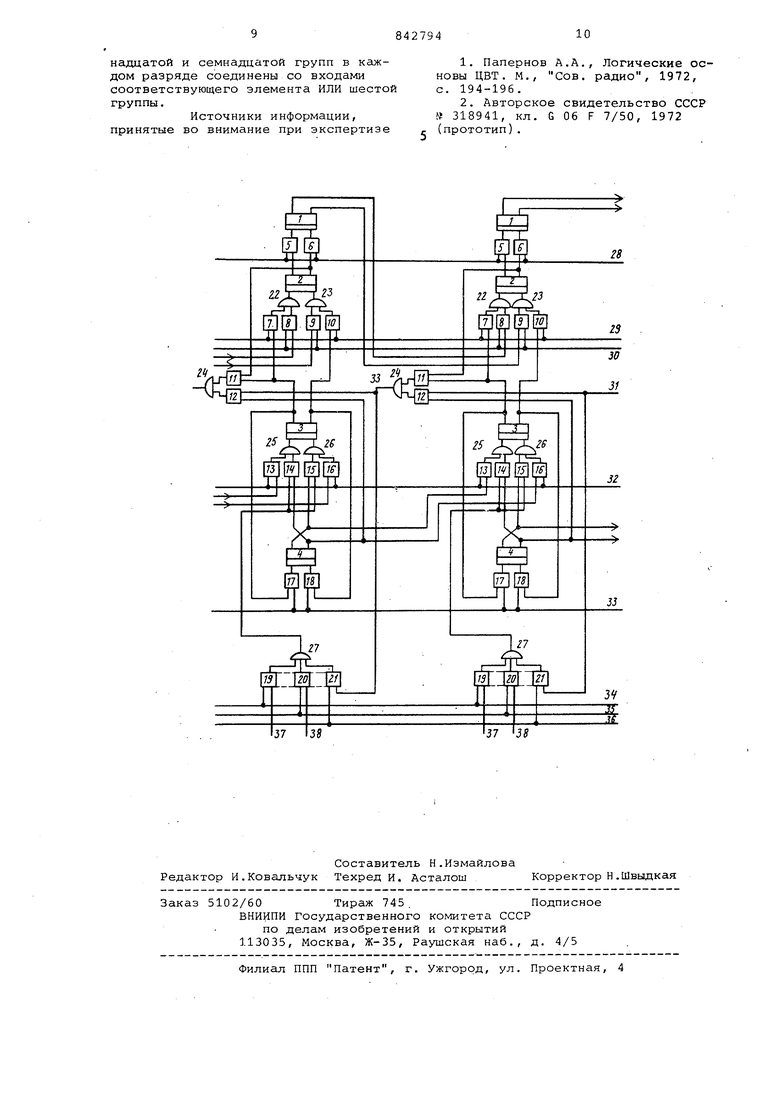

Поставленная цель достигается тем, ЧТО в арифметическое устройство содержащее основной и вспомогательны регистры сумматора, основной и вспомогательный регистры множителя, элементы И, ИЛИ, управляющие шины уст-, ройства, причем входы каждого разряда основного регистра множителя соединены с выходами соответствующих .элементов И первой и второй групп, первые входы которых подключены соответственно к инверсному и прямому выходам соответствующего разряда вспомогательного регистра множителя, а вторые входы - к шине управления записью кода в основной регистр множителя, входы каждого разряда вспомогательного регистра подключены к выходам соответствующих элементов ИЛИ первой и второй групп, входы котооых подключены к выходам соответствукхдих элементов И третьей, четвертой, пятой и шестой групп, первые входы элементов И третьей и шестой групп и первые входы элементов И четвертой и пятой групп подключены соответственно к шине управления записью кода в вспомогательный регистр множителя и к шине управления сдвигом кода в регистре множителя, вторые входы соответствуняцих элементов И четвертой и пятой групп в каждом раэряде соединены соответственно с инверсным и прямим входом последующего разряда основного регистра множителя, вторые входы соответствующих элементов И третьей и шестой групп соединены соответственно с инверсным и прямым выходами соответствующего разряда основного регистра сумматора, выходы которого соединены с выходами соответствующих элементов ИЛИ третьей и четвертой,групп, входы которых соединены с выходами соответствующих эле ментов И седьмой, восьмой, девятой и десятой групп, первые входы элементов И седьмой и десятой групп в каждом разряде подключены к шине управления сдвигом кода в регистрах сумматора, вторые входы - соответственно к инверсному и прямому выходам после дующего разряда вспомогательного регистра сумматора, первые входь элеме тов И восьмой и девятой групп соединены с прямым и инверсным выходами соответствующего разряда вспомогательного регистра сумматора, вторые входы объединены и соединены с выхо.дом соответствующего элемента ИЛИ пя той группы, входы которого соединены с выходами.соответствующих элементов И одиннадцатой, двенадцатой и тринад цатой групп,.первые входы которых подключены соответственно к первой, второй и третьей шинам управления сложением по модулю 2, вторые входы элементов И одиннадцатой и двенадцатой групп подключены к шинам приема соответствующего инверсного и прямого кода, входы каждого разряда вспомогательного регистра сумматора соед нены с выходами соответствующих элементов И четырнадцатой и пятнадцатой групп, первые входы которых подключе ны к третьей шине управления записью кода в вспомогательный регистр сумма тора, вторые входы соединены соответ ственно с инверсным и прямым выхода-, ми .соответствующего разряда основного регистра сумматора, в него введены шестнадцатая и семнадцатая группы элементов И и шестая группа элементов ИЛИ., причем в каждом разряде пер вый вход элемента И шестнадцатой гру пы подключен к прямому выходу соотве ствукддего разряда вспомогательного регистра множителя, второй вход - к инверсному выходу соответствующего разряда основного регистра сумматора первый вход элемента И семнадцатой группы в каждом разряде, кроме младшего разряда, соединен с выходом элемента ИЛИ шестой группы предыдущего разряда и вторым входол - соответствующего элемента И тринадцатой группы, первый вход элемента И семнадцатой группы мпадшего разряда подключен к шине сквозного переноса, второй вход элемента И семнадцатой группы соединен с прямым выходом соответствующего разряда вспомогательного регистра сумматора, выходы элементов И шестнадцатой и семнадцатой групп в каждом разряде соединены со входами соответствующего элемента ИЛИ, шестой группы. На чертеже,Приведена функциональная схема двух двоичных разрядов арифметического устройства параллельного действия, Схема содержит триггеры (Тр) 1 основного регистра множителя (частного) , типа RS; триггеры 2 вспомогательного регистра множителя (частного/, типа RS,триггеры 3 основного регистра сумматора, типа RS, триггеры 4 вспомогательного регистра сум-матора, типа RS, логические элемен-. ты И 5-21; логические Элементы ИЛИ 22-27; шину 28 управления (ШУ) пересылкой кода из вспомогательного в основной регистр множителя, шину 29 управления пересылкой кода из основного регистра сумматора во вспомогательный регистр множителя, шину 30 управления сдвигом кода вправо в регистре множителя, шину 31 сквозного переноса, шину 32 управления сдвигом кода вправо в регистре сумматора, шина 33 управления пересылкой кода из основного во вспомогательный регистр сумматора, шину 34 управления выполнением элементарной операции (ЭО) сложения по модулю 2 с инверсным кодом ВТОР9ГО слагаемого, шину 35 управления.выполнением ЭО сложения по модулю 2 с прямым кодом второго слагаемого, шину 36 управления выполнением ЭО второго слагаемого по модулю 2, шину 37 приема (ШП) инверсного кода второго слагаемого, . шину 38 приема прямого кода второго слагаемого.. Рассмотрим работу предлагаемого АУ на примере выполнение операции сложения двух положительных чисел, представленных в двоичном коде, при этом код первого слагаемого хранится в основном триггерном регистре сумматора (триггеры 3), а код второго слагаемого поступает в устройство по шине 38 приема кода. По первому временному такту . (t } выполняется ЭО пересылки кода первого слагаемого из Тг 3 во вспомогательные регистры множителя и сумматора (Тг2,Тг4). Для выполнения этой ЭО на ШУ 29 и ШУ 33 одновременно подаются исполнительные импульсы, в результате чего в Тг2 и Тг4 будут занесены коды одинаковых чисел. По второму временному такту (t) выполняется ЭО первого сложения по модулю 2 кода первого слагаемого, хранящегося в Тг2 ТгЗ и Тг4, и код второго слагаемого, поступающего в АУ по шине 38. Для выполнения этой ЭО на ШУ 35 подается исполнительный импульс. В тех двоичных разрядах АУ в которых на шине 38 имеется высокий (низкий) потенциал, соответствующий коду единицы, исполнительный импульс по цепи И 20, ИЛИ 27 поступает на счетный вход ТгЗ и изменяет его сос тояние, т.е. выполняет сложение кодов по модулю 2. После переключения ТгЗ начинает формироваться и распрос траняться в сторону старших разрядов потенциал сквозного переноса. По третьему временному такту осуществляется пересылка результата ело жения кодов по модулю 2, хранящегося в ТгЗ, в Тг4. Эта элементарная операция необходима для обеспечения фор мирования сквозного переноса и для подготовки выполнения ЭО второго ело жения по модулю 2. По четвертому временному такту (tf ) после завершения распространения потенциала переноса на ВУ 36 подается исполнительный импульс. В тех двоичных разрядах АУ, в которых по шине 31 из младшего разряда поступает потенциал переноса, исполнительный импульс по цепи И 21, ИЛИ 27 поступает на счетный вход ТгЗ- и выполн ет ЭО второго сложения кода по модулю 2. Четвертый такт завершает выпол нение операции сложения двух кодов. операция вычитания, кодов осуществ ляется аналогично рассмотренному выше выполнению операции сложения. Отли ие состоит в том,/ что по второму временному такту на счетный вход ТгЗ подается код с ШП 37 (а не ПШ 38). Операция пересылки кода из основного регистра множителя в основной регистр сумматора осуществляется за два временных такта.. По первому временному такту выполняются ЭО пересылки кода из основ ного регистра множителя во вспомогательный регистр (Тг1, Тг2) и установ ка в нулевое состояние основного и вспомогательного регистров сумматора (ТгЗ, Тг4). В результате выполнения этих ЭО в тех разрядах АУ, в которых Тг2 установлены в единичное состояние, вырабатывается потенцигш сквозного переноса, поступающий И 21 старшего разряда, По второму временному такту осуществляется непосредственная передача кода регистра множителя в основной регистр сумматора, осуществлявмая за счет поступления исполнительрого сигнала на ШУ 36. Если на первы 1аход И 21 поступил потенциал сквозного переноса из младшего разряда, то сигнал по цепи И 21 ИЛИ 27 поступает на счетный вход ТгЗ и изменяет его состояние на инверсное, что эквивалентно пересылке кода из Тг1 в ТгЗ. Операция умножения кодов в предлагаемом устройстве выполняется путем последовательных сложений кода, хранящегося в регистре сумматора, и кода, поступающего по ШП 38, и сдвигов кодов, хранящихся в регистрах сумматора и множителя, вправе на один разряд. Выполнение сдвигов кодов в регистрах сумматора и множителя осуществляется за два временных такта. По первому такту код основного регистра множителя (Тг1) пересылается со сдвигом на один разряд второго во вспомогательный регистр множителя {Тг2). Для выполнения этой ЭО на ШУ 30 подается исполнительный импульс. По второму такту код числа, хранящийся в триггерах вспомогательного регистра множителя (Тг2), пересылается в основной триггерный регистр множителя (Тг1). Для выполнения этой ЭО на ШУ 28 подается- исполнительный импульс. Сдвиг кода в регистре сумматора осуществляется аналогичным образом. Отличие состоит только в тОм, чтЬ пересылка кода во вспомогательный регистр выполняется без сдвига, а пересылк-а кода из вспомогательного регистра в основной выполняется со сдвигом кода.на один разряд вправо. Для выполнения названных ЭО испо.-;-, нительные импульсы последовательно передаются на ШУ 33 и 32. При условии, что код множителя хранится в основном регистре множителя (Тг), код множимого поступает в АУ по ШП 38, а регистры сумматора установлены в нулевое состояние на первом этапе выполнения операции умножения код регистра множителя сдвигается вправо до тех пор, пока в последнем (младшем) разряде регистра не появится код единицы. После этого сдвиги кода в регистре множителя прекращаются и выполняется операция сложения кода сумматора с кодом,.поступающим по ШП 38. Операция сложения кодов в ходе выполнения операции умножения идентична рассмотренной отдельной операции сложения.После выполнения операции сложения производится одновременный сдвиг кодов сумматора и регистра множителя вправо на один разряд. Если после выполнения ЭО сдвига кодов на один разряд вправо в последнем разряде регистра множителя снова хранится код единицы, то операции сложения и сдвига повторяются. Если же в последнем регистра хранится код нуля, то выполняется повторЕлай сдвиг кодов

регистров сумматора и множителя до тех пор, пока не будет сделано число сдвигов, равное числу двоичных разрядов регистра множителя.

Предлагаемое устройство обеспечивает выполнение групповой операциц умножения кодов, которая заключается в умножении ряда кодов множимого на один множитель без прекращения процесса умножения на последовательный вход новых сомножителей Если в известных устройствах операция умножения реализует соотношение Z XY, то в предлагаемом устройстве можно выполнять операцию Z X (Y , Yri , . , . Y,() . При этом не требуется прерывать.процесс умножения для ввода и хранения в одном из - регистров АУ очередного множимого

Yl.Y.i,...

Указанные коды множимых могут.храниться в любых регистрах ЭВМ, имеющих связь с АУ через элементы ИЛИ 27.

Операция группового умножения обеспечивает сокращение времени выполнения операций умножения ряда сомножителей на один множитель приблизительно в 1,5 раза.

формула изобретения

Арифметическое устройство, содержащее основной и вспомогательный регистры сумматора, основной и вспомогательный регистры множителя, элементы И, ИЛИ, управляющие шины устройства, причем входы каждого разряда основного регистра множителя соединены с выходами соответствующих элементов И первой и второй групп, .первые входы которых подключены соответственно к инверсному и прямому выходам соответствующего разряда вспомогательного регистра множителя, а вторые входы - к шине управления записью кода в основной регистр множителя , входы каждого разряда вспомогательного регистра подключены к выходам соответствующих элементов ИЛИ первой и второй групп, входы которых подключены к выходам соответствующих элементов И третьей, четвертой, пятой и шестой групп, первые входы элементов И третьей и шестой групп и первые входы элементов И четвертой и пятой групп подключены соответственно к шине управления записью кода в вспомогательный регистр множителя и к шине управления сдвигом кода в регистре множителя, вторые входы соответствующих элементов И четвертой и пятой групп в каждом разряде соединены соответственно с инверсным и прямым выходом последующего разряда основного регистра множителя, вторые входы соответствукяцих элементов И третьей и шестой групп соединены соответственно с

инверсным и прямым .выходами соответствующего разряда основного регистра сумматора, выходы которого соединены с выходами соответствующих элементов ИЛИ третьей и четвертой групп входы которых соединены с выходами соответствующих элементов И седьмой, восьмой, девятой и десятой групп, первые входы элементов И седьмой и десятой групп в каждом разряде подключены к шине управления сдвигом кода в регистре сумматора, вторые входы - соответственно к инверсному и прямому выходам пЬследующего разряда вспомогательного регистра сумматора, первые входы элементов И восьмой и девятой групп соединены с прямым и инверсным выходами соответствующего разряда вспомогательного регистра сумматора, вторые входы объединены и соединены с выходом соответствующего элемента ИЛИ пятой группы, входы которого соединены с выходами соответствующих элементов И одиннадцатой, двенадцатой и тринадцатой групп, первые входы которых подключены соответственно к первой, второй и третьей шинам управления по модулю 2, вторые входы элементов И одиннадцатой и двенадцатой групп подключены к шинам приема соответственно инверсного и прямого кода, входы каждого разряда вспомогательного регистра сумматора соединены с выходами соответствующих элементов И четырнадцатой и пятнадцатой групп, первые входы которых подключены к третьей шине управления записью кода в вспомогательный регистр сумматора, вторые входы соединены соответственно с инверсным и прямым выходами соответствующего, разряда основного регистра сумматора, отличающееся тем, что, с целью повышения быстродействияи уменьшения количества необходимого оборудования, в него введены шестнадцатая и семнадцатая группы элементов И и шестая группа элементов ИЛИ, причем в каждом разряде первый вход элемента И шестнадцатой .группы подключен к-прямому выходу соответствующего разряда вспомогательного регистра множителя, второй вход - к инверсному выходу соответствующего разряда основного регистра сумматора, первый вход элемента И семнадцатой группы в каждом разряде, кроме младшего разряда, соединен с выходом элемента ИЛИ шестой группы предыдущего разряда и вторым входом соответствующего элемента И тринадцатой группы, первый вход элемента И семнадцатой группы младшего разряда подключен к шине сквозного переноса, второй вход элемента И семнадцатой группы соединен с прямым выходом соответствующего разряда вспомогательного регистра сумматора, выходы элементов И шестнадцатой и семнадцатой групп в каждом разряде соединены-со входами соответствующего элемента ИЛИ шестой группы. Источники информации, принятые во внимание при экспертизе 1.Папернов А.Д., Логические основы ЦВТ. М. Сов. радио, 1972, с. 194-196. 2.Авторское свидетельство СССР № 318941, кл. G Об F 7/50, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Арифметическое устройство | 1983 |

|

SU1239710A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Устройство для умножения | 1981 |

|

SU997031A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| Накапливающий сумматор | 1984 |

|

SU1176323A1 |

Авторы

Даты

1981-06-30—Публикация

1979-01-25—Подача