(5) ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТМЕТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2276457C2 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1267272A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1285392A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Асинхронный электропривод | 1989 |

|

SU1697252A1 |

| Устройство для управления многофазным вентильным преобразователем | 1983 |

|

SU1111248A1 |

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2014 |

|

RU2589404C2 |

| Устройство для управления многофазным выпрямителем | 1981 |

|

SU955510A1 |

1

Устройство относится к электроизмерительной технике и предназначено для измерения среднего значения переменных напряжений произвольной формы.

Известен цифровой вольтметр, со держащий устройства сравнения и подключенный к одному из его входов генератор опорного пилообразного напряжения, период,которого много больше периода измеряемого напряжения, а также логическое устройство, блок управления, ключи и интегратор 1.

Недостатками данного устройства являются низкая точность и помехоустойчивость при измерении переменных напряжений.

Известен цифровой интегрирующий BOjIbTMeTp, содержащий устройство сравнения и подключенный к одному из его входов генератор опорного пилообразного напряжения, период которого много больше периода измерпемого напряжения, а также последовательно соединенные генератор импульсов эталонной частоты, ключевой элемент, двоично-десятичный счетчик, отсчетное устройство, усилитель-ограничитель и логический блок, причем генератор опорного пилообразного напряжения выполнен двухполярным и подключен на вход усилителя-ограничителя, выход которого подсоединен

10 к одному из входов логического блока, к другому входу которого подключен выход устройства сравнения, на вход которого непосредственно подается измеряемое напряжение, а

15 выходы логического блока подключены соответственно к управляющему входу ключевого элемента и шинам сложения и вычитания реверсивного двоичного десятичного счетчика, соединенного с отсчетным устройством 2.

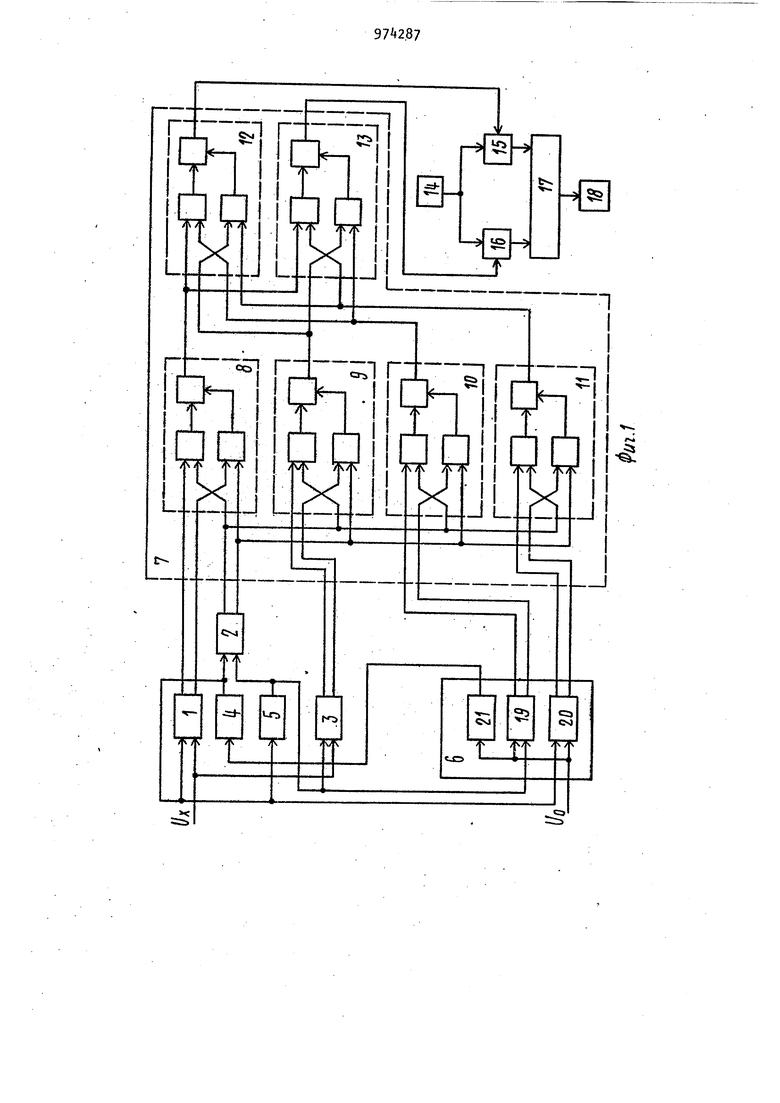

Однако устройство характеризуется низкой точностью и помехоустойчи3востью при измерении переменных напряжений. Цель изобретения - повышение точности и помехоустойчивости при измерении переменных напряжений. Поставленная цель достигается тем что в цифровой интегрирующий вольтметр, содержащий тактовый генератор, выполненный на датчике длительности цикла измерения, вход которого соединен с первым входом тактового генератора, подключенным к шине опорного напряжения, а выход - с первым выходом тактового генератора, подключенным к входу генератора опорного пилообразного напряжения, выход которого соединен с первым входом первого блока сравнения, второй вход которого соединен с шиной входного осигнала, а прямой и инверсный выходы которого соединены соответственно с первым и вторым входами логического блока, выполненного на элементе 2-2И-ИЛИ, первые, вторые и четвертые входы которого соединены соответственно с первыми, вторыми, третьими и четвертыми входами логического бло ка, первый выход которого соединен с управляющим входом ключевого элемента, информационный вход которого соединен с выходом эталонного генера тора, а выход - с первым входом интегратора, выход которого соединен с отсчетным устройством, в него введены инвертор, второй и третий блок сравнения второй ключевой элемент, в тактовь|й генератор введены четвертые и пятые блоки сравнения, а логический блок введены второй, третий, четвертый, пятый и шестой элементы 2-2И-ИЛИ, первый и второй входы второго элемента 2-2И-ИЛИ соединены соответственно с пятым и шестым входами логического блока, первый и второй входы третьего элемента 2-2И-ИЛ соответственно с седьмым и восьмым входами логического блока, а первый и второй входы четвертого элемента 2-2И-ИЛИ соответственно - с девятым и десятым входами логического блока, третьи входы второго, третьего и чет вертого элементов 2-2И-ИЛИ соединены с третьим входом логического блока, а их четвертые входы - с четвертым входом логического блока, причем выход первого элемента 2-2И-ИЛИ соединен с первыми входами пятого и шестого элемента 2-2И-ИЛИ, при этом выход второго элемента 2-2И-ИЛИ соеди7нен со вторыми входами пятого и шестого элементов 2-2И-ИЛИ, выход третьего элемента 2-2И-ИЛИ - с третьим входом пятого и четвертым входом шестого элементов 2-2И-ИЛИ, выход четвертого элемента 2-2И-ИЛИ - с четвертым входом пятого элемента 2-2И-ИЛИ, подключенного к первому выходу логического блока, и третьим входом шестого элемента 2-2И-ИЛИ, выход которого соединен со вторым выходом логического блока, подключенного к управляющему входу второго ключевого элемента, информационный вход которого соединен с выходом эталонного генератора, а выход - со вторым входом интегратора, при этом первый вход второго блока сравнения соединен непосредственно с выходом генератора опорного пилообразного напряжения и входом инвертора , а второй вход с выходом инвертора и первым входом третьего блока сравнения, апрямой и инверсный выходы второго блока сравнения соединены соответственно с третьим и четвертым входами логического блока, пятый и шестой выходы которого соединен соответственно с прямым и инверсным выходами третьего блока сравнения, второй вход которого соединенс шиной входного напряжения, причем вторые прямой и ин- . версный выходы тактового генератора соединены с седьмым и восьмым входами логического блока, третий прямой и инверсный выходы тактового генератора соединены с девятым и десятым входами логического блока, кроме того, первые входы четвертого и пятого блоков сравнения соединены с первым входом тактового генератора, второй вход четвертого блока сравнения со вторым входом тактового генератора, подключенного к выходу генератора пилообразного опорного напряжения, а второй вход пятого блока сравнения - к третьему входу тактового генератора, подключенного к выходу инвертора, прямой и инверсный выходы четвертого блока сравнения соединены соответственно со вторым прямым, и инверсным выходами тактового генератора, а прямой и инверсный выходы пятого блока сравнения - с третьим прямым и инверсным выходами тактового генератора. На фиг. 1 приведена функциональная схема цифрового вольтметра; на

фиг. 2 - временные диаграммы работы отдельных его узлов.

Вольтметр содержит блоки 1-3 сравнения, генератор k опорного пилообразного напряжения, инвертор 5, тактовый генератор 6, логический блок 7 выполненный на элементах 8-13 2-2И-ИЛИ, эталонный генератор 1, ключевые элементы 15 и 16, интегратор 17 и отсчетное устройство 18.

Тактовый генератор 6 содержит блоки 19 и 20 сравнения и задатчмк 21 длительности цикла измерения.

Измеряемое напряжение U подается на первые входы блоков 1 и 3 сравнения, на вторые входы которых поступает прямое и инвертированное пилообразное напряжение с выхода генератора k и инвертора 5. Синхронизирующий вход генератора k пилообразного напряжения соединен с выходом задатчика 21 длительности цикла тактового генератора 6. Прямые и инвертированные выходы блоков 1, 2, 3, 19 и 20 сравнения соединены со входами логического блока 7, выходами подключенного к управляющим входам ключей 15 и 16. Выход эталонного генератора k через ключи 15 и 16 свя-. зан с суммирующим и вычитающим входами интегратора 17. выходом соединенного с отсчетным устрйством 18.

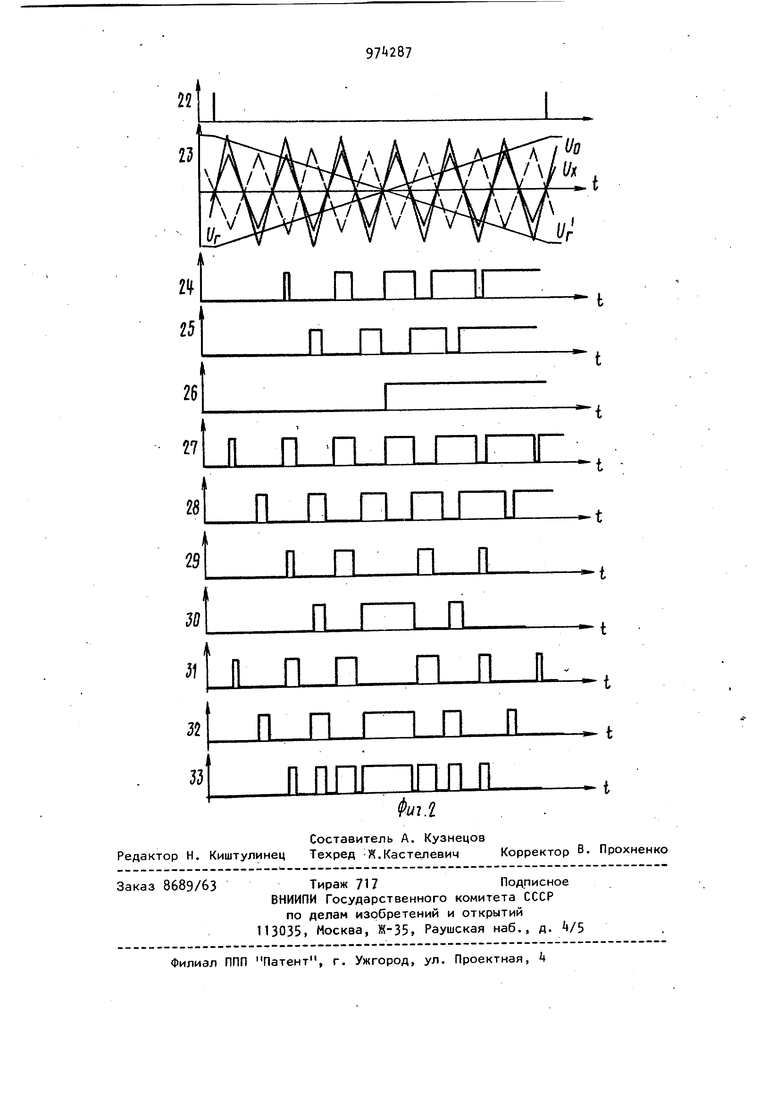

Цикл измерения задается тактовым генератором 6, на выходе задатчика 21 длительности цикла образуются импульсы запуска (фиг. 2, 22) генератора k опорного пилообразного напряжения. Прямое опорное пилообразное напряжение Ur (фиг. 2, 23) подается на входы блоков 1, 2 и 20 . сравнения, а инвертированное u|(фиг. 2. 23) - на блоков устройств сравнения 2, 3 и 19.

Измеряемое периодическое напряжение DX (фиг. 2, 23) подается на сигнальные входы блоков 1 и 3 сравнения а опорное напряжение UQ (фиг. 2, 23) через первый вход тактового генератора 6 на вторые входы блоков 19 и 2 сравнения и синхронизирующий вход за датчика 21 длительности цикла.

Опорное напряжение UQ представляет собой переменное напряжение, частота и форма - которого соответствуют измеряемому напряжению, амплитуда равна максимально предельному значению измеряемого сигнала, а фаза по отношению к измеряемому напряжению DX может составлять О или Ji , На прямых и инверсных выходах блоков 1 и 3 сравнения образуются прямоугольные импульсы, когда измеряемое напряжение (iyi больше или меньше пилообразного напряжения 11(1)/-).

На фиг. 2, 24 и 2,25 показаны напряжения на прямых выходах блоков 1 и 3 сравнения соответственно при фазе сигнала Ux, изображенного на. фиг. 2, 23 сплошной линией. При изменении фазы сигнала (i на Л (на фиг. 2, 23 показан штриховой линией) напряжение,показанное на фиг. 2, , образуется на выходе блока 3 сравнения, а на-фиг. 2, 25 на выходе блока

Iсравнения.

Блок 2 сравнения из прямого и инвертированного пилообразного напряжения формирует прямоугольные импульсы (фиг. 2, 26).

На выходах блоков 19 и 20 сравнения тактового генератора 6 образуются прямоугольные импульсы, длительность которых равна временным интервалам, когда опорное напряжение UQ больше или меньше текущего значения пилообразного напряжения Ur-(Ur).

На фиг. 2, 27 и 2, 28 показаны напряжения на выходах устройств сравнения 19 и 20, а на фиг. 2, 31, 2, 32 на выходах элементов 10 и 11 соответственно.

Прямые и инверсные выходы блоков 1, 2, 3, 19 и 20 сравнения подключены ко входам элементов 8, 9 Ю,

IIлогического блока 7.

В результате, при фазе сигнала U изображенного на фиг. 2, 23 сплошной линией, напряжение на выходе элемента 8 соответствуетпредставленному на фиг. 2, 29, а на выходе элемента 9 на фиг. 2, 30. При изменении фазы сигнала U на л напряжение в соответствии с фиг. 2, 29 образуется на выходе элемента 9, а в соответствии с фиг. 2, 30 - на выходе элемента.8.

Выходы элементов 8-11 подключены ко входам элементов 12 и 13 логического блока 7.

При нулевом фазовом сдвиге между сигналами UQ и Ux. импульсы фиг. 2, 29 совпадут по времени с импульсами фиг. 2, 31, а импульсы фиг. 2, 30 с импульсами фиг. 2, 32 на выходе элементов 10 и 11 соответственно и на выходе элемента 12 образуется напря-i жение фиг. 2, 33. На выходе элемен 7 та 13 будетпри этом постоянно присутствовать нулевой уровень. При изменении фазы сигнала U на Л отмеченное выше временное совпадение импульсов будет происходить на входах элемента 13 и сигнал фиг. 2, 33 появится на выходе этой схемы, а на выходе элемента 12 будет постоянно присутствогаать нулевое напряжение. Таким образом, при нулевой фазе через ключ 15 происходит подключение эталонного генератора 1А к суммирующему входу интегратора 17, а при фазе - через ключ 16 - к вычитающему ВХОДУ интегратора. К концу.цикла измерения отсчетное устройство 18 зафиксирует величину на выходе интегратора 17, пропорцио нальную среднему значению измеряемого переменного напряжения, причем знак результата измерения содержит .информацию о фазе измеряемого напря жения. Результат измерения является преобразованием усредненных за цикл измерений мгновенных значений переменного напряжения. В устройстве в результате использования для измерения обеих полуволн переменного напря жения удваивается число измерений мгновенных значений входного сигнала за один цикл, что обеспечивает по вышение точности измерения, особенно при флуктуациях амплитуды измеряемого сигнала. Использование в устройстве опорного, сигнала обеспечивает повышение помехоустойчивости по сравнению с прототипом. В случае флуктуацией по фазе входного напряжения обеспечивается селективное измерение составляющих синфазный и противофазный пря моугольному напряжению, подаваемому ;на логический блок с тактоЕЮго ге|нератора, и подавление составляющих с фазовым сдвигом, отличающимся от значений О или 1Г относительно опорного сигнала U. Формула изобретения Цифровой интегрирующий вольтметр, содержащий тактовый генератор, выполненный на датчике длительности цикла измерения, вход которого соеди нен с первым входом тактового генера тора, подключенным к шине опорного 7 напряжения, а выход - с первым выходом тактового генератора, подключенным к,входу генератора опорного пилообразного напряжения, выход которого соединен с первым входом первого блока сравнения, второй вход которого соединен с шиной входного сигнала, а прямой и инверсный выходы которого соединены соответственно с первым и вторым входами логического блока, выполненного на элементе 2-2И-ИЛИ, первые, вторые, третьи и четвертые входы которого соединены соответственно с первыми, вторыми, третьими и четвертыми входами логического блока, первый еыход которого соединен с управляющим входом ключевого элемента, информационный вход которого соединен с выходом эталонного генератора, а выход - с первым входом интегратора , выход которого соединен с отсчетным устройством, отличаю щийс я тем, что, с целью уменьшения погрешности измерения среднего значения переменного напряжения и повышения помехоустойчивости, в него введены инвертор, второй и третий блоки сравнения, второй ключевой элемент, в тактовый генератор введены четвертые и пятые блоки сравнения, а в логический блок введены второй, третий, четвертый, пятый и шестой элементы 2-2И-ИЛИ, первый и второй . входы второго элемента 2-2И-ИЛИ соединены соответственно с пятым- и шестым входами логического блока, первый и второ.й входы третьего элемента 2-2И-ИЛИ соответственно - с седьмым и восьмым входами логического блока, а первый и второй входы четвертого элемента 2-2И-ИЛИ соответственно с девятым и десятым входами логического блока, третьи входы второго, третьего и четвертого элементов 2-2И-ИЛИ соединены с третьим входом логического блока, а их четвертые входы - с четвертым входом логического блока, причем выход первого элемента 2-2И-ИЛИ соединен с первыми входами пятого и шестого элемента 2 2И-ИЛИ, при этом выход второго элемента 2-2И-ИЛИ соединен со вторыми входами пятого и шестого элементов 2-2И-ИЛИ, выход третьего элемента 2-2И-ИЛИ - с третьим вхрдом пятого и четвертым входом шестого элементов 2-2И-ИЛИ, выход четвертого элемента 2-2И-ИЛИ - с четвертым входом пятого элемента 2-2И-ИЛИ, под9ключенного к первому выходу логического блока, и третьим входом шестого элемента 2-2И-ИЛИ, выход которо го соединен со вторым выходом логического блока,подключенного к управ лякмцему входу второго ключевого элемента, информационный вход которогсС соединен с выходом эталонного генератора, а выход - со вторым входом интегратора, при этом первый вход второго блока сравнения соединен непосредственно с выходом генератора опорного пилообразного напряжения, и входом инвертора, а второй вход с выходом инвертора и первым входом третьего блока сравнения, а прямой и инверсный выходы второго блока сравнения соединены соответственно с третьим и четвертым входами логического блока, пятый и шестой выхокоторого соединены соответственно ды с прямым и инверсным выходами третьего блока сравнения, второй вход которого соединен с шиной входного напряжения j причем вторые прямой и инверсный выходы тактового генератора соединены с седьмым и восьмым входами логического-блока, третий прямой и инверсный выходы тактового гене37ратора соединены с девятым и десятым входами логического блока, кроме того, первые входы четвертого и пятого блоков сравнения соединены с первым входом тактового генератора, второй вход четвертого блока сравнения - со вторым входом тактового генератора, подключенного к выходу генератора пилообразного опорного напряжения, а второй вход пятого блока сравнения - к третьему входу тактового генератора, подключенного-к выходу инвертора, прямой и инверсный выходы четвертого блока сравнения соединенысоответственно со вторыми прямым и инверсным выходами тактового генератора, .а прямой и инверсной выходы пятого блока сравнения - с третьими прямым и инверсным выходами тактового генератора. Источники информации, принятые во внимание при экспертизе 1.Цифровые электроизмерительные приборы. Под ред. В.Н. Шляндина. М., Энергия, 1972, с. 176-178.. 2.Авторское свидетельство СССР № 235201, кл. G 01 R 19/25, 19б7 (прототип). ГЛ ., ,. -1 , I

Авторы

Даты

1982-11-15—Публикация

1981-05-18—Подача