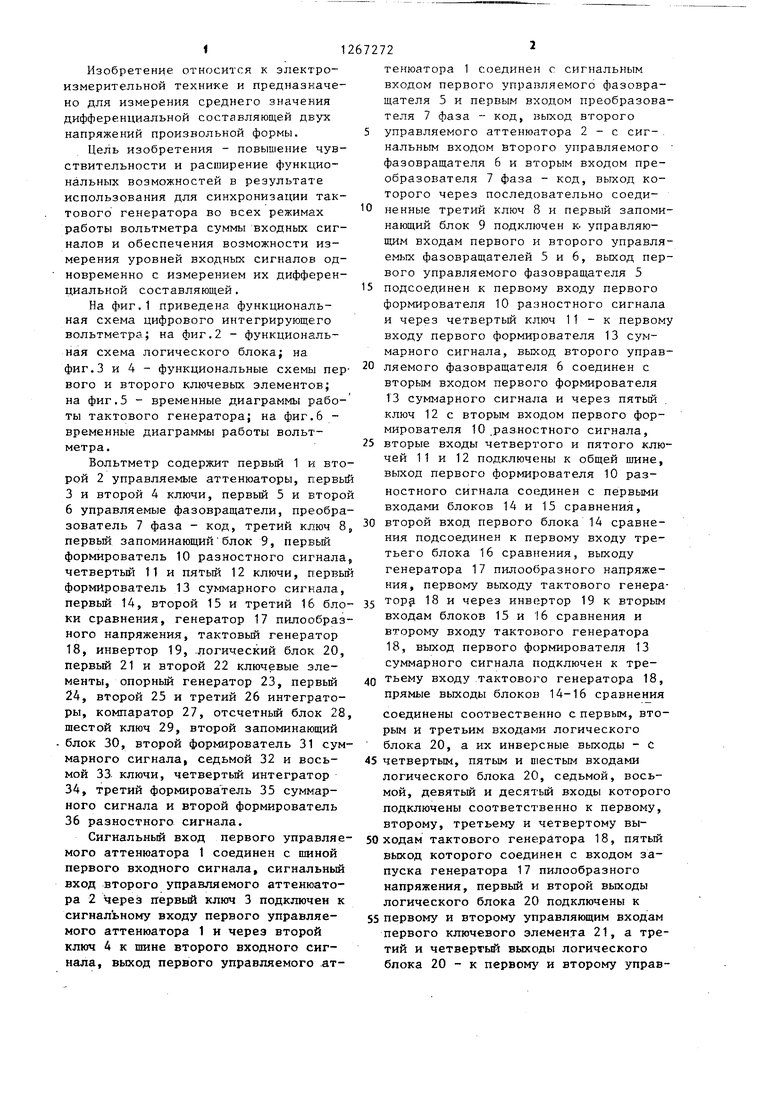

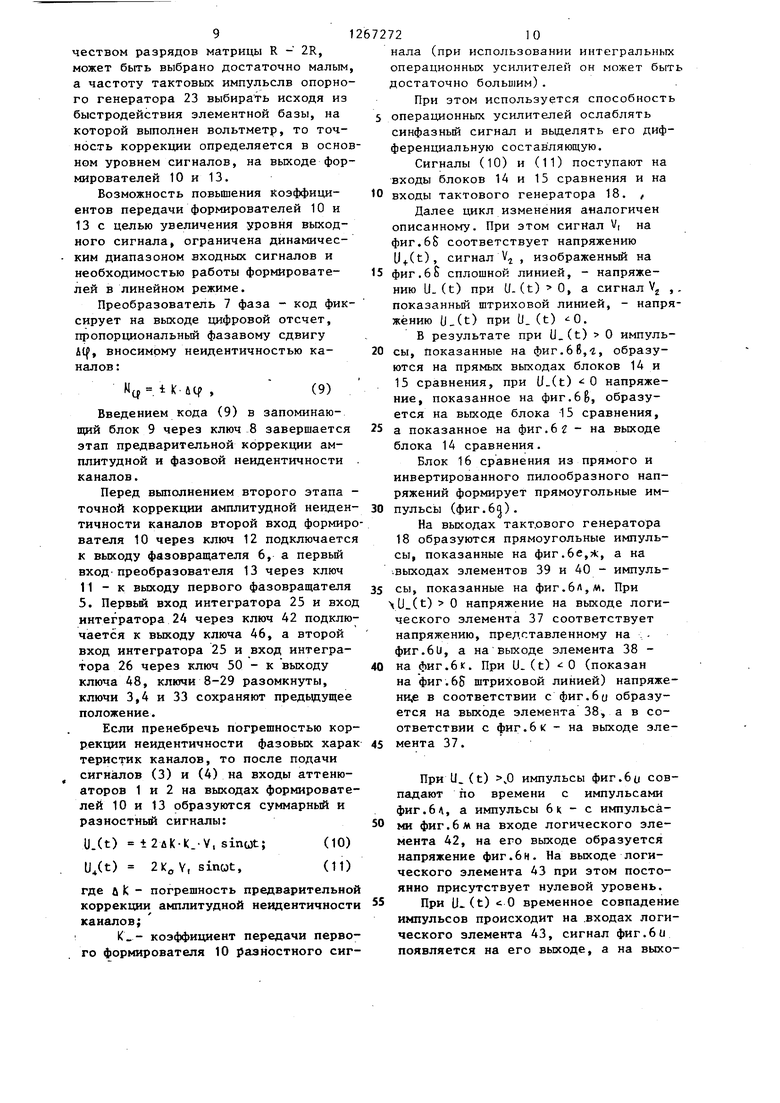

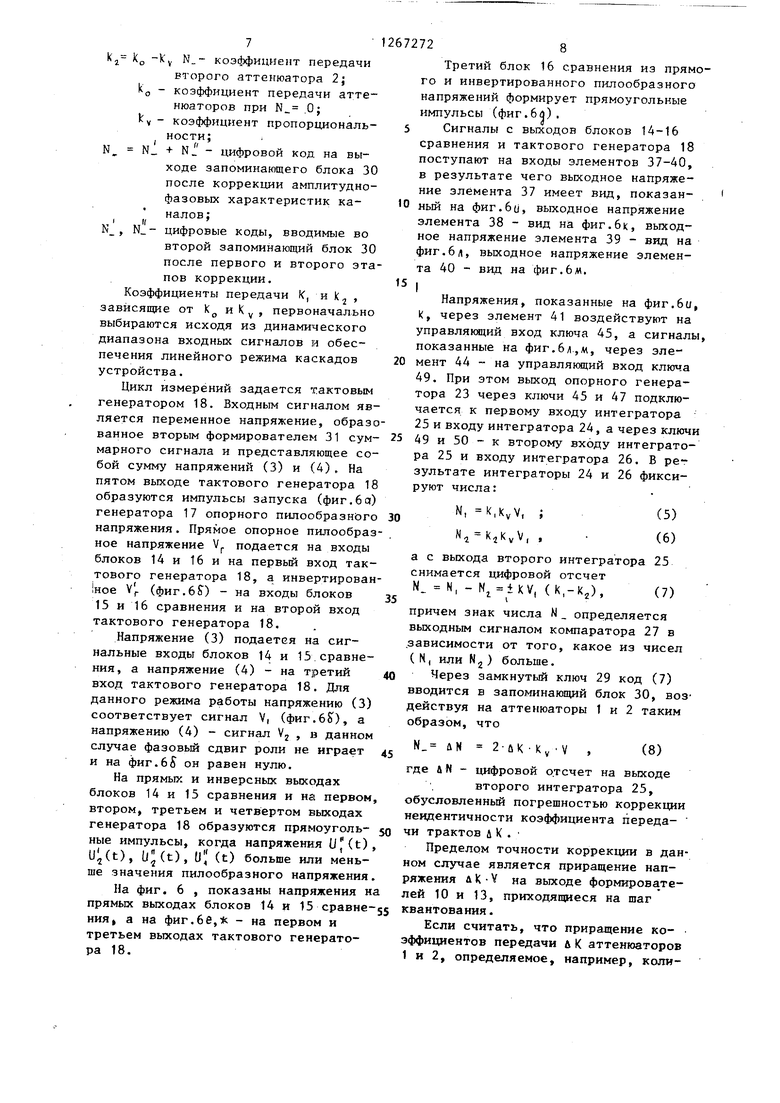

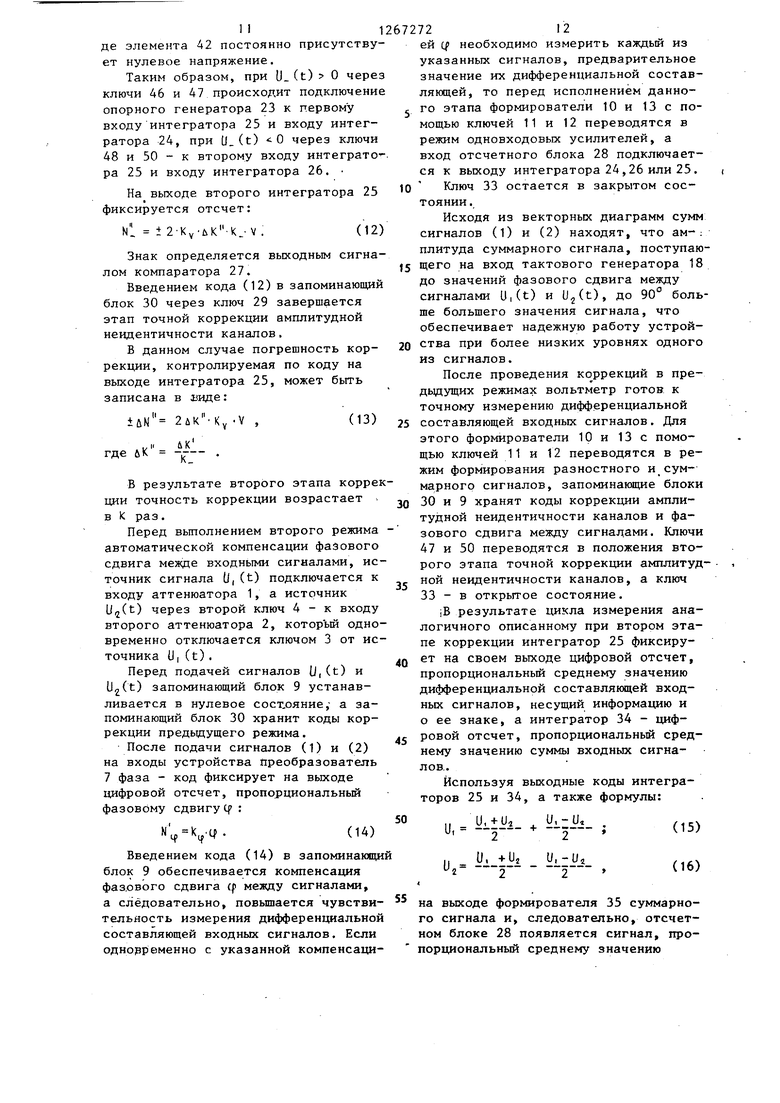

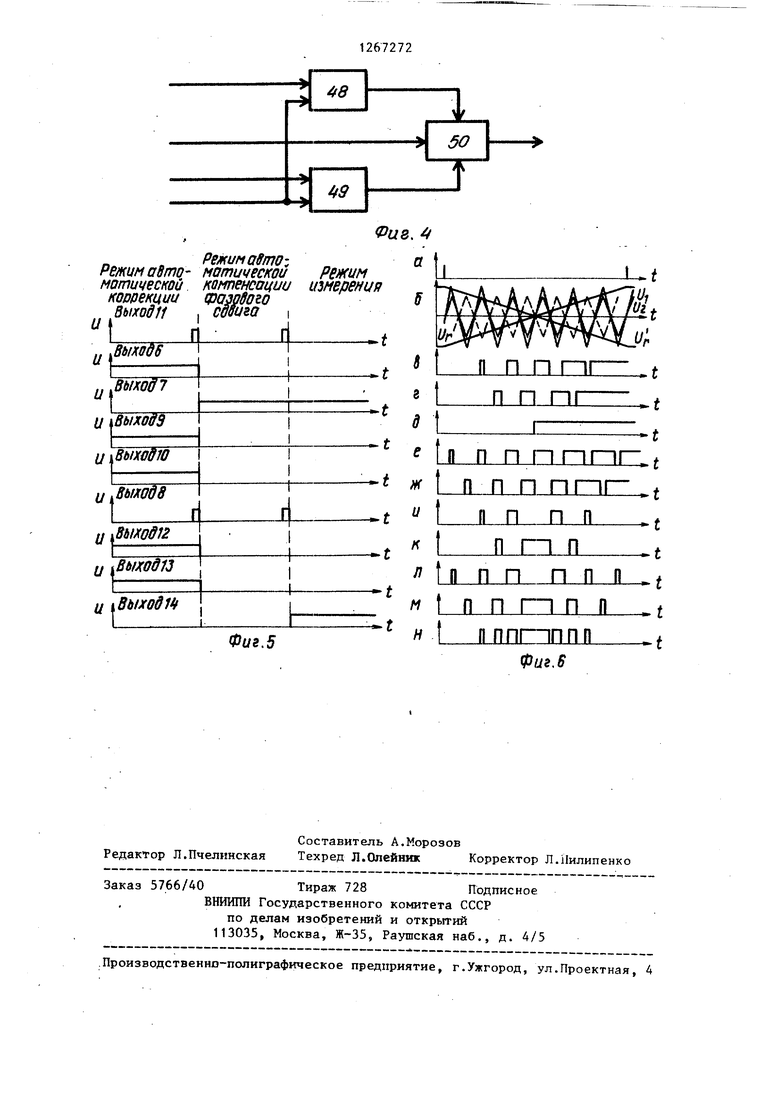

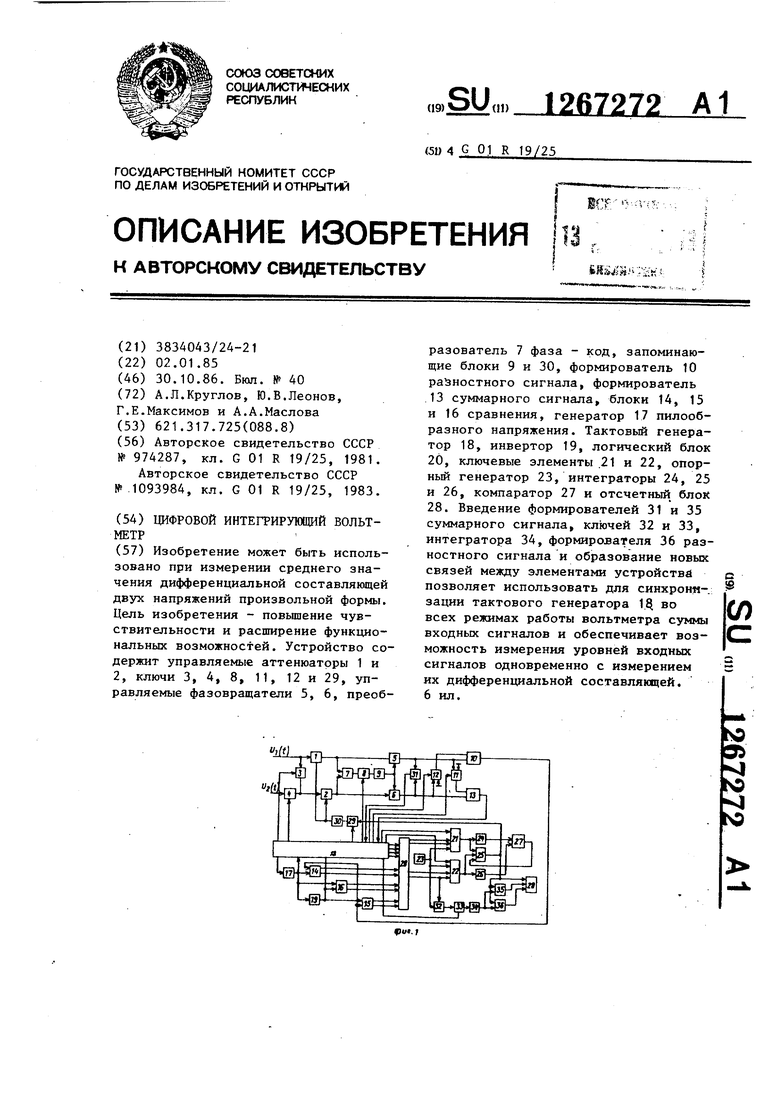

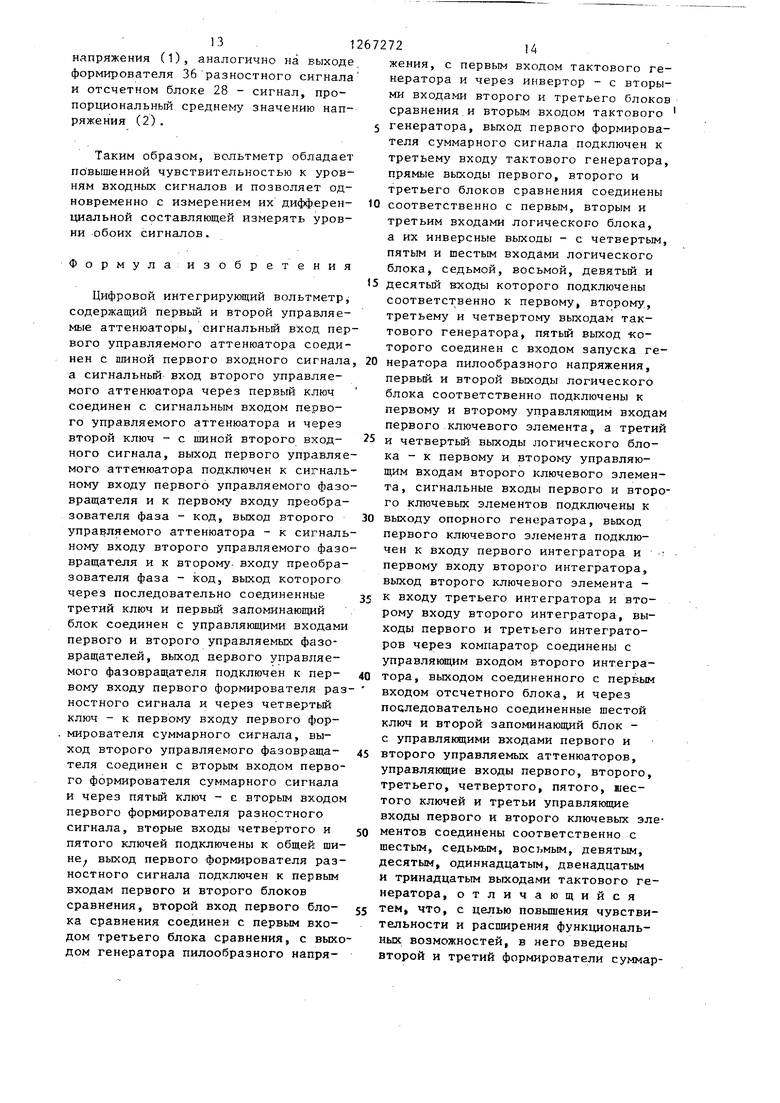

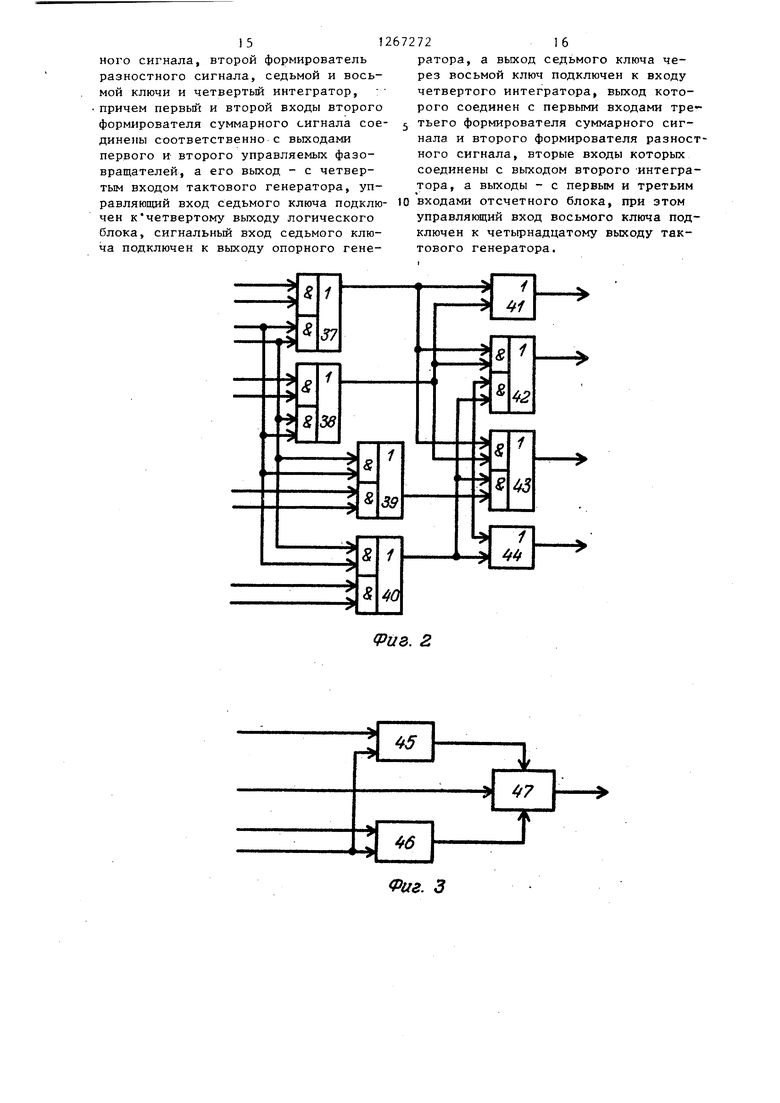

1 Изобретение относится к электроизмерительной технике и предназначено для измерения среднего значения дифференциальной составляющей двух напряжений произвольной формы. Цель изобретения - повышение чувствительности и расширение функциональных возможностей в результате использования для синхронизации тактового генератора во всех режимах работы вольтметра суммы входных сигналов и обеспечения возможности измерения уровней входных сигналов одновременно с измерением их дифференциальной составляющей, На фиг.1 приведена функциональная схема цифрового интегрирующего вольтметра; на фиг.2 - функциональная схема логического блока; на фиг.З и 4 - функциональные схемы пер вого и второго ключевых элементов; на фиг.З - временные диаграммы работы тактового генератора; на фиг.6 временные диаграммы работы вольтметра. Вольтметр содержит первый 1 и вто рой 2 управляемые аттенюаторы, первы 3 и второй 4 ключи, первьй 5 и второ 6 управляемые фазовращатели, преобра зователь 7 фаза - код, третий ключ 8 первый запоминающийблок 9, первьй формирователь 10 разностного сигнала четвертый 11 и пятый 12 ключи, первы формирователь 13 суммарного сигнала. первьй 14, второй 15 и третий 16 бло ки сравнения, генератор 17 пилообраз ного напряжения, тактовый генератор 18, инвертор 19, .логический блок: 20, первый 21 и второй 22 ключевые элементы, опорный генератор 23, первьй 24, второй 25 и третий 26 интеграторы, компаратор 27, отсчетньй блок 28 шестой ключ 29, второй запоминающий блок 30, второй формирователь 31 сум марного сигнала, седьмой 32 и восьмой 33 ключи, четвертьй интегратор 34, третий формирователь 35 суммарного сигнала и второй формирователь 36 разностного сигнала. Сигнальньй вход первого управляе

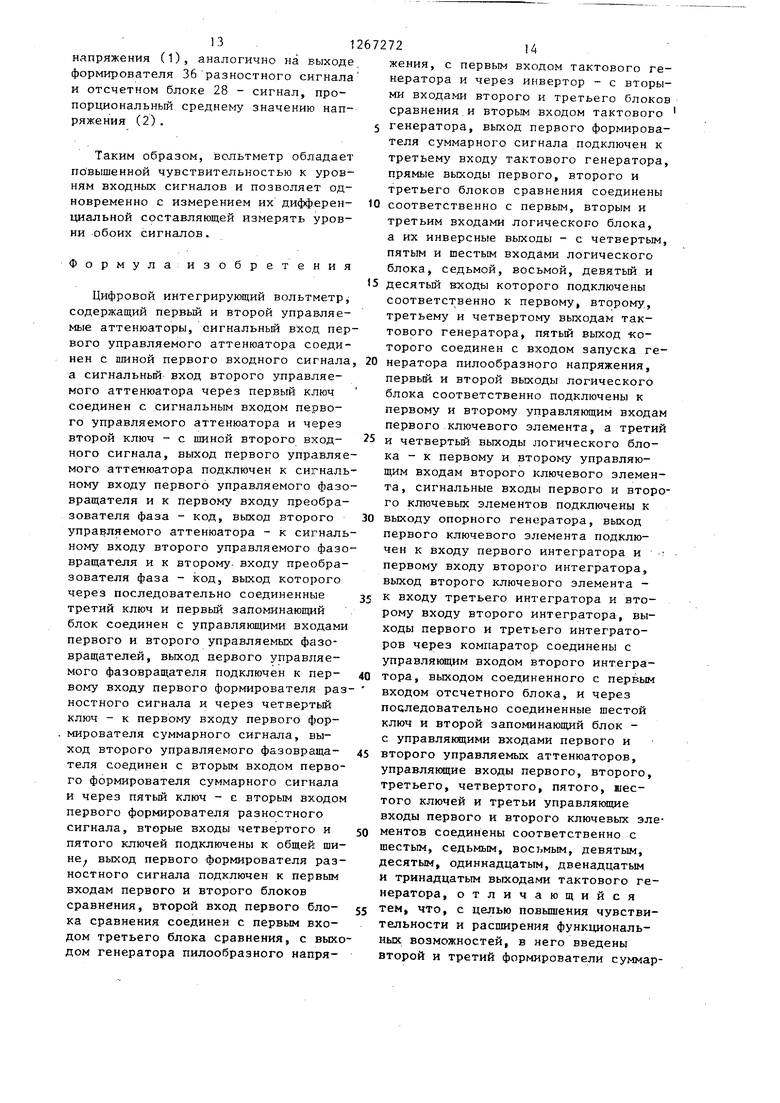

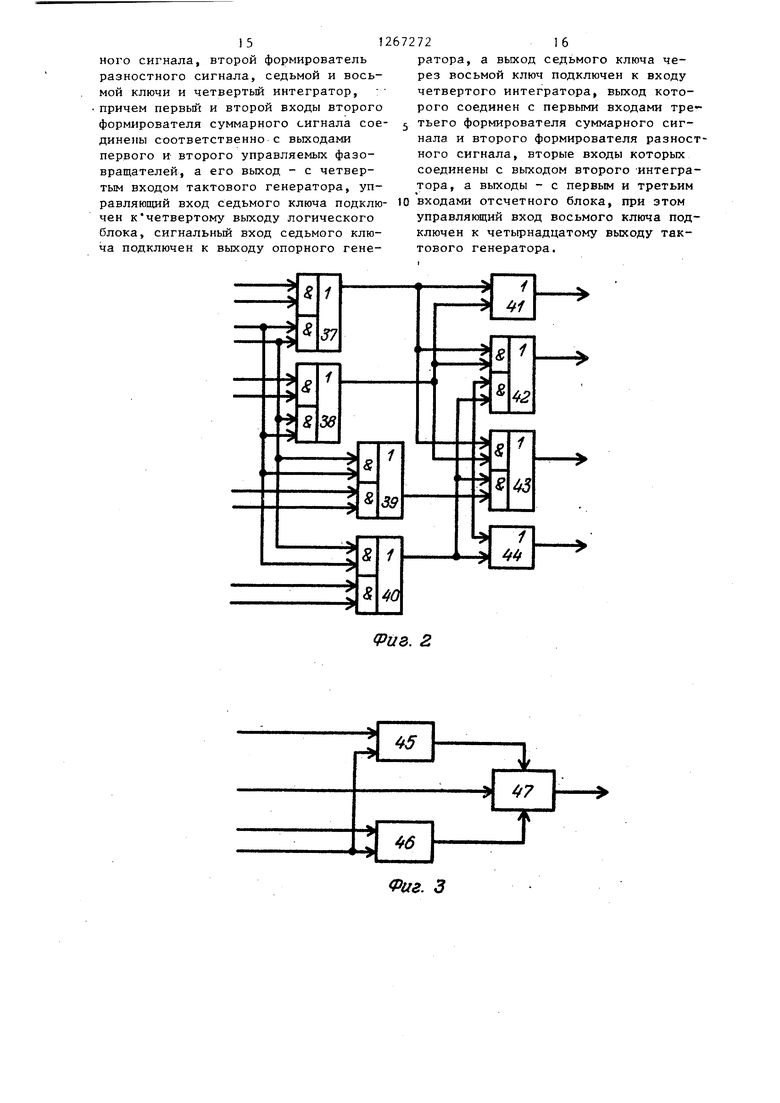

мого аттенюатора 1 соединен с шиной первого входного сигнала, сигнальньй вход второго управляемого аттенюатора 2 через первый ключ 3 подключен к сигнальному входу первого управляемого аттенюатора 1 и через второй ключ 4 к шине второго входного сигнала, выход первого управляемого .атвыход которого соединен с входом запуска генератора 17 пилообразного напряжения, первый и второй выходы логического блока 20 подключены к 55 первому и второму управляющим входам первого ключевого элемента 21, а третий и четвертьй выходы логического блока 20 - к nepBOMj и второму управ2тенюатора 1 соединен с сигнальным входом первого управляемого фазовращателя 5 и первым входом преобразователя 7 фаза - код, выход второго управляемого аттенюатора 2-е сиг- . нальным входом второго управляемого фазовращателя 6 и вторым входом преобразователя 7 фаза - код, выход которого через последовательно соединенные третий ключ 8 и первый запоминающий блок 9 подключен к- управляющим входам первого и второго управляемых фазовращателей 5 и 6, выход первого управляемого фазовращателя 5 подсоединен к первому входу первого формирователя 10 разностного сигнала и через четвертьш ключ 11 - к первому входу первого формщювателя 13 суммарного сигнала, выход второго управляемого фазовращателя 6 соединен с вторым входом первого формирователя 13 суммарного сигнала и через пятый ключ 12 с вторым входом первого формирователя 10 .разностного сигнала, вторые входы четвертого и пятого ключей 11 и 12 подключены к общей шине, выход первого формирователя 10 разностного сигнала соединен с первыми входами блоков 14 и 15 сравнения, второй вход первого блока 14 сравнения подсоединен к первому входу третьего блока 16 сравнения, выходу генератора 17 пилообразного напряжения, первому выходу тактового генера Р через инвертор 19 к вторым входам блоков 15 и 16 сравнения и второму входу тактового генератора 18, выход первого формирователя 13 суммарного сигнала подключен к третьему входу тактового генератора 18, прямые выходы блоков 14-16 сравнения соединены соотвественно с первым, вторым и третьим входами логического блока 20, а их инверсные выходы - С четвертым, пятым и шестым входами логического блока 20, седьмой, восьмой, девятьй и десятьй входы которого подключены соответственно к первому, второму, третьему и четвертому выходам тактового генератора 18, пятый

честном разрядов матрицы R - 2R, может быть выбрано достаточно малым, а частоту тактовых импульслв опорного генератора 23 выбирать исходя из быстродействия элементной базы, на которой вьтолнен вольтметр, то точность коррекции определяется в основном уровнем сигналов, на выходе формирователей 10 и 13.

Возможность повышения коэффициентов передачи формирователей 10 и 13 с цепью увеличения уровня выходного сигнала, ограничена динамичесКИМ диапазоном входных сигналов и необходимостью работы формирователей в линейном режиме.

Преобразователь 7 фаза - код фиксирует на выходе цифровой отсчет, пропорциональный фазавому сдвигу 41, вносимому неидентичностью каналов :

М( , (9)

Введением кода (9) в запоминающий блок 9 через ключ 8 завершается этап предварительной коррекции амплитудной и фазовой неидентичности . каналов.

Перед выполнением второго этапа точной коррекции амплитудной неидентичности каналов второй вход формирователя 10 через ключ 12 подключается к выходу фазовращателя 6, а первый ВХОДпреобразователя 13 через ключ 11 - к выходу первого фазовращателя 5. Первый вход интегратора 25 и вход интегратора 24 через ключ 42 подключается к выходу ключа 46, а второй вход интегратора 25 и вход интегратора 26 через ключ 50 - к выходу ключа 48, ключи 8-29 разомкнуты, ключи 3,4 и 33 сохраняют предьщущее положение.

Если пренебречь погрешностью коррекции неидентичности фазовых харак теристик каналов, то после подачи сигналов (3) и (4) на входы аттенюаторов 1 и 2 на выходах формирователей 10 и 13 образуются суммарный и разностный сигналы:

U.(t) t 2uK-K.-V, sinwt; (10) U(t) 2X0 V, sinot, (11)

где u k - погрешность предварительной коррекции амплитудной неидентичности каналов;

коэффициент передачи первого формирователя 10 разностного сигнала (при использовании интегральных операционных усилителей он может быть достаточно большим).

При этом используется способность операционных усилителей ослаблять синфазный сигнал и выделять его дифференциальную составляющую.

Сигналы (10) и (11) поступают на входы блоков 14 и 15 сравнения и на

входы тактового генератора 18. /

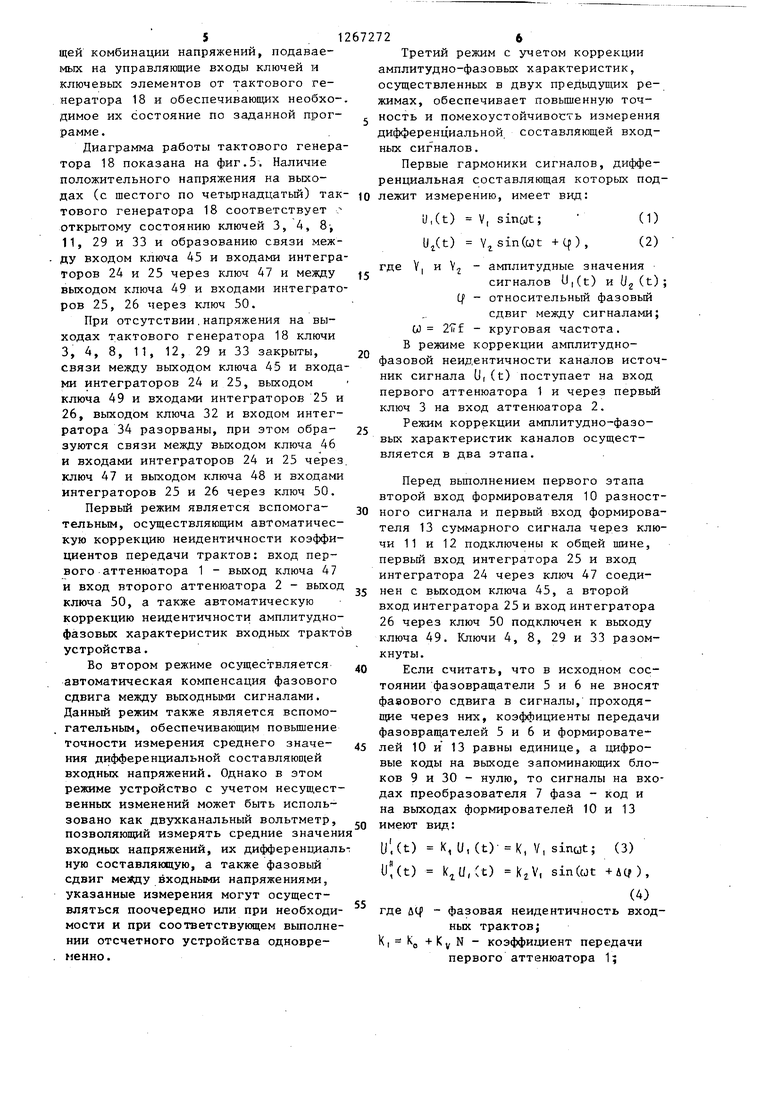

Далее цикл изменения аналогичен описанному. При этом сигнал V, на фиг,б5 соответствует напряжению U4.(t), сигнал V. , изображенный на

фиг.б5 сплошной линией, - напряжению и. (t) при (J- (t) О, а сигнал V , , показанный штриховой линией, - напряжению 0(t) при (J. (t) 0.

В результате при U(t) О импульсы. Показанные на фиг.6 В,-г, образуются на прямых выходах блоков 14 и 15 сравнения, при U(t) 0 напряжение, показанное на фиг.бВ, образуется на выходе блока 15 сравнения,

а показанное на фиг.62 - на выходе блока 14 сравнения.

Блок 16 сравнения из прямого и инвертированного пилообразного напряжений формирует прямоугольные импульсы (фиг.б).

На выходах такт.ового генератора 18 образуются прямоугольные импульсы, показанные на фиг.бе,ж, а на .выходах элементов 39 и 40 - импульсы, показанные на фиг.6л,«. При U(t) О напряжение на выходе логического элемента 37 соответствует напряжению, представленному на ;фиг.би, а на выходе элемента 38 на фиг.61C. При U. (t) - О (показан

на фиг.65 штриховой линией) напряжени,е в соответствии с фиг.би образуется на выходе элемента 38, а в соответствии с фиг.6 к - на выходе элемента 37.

При U. (t) 0 импульсы фиг.ба совпадают по времени с импульсами фиг.6А, а импульсы 6к - с импульсаI,JH фиг.6м на входе логического элемента 42, на его выходе образуется напряжение фиг.бн. На выходе логического элемента 43 при этом постоянно присутствует нулевой уровень.

При и.(t) с О временное совпадение импульсов происходит на .входах логического элемента 43, сигнал фиг.би появляется на его выходе, а на выхоkj,- Kg -Ку коэффициент передачи второго аттенюатора 2j kg - коэффициент передачи аттенюаторов при N.0; ky - коэффициент пропорциональности;N + N - цифровой код. на выходе запоминающего блока 30 после коррекции амплитуднофазовых характеристик каналов:ч цифровые коды, вводимые во второй запоминающий блок 30 после первого и второго эта пов коррекции. Коэффициенты передачи К, и К , зависящие от К иК, первоначально выбираются исходя из динамического диапазона входных сигналов и обеспечения линейного режима каскадов устройства. Цикл измерений задается тактовым генератором 18. Входным сигналом является переменное напряжение, образо ванное вторым формирователем 31 суммарного сигнала и представляющее собой сумму напряжений (3) и (4). На пятом выходе тактового генератора 18 образуются импульсы запуска (фиг.6а) генератора 17 опорного пилообразного напряжения. Прямое опорное пилообраз ное напряжение V. подается на входы блоков 14 и 16 и на первый вход тактового генератора 18, а инвертирован 1ное Vr (фиг.бв) - на входы блоков 15 и 16 сравнения и на второй вход тактового генератора 18. Напряжение (3) подается на сигнальные входы блоков 14 и 15 сравнения, а напряжение (4) - на третий вход тактового генератора 18. Для данного режима работы напряжению (3) соответствует сигнал V| (фиг.б5), а напряжению (4) - сигнал Vj , в данном случае фазовый сдвиг роли не играет и на фиг.бд он равен нулю. На прямых и инверсных выходах блоков 14 и 15 сравнения и на первом втором, третьем и четвертом выходах генератора 18 образуются прямоугольные импульсы, когда напряжения Uj(t) (t), (J5(t), и (t) больше или меньше значения пилообразного напряжения На фиг. 6 , показаны напряжения н прямьк выходах блоков 14 и 15 сравне ния, а на фиг.бе, - на первом и третьем выходах тактового генератора 18. 728 Третий блок 16 сравнения из прямого и инвертированного пилообразного напряжений формирует прямоугольные импульсы (фиг.6а), Сигналы с выходов блоков 14-16 сравнения и тактового генератора 18 поступают на входы элементов 37-40, в результате чего выходное напряжение элемента 37 имеет вид, показанный на фиг.би, выходное напряжение элемента 38 - вид на фиг.бк, выходное напряжение элемента 39 - вид на фиг.бд, выходное напряжение элемента 40 - вид на фиг.6м, Напряжения, показанные на фиг.би, k, через элемент 41 воздействуют на управляюищй вход ключа 45, а сигналы, показанные на фиг.6А,м, через элемент 44 - на управлякщий вход ключа 49. При этом выход опорного генератора 23 через ключи 45 и 47 подключается к первому входу интегратора 25 и входу интегратора 24, а через ключи 49 и 50 - к второму входу интегратора 25 и входу интегратора 26. В результате интеграторы 24 и 26 фиксируют числа;. N, ,KvV, N kjK,V, а с выхода второго интегратора 25 снимается цифровой отсчет М N, - N ±KV, (k,-k,), причем знак числа М определяется выходным сигналом компаратора 27 в зависимости от того, какое из чисел (N, иди N) больше. Через замкнутый ключ 29 код (7) вводится в запоминающий блок 30, воздействуя на аттенюаторы 1 и 2 таким образом, что N UN 2-uK К. где 4N - цифровой отсчет на выходе второго интегратора 25, обусловленный погрешностью коррекции неидентичности коэффициента передачи трактов U К. Пределом точности коррекции в данном случае является приращение напяжения д V на выходе формироватеей 10 и 13, приходящиеся на шаг вантования, Если считать, что приращение коффициентов передачи & К аттенюаторов 1 и 2, определяемое, например, колиляющим входам второго ключевого элемента 22, сигнальные входы ключевых элементов 21 и 22 подключены к выходу опорного генератора 23, выход пер вого ключевого элемента 21 подключен к входу первого интегратора 24 и первому входу второго интегратора 25, выход второго ключевого элемента . 22 - к входу третьего интегратора 26 и второму входу второго интегратора 25, выходы интеграторов 24 и 26 чере компаратор 27 соединены с управляющим входом второго интегратора 25, выходом соединенного с первым входом отсчетного блока 28 и через последовательно соединенные шестой ключ 29 и второй запоминакяций блок 30 - с управляющими входами первого и второ го управляемых аттенюаторов 1 и 2, управляющие входы ключей 3, 4, 8, 11 12 и 29 и третьи управляющие входы ключевых элементов 21 и 22 соединены соответственно с. шестым, седьмым, восьмым, девятым, десятым, одиннадца тым, двенадцатым и тринадцатым выходами тактового генератора 18, пер. вый и второй входы второго формирователя 31 суммарного сигнала соеди- . иены соответственно с выходами управ ляемых фазовращателей 5 и 6, а его выход - с четвертым входом тактового генератора, управлякнций вход седьмого ключа 32 подключен к четвертому выходу логического блока 20, сигналь ный вход седьмого ключа 32 - к выходу опорного генератора 23, а выход седь|мого ключа 32 через восьмой ключ 33 - к входу четвертого интегратора 34, выход которого соединен с первыми входами третьего формирователя 35 суммарного сигнала и второго формирователя 36 разностного сигнала, вторые входы которых соединены с выходом второго интегратора 25, а выходы - с вторым и третьим входами отсчетного блока 28, управляющий вход восьмого ключа 33 подключен к четырнадцатому вьсходу тактового генератрра 18, Логический блок 20 содержит первый 37 - восьмой 44 логические элементы, первый и второй входы логических элементов 37-40 являются соответственно первым и четвертым, вторым и пятым, седьмым и восьмым, девятым и десятым входами логического блока 20, а их третьи и четвертые входы являются соответственно третьим и шестым входами логического блока 20, выходы логических элементов 37 и 38 соответственно соединены с первыми и вторы да входами логических элементов 41-43, выход логического элемента 39 соединен с третьими входами логических элементов 42 и 43 и первым входом логического элемента 44, выход логического элемента40 соединен с четвертыми входами логических элементов 42 и 43 и вторым входом логического элемента 44, выходы логических элементов 41-44 являются соответственно первым, вторым, третьим и четвертым выходами логического блока 20, Первый ключевой элемент 21 образуют девятьй 45, десятый 46 и одиннадцатый 47 ключи сигнальные входы ключей 45 и 46 являются сигнальным входом первого ключевого элемента 21, управляюцие входы ключей 45-47 являются соответственно первым, вторым и третьим управлянщими входами ключевого элемента 21, выходы ключей 45 и 46 соединены с входами ключа 47, выход которого является выходом ключевого элемента 21. Второй ключевой элемент 22 содержит двенадцатый 48, тринадцатый 49 и четырнадцатый 50 ключи, сигнальные входы ключей 48 и 49 являются сигнальным входом ключевого элемента 22, управляющие входы ключей 48-50 - со-. ответственно первым, вторым и третьим управляющими входами ключевого элемента 22, выходы ключей 48 и 49 соединены с входами ключа 50, выход которого является выходом ключевого элемента 22, Вольтметр работает следующим образом. Вольтметр может работать в следующих режимах, 1,В режиме автоматической коррекции неидентичности амплитуднофазовых характеристик каналов; 2,В режиме автоматической компенсации фазового сдвига между входными сигналами; 3,В режиме измерения дифференциальной составляющей входных напряений . Управление указанными режима осуществляется при помощи ключей 3, 4, 8, 11, 12, 29 и 33 и ключевых элементов 21 и 22, В каящом из перечисленных режимов возможно осуществление соответствующей комбинации напряжений, подаваемых на управляющие входы ключей и ключевых элементов от тактового генератора 18 и обеспечивающих необходимое их состояние по заданной программе. Диаграмма работы тактового генера тора 18 показана на фиг.5. Наличие положительного напряжения на выходах (с шестого по четьфнадцатый) так тового генератора 18 соответствует , открытому состоянию ключей 3, 4, 8-, 11, 29 и 33 и образованию связи между входом ключа 45 и входами интегра торов 24 и 25 через ключ 47 и ме;жду выходом ключа 49 и входами интеграто ров 25, 26 через ключ 50. При отсутствии.напряжения на выходах тактового генератора 18 ключи 3, 4, 8, 11, 12, 29 и 33 закрыты, связи между выходом ключа 45 и входа ми интеграторов 24 и 25, выходом ключа 49 и входами интеграторов 25 и 26, выходом ключа 32 и входом интегратора 34 разорваны, при этом образуются связи между выходом ключа 46 и входами интеграторов 24 и 25 через ключ 47 и выходом ключа 48 и входами интеграторов 25 и 26 через ключ 50. Первый режим является вспомогательным, осуществляющим автоматическую коррекцию неидентичности коэффициентов передачи трактов: вход первого аттенюатора 1 - выход ключа 47 и вход второго аттенюатора 2 - выход ключа 50, а также автоматическую коррекцию неидентичности амплитуднофазовых характеристик входных тракто устройства. Во втором режиме осуществляется автоматическая компенсация фазового сдвига между выходными сигналами. Данньй режим также является вспомогательным, обеспечивающим повьшение точности измерения среднего значеНИН дифференциальной составляюп1ей входных напряжений. Однако в этом режиме устройство с учетом несуш,ественных изменений может быть использовано как двухканальный вольтметр, позволяющий измерять средние значени входных напряжений, их дифференидаль ную составляющую, а также фазовый сдвиг мезвду входными напряжениями, указанные измерения могут осуществляться поочередно или при необходимости и при соответствующем выполнении отсчетного устройства одновременно. Третий режим с учетом коррекции амплитудно-фазовых характеристик, осуществленных в двух предыдущих режимах, обеспечивает повышенную точность и помехоустойчивость измерения дифференциальной составляющей входных сигналов. Первые гармоники сигналов, дифференциальная составляющая которых подлежит измерению, имеет вид: LJ,(t) V, sincot; (1) Ui(t) Y sinCut +Cf) , (2) где V| и V - амплитудные значения сигналов Ji(t) и Ug (t) ; Ц - относительный фазовый сдвиг между сигналами; U 21Т - круговая частота. В режиме коррекции амплитуднофазовой неидентичности каналов источник сигнала (Jr (t) поступает на вход первого аттенюатора 1 и через первьш ключ 3 на вход аттенюатора 2. Режим коррекции амплитудно-фазовых характеристик каналов осуществляется в два этапа. Перед выполнением первого этапа второй вход формирователя 10 разностного сигнала и первьш вход формирователя 13 суммарного сигнала через ключи 11 и 12 подключены к общей шине, первый вход интегратора 25 и вход интегратора 24 через ключ 47 соединен с выходом ключа 45, а второй вход интегратора 25 и вход интегратора 26 через ключ 50 подключен к выходу ключа 49. Ключи 4, 8, 29 и 33 разомкнуты. Если считать, что в исходном состоянии фазовращатели 5 и 6 не вносят фазового сдвига в сигналы, проходящие через них, коэффициенты передачи фазовращателей 5 и 6 и формировате лей 10 и 13 равны единице, а цифровые коды на выходе запоминающих блоков 9 и 30 - нулю, то сигналы на входах преобразователя 7 фаза - код и на выходах формирователей 10 и 13 имеют вид: UUt) 1, U,(t)- K, V, sinut; (3) U(t) ,(t) г, sinCcjt -I-AQ), где utf - фазовая неидентичность входных трактов; К|-Кд +KyN - коэффшдиент передачи первого аттенюатора 1; де элемента 42 постоянно присутству ет нулевое напряжение. Таким образом, при U(t) О чере ключи 46 и 47 происходит подключени опорного генератора 23 к первому входу интегратора 25 и входу интегратора 24, при Ll(t) 0 через ключи 48 и 50 - к второму входу интеграто ра 25 и входу интегратора 26. На выходе второго интегратора 25 фиксируется отсчет: N 1 2-КуЬК Л -V Знак определяется выходным сигна лом компаратора 27. Введением кода (12) в запоминающий блок 30 через ключ 29 завершается этап точной коррекции амплитудной неидентичности каналов. В данном случае погрешность коррекции, контролируемая по коду на выходе интегратора 25, может быть записана в иде: ±uN -V ..и ил где йК -.г- В результате второго этапа корре ции точность коррекции возрастает . в К раз. Перед выполнением второго режима автоматической компенсации фазового сдвига межде входными сигналами, ис точник сигнала У,(t) подключается к входу аттенюатора 1, а источник UjCt) через второй ключ 4 - к входу второго аттенюатора 2, который одно временно отключается ключом 3 от ис точника и,(t). Перед подачей сигналов (J, (t) и U2(t) запоминающий блок 9 устанавливается в нулевое состояние,- а запоминающий блок 30 хранит коды коррекции предьщущего режима. После подачи сигналов (1) и (2) на входы устройства преобразователь 7 фаза - код фиксирует на выходе цифровой отсчет, пропорциональный фазовому сдвигу Cf : (1 Введением кода (14) в запоминающи блок 9 обеспечивается компенсация фаз.ового сдвига (f между сигналами, а следовательно, повьшзается чувствительность измерения дифференциальной составляющей входных сигналов. Если однорременно с указанной компенсацией у необходимо измерить каждый из указанных сигналов, предварительное значение их дифференциальной составляющей, то перед исполнением данного этапа формирователи 10 и 13 с помощью ключей 11 и 12 переводятся в режим одновходовых усилителей, а вход отсчетного блока 28 подключается к выходу интегратора 24 ,26 или 25. Ключ 33 остается в закрытом состоянии. Исходя из векторных диаграмм сумм сигналов (1) и (2) находят, что ам-: плитуда суммарного сигнала, поступающего на вход тактового генератора 18 до значений фазового сдвига между сигналами U|(t) и (i(t)f до 90° больше большего значения сигнала, что обеспечивает надежную работу устройства при более низких уровнях одного из сигналов. После проведения коррекций в предьздущих режимах вольтметр готов к точному измерению дифференциальной составляющей входных сигналов. Для этого формирователи 10 и 13 с помощью ключей 11 и 12 переводятся в режим формирования разностного и суммарного сигналов, запоминающие блоки 30 и 9 хранят коды коррекции амплитудной неидентичности каналов и фазового сдвига между сигналами. Ключи 47 и 50 переводятся в положения второго этапа точной коррекции амплитудной неидентичности каналов, а ключ 33 - в открытое состояние. ;В результате цикла измерения аналогичного описанному при втором этапе коррекции интегратор 25 фиксирует на своем выходе цифровой отсчет, пропорциональный среднему значению дифференциальной составляющей входных сигналов, несущий информацию и о ее знаке, а интегратор 34 - цифровой отсчет, пропорциональный среднему значению суммы входных сигналов.. Используя выходные коды интеграторов 25 и 34, а также формулы: y, + Ui у,-и. Ut - - - и. +Uj U, 2 а выходе формирователя 35 суммарноо сигнала и, следовательно, отсчетом блоке 28 появляется сигнал, проорциональный среднему значению 131 напряжения (1), аналогично на выходе формирователя 36разностного сигнала и отсчетном блоке 28 - сигнал, пропорциональный среднему значению напряжения (2) . Таким образом, вольтметр обладает повышенной чувствительностью к уровням входных сигналов и позволяет одновременно с измерением их дифференциальной составляющей измерять уровни обоих сигналов. Формулаизобретения Цифровой интегрирукщий вольтметр, содержащий первьш и второй управляемые аттенюаторы, сигнальный вход пер вого управляемого аттенюатора соединен с шиной первого входного сигнала а сигнальный вход второго управляемого аттенюатора через первый ключ соединен с сигнальным входом первого управляемого аттенюатора и через второй ключ - с шиной второго входного сигнала, выход первого управляе мого аттенюатора подключен к сигналь ному входу первого управляемого фазо вращателя и к первому входу преобразователя фаза - код, выход второго управляемого аттенюатора - к сигналь ному входу второго управляемого фазо вращателя и к второму, входу преобразователя фаза - код, выход которого через последовательно соединенные третий ключ и первый запоминающий блок соединен с управляющими входами первого и второго управляемых фазовращателей, выход первого управляемого фазовращателя подключен к первому входу первого формирователя раз ностного сигнала и через четвертьш ключ - к первому входу первого фор. мирователя суммарного сигнала, выход второго управляемого фазовращателя соединен с вторым входом первого формирователя суммарного сигнала и через пятый ключ - е вторым входом первого формирователя разностного сигнала, вторые входы четвертого и пятого ключей подключены к общей шине выход первого формирователя разностного сигнала подключен к первым входам первого и второго блоков сравнения, второй вход первого блока сравнения соединен с первым входом третьего блока сравнения, с выхо дом генератора пилообразного напря72жения, с первым входом тактового генератора и через инвертор - с вторыми входами второго и третьего блоков сравнения,и вторым входом тактового генератора, выход первого формирователя суммарного сигнала подключен к третьему входу тактового генератора, прямые вьЕходы первого, второго и третьего блоков сравнения соединены соответственно с первым, вторым и третьим входами логического блока, а их инверсные выходы - с четвертым, пятым и щестым входами логического блока, седьмой, восьмой, девятый и десятый входы которого подключены соответственно к первому, второму, третьему и четвертому выходам тактового генератора, пятый выход которого соединен с входом запуска генератора пилообразного напряжения, первый и второй выходы логического блока соответственно подключены к первому и второму управляющим входам первого ключевого элемента, а третий и четвертьй выходы логического блока - к первому и второму управляющим входам второго ключевого элемента, сигнальные входы первого и второго ключевых элементов подключены к выходу опорного генератора, выход первого ключевого элемента подключен к входу первого интегратора и первому входу второго интегратора, выход второго ключевого элемента к входу третьего интегратора и второму входу второго интегратора, выходы первого и третьего интеграторов через компаратор соединены с управляннцим входом второго интегратора, выходом соединенного с первым входом отсчетного блока, и через последовательно соединенные шестой ключ и второй запоминающий блок с управляющими входами первого и второго управляемых аттенюаторов, управляющие входы первого, второго, третьего, четвертого, пятого, иестого ключей и третьи управляющие входы первого и второго ключевых элементов соединены соответственно с шестым, седьмым, восьмым, девятым, десятым, одиннадцатым, двенадцатым и тринадцатым выходами тактового генератора, отличающийся тем, что, с целью повышения чувствительности и расширения функциональных возможностей, в него введены второй и третий формирователи суммар1512672

ного сигнала, второй формирователь разностного сигнала, седьмой и восьмой ключи и четвертый интегратор, причем первый и второй входы второго формирователя суммарного сигнала сое- 5 инены соответственно с выходами первого и второго управляемых фазовращателей, а его выход - с четвертым входом тактового генератора, управляющий вход седьмого ключа подклю- Ю чен кчетвертому выходу логического блока, сигнальный вход седьмого ключа подключен к выходу опорного гене7216

ратора, а выход седьмого ключа через восьмой ключ подключен к входу четвертого интегратора, выход которого соединен с первыми входами третьего формирователя суммарного сигнала и второго формирователя разностного сигнала, вторые входы которых соединены с выходом второго интегратора, а выходы - с первым и третьим входами отсчетного блока, при этом управляющий вход восьмого ключа подключен к четьфнадцатому выходу тактового генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1285392A1 |

| Стробоскопический преобразователь | 1990 |

|

SU1721522A1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094915C1 |

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 2003 |

|

RU2248097C2 |

| Адаптивный корректор многоканального сигнала с ортогональными составляющими | 1990 |

|

SU1807571A1 |

| УСТРОЙСТВО ДЛЯ КОМПЕНСАЦИИ АМПЛИТУДНО-ЧАСТОТНЫХ ИСКАЖЕНИЙ В ЛИНЕЙНЫХ ТРАКТАХ С ИСПОЛЬЗОВАНИЕМ ДВУХМЕРНЫХ МЕТРИЧЕСКИХ ПРОСТРАНСТВ | 2006 |

|

RU2342781C2 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

| Цифровой интегрирующий вольтметр | 1981 |

|

SU974287A1 |

Изобретение может быть использовано при измерении среднего значения дифференциальной составляющей двух напряжений произвольной формы. Цель изобретения - повышение чувствительности и расширение функциональных вoзмoжнocteй. Устройство содержит управляемые аттенюаторы 1 и 2, ключи 3, 4, 8, 11, 12 и 29, управляемые фазовращатели 5, 6, преобразователь 7 фаза - код, запоминающие блоки 9 и 30, формирователь 10 разностного сигнала, формирователь .13 суммарного сигнала, блоки 14, 15 и 16 сравнения, генератор 17 пилообразного напряжения. Тактовый генератор 18, инвертор 19, логический блок 20, ключевые элементы ,21 и 22, опорный генератор 23, интеграторы 24, 25 и 26, компаратор 27 и отсчетньй блок 28. Введение формирователей 31 и 35 суммарного сигнала, ключей 32 и 33, интегратора 34, формирователя 36 разностного сигнала и образование новых связей между элементами устройства i позволяет использовать для синхронизации тактового генератора 1Q во СЛ всех режимах работы вольтметра суммы входных сигналов и обеспечивает возможность измерения уровней входных сигналов одновременно с измерением их дифференциальной составляющей. 6 ил.

(PU8. 2

Н

Фиг. 3 „PsjKufiaffmoРе/кимаВто-матическоиматическойкатенсации коррекциисразоЗого Выходи coausa

Фиг.5

п п п ппг-11- t

п п п пгпг-

и

п п п п

п Г1 п

к л

п п п п п п ,

W 1 п п I-I п п , t I ППП1-1ППП

Фиг.6 Режим измерений

| Цифровой интегрирующий вольтметр | 1981 |

|

SU974287A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-10-30—Публикация

1985-01-02—Подача