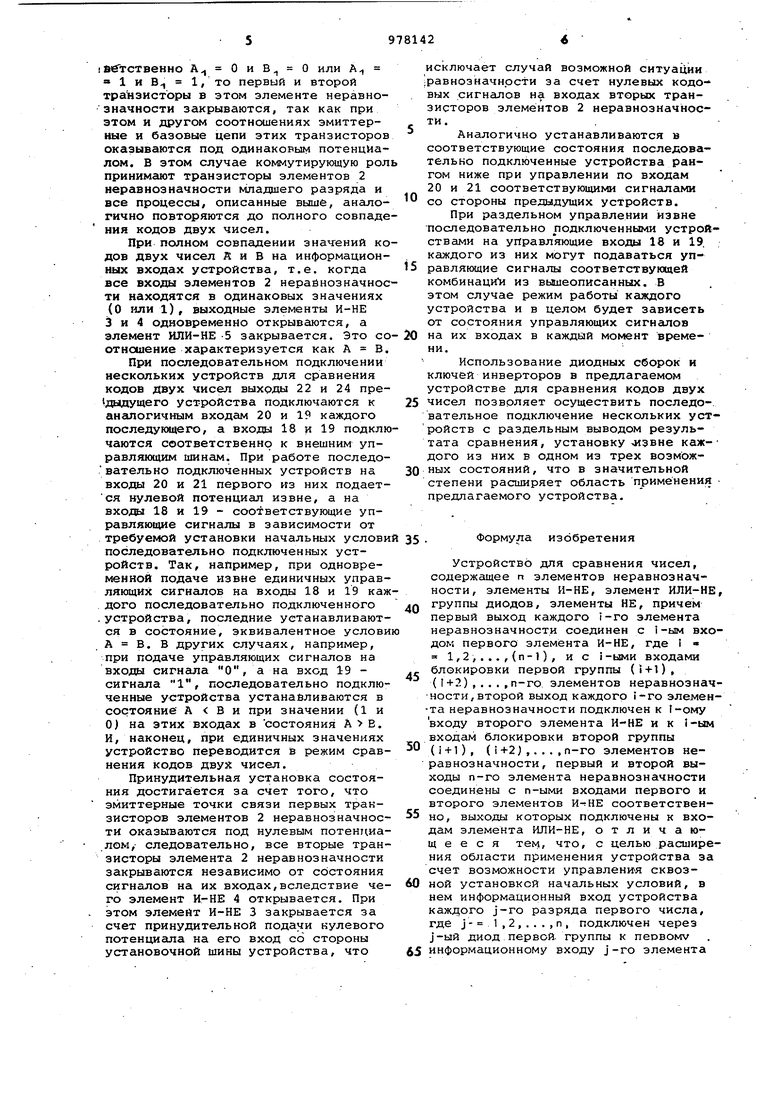

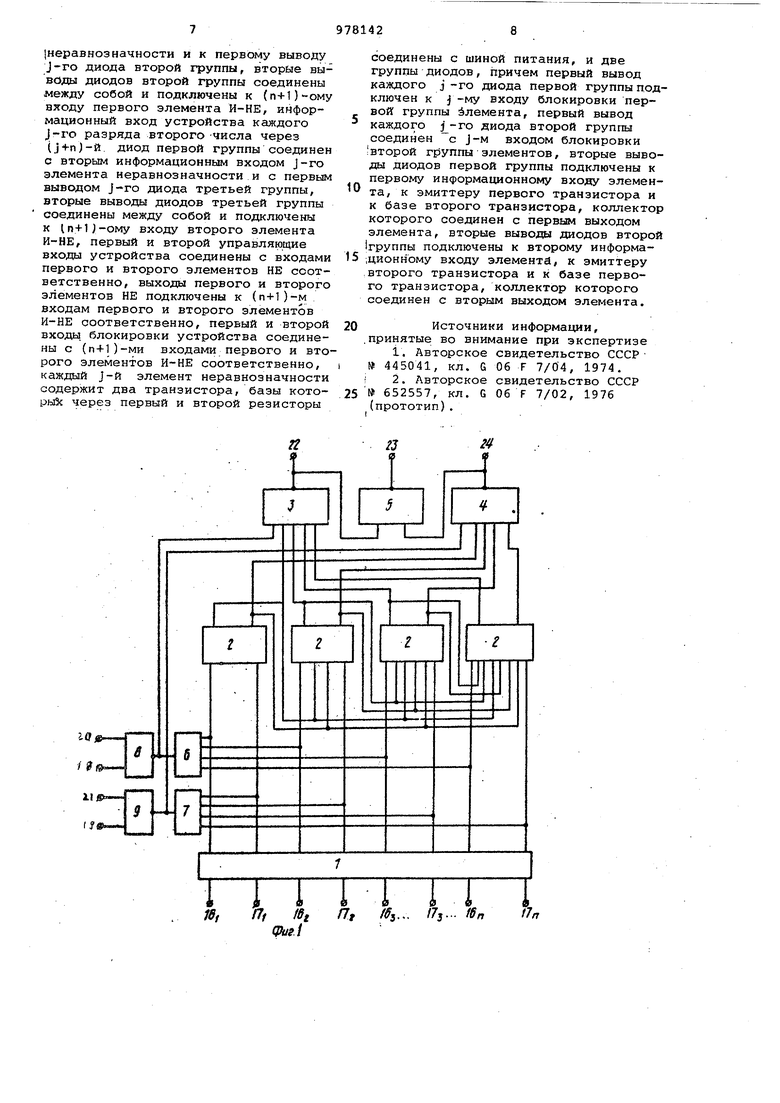

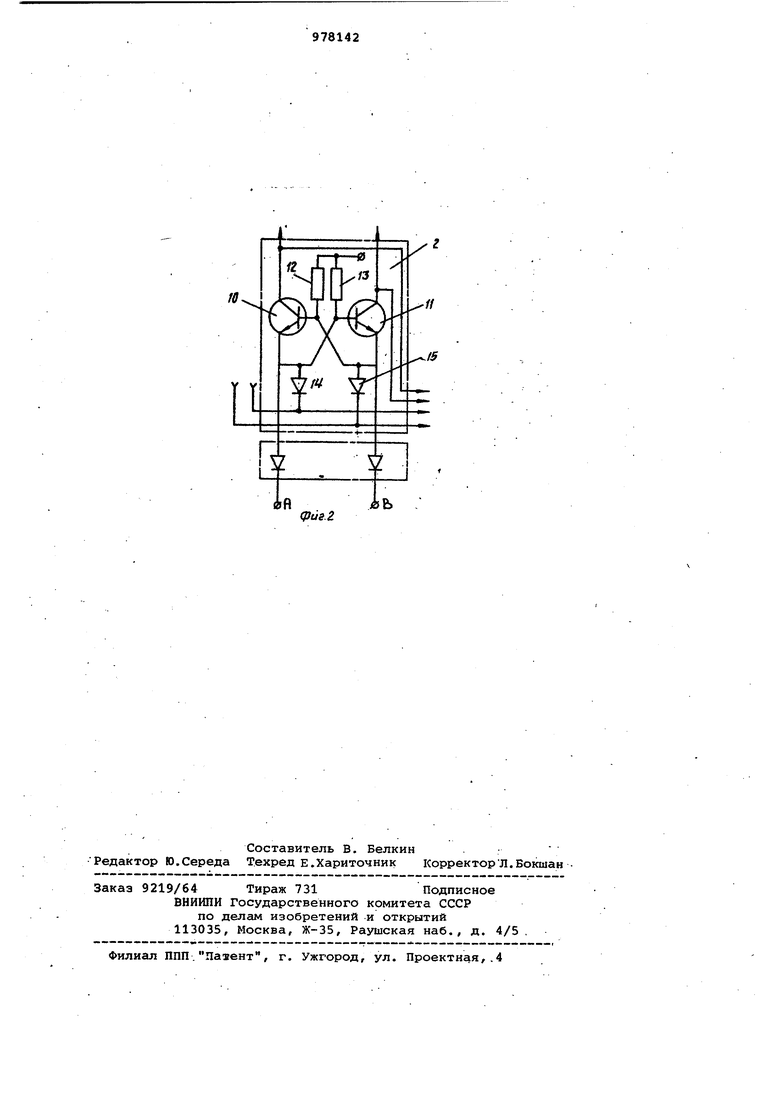

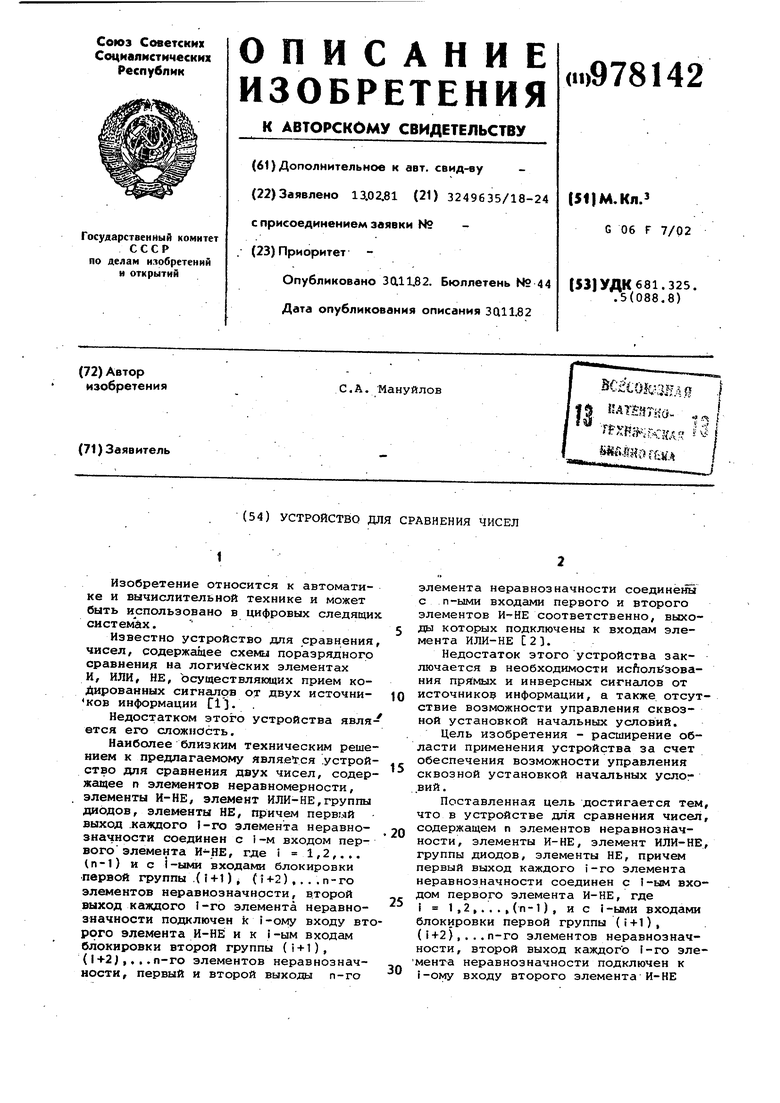

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых следящи системах. Известно устройство для сравнения чисел, содержащее схемы поразрядного сравнения на логических элементах И, ИЛИ, НЕ, осуществляющих прием код1(ироваиных сигналов от двух источни ков информации С1. . Недостатком этого устройства явля ется его сложность. Наиболее близким техническим реше нием к предлагаемому является .устрой ство для сравнения двух чисел, содер жащее п элементов неравномерности, элементы И-НЕ, элемент ИЛИ-НЕ,группы диодов, элементы НЕ, причем первый выход .каящого 1-го элемента неравнозначности соединен с i-м входом первого элемента И-НЕ, где i 1,2,... (п-1) и с i-ыми входами блокировки первой группы .( Я-1), (i-i-2) ,, . .п-го элементов неравнозначности, второй выход каждого 1-го элемента неравнозначности подключен к i-ому входу вт рого элемента И-НЕ и к i-ым входам блокировки второй группы (i+1), ( H-2i,,..п-го элементов неравнозначности, первый и второй выходы п-го элемента неравнозначности соединены с п-ыми входами первого и второго элементов соответственно, выходы которых подключены к входам элемента ИЛИ-НЕ С 2). Недостаток этого устройства заключается в необходимости исйол1 зования прямых и инверсных сигналов от источников информации, а также отсутствие возможности управления сквозной установкой начальных условий. Цель изобретения - расширение области применения устройства за счет обеспечения возможности управления сквозной установкой начальных усло.вий. Поставленная цель достигается тем, что в устройстве для сравнения чисел, содержащем п элементов неравнозначности, элементы И-НЕ, элемент ИЛИ-НЕ, группы диодов, элементы НЕ, причем первый выход каждого i-ro элемента неравнозначности соединен с 1-ым входом первого элемента И-НЕ, где i 1 ,2 ,. . , , ( , и с i-ыми входами блокировки первой группы (i+1), (i +2),...n-го элементов неравнозначности, второй выход каждого i-ro элемента неравнозначности подключен к i-ому входу второго элемента И-НЕ и к t-ым входам блокировки второй .группы (i+1), (1+2},.,.,п-го элементов неравнозначности, перый и второй (ВЫХОДЫ п-го элемента неравнозначности ..соединены с п-ыми входами перво го и второго элементов И-НЕ соответственно, выходы которых подключены к входам элемента ИЛИ-НЕ, информационный вход устройства каждого j-ro раз ряда первого числа, где j 1,2,..., подключен- через J-ый диод первой гру пы к первому информационному входу. J-ro элемента неравнозначности и к первому выводу j-ro диода второй :группы, вторые выводы диодов второй группы соединены между собой и подключены к (п+П-ому входу первого элемента И-НЕ, информационный вход устройства каждого j-ro разряда второго числа через (j+n)-ый диод первой группы соединен с вторым информационным входом j-ro элемента нерав нозначности и с первым выводом j-rp диода третьей группы, вторые выводы диодов третьей группы соединены между собой и подключены к (п+1)-ому входу второго элемента И-НЕ, первый и второй ..управляющие входы устройства соединены с входами первого и вто рого элементов НЕ соответственно, вы ходы первого и второго элементов НЕ подключены к (п+1)-ым входам первого и второ.го элементов И-НЕ соответственно, первый и второй входы блокировки устройства соединены с (п+1)-ы входами первого и второго элементов соответственно, каждый j-ый элемент неравнозначности содержит два транзистора, базы которых через первый и второй резисторы соединены с шиной пита;ния, и две группы диодов причем первый вывод каждого j-ro диода первой группы подключен к j-ом входу блокировки первой группы элемента, первый вывод каждого j-ro дио да второй группы соединен с j-ым входом блокировки второй группы элементов, вторые выводы диодов первой группы подключены к первому информационному входу элемента, к эмиттеру первого транзистора и к базе второго транзистора, коллектор которого соединен с первым выходом элемента, вто рые выводы диодов второй группы подключены к второму информационному входу элемента, к эмиттеру второго транзистора и к базе первого транзис тора, коллектор которого соединен с вторым выходом элемента. На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - принципиальная схема одiHoro из элементов неравнозначности устройства. Устройство содержит группу диодов 1, п элементов неравнозначности 2у 27,..,2пI элементы И-НЕ 3 и 4, элемент ИЛИ-НЕ 5., группы диодов 6 и 7, элементы НЕ 8 и 9. Элементы 2 неравнозначности содержат транзисторы 10 и 11, резисторы 12 и 13, диоды первой группы 14, диоды второй группы 15, устройство имеет информационные входы 16, 16j,...16n, 17, 172,... 17п,. входы 18 и 19 управления, входы 20 и 21 блокировки, выходы 22-24. Устройство работает следующим образом. При одновременной подаче сигналов от источников А и В информации на соответствующие входы элементов 2 неравнозначности сравнение значений чисел производится поразрядно, начиная от стариего разряда. Так, например, если на входы А и В элементов 2 неравнозначности старшего разряда поданы сигналы соответственно А О, В 1, то первый транзистор- в этом элементе неравнозначности открывается вследствие того, что его база находится под высоким потенциалом, а эмиттер - под нулевым. Второй транзистор в этом элементе неравнозначности закрывается вследствие того, что его база находится под нулевым, а эмиттер - под высоким потенциалом. Через открытый транзиртор элемента 2 неравнозначности старшего разряда и диоды подаетсяпотенциал на эмиттеры первых, и базы вторых транзисторов всех последующих элементов 2 неравнозначности младших разрядов. В этом случае вторые транзисторы элементов 2 неравнозначности закрываются, независимо от значения сигналов на их входах, а первые транзисторы этих же элементов могут находиться в безразличном состоянии. При этом элемент И-НЕ 3 закрывается вследствие того, что,по крайней мере, один из первых транзисторов элемента 2 неравнозначности находится в открытом состоянии, а -элемент И-НЕ 4 открывается, так как все вторые транзисторы элементов 2 неравнозначности закрыты. Выходной элемент ИЛИ-НЕ 5 также находится в открытом состоянии вследствие того, что выходной элемент И-НЕ 3 закрыт. Высокий уровень потенциала на выходе элемента И-НЕ 3 соответствует соотношению А В. В противном случае, если на входы элемента 2 неравнозначности старшего разряда поданы кодовые сигналы соответственно А 1, В-) 0, то выходные элементы И-НЕ 3 и ИЛИ-НЕ 5 будут находиться в открытом состоянии, а элемент И-НЕ 3 закрывается. Высокий уровень потенциала на выходе элемента И-НЕ 4 в этЬм случае соответствует соотношению А В. .Если на выходы элемента 2 неравнозначности старшего разряда подаются одноуровневые кодовые сигналы соотбтственно или А 1 и В 1, то первый и второй ранзисторы в этом элементе неравноначности закрываются, так как при том и другом соотношениях эмиттерные и базовые цепи этих транзисторов оказываются под одинаковым потенциаом. В этом случае коммутирующую роль принимгиот транзисторы элементов 2 неравнозначности младшего разряда и все процессы, описанные выше, аналогично повторяются до полного совпадения кодов двух чисел.

При полном совпадении значений кодов двух чисел Д и В на информационных входах устройства, т.е. когда все входы элементов 2 нерайнозначности находятся в одинаковых значениях (О или 1), выходные элементы И-НЕ 3 и 4 одновременно открываются, а элемент ИЛИ-НЕ -5 закрывается. Это соотношение характеризуется как А В. При последовательном подключении нескольких устройств для сравнения кодов двух чисел выходы 22 и 24 предыдущего устройства подключаются к аналогичным входам 20 и 19 каждого последующего, а входы 18 и 19 подключаются соответственно к внешним управл51ю цим шинам. При работе последовательно подключенных устройств на входы 20 и 21 первого из них подается нулевой потенциал извне, а на входы 18 и 19 - соответствующие управляющие сигналы в зависимости от требуемой установки начальных условий последовательно подключенных устройств. Так, например, при одновременной подаче извне единичных управляющих сигналов на входы 18 и 19 каждого последовательно подключенного

устройства, последние устанавливаются в состояние, эквивалентное условию А В. В других случаях, например, при подаче управляющих сигналов на входы сигнала О, а на вход 19 сигнала 1, последовательно подключенные устройства устанавливаются в состояние А В и при значении (1 и 0) на этих входах в состояния А Е. И, наконец, при единичных значениях устройство переводится в режим сравнения кодов двух чисел.

Принудительная установка состояния достига1ется за счет того, что эмиттерные точки связи первых транзисторов элементов 2 неравнозначности оказываются под нулевым потенциалом/ следовательно, все вторые транзисторы элемента 2 неравнозначности закрываются независимо от состояния сигнс1лов на их входах,вследствие чего элемент И-НЕ 4 открывается. При этом элемент И-НЕ 3 закрывается за счет принудительной подачи нулевого потенциала на его вход со стороны установочной шины устройства, что

исключает случай возможной ситуации ;равнозначнрсти за счет нулевых кодовых сигналов на входах вторых транзисторов элементов 2 неравнозначности.

Аналогично устанавливаются в

соответствующие состояния последовательно подключенные устройства рангом ниже при управлении по входам 20 и 21 соответствующими сигналами

со стороны предыдущих устройств.

При раздельном управлении извне последовательно подключенными устройствами на управляющие входы 18 и 19. каждого из них могут подаваться управляющие сигналы соответствующей комбинаций из вышеописанных. В этом случае режим работы каждого устройства и в целом будет зависеть от состояния управляющих сигналов

на их входах в каждый момент времени.

Использование диодных сборок и ключей инверторов в предлагаемом устройстве для сравнения кодов двух

чисел позволяет осуществить последо-. вательное подключение нескольких устройств с раздельным выводом результата сравнения, установку лзвне каж- дого из них в одном из трех воэможных состояний, что в значительной

степени расширяет область применения предлагаемого устройства.

Формула изобретения

35 .

Устройство для сравнения чисел, содержащее п элементов неравнозначности, элементы И-НЕ, элемент ИЛИ-НЕ,

0 диодов, элементы НЕ, причем первый выход каждого i-ro элемента неравнозначности соединен с 1-ым входом первого элемента И-НЕ, где i « 1,2,...,(п-1), и с i-ыми входами

г блокировки первой группы (+1),

(t+2)....,п-го элементов неравнозначности, второй выход каждого i-ro элемента неравнозначности подключен к 1-ому входу второго элемента И-НЕ и к i-ым входам блокировки второй группы (i+l), (i+2),...,п-го элементов неравнозначности, первый и второй выходы п-го элемента неравнозначности соединены с п-ыми входами первого и второго элементов соответствен5

но, выходы которых подключены к входам элемента ИЛИ-НЕ, отличающееся тем, что, с целью расширения области применения устройства эа счет возможности управления сквозной установкой начальных условий, в нем информационный вход устройства каждого j-ro разряда первого числа, где j- 1 , 2 , . . . , п , подключен через j-ый диод первой, группы к первому

55 информационному входу j-ro элемента неравнозначности и к первому выводу J-ro диода второй группы, вторые выводы диодов второй группы соединены между собой и подключены к (п+1)ому входу первого элемента И-НЕ, информационный вход устройства каждого j-ro разряда второго -числа через (j4-n)-й. диод первой группы соединен с вторым информационным входом J-ro элемента неравнозначности и с первым выводом J-ro диода третьей группы, вторые выводы диодов третьей группы соединены между собой и подключены к 1п+и-ому входу второго элемента И-НЕ, первый и второй управляющие входы устройства соединены с входами первого и второго элементов НЕ соответственно, выходы первого и второго элементов НЕ подключены к (п+1)-м входам первого и второго элементов И-НЕ соответственно, первый и второй входы, блокировки устройства соединены с (п-И)-ми входами первого и вто рого элементов И-НЕ соответственно, каждый J-й элемент неравнозначности содержит два транзистора, базы котоphik через первый и второй резисторы

п

Г I i i i i

/7 I6i П, /ifj... /73... 16 n

19, фиг I

t7n соединены с шиной питания, и две группы диодов, причем первый вывод каждого j-го диода первой группы подключен к j -му входу блокировки первой группы Элемента, первый вывод каждого диода второй группы соединен с J-M входом блокировки ;второй группы элементов, вторые выводы диодов первой группы подключены к первому информационному входу элемента, к эмиттеру первого транзистора и к базе второго транзистора, коллектор которого соединен с первым выходом элемента, вторые выводы диодов второй Ьруппы подключены к второму информадионному входу элемента, к эмиттеру второго транзистора и к базе первого транзистора, коллектор которого соединен с вторым выходом элемента. Источники информации, принятые во внимание при экспертизе i. Авторское свидетельство СССР № 445041, кл. G 06 F 7/04, 1974. 2. Авторское свидетельство СССР 652557, кл. G Об F 7/02, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1979 |

|

SU771666A1 |

| Устройство для сравнения двоичных чисел | 1982 |

|

SU1051530A1 |

| Адаптивное вычислительное устройство | 1977 |

|

SU734679A1 |

| Устройство для отображения графической информации на газоразрядном матричном индикаторе | 1987 |

|

SU1495846A1 |

| Устройство для выделения максимального из чисел | 1978 |

|

SU763889A1 |

| Устройство для выделения многоразрядного кода | 1978 |

|

SU746501A1 |

| Устройство для определения экстремальных чисел | 1980 |

|

SU903861A1 |

| Устройство для сравнения чисел | 1978 |

|

SU691847A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Устройство ассоциативного распознавания образов | 1985 |

|

SU1330644A1 |

Авторы

Даты

1982-11-30—Публикация

1981-02-13—Подача