Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ), и может быть реализовано в виде БИС ЗУ на совмещенных биполярных транзисторных п-р-п-р-структурах;

Цель изобретения - упрощение буферного ЗУ.

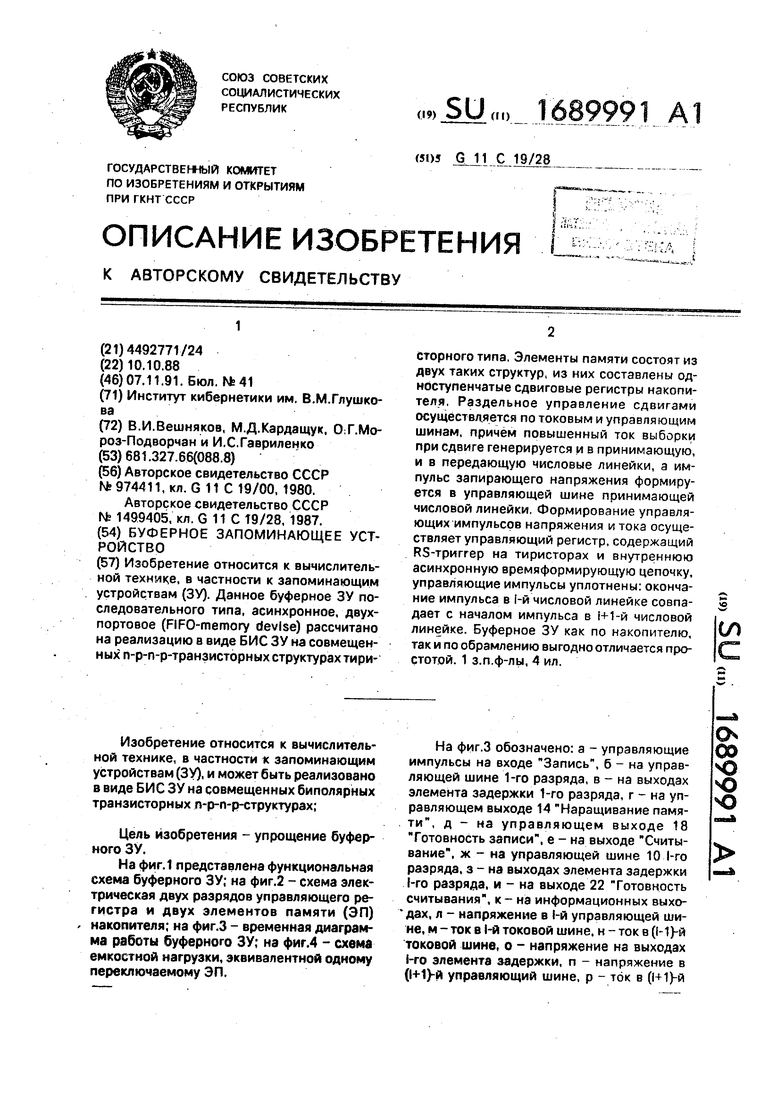

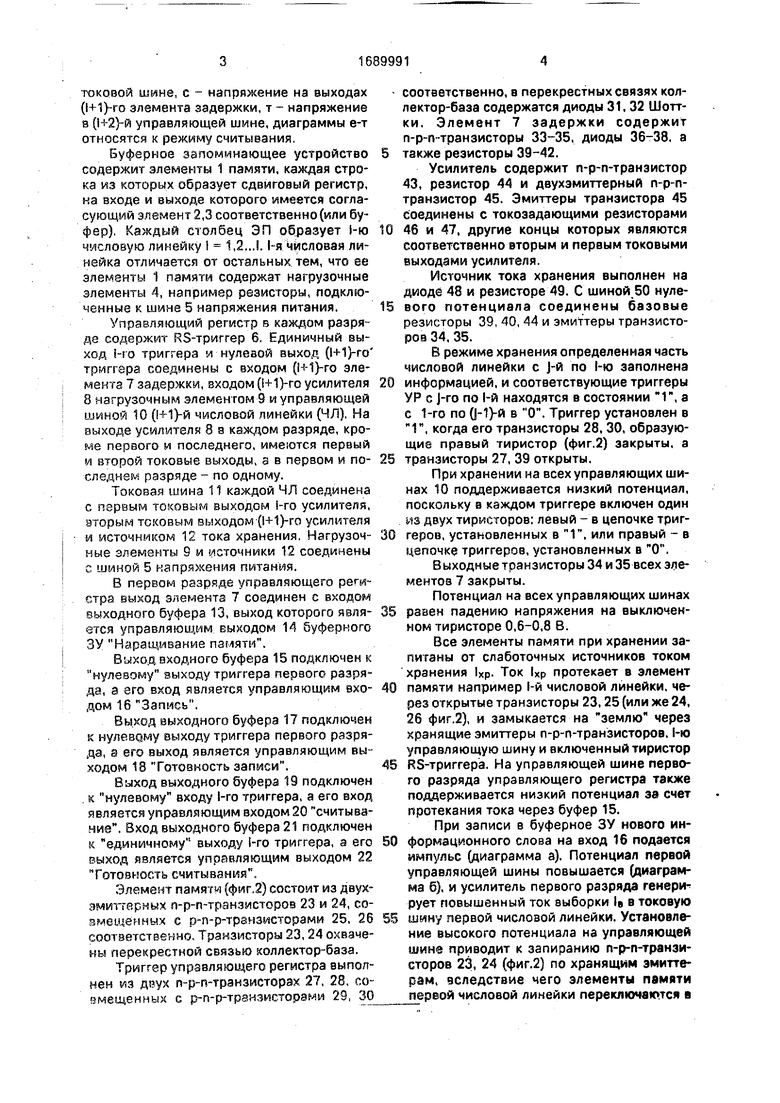

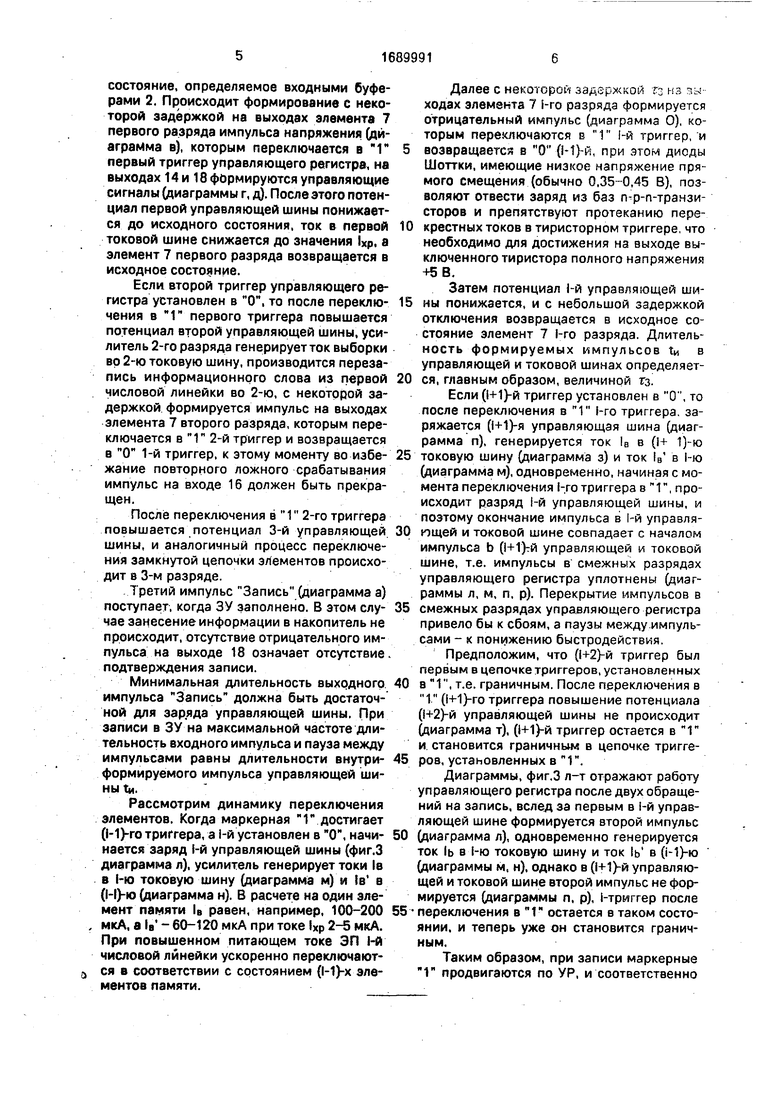

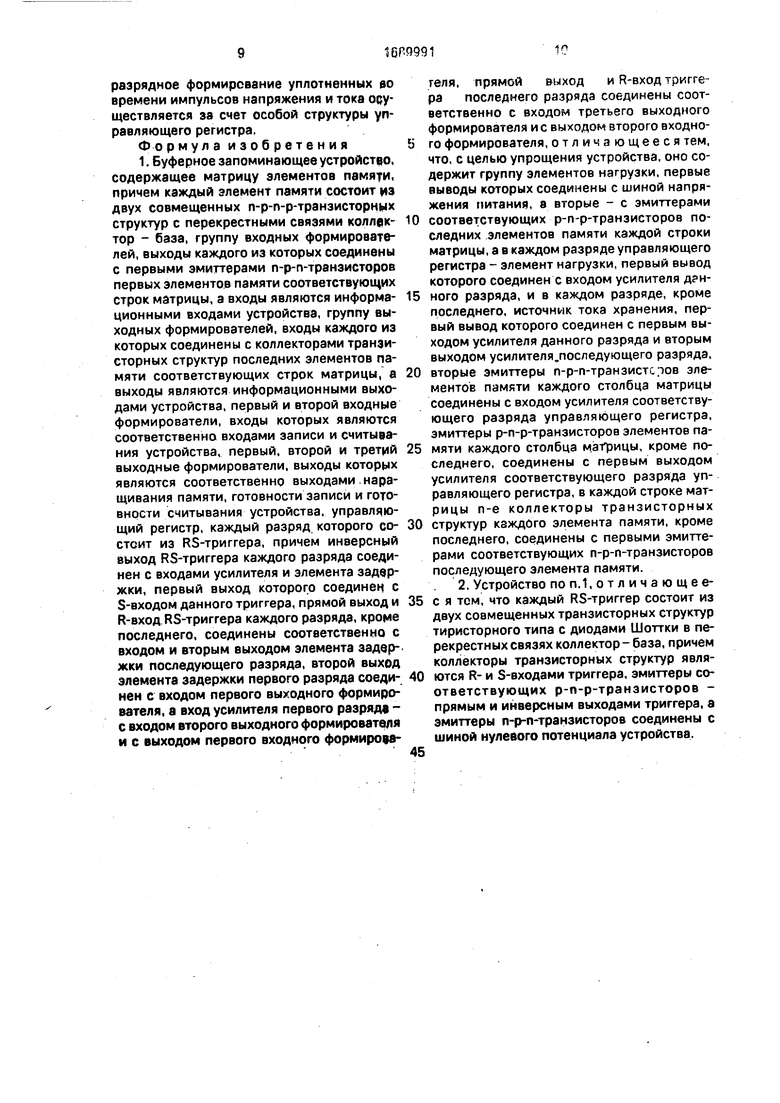

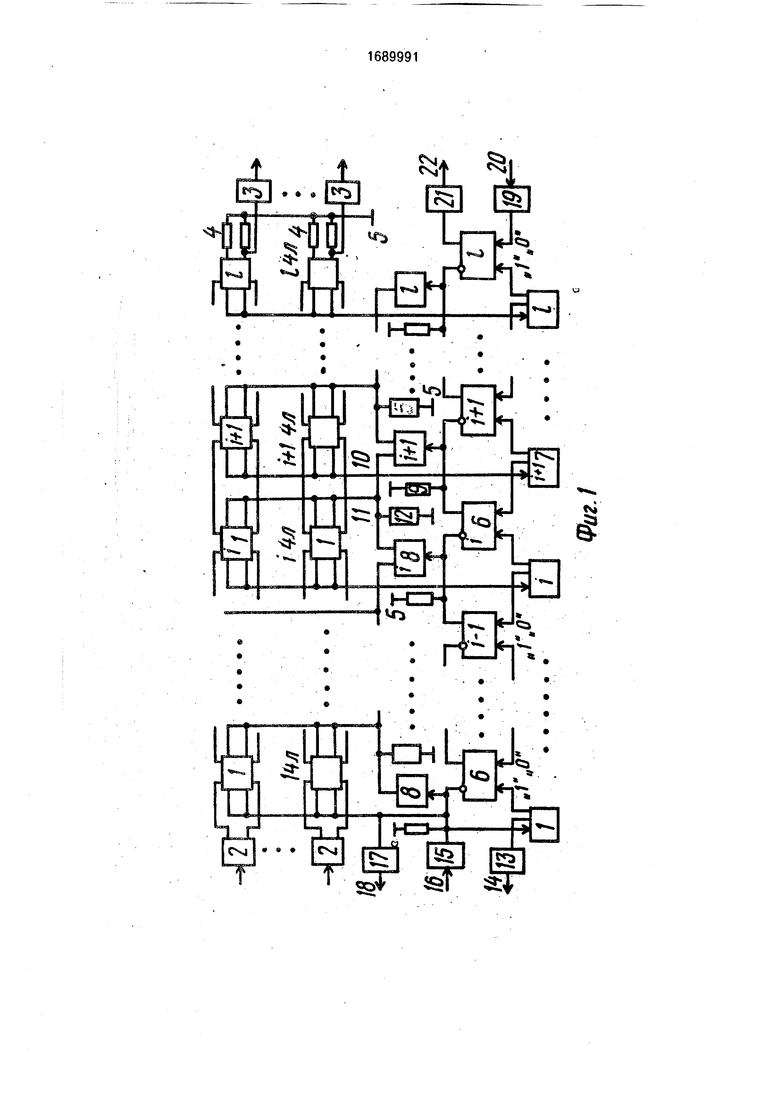

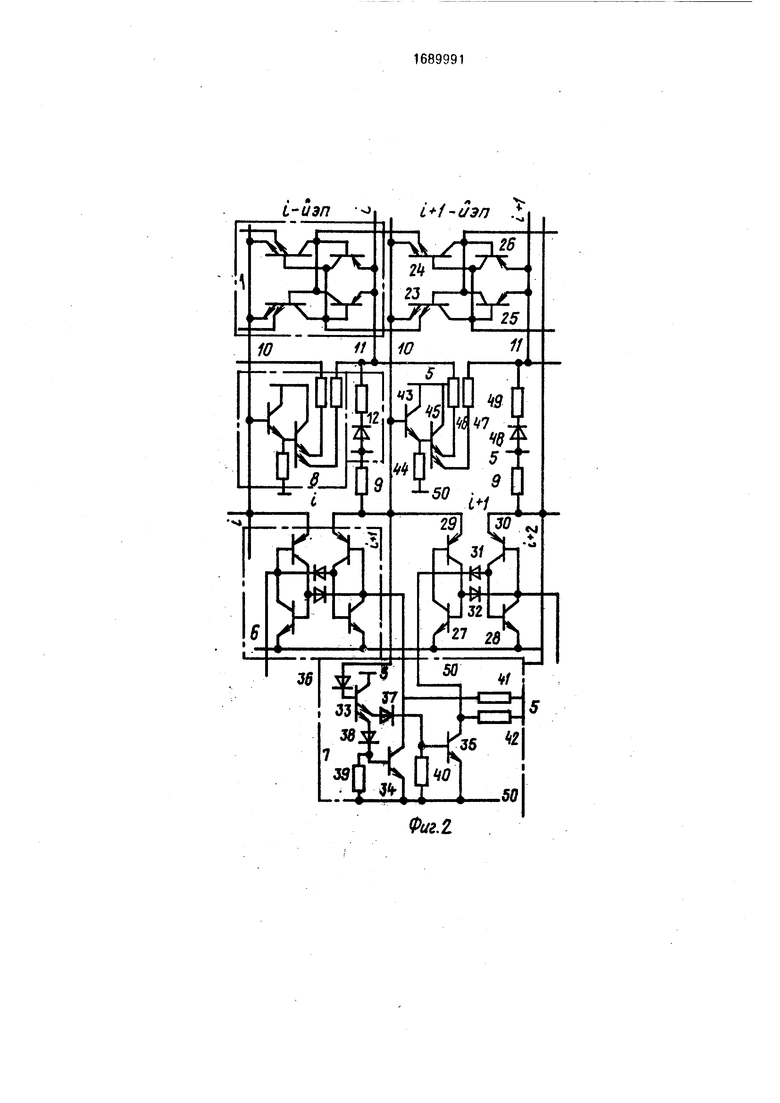

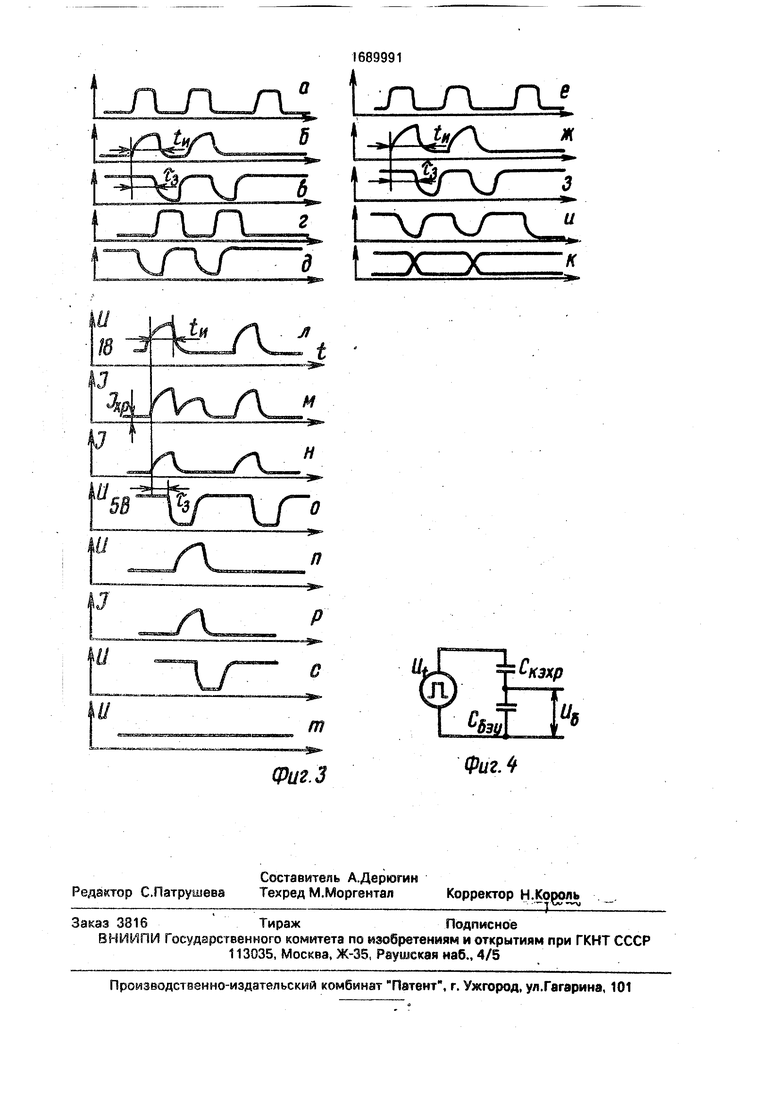

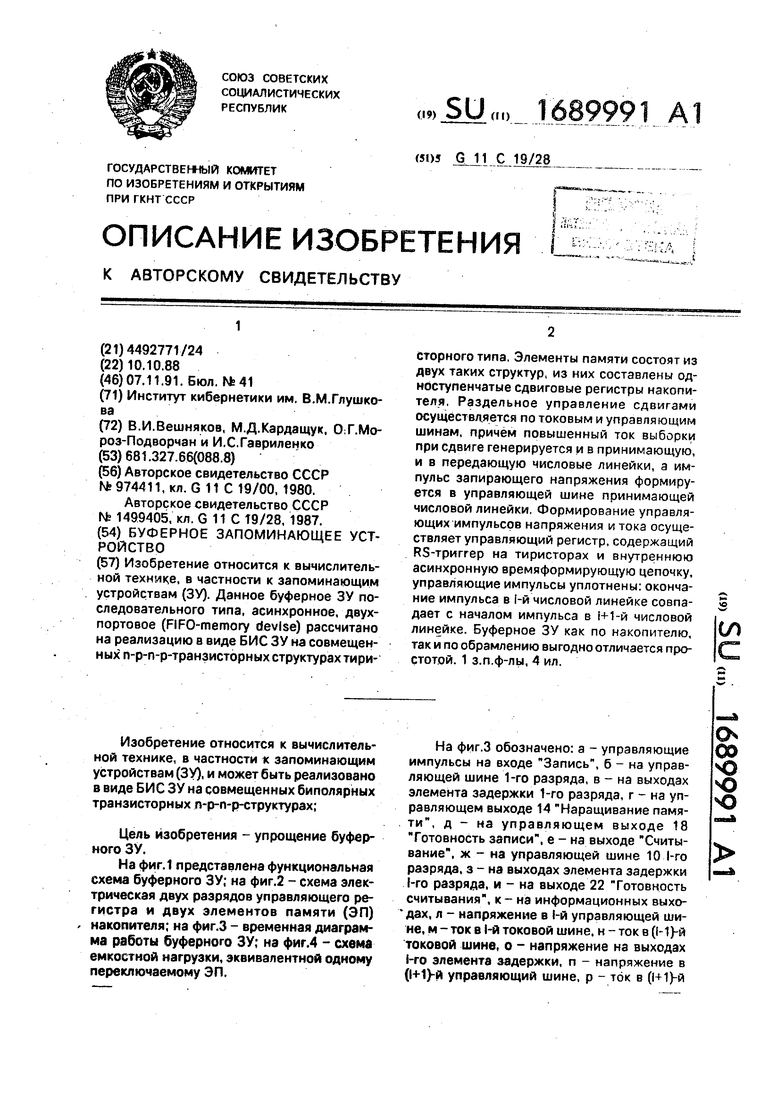

На фиг.1 представлена функциональная схема буферного ЗУ; на фиг.2 - схема электрическая двух разрядов управляющего регистра и двух элементов памяти (ЭП) накопителя; на фиг.З - временная диаграмма работы буферного ЗУ; на фиг.4 - схема емкостной нагрузки, эквивалентной одному переключаемому ЭЛ,

На фиг.З обозначено: а - управляющие импульсы на входе Запись, б - на управляющей шине 1-го разряда, в - на выходах элемента задержки 1-го разряда, г-на управляющем выходе 14 Наращивание памяти, д - на управляющем выходе 18 Готовность записи, е - на выходе Считывание, ж - на управляющей шине 10 1-го разряда, з - на выходах элемента задержки 1-го разряда, и - на выходе 22 Готовность считывания, к - на информационных выхо- дах, л - напряжение в 1-й управляющей шине, м - ток в 1-й токовой шине, н - ток в (И)-й токовой шине, о - напряжение на выходах 1-го элемента задержки, п - напряжение в (1+1)-й управляющий шине, р - ток в (1+1 )-й

о

00

ю ю ю

токовой шине, с - напряжение на выходах (+1)-го элемента задержки, т - напряжение в (+2)-й управляющей шине, диаграммы е-т относятся к режиму считывания,

Буферное запоминающее устройство содержит элементы 1 памяти, каждая строка из которых образует сдвиговый регистр, на входе и выходе которого имеется согласующий элемент 2,3 соответственно (или буфер). Каждый столбец ЭП образует 1-ю числовую линейку I 1.2...1.1-я числовая линейка отличается от остальных тем, что ее элементы 1 памяти содержат нагрузочные элементы 4, например резисторы, подключенные к шине 5 напряжения питания.

Управляющий регистр в каждом разряде содержит RS-триггер 6. Единичный выход Но триггера и нулевой выход (1+1}-го триггера соединены с входом (-Н)-го элемента 7 задержки, входом (1+1)-го усилителя 8 нагрузочным элементом 9 и управляющей шиной 10 (1+1)-й числовой линейки (ЧЛ). На выходе усилителя 8 в каждом разряде, кроме первого и последнего, имеются первый и второй токовые выходы, а в первом и последнем разряде - по одному.

Токовая шина 11 каждой ЧЛ соединена с первым токовым выходом 1-го усилителя, вторым токовым выходом (1+1)-го усилителя и источником 12 тока хранения. Нагрузочные элементы 9 и источники 12 соединены с шиной 5 напряжения питания.

В первом разряде управляющего регистра выход элемента 7 соединен с входом выходного буфера 13, выход которого является управляющим выходом 14 буферного ЗУ Наращивание памяти.

Выход входного буфера 15 подключен к нулевому выходу триггера первого разряда, а его вход является управляющим входом 16 Запись.

Выход выходного буфера 17 подключен к нулевому выходу триггера первого разряда, а его выход является управляющим выходом 18 Готовность записи.

Выход выходного буфера 19 подключен к нулевому входу 1-го триггера, а его вход является управляющим входом 20 считывание. Вход выходного буфера 21 подключен sc единичному выходу 1-го триггера, а его выход является управляющим выходом 22 Готовность считывания.

Элемент памяти (фиг,2) состоит из двух- эмиттерных п-р-п-транзисторов 23 и 24, со- ямещенных с р-п-р-транзисторами 25, 26 соответственно. Транзисторы 23,24 охвачены перекрестной связью коллектор-база.

Триггер управляющего регистра выполнен из друх п-р-п-транзисторах 27, 28, совмещенных с р-п-р-транзисторами 29, 30

- соответственно, в перекрестных связях коллектор-база содержатся диоды 31.32 Шотт- ки. Элемент 7 задержки содержит n-p-п-транзисторы 33-35, диоды 36-38, а

также резисторы 39-42.

Усилитель содержит п-р-п-транзистор 43, резистор 44 и двухэмиттерный п-р-п- транзистор 45. Эмиттеры транзистора 45 соединены с токоэадающими резисторами

0 46 и 47, другие концы которых являются соответственно вторым и первым токовыми выходами усилителя.

Источник тока хранения выполнен на диоде 48 и резисторе 49. С шиной 50 нуле5 вого потенциала соединены базовые резисторы 39. 40, 44 и эмиттеры транзисторов 34, 35.

В режиме хранения определенная часть числовой линейки с j-й по Но заполнена

0 информацией, и соответствующие триггеры УР с J-ro по 1-й находятся в состоянии Г, а с 1-го по (|-1)-й в О. Триггер установлен в 1, когда его транзисторы 28, 30, образующие правый тиристор (фиг.2) закрыты, а

5 транзисторы 27, 39 открыты.

При хранении на всех управляющих шинах 10 поддерживается низкий потенциал, поскольку а каждом триггере включен один из двух тиристоров: левый - в цепочке триг0 геров, установленных в 1, или правый - в цепочке триггеров, установленных в О.

Выходные транзисторы 34 и 35 всех элементов 7 закрыты.

Потенциал на всех управляющих шинах

5 равен падению напряжения на выключек- ном тиристоре 0,6-0,8 В.

Все элементы памяти при хранении за- питаны от слаботочных источников током хранения Хр. Ток Хр протекает в элемент

0 памяти например 1-й числовой линейки, через открытые транзисторы 23,25 (или же 24, 26 фиг.2), и замыкается на землю через хранящие эмиттеры n-p-n-транзисторов, 1-ю управляющую шину и включенный тиристор

5 RS-триггера. На управляющей шине первого разряда управляющего регистра также поддерживается низкий потенциал за счет протекания тока через буфер 15.

При записи в буферное ЗУ нового ин0 формационного слова на вход 16 подается импульс (диаграмма а). Потенциал первой управляющей шины повышается (диаграмма б), и усилитель первого разряда генерирует повышенный ток выборки В в токовую

5 шину первой числовой линейки. Установление высокого потенциала на управляющей шине приводит к запиранию п-р-п-транзисторов 23, 24 (фиг.2) по хранящим эмиттерам, вследствие чего элементы памяти первой числовой линейки переключаются в

состояние, определяемое входными буферами 2. Происходит формирование с некоторой задержкой на выходах элемента 7 первого разряда импульса напряжения (диаграмма в), которым переключается в Г 5 первый триггер управляющего регистра, на выходах 14 и 18 формируются управляющие сигналы (диаграммы г, д). После этого потенциал первой управляющей шины понижается до исходного состояния, ток в первой 10 токовой шине снижается до значения lxp, a элемент 7 первого разряда возвращается в исходное состояние.

Если второй триггер управляющего регистра установлен в О, то после переклю- 15 чения в 1м первого триггера повышается потенциал второй управляющей шины, усилитель 2-го разряда генерирует ток выборки во 2-ю токовую шину, производится перезапись информационного слова из первой 20 числовой линейки во 2-ю, с некоторой задержкой формируется импульс на выходах элемента 7 второго разряда, которым переключается в Г 2-й триггер и возвращается в О 1-й триггер, к этому моменту во избе- 25 жание повторного ложного срабатывания импульс на входе 16 должен быть прекращен.

После переключения в 1 2-го триггера повышается потенциал 3-й управляющей 30 шины, и аналогичный процесс переключения замкнутой цепочки элементов происходит в 3-м разряде.

Третий импульс Запись (диаграмма а) поступает, когда ЗУ заполнено. В этом слу- 35 чае занесение информации в накопитель не происходит, отсутствие отрицательного импульса на выходе 18 означает отсутствие, подтверждения записи.

Минимальная длительность выходного 40 импульса Запись должна быть достаточной для заряда управляющей шины. При записи в ЗУ на максимальной частоте длительность входного импульса и пауза между импульсами равны длительности внутри- 45 формируемого импульса управляющей шины 1и.

Рассмотрим динамику переключения элементов. Когда маркерная Г достигает (М)-го триггера, а 1-й установлен в О, начи- 50 нается заряд 1-й управляющей шины (фиг.З диаграмма л), усилитель генерирует токи 1в в 1-ю токовую шину (диаграмма м) и 1в в (М}-ю (диаграмма н). В расчете на один элемент памяти 1В равен, например, 100-200 55 , мкА1а1в -бО-120мкАпритоке1хр2-5мкА. При повышенном питающем токе ЭП 1-й числовой линейки ускоренно переключают- ся в соответствии с состоянием (1-1)-х элементов памяти.

Далее с некоторой задержкой г: из ы ходах элемента 7 i-ro разряда формируется отрицательный импульс (диаграмма О), которым переключаются в 1 1-й триггер, и возвращается в О (И}-й при этом диоды Шоттки, имеющие низкое напряжение прямого смещения (обычно 0,35-0,45 В), позволяют отвести заряд из баз п-р-п-транзи- сторов и препятствуют протеканию перекрестных токов в тиристорном триггере, что необходимо для достижения на выходе выключенного тиристора полного напряжения +5 В.

Затем потенциал 1-й управляющей шм- ны понижается, и с небольшой задержкой отключения возвращается в исходное состояние элемент 7 1-го разряда. Длительность формируемых импульсов и, в управляющей и токовой шинах определяется, главным образом, величиной тз.

Если (1+1)-й триггер установлен в О, то после переключения в 1 1-го триггера, заряжается (1+1)-я управляющая шина (диаграмма п), генерируется ток а в (1+ 1)-ю токовую шину (диаграмма з) и ток в в i-ю (диаграмма м), одновременно, начиная с момента переключения 1-го триггера в Г, происходит разряд 1-й управляющей шины, и поэтому окончание импульса в 1-й управляющей и токовой шине совпадает с началом импульса b (1+1)тй управляющей и токовой шине, т.е. импульсы в смежных разрядах управляющего регистра уплотнены (диаграммы л, м, п, р). Перекрытие импульсов в смежных разрядах управляющего регистра привело бы к сбоям, а паузы между импульсами - к понижению быстродействия.

Предположим, что (+2}-й триггер был первым в цепочке триггеров, установленных в 1, т.е. граничным. После переключения в 1 (-И)-го триггера повышение потенциала (+2)-й управляющей шины не происходит (диаграмма т), (1+1)-й триггер остается в Г и становится граничным в цепочке триггеров, установленных в 1.

Диаграммы, фиг.З л-т отражают работу управляющего регистра после двух обращений на запись, вслед за первым в 1-й управляющей шине формируется второй импульс (диаграмма л), одновременно генерируется ток 1ь в i-ю токовую шину и ток ь в (И}-ю (диаграммы м, н), однако в (1+1)-й управляющей и токовой шине второй импульс не формируется (диаграммы п, р), i-триггер после переключения в 1 остается в таком состоянии, и теперь уже он становится граничным.

Таким образом, при записи маркерные 1 продвигаются по УР, и соответственно

по управляющим шинам числовых линеек пробегают слева направо уплотненные импульсы напряжения, а по токовым шинам пробегают уплотненные импульсы тока: 1ь - в принимающих числовых линейках, 1ь - в передающих. Этими импульсами информационные слова продвигаются по числовым линейкам буферного ЗУ. Продвижение каждой маркерной Г прекращается установлением в 1 последнего в цепочке триггеров, установленных до этого в О, а информационное слово при этом перезаписывается в последнюю незанятую числовую линейку.

При считывании коротким импульсом по входу Считывание (диаграмма е) переключается в О 1-й триггер управляющего регистра. Если (-1}-й триггер установлен в 1, то потенциал 1-й управляющей шины повышается (диаграмма ж), усилитель 1-го разряда генерирует ток 1ь в (1-1}-ю токовую шину, происходит перезапись слова из (1-1)- й числовой линейки в l-ю. Далее с задержкой гз на выходе элемента 7 1-го разряда формируется отрицательный импульс (диаграмма з), которым переключается в О (1-1)-й триггер, а 1-й возвращается в 1. Если (-2)-й триггер в 1 то далее аналогичный процесс переключений замкнутой цепочки элементов происходит s (1-1)-м разряде управляю- щего регистра и заканчивается он переключением в О (l-2)-to триггера и возвращением а 1 (-1)-го и т.д.

Временные диаграммы фиг.З е-к иллюстрируют три обращения на считывание, После двух из них на выходе 22 имеются отрицательные импульсы (диаграмма и) снятия-восстановления готовности считывания, которые могут быть использованы для подтверждения действительного считыва- ния. Третий импульс Считывание поступает, когда вся информация мз ЗУ считана. В этом случае 1-й триггер управляющего регистра переключается в О, готовность считывания снимается, но не восстанавливается, информация в выходной числовой линейке не изменяется (диаграмма к).

Длительность импульса Считывание должна быть достаточной для переключения триггера (ограничение снизу), но не дол- жна превосходить tu, чтобы избежать одновременного воздействия установочных сигналов по R- и S-входам 1-го триггера.

Таким образом, при считывании по управляющему регистру продвигается мар- керный О, продвижение его заканчивается установлением в О последнего в цепочке триггеров, установленных до этого в 1. За такой цикл весь массив хранимых в буферном ЗУ данных сдвигается на одну числовую линейку к выходу.

Как и при записи возможно многократное считывание с периодом обращения не менее 2 tu. Возможно совмещение асинхронной записи и считывания, происходящих с различной частотой, при этом маркерные Г и О, продвигаются по управляющему регистру навстречу, прерывание их происходит в граничном разряде управляющего регистра без конфликтных ситуаций.

Управляющий регистр буферного ЗУ не имеет цепи начальной установки. При включении питания триггеры управляющего регистра устанавливаются в произвольное состояние, однако затем происходит упорядочение, правая часть управляющего регистра заполняется 1, левая О. Для подготовки буферного ЗУ к работе необходимо очистить (обнулить) УР подачей серии импульсов Считывание.

Рассмотрим переходной процесс переключения (i+1)-ro элемента памяти (фиг.2). Положим транзисторы 24.26 в нем открыты, а 23, 25 закрыты, а в 1-м элементе памяти наоборот. Импульс запирающего напряжения в (+1)-й управляющей шине приложен к емкостной нагрузке, фиг.4, где Скэхр - емкость коллектор - хранящий эмиттер транзистора 24, Сбэу - емкость база - управляющий эмиттер транзистора 23. Напряжение, передаваемое в базу транзисторы 23, определяется емкостным делителем и равно

U6 UtCioxp /(Скэхр + Сбэу),

где Ut - мгновенное значение напряжения в управляющей шине.

При одинаковых площадях эмиттеров в транзисторе 23 (24) Скэхр «« Сбэу, в этом случае примерно половина напряжения Ut передается в базу транзистора 23, заряжая ее током, протекающим через открытый транзистор 23 1-го ЭП. Когда Ue на 0,7-0,8 В превышает потенциал 1-й управляющей шины, тиристор включается.

Для ускорения включения тиристора и быстрого разряда базы транзистора 24(i+1}- й тиристорный элемент памяти запитывает- ся повышенным током, вытекающим из элемента через управляющий эмиттер транзистора 23 и далее в коллектор транзистора 23 1-го ЭП и i-ю управляющую шину.

Упрощение буферного ЗУ достигается использованием более простых элементов памяти, схемой организации их в одноступенчатые накопительные регистры с особой организацией перезаписи (сдвига) информации в смежных числовых линейках. Поразрядное формирование уплотненных во времени импульсов напряжения и тока осуществляется за счет особой структуры управляющего регистра.

Формулаизобретения

1. Буферное запоминающее устройство, содержащее матрицу элементов памяти, причем каждый элемент памяти состоит из двух совмещенных п-р-п-р-транзисторных структур с перекрестными связями коллеж- тор - база, группу входных формирователей, выходы каждого из которых соединены с первыми эмиттерами п-р-п-транзисторов первых элементов памяти соответствующих строк матрицы, а входы являются информа- ционными входами устройства, группу выходных формирователей, входы каждого из которых соединены с коллекторами транзисторных структур последних элементов памяти соответствующих строк матрицы, а выходы являются информационными выходами устройства, первый и второй входные формирователи, входы которых являются соответственно входами записи и считывания устройства, первый, второй и третий выходные формирователи, выходы которых являются соответственно выходами наращивания памяти, готовности записи и готовности считывания устройства, управляющий регистр, каждый разряд которого со- стоит из RS-триггера, причем инверсный выход RS-триггера каждого разряда соединен с входами усилителя и элемента задержки, первый выход которого соединен с S-входом данного триггера, прямой выход и R-вход RS-триггера каждого разряда, кроме последнего, соединены соответственно с входом и вторым выходом элемента задержки последующего разряда, второй выход элемента задержки первого разряда соеди- нен с входом первого выходного формирователя, а вход усилителя первого разряда - с входом второго выходного формирователя и с выходом первого входного формирова

геля, прямой выход и R-вход триггера последнего разряда соединены соответственно с входом третьего выходного формирователя и с выходом второго входного формирователя, отличающееся тем, что, с целью упрощения устройства, оно содержит группу элементов нагрузки, первые выводы которых соединены с шиной напряжения питания, а вторые - с эмиттерами соответствующих p-n-p-транзисторов последних элементов памяти каждой строки матрицы, а в каждом разряде управляющего регистра - элемент нагрузки, первый вывод которого соединен с входом усилителя ного разряда, и в каждом разряде, кроме последнего, источник тока хранения, первый вывод которого соединен с первым выходом усилителя данного разряда и вторым выходом усилителя.последующего разряда, вторые эмиттеры n-p-n-транзистспов элементов памяти каждого столбца матрицы соединены с входом усилителя соответствующего разряда управляющего регистра, эмиттеры p-n-p-транзисторов элементов памяти каждого столбца матрицы, кроме последнего, соединены с первым выходом усилителя соответствующего разряда управляющего регистра, в каждой строке матрицы n-е коллекторы транзисторных структур каждого элемента памяти, кроме последнего, соединены с первыми эмиттерами соответствующих п-р-п-транзисторов последующего элемента памяти.

2. Устройство поп.1,отличающее- с я тем, что каждый RS-триггер состоит из двух совмещенных транзисторных структур тиристорного типа с диодами Шоттки в перекрестных связях коллектор- база, причем коллекторы транзисторных структур являются R- и S-входами триггера, эмиттеры соответствующих p-n-p-транзисторов - прямым и инверсным выходами триггера, а эмиттеры n-p-n-транзисторов соединены с шиной нулевого потенциала устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющий регистр для буферного запоминающего устройства | 1987 |

|

SU1499405A1 |

| Регистр сдвига для буферного запоминающего устройства | 1985 |

|

SU1432609A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Управляющий регистр для буферного запоминающего устройства | 1984 |

|

SU1231536A1 |

| Устройство для считывания информации из блоков памяти | 1978 |

|

SU746719A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Регистр для буферного запоминающего устройства | 1984 |

|

SU1170511A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ). Данное буферное ЗУ последовательного типа, асинхронное, двухпортовое (FIFO-memory devise) рассчитано на реализацию в виде БИС ЗУ на совмещенных n-p-n-p-транзисторных структурах тиристорного типа. Элементы памяти состоят из двух таких структур, из них составлены одноступенчатые сдвиговые регистры накопителя, Раздельное управление сдвигами осуществляется по токовым и управляющим шинам, причем повышенный ток выборки при сдвиге генерируется и в принимающую, и в передающую числовые линейки, а импульс запирающего напряжения формируется в управляющей шине принимающей числовой линейки. Формирование управляющих импульсов напряжения и тока осуществляет управляющий регистр, содержащий RS-триггер на тиристорах и внутреннюю асинхронную времяформирующую цепочку, управляющие импульсы уплотнены: окончание импульса в f-й числовой линейке совпадает с началом импульса в i+1-й числовой линейке. Буферное ЗУ как по накопителю, так и по обрамлению выгодно отличается простотой. 1 з.п.ф-лы, 4 ил. (Л

И

nL±U

1ДПШ

.§

в |СЧ|

J :

HSh1

to

I

rthS

гм

«о ,

ю

Р I «Ј 4, 5Са

i-йэп -

.л.

L+1-иЭЛ .

Фиг.Z

ft «UKVW.T

I -

&

1 VmagayУ.11,11Ц|ии«таю вдшм

д

.in

™%ам-ЈЩй/%вхпаоаш «.

фуг. 4

| Буферное запоминающее устройство | 1980 |

|

SU974411A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Управляющий регистр для буферного запоминающего устройства | 1987 |

|

SU1499405A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-11-07—Публикация

1988-10-10—Подача