1

Изобретение относится к автоматике и вычислительной технике.

Известно адаптивное вычислительное устройство, содержащее многофункциональные блоки, дешифраторы, схемы совпадения и логические элементы ll.

Однако это устройство не всегда обеспечивает требуемый уровень надежности.

Наиболее близким техническим решением к предлагаемому устройству является адаптивное вычислительное устройство, содержащее многофункциональные блоки с кодовой настройкой функций, регистры сдвига, элементы неравнозначности, элементы И и ИЛИ И,

Однако это устройство не всегда удовлетворяет предъявляемым к нему требованиям производительности вследствие значительных затрат времени на настройку и перенастройку устройства после обнаружения отказа, так как перенастройка в нем организуется методо « последова- тельного поиска настройки, обеспечивак щей работоспособность устройства В известном устройстве отсутствует выдача правильного результата вычислений при наличии отказа, из-за чего требуется повторение вычислений после перенастройЕЯ.

Цель изобретения - повышение провэводктельности устройства,

Поставленкая цель достигается тем, что устройство содержит восстанавливающий оргйн, блок памяти, блоков приоритета, причем выход j -го многофункционального блока связан с j -ым вкодом

10 коммутатора k-ый выход первой группы выходов каждого i го блока приоритета свазан с первьпи входом ( iu )ого элемента И ис ( )-ым входом комму 15татора, где j - 1, 2, ,.. п , i 1, 2, ,. 5 г 1.- i,i j---1H biS выход коммутатора соедннен с i -ым входом восстанавлйваюшего органа и с первым входом i -го элемента неравноэначноста, выход

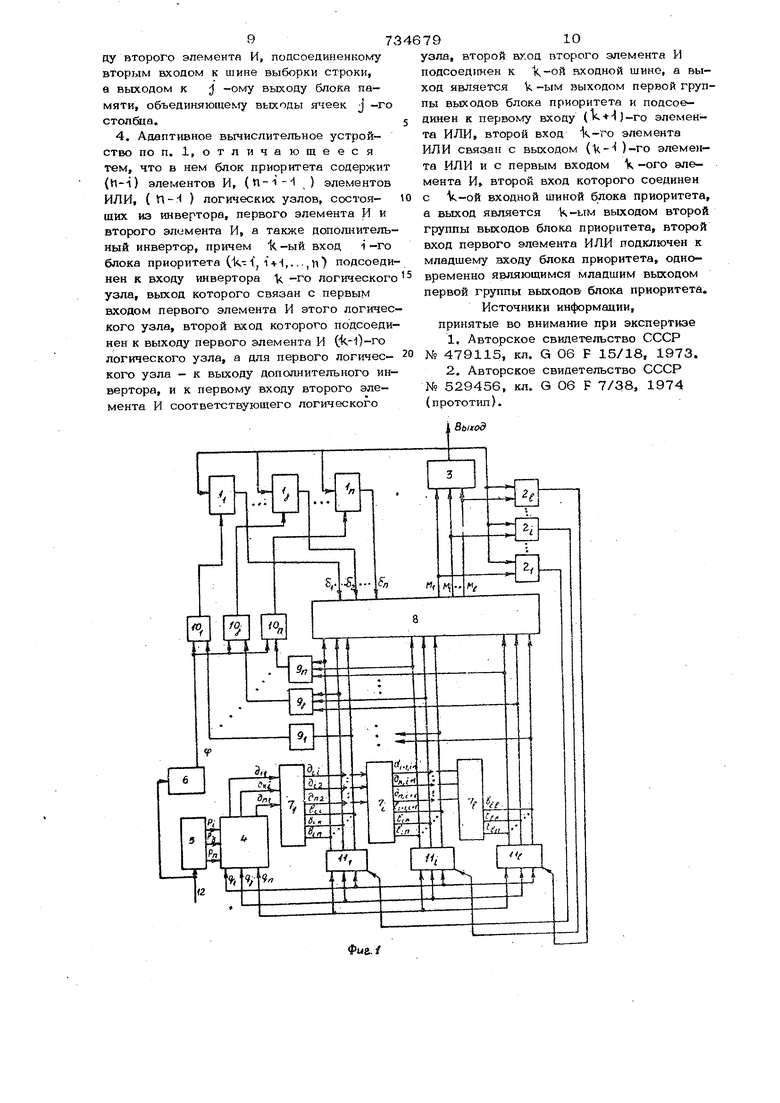

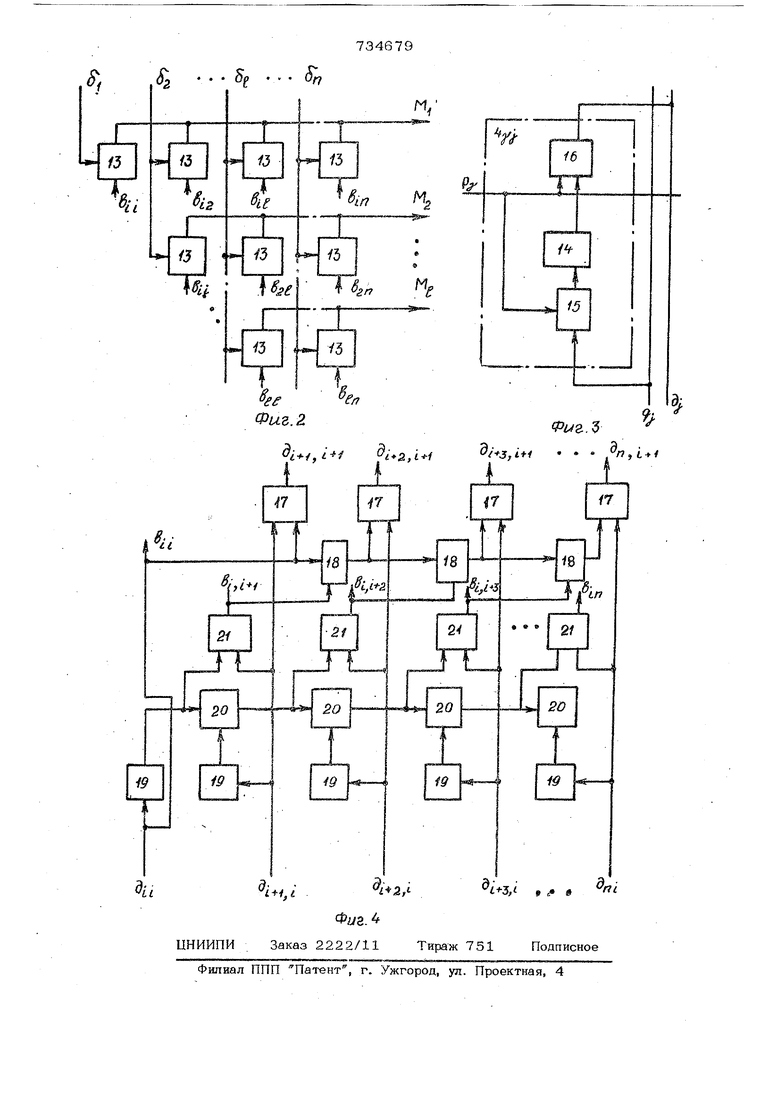

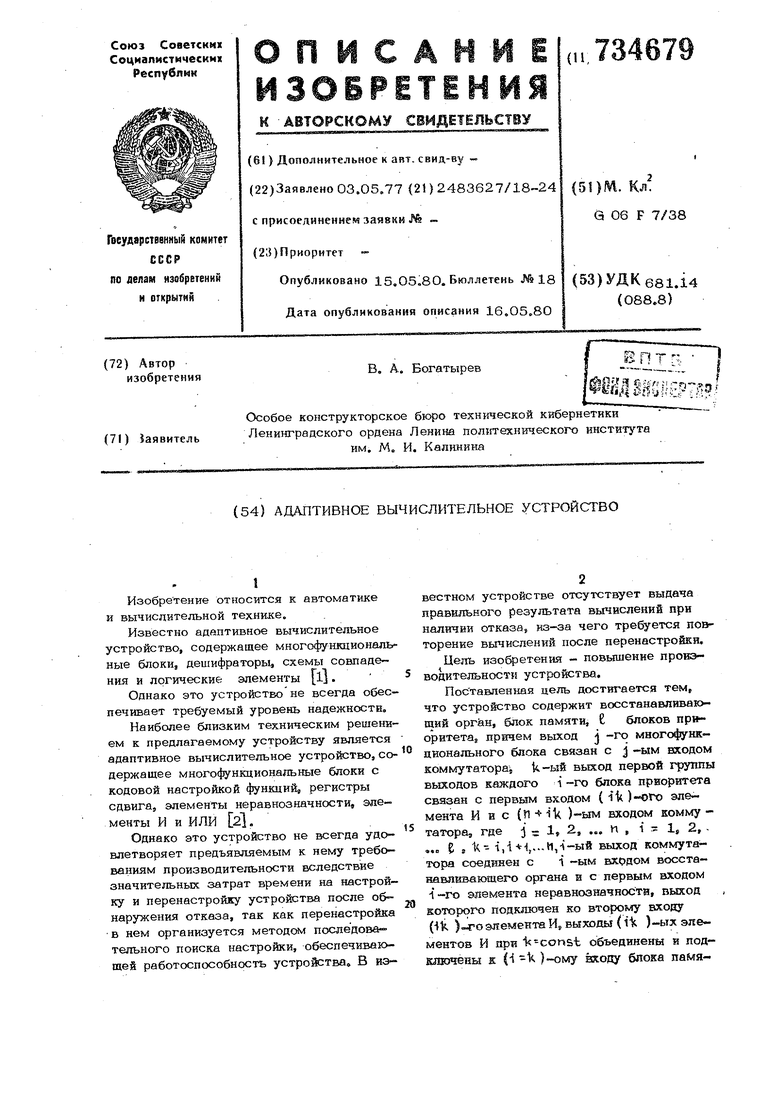

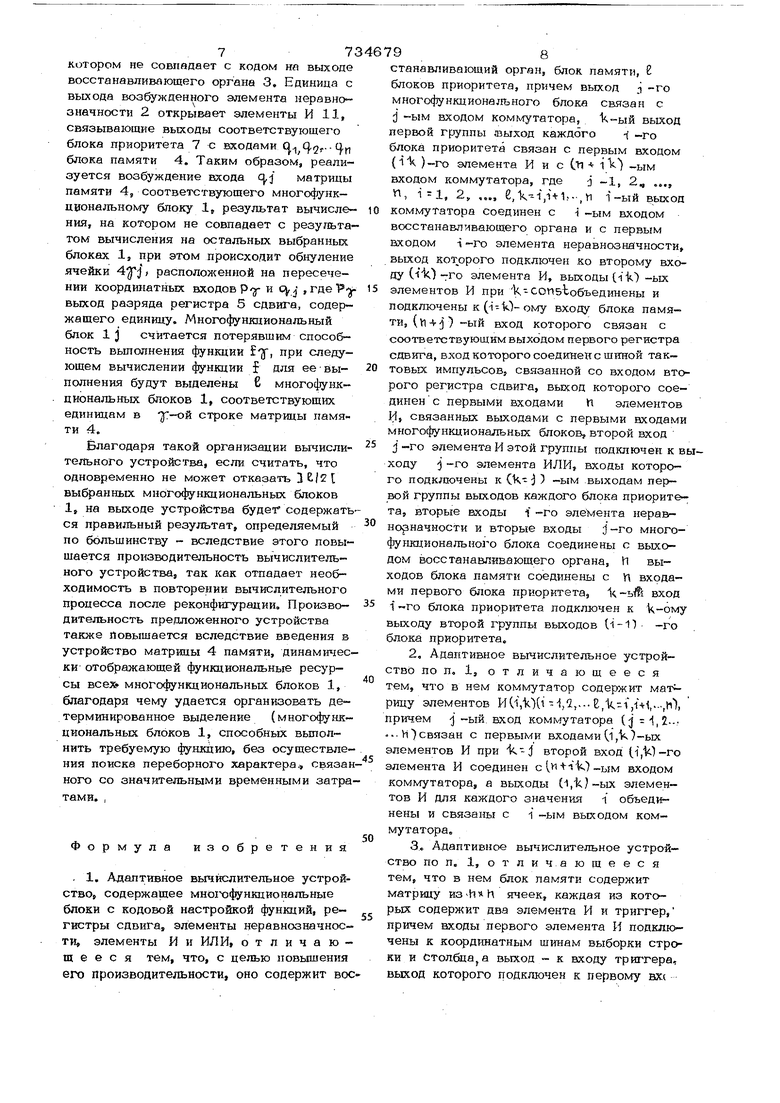

20 которого подключен ко второму входу OK )го элемента И, выходы (ilt )-ых элементов И при 1«-const объединены и подключены S (i -1 )-ому Ёосоду блока памяответствующим выходом первого регистра .сдвига, вход KOTQporo соединен с шиной тактовых импульсов, связанной со входом второго регистра сдвига, выход которого соединен с первыми входами И элементов И, связанных выходами с первыми входами многофункциональных блоко второй вход j-ro элемента И этой группы, подключен к выходу }-го элемента ИЛИ, входы которого подключены к (1 - j )-ым выходам первой группы выходов каждого блока приоритета, вторые входы -i-ro элемента неравнозначности и вторые входы j-го многофункциональнего блока соединены с вь1ходом восста- навливающего органа, Ч выходов блока памяти соединены с И входами первого блока приоритета, k -ый вход i -го блока приоритета подключен к k-ому. выходо второй группы выходов ( i -1) -го блока приоритета (kii l-Vl,..., n)В предлагаемом устройстве коммутатор содержит матрицу элементов И ( 1, k) ( i -1, 2, 3 .... Е ; ,,.-, П), при чем j -ый вход коммутатора ( -) 1, 2, ..., П ) связан с первыми входами { i , 1)-ых элементов И при К j второй вход ( 1 г 1 ) -го элемента И соединен с ( h + + (1)-ым входом коммутатора, а выходы (lk)-bix элементов И для каждого значения i объединены и связаны с i -ым выходом коммутатора. Блок памяти предлагаемого устройства содержит матрицу ячеек, каждая из которых содержит два элемента И и триггер, причем входы первого элемента И подключены к координатным шинам выборки строки и столбца а выход к входу триггера, выход к,ото-: рого подключен к первому входу второго элемента И, подсоединенному вторым входом к шине выборки строки, а выходом к Янэму выходу блока памяти, объединяюще му выходы 51Чеек j-го столбца/ Блок приоритета содержит ( И -1 ) Элементов И, (п-1-1) элементов ИЛИ, (ti-i) логичес ких узлов, состояшж . из инвертора, первого элемента И и второго элемента И, а также дополнительный инвертор, причем К-ый вход i-ro блока приоритета tX-ijlHy-.H) подсоединен к входу инвертора логического узла, выход котороро связан с первым входом первого элемента И этого логического узла, второй вход которого подсоединен к выходу первого элемента И (4-1 -го логического узла, а для первого логического узла - к вы- BONjy входу второго элемента И соотве- ствующего логического узла, второй вход второго элемента И подсоединен к Ч -ой входной шине, а выход является k -ым вьгходом первой группы выходов блока приоритета и подсоединен к первому входу (I. )-го элемента ИЛИ, второй вход V-oro элемента ИЛИ связан с выходом (k - )-го элемента ИЛИ и с первым входрм k -ого элемента И, второй вход ко- торогчэ соединен с k-ой входной шиной блока приоритета, а выход является -ым выходом второй группы выходов блока приоритета, второй вход первого элемента ИЛИ подключен к младшему входу блока приоритета, одновременно являющимся младшим выходом первой группы выходов блока приоритета. На фиг. 1 представлена блок-схема . предложенного адаптивного вычислительного устройства, на фиг, 2 - схема коммутатора; на фиг. 3 - ячейка блока памяти на фиг. 4 - схема блока приоритета Предложенное устройство содержит многофункциональные блоки 1, элементы 2 неравнозначности, восстанавливакиций орган 3, блок 4 памяти, регистры 5, 6 сдвига, блоки 7 приоритета, коммутатор 8, элементы ИЛИ 9, элементы И 1О, 11. Восстанавливающий орган 3 имеет нечетное число входов, причем если это число &, TD в устройстве имеется & элементов 2 неравнозначности, 6 блоков 7 приоритета, элементов 11 ii; ( i .It 2, .,., t,k-1,i-Vi,..,tt ). Если в устройстве содержится tt функциональных блоков, то размерность матрицы памяти 4 будетП И, в устройстве содержится П элементов ИЛИ 9 и И 10. Регистр 5 содержит И. разрядов, а регистр 6 - П групп разрядов по разрядов в каждой, причем сдвиг в нем осуществляется на IBogf nt разрядов сразу. Выходы 9, Sj,.--, 9у матрицы памяти 4 подключены к входам первого блока приоритета 7. Входы блока приоритета 7 подключены к выходам 9i, Э|,...9„ I-- -го блока приоритета 7. Выходы 131 блоков приоритета подключены к входам коммутатора 8, связывающему выходы многофункциональных блоков 1 с входами 1А,,}Л2,-,,восстанавливающего органа 3. Входы восстанавливак ® ° органа 3NA, 2,...,Лe связаны также с входами элементов неравнозначности 2, другие входы которых соединены с выхо- 57 дом восстанавливаютего оргона 3 связанным с входами многоф -нкционапьных блоков 1. Выходы элементов неравнозначности 2 подсоединены к втормм входам соответствующих элементов И llj связывающим выходы блоков приоритета 7 с соответствующими входами матрицы памяти 4 i,Z,( Р этом к входу матрицы памяти подключены выходы элементов И lllV при Вход тактовых импульсоп 12 подключен к регистрам сдвига 5, 6. Выходы Р, Р2,.--ри---Pvi ра 5 подсоединены к матрице памяти 4, Выходы последней группы разрядов F ре- гистра сдвига 6 через элементы И Ю, связанных посредством элементов ИЛИ 9 с выходами t)i1. блоков приоритета 7i, подключены к входам кодовой настройки многофункциональных блоков 1 При этом входы элемента ИЛИ 9J подключены к выходам элементов И 11 ik при ks. Коммутатор 8 содержит матрицу элемен- тов И ISik, причем вход комму- татора 8 связан с первыми входами элементов И 13 ik при Вторые входы элементов И 13 ik соединены с соотвегствующими t)iV. входами коммутатора 8. Выходы lie -ьк элементов И 13 для каждого значения л объединены и овя- заны с выходом 1.1 коммутатора 8. Ячейка памяти 4 содержит триггер 14 и элементы И 15, 16. Причем входы элемента И 15 подключены к координатным щинам выборки строки Ру и столбца , а выход - к входу триггера 14, выход которого подключен к первому входу второго элемента И 16 подсоединенному вто рым входом к шине выборки строки рЗР, а выходом - к выходу блока 4 памяти 3i объединяющему выходы ячеек -го столбца. Блок приоритета- Tl содержит (vi-i ) элементов И I7(.h-i-1) элементов ИЛИ 18,См-1) логических узлов, состоящих из инвертора 19, элемента И 2О 21, а также дополнительный инвертор 19. Причем вход 9lti((,,.--,i) подсоединен к входу инвертора 191, выход которого связан с первым входом элемента И 20ik второй вход которого подсоединен к выходу элемента И SOk-- и к первому входу элемента И 21, второй вход элемента И 21V связан с входом i-ro блока 7 приоритета, а выход является ii блока 7 приоритета и подсоединен к первому входу элемента ИЛИ ISk+i Второй вход элемента ИЛИ связан с выходом элемента ИЛИ 18Kи с первым входом элемента И 17k втоG796рой вход которого соедшген с вхоциой шиной Skf, а выход - с выходной шиной 0,ki-« Второй вход первого элемента ИЛИ 18142 подключен к входу 3li блока приоритета 7, связанного с его вьгхо- дом bii. Работа устройства заключается в сдецуюшем, В регистр сдвига 6 заносятся коды настроек на функции l,2.-, )д составля ювдих функцию ,---, возложенную на устройство. В регистр 5 сдвига заносится одна единица. В ячейку 4 -yj блока 4 памяти заносится информация о способности j-го многофункционального блока 1 вьшолнить функцию 53, при этом , если блок 1; способен реализовать функцию д, в противном случае 45j O. Последовательность выполнения функций задается посредством регистров 5, 6 сдвига, причем переход к выпопне- нию следующей ло порядку функции орга- низуется путем сдвига единицы в регистре 5 и кодов настройки в регистре 6. На выход блока и памяти 4 поступает содержимое строки, соответствующей месту нахождения единицы в регистре 5 сдвига, на выходах ,c..,b первого блока 7 приоритета вьщается первая из этой стро- кн единица, на выходах Ьг,,Ь-,. ° рого блока 7 приоритета выделяется вторая единица, и т.д. Посредством коммутатора 8 выход многофункционального блока 1, соответствующей первой единице на выходах блока памяти 4, подключается к к первому вкоду восстанавливающего органа 3, выход многофункционального блока 1, соответствующего второй единице под ключается ко второму входу восстанавливающего органа 3, и т.д. Одновременно, посредством элементов И 1О осуществляется подача кода настройки с выхода F последней группы разрядов регистр 6 сдвига на входы настройки и многофункциональных блоков 1, определяемых единицами на выходах схем приоритета 7bUj Ha выходе воостанавливеющего органа 3 образуется результат вычисленияс определяемый большинством по результатам вычислений в многофункциональных блоках 1, Соответствующих единицам на выходах блоков 7 приоритета. Результат с выхода восстанавливающего органа 3 подается на входы многофункциональных блоков, для дальнейшего вычисления функции f , 2--1 п}- элементах неравнозначности 2 производится выделение входа восстанавливающего органа 3, код на котором не совпадает с кодом на выходе восстанавливающего органа 3, Единица с выхода возбужденного элемента неравнозначности 2 открывает элементы И 11, связывающие выходы соответствующего блока приоритета 7 с входами ,Cj,2,.-Cj,fi блока памяти 4. Таким образом, реализуется возбуждение входа матрицы памяти 4, соответствующего много4ункциональному блоку 1, результат вычисления, на котором не совпадает с резупьта™ том вычисления на остальных выбранных блоках 1, при этом происходит обнуление ячейки расположенной на пересечении координатных входов Pj- и cj,j ,гдеР выход разряда регистра 5 сдвига, содержащего единицу. Многофункциональный блок 1J считается потерявшим способность выполнения функции fJTt следующем вычислении функции f для ее-выполнения будут выделены € многофункциональных блоков 1, соответствующих единицам в f-o& строке матрицы памяти 4. Благодаря такой организации вычислительного устройства, если считать, что одновременно не может отказать ЗЬ|2 выбранных многофункциональных блоков 1, на выходе устройства будет содержать ся правильный результат, определяемый по большинству - вследствие этого повышается производительность вычислительного устройства, так как отпадает необходимость в повторении вычислительного процесса после реконфигурации. Производительность предложенного устройства также Повышается вследствие введения в устройство матршхы 4 памяти, динам1гаес ки отображающей функциональные ресурсы все многофункциональных блоков 1, благодаря чему удается организовать детерминированное выделение (многофункциональных блоков 1, способных вьшол- нить требуемую функцию, без осуществления поиска переборного характера связан ного со значительными временными затра тами. , Формула изобретения . 1. Адаптивное вычислительное устройство, содержаВ1ее мнО1Х)функционаяьные блоки с кодовой настройкой функций, ре гистры сдвига, элементы неравнозначности, элементы И и ИЛИ, отличающееся тем, что, с целью повышения его производительности, оно содержит во станавливающий орган, блок памяти, блоков приоритета, причем выход j -го многофункционального блока связан с j -ым входом KOMfvryTaTopa, . k-ый выход первой группы языход каждого i -го блока приоритета связан с первым входом (i-k )го элемента И и с (п - ) -ым входом коммутатора, где j -1, 2, ..., , , 2 2,k--i,i4l..,n i-ый вькод коммутатора соединен с -i -ым входом восстанавливающего органа и с первым аходом i -го элемента неравнозначности, выход которого подключен ко второму входу Clk) гго элемента И, выходы (i и) -ых элементов И при К-соп&Ьобъединены и подключены к (i-Ю-ому входу блока памяти, (VI4 j ) -ый вход которого связан с соответствующим выходом первого регистра сдвига, вход которого соединен с шиной тактовых импульсов, связанной со входом второго регистра сдвига, выход которого соединен с первыми входами U элементов И, связанных вь5Ходами с первыми входами многофункциональных блоков, второй вход j -го элемента И этой группы подключен к выходу j-го элемента ИЛИ, входы которого подк/почены к (К- j ) -ым выходам первой группы выходов каждого блока приоритета, вторые входы 1 -го элемента неравнорначности и вторые входы j-ro много4)упкционального блока соединены с выходом восстанавливающего органа, И выходов блока памяти соединены с П входами первого блока приоритета, вход i ГО блока приоритета подключен к k-ому выходу второй группы выходов (i-n -го блока приоритета. 2,Адаптивное вычислительное устройство по п, 1, отличающееся тем, что в нем коммутатор содержит мат рицу элементов И(1,1.)(,--. E,k-i,i4l,...,i), причем j -ый. вход коммутатора ( - (,2... ..И) связан с первыми входами (,1 , Vbix элементов И при j второй вход (i,W-ro элемента И соединен с l.Mt-sk) ым входом коммутатора, а выходы (i,k)-bix элементов И для каждого значения i объединены и связаны с 1 -ым выходом коммутатора,, 3.Адаптивное вычислительное устройство по п. 1, о т л и ч а ю щ е е с я тем, что в нем блок памяти содержит матрицу ячеек, каждая из которых содержит два элемента И и триггер, причем входы первого элемента И подключены к коордт шатным шинам выборки строки и СтолбцаJа выход - к входу триггера, выход которого подключен к первому вх( 73 ду второго элемента И, подсоединенко1 лу вторым входом к шине выборки строки, а выходом к j -ому выходу блока памяти, oбъeдиняюlцe fy выходы J -го столбца. 4. Адаптивное вычислительное устройство по п. 1,отличающееся тем, что в нем блок приоритета содержит (tt-i) элементов И, { l-i--1 ) элементов ИЛИ, ( П-И ) логических узлов, состоящих из инвертора, первого элемента И и второго элемента И, а также дополнительный инвертор, причем К -ый вход -i -го блока приоритета (1,-: 1, ,. .. v) подсоединен к входу инвертора -го логического узла, выход которого связан с первым входом первого элемента И этого логического узла, второй вход которого подсоединен к выходу первого элемента И (.k-l)-ro логического узла, а для первого логического узла - к выходу дополнительного ийвертора, и к первому входу второго элемента И соответствующего логического 7910 узла, второй вход второго элемента И подсоед1шен к Х-ой входной шнно, а выход является k -ым выходом первой группы выходов блока приоритета и подсое- динен к первому входу (1 )-го элемента ИЛИ, второй вход элемента ИЛИ связан с выходом (k-i )-го элемента ИЛИ и с первым входом Ч -ого элемента И, второй вход которого соединен с k-ой входной шиной блока приоритета. а выход является К-ым выходом второй группы выходов блока приоритета, второй вход первого элемента ИЛИ подключен к младшему входу блока приоритета, одновременно являющимся младшим выходом первой группы выходов- блока приоритета, Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР 479115, кл. G Об F 15/18, 1973. 2. Авторское свидетельство СССР № 529456, кл. G 06 F 7/38, 1974 (прототип).

5) . 5jp - О/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| Устройство для построения гистограммы | 1988 |

|

SU1688261A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для вычисления булевых производных | 1986 |

|

SU1370651A1 |

| Устройство для упорядочивания @ чисел | 1982 |

|

SU1062687A1 |

| Устройство для автоматического диагностирования группы однотипных логических блоков | 1987 |

|

SU1444778A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

Авторы

Даты

1980-05-15—Публикация

1977-05-03—Подача