f Изобретение относится к вычислительной технике и может быть использовано в системах автоматического контроля интегральных схем, а также блоков и устройств дискретного действия при их производстве и эксплуатации.

По основному авт.св.№ 696464 известна система для контроля электронных устройств,содержащая цифровую вычислительную машину, блок сравнения, сдвиговый регистр, счетчик, тактовый .генератор и распределитель импульсов . Управляющий выход ЦВМ соединен с первым (запуска1адим) входом тактового генератора, первый и второй информационные входы ЦВМ со.адииены соответственно с первыми входами блока сравнения и входами контролируемого устройства..Выход тактового генератора соединен с распределителем импульсов, первый, второй и третий выходы которого соединены соответственно с управляющим входом блока сравнения, с первым и вторым входом сдвигового регистра и с входом счетчика. Информационные выходы счетчика соединены с информационными входами ЦВМ, выход сигнала переполнения счетчика соединен

с вторым запрещающим входом тактового генератора и с входом Останов ЦВМ. Выход контролируемого устройства соединен с вторым входом блока сравнения, выход которого соединен с третьим входом сдвигового регистра. Выход сдвигового регистра соединен с входом Прерывание ЦВМ С1.

Недостатком известной системы

10 контроляявляется ее низкое быстродействие за счет того, что на каждом шаге тестовой последовательности происходит полный цикл просмотра содержимого блока сравнения. Дейст15вительно, в известной системе результат сравнения эталонных сигналов и сигналов контролируемого.устройства, формирующийся в блоке сравнения, передается в сдвиговый регистр и затем

20 производится анализ всех разрядов сдвигового регистра; В то же время на практике в большинстве случаев встречаются две ситуации: либо эталонный код и сигналы контролируемого

25 устройства полностью совпадают, либо имеет место несовпадение в отдельных разрядах. В первой ситуации вообще не имеет смысла анализировать содержимое блока сравнения, а во

30 второй - проверка разрядов сдвигового

регистра должна вестийь начиная с первого разряда только до тех пор, пока не будет обнаружен последний разряд несовпадения. При выполнении указанных условий можно значительно повысить быстродействие системы контроля.

Цель изобретения - повышение быстродействия системы для контроля электронных устройств.

Поставленная цель достигается тем, что в систему контроля эталонных устройств введены фо и-1иров атель сигналов и блок коррекции, содержащий группу триггеров, группу элементов И и дешифратор, выходы которого подключены к первым выходам соответствующих элементов И группы, выходы которых подключены к входам соответствующих триггеров группы, выходы которых подключены к третьему входу блока сравнения, выход которого .соединен с первым входом формирователя сигналов, первый выход которого соединен с вторым входом тактового генератора и входом Останов цифровой вычислительной Машины, второй выход формирователя сигналов соединен с вторым входом сдвигового регистра и входом двойного счетчика, информационныйвыход которого подключен к входу дешифратора блока коррекции, выход сдвигового регистра соединен с вторыми входами элементов И группы блока коррекции, второй вход формирователя сигналов соединен с третьим выходом распределителя импульсов.

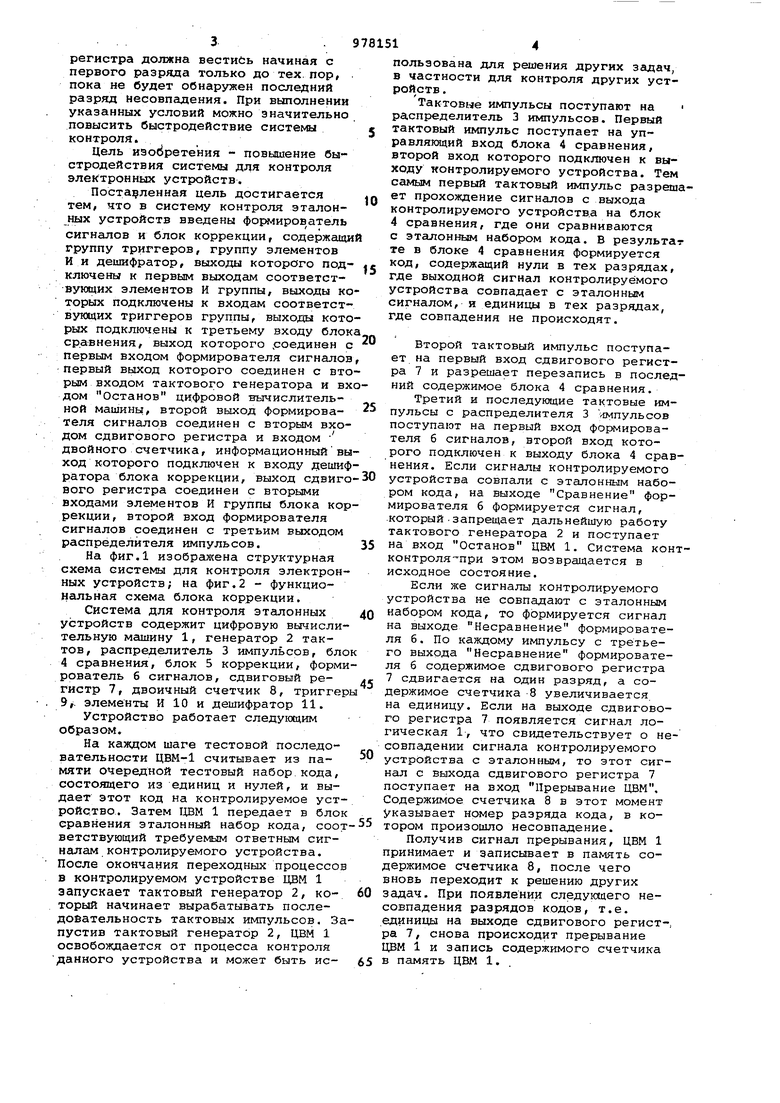

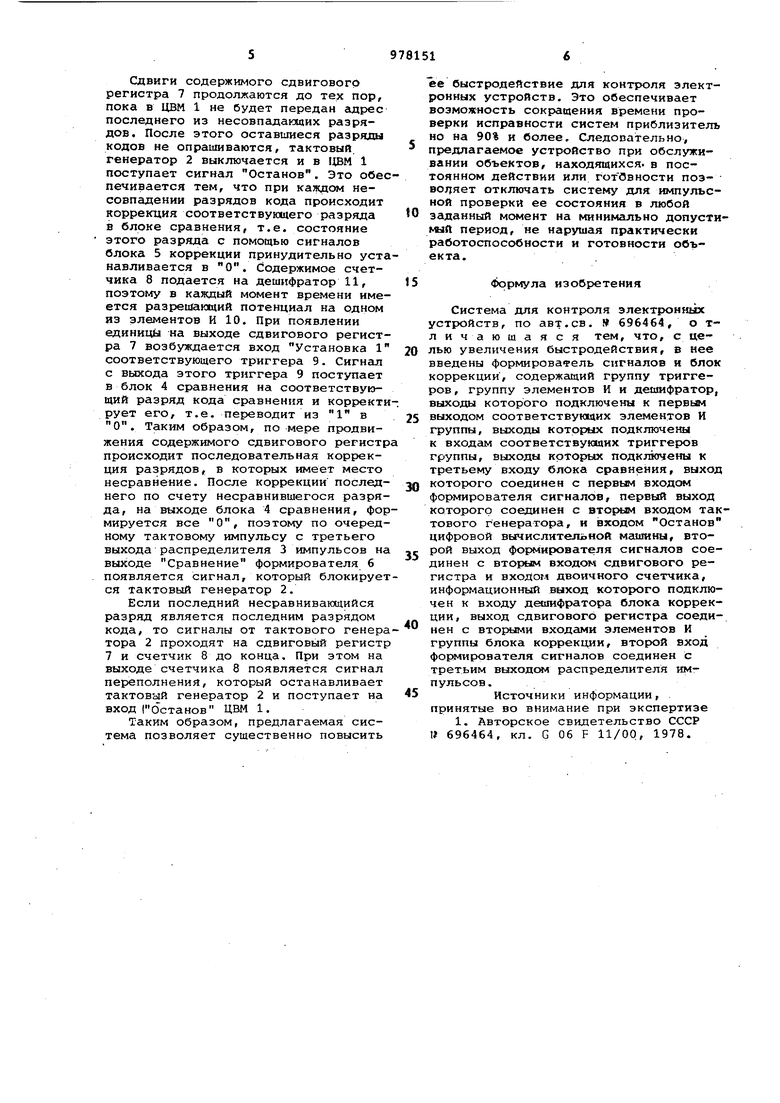

На фиг.1 изобретена структурная схема системы для контроля электронных устройств; на фиг.2 - функциональная схема блока коррекции.

Система для контроля эталонных устройств содержит цифровую вычислительную машину 1, генератор 2 тактов, распределитель 3 импульсов, блок 4 сравнения, блок 5 коррекции, формирователь б сигналов, сдвиговый регистр 7, двоичный счетчик 8, триггеры 9г элементы И 10 и дешифратор И.

Устройство работает следующим образом.

На каждом шаге тестовой последовательности ЦВМ-1 считывает из памяти очередной тестовый набор кода, состоящего из единиц и нулей, и выдает этот код на контролируемое устройство. Затем ЦВМ 1 передает в блок сравнения эталонный набор кода, соответствующий требуемым ответным сигналам контролируемого устройства. После окончания переходных процессов в контролируемом устройстве ЦВМ 1 запускает тактовый генератор 2, который начинает вырабатывать последовательность тактовых импульсов. Запустив тактовый генератор 2, ЦВМ 1 освобождается от процесса контроля данного устройства и может быть использована для решения других задач, в частности для контроля других устройств .

Тактовые импульсы поступают на распределитель 3 импульсов. Первый тактовый импульс поступает на управляющий вход блока 4 сравнения, второй вход которого подключен к выходу контролируемого устройства. Тем самым первый тактовый импульс разрешет прохождение сигналов с выхода контролируемого устройства на блок 4 сравнения, где они сравниваются с эталонным набором кода. В результа те в блоке 4 сравнения формируется код, содержащий нули в тех разрядах, где выходной сигнал контролируемого устройства совпадает с эталонным сигналом, и единицы в тех разрядах, где совпадения не происходят.

Второй тактовый импульс поступает на первый вход сдвигового регистра 7 и разрешает перезапись в последний содержимое блока 4 сравнения.

Третий и последующие тактовые импульсы с распределителя 3 дапульсов поступают на первый вход формирователя 6 сигналов, второй вход которого подключен к выходу блока 4 сравнения. Если сигналы контролируемого устройства совпали с эталонным набором кода, на выходе Сравнение формирователя 6 формируется сигнал, .который-запрещает дальнейшую работу тактового генератора 2 и поступает на вход Останов ЦШ1 1. Система конконтроля- при этом возвращается в исходное состояние.

Если же сигналы контролируемого устройства не совпадают с эталонным набором кода, то формируется сигнал на выходе Несравнение формирователя б. По каждому импульсу с третьего выхода Несравнение формирователя 6 содержимое сдвигового регистра 7 сдвигается на один разряд, а содержимое счетчика -8 увеличивается, на единицу. Если на выходе сдвигового регистра 7 появляется сигнал логическая 1, что свидетельствует о несовпадении сигнала контролируемого устройства с эталонным, то этот сигнал с выхода сдвигового регистра 7 поступает на вход Прерывание ЦВМ. Содержимое счетчика 8 в этот момент указывает номер разряда кода, в котором произошло несовпадение.

Получив сигнал прерывания, ЦВМ 1 принимает и записывает в память содержимое счетчика 8, после чего вновь переходит к решению других задач. При появлении следугацего несовпадения разрядов кодов, т.е. единицы на выходе сдвигового регистра 7, снова происходит прерывание ЦВМ 1 и запись содержимого счетчика в память ЦВМ 1.

Сдвиги содержимого сдвигового регистра 7 продолжаются до тех пор, пока в ЦВМ 1 не будет передан гщрес последнего из несовпадающих разрядов. После этого оставшиеся разряды кодов не опрашиваются, тактовый генератор 2 выключается и в 1ЩМ 1 поступает сигнал Останов. Это обеспечивается тем, что при каждом несовпадении разрядов кода происходит коррекция соответствующего разряда в блоке сравнения, т.е. состояние этого разряда с помощью сигналов блока 5 коррекции принудительно устанавливается в О. Содержимое счетчика 8 подается на дешифратор 11, поэтому в каждый момент времени имеется разрешающий потенциал на одном из элементов И 10. При появлении единицы на выходе сдвигового регистра 7 возбуждается вход Установка 1 соответствующего триггера 9. Сигнал с выхода этого триггера 9 поступает в блок 4 сравнения на соответствующий разряд кода сравнения и корректи рует его, т.е. переводит из 1 в О. Таким образом, по мере продвижения содержимого сдвигового регистр происходит последовательная коррекция разрядов, в которых имеет место несравнение. После коррекции последнего по счету несравнившегося разряда, на выходе блока 4 сравнения, формируется все О, поэтому по очередному тактовому импульсу с третьего выхода распределителя 3 импульсов на выходе Сравнение формирователя 6 появляется сигнал, который блокируется тактовый генератор 2.

Если последний несравнивающийся разряд является последним разрядом кода, то сигналы от тактового генератора 2 проходят на сдвиговый регистр 7 и счетчик 8 до конца. При этом на выходе счетчика 8 появляется сигнал переполнения, который останавливает тактовый генератор 2 и поступает на вход (Останов ЦВМ 1.

Таким образом, предлагаемая система позволяет существенно повысить

ее быстродействие для контроля электронных устройств. Это обеспечивает возможность сокращения времени проверки исправности систем приблизитель но на 90% и более. Следовательно, предлагаемое устройство при обслуживании объектов, находящихся, в постоянном действии или готОвности поэвоцяет отключать систему для импульсной проверки ее состояния в любой заданный момент на минимально допустиi jft период, не нарушая практически работоспособности и готовности объекта.

Формула изобретения

Система для контроля электронных устройств, по авт.св. 696464, о тличающаяся тем, что, с целью увеличения быстродействия, в нее введены формирователь сигналов и блок коррекции, содержащий группу триггеров , группу элементов И и дешифратор, выходы которого подключены к первым выходом соответствующих элементов И группы, выходы которых подключены к входам соответствующих триггеров группы, выходы которых подктаочены к третьему входу блока сравнения, выход которого соединен с первым входом формирователя сигналов, первый выход которого соединен с BTOEXJM входом тактового Генератора, и входом Останов цифровой вычислительной машины, второй выход формирователя сигналов соединен с вторым входом сдвигового регистра и входом двоичного счетчика, информационный выход которого подключен к входу детяифратора блока коррекции, выход сдвигового регистра соединен с вторыми входами элементов И группы блока коррекции, второй вход формирователя сигналов соединен с третьим выходом распределителя импульсов .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 1 696464, кл. G 06 F 11/00, 1978.

Д

--

/ч

-- ш

/г

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для контроля электронных устройств | 1988 |

|

SU1667074A1 |

| Система для контроля электронных устройств | 1977 |

|

SU696464A1 |

| Система для контроля сложных релейных распределителей | 1985 |

|

SU1252780A1 |

| Система для контроля электронных устройств | 1980 |

|

SU1005063A2 |

| СИСТЕМА ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2011 |

|

RU2466448C1 |

| Система для контроля сложных релейных распределителей | 1987 |

|

SU1522209A2 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для контроля электронных устройств | 1984 |

|

SU1231505A1 |

| Запоминающее устройство | 1982 |

|

SU1295447A1 |

Авторы

Даты

1982-11-30—Публикация

1978-09-27—Подача