f

10

15

Изобретение, относится к вычислительной технике и автоматике и может быть использовано в системах автома- ического .контроля интегральных микосхем, а также блоков и устройств искретного действия при их производстве и эксплуатации, Цель изобретения - повьшение быстродействия устройства.

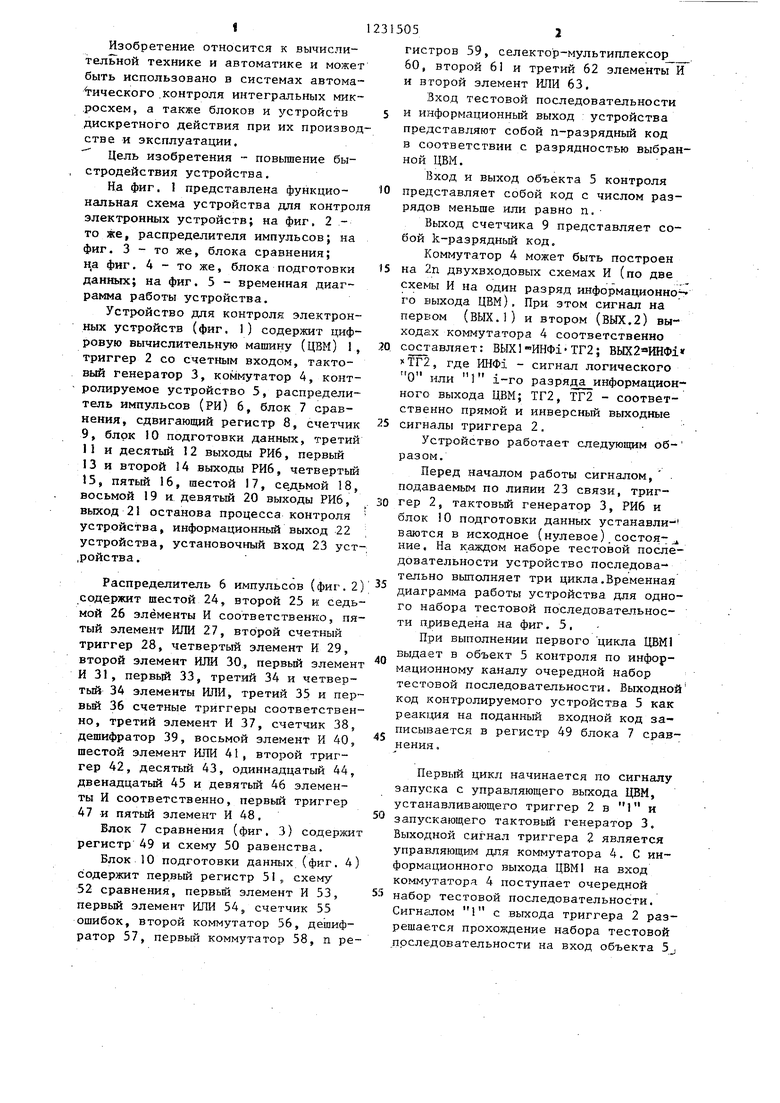

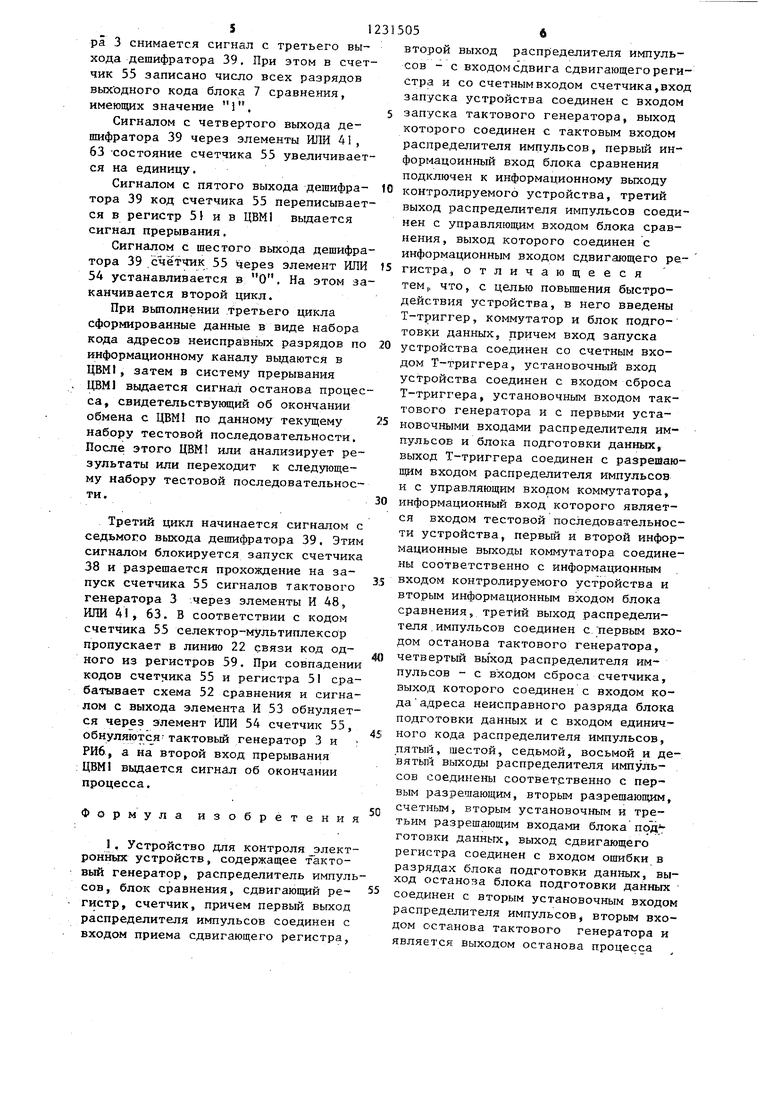

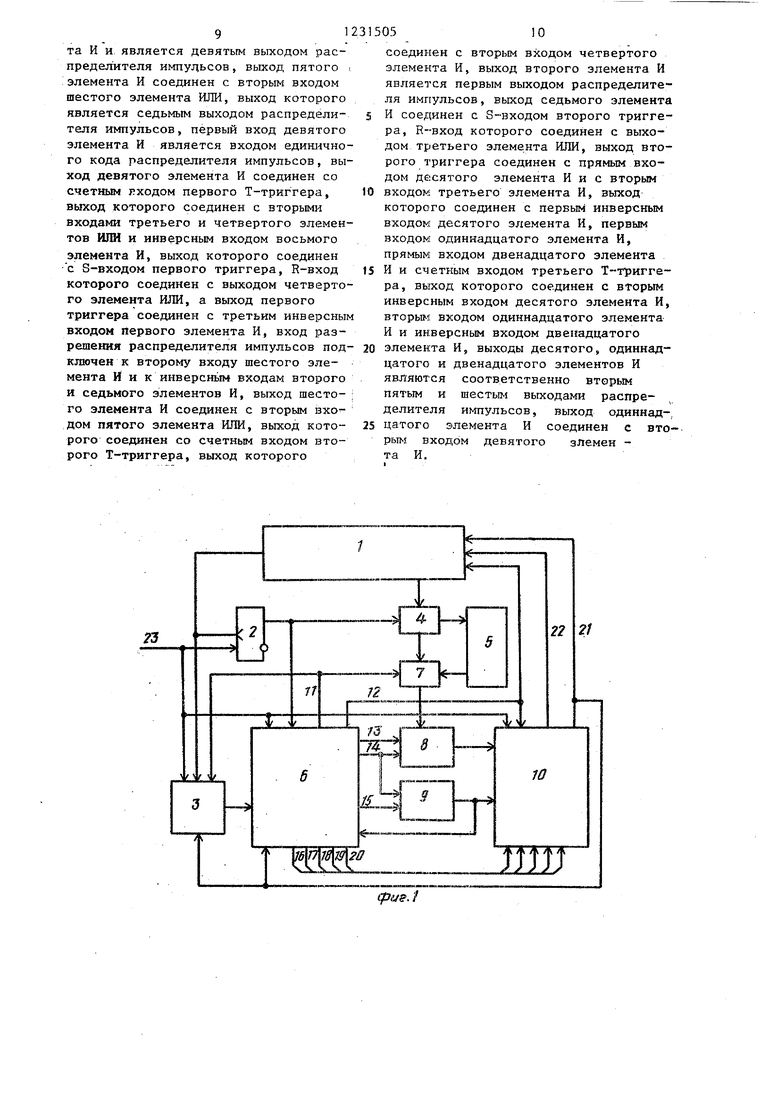

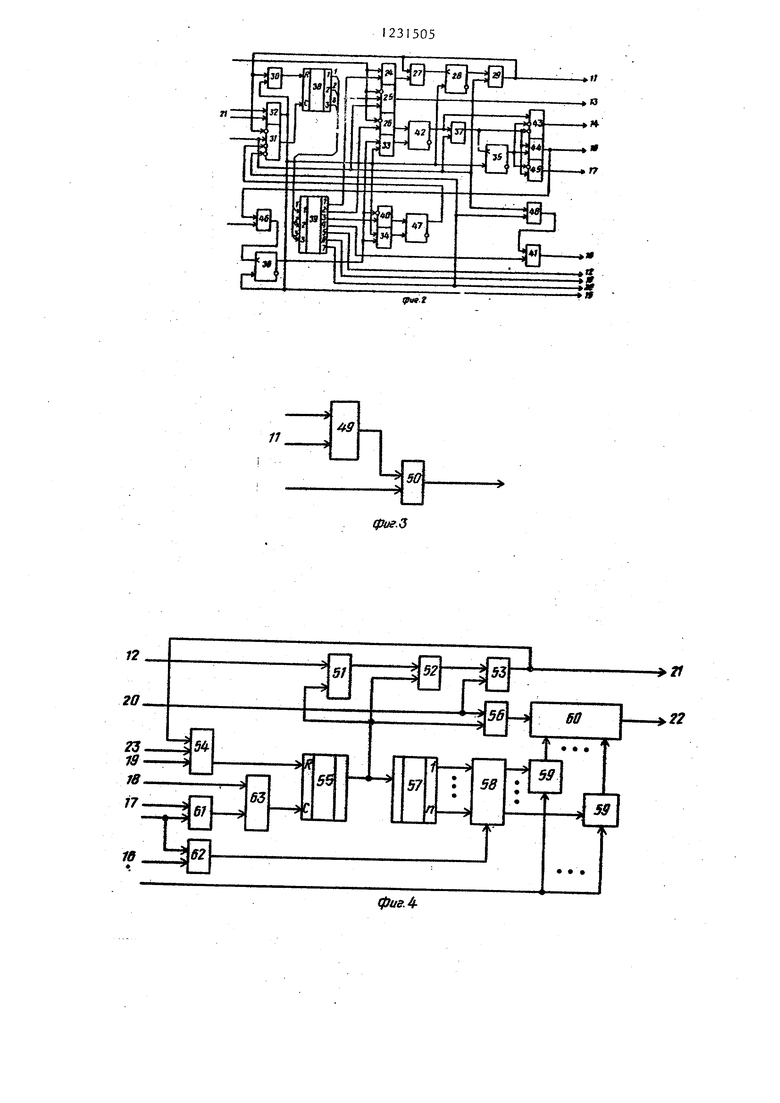

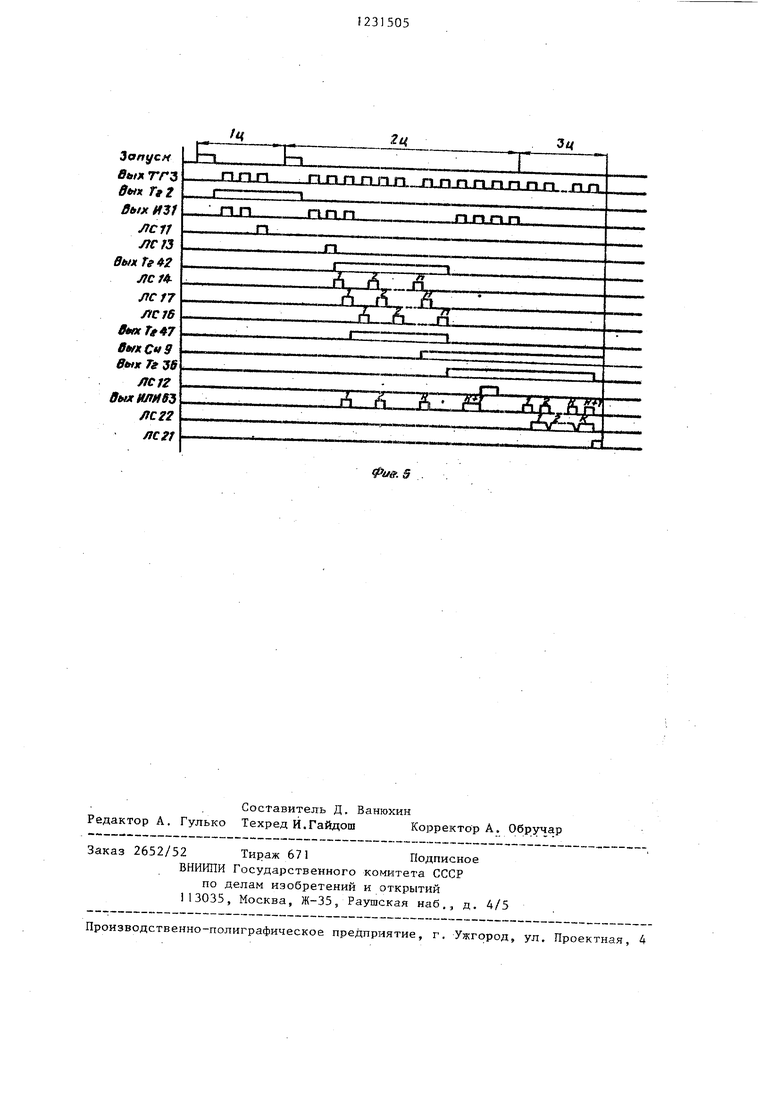

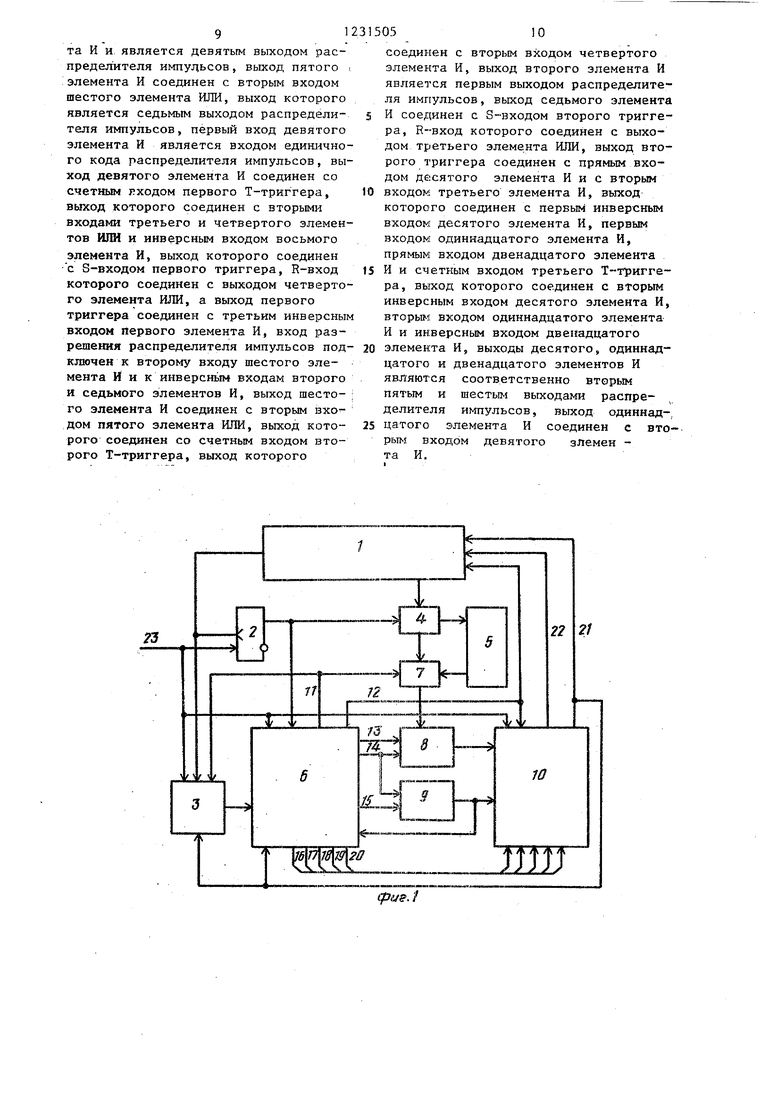

На фиг, 1 представлена функциональная схема устройства для контроля электронных устройств; на фиг, 2 - то же, распределителя импульсов; на фиг. 3 - то же, блока сравнения; н,а фиг, 4 - то же, блока подготовки данных; на фиг, 5 - временная диаграмма работы устройства.

Устройство для контроля электронных устройств (фиг, 1) содержит цифровую вычислительную машину (ЦВМ) 1, триггер 2 со счетным входом, тактовый генератор 3, коммутатор 4, конт- ролируемое устройство 5, распределитель импульсов (РИ) 6, блок 7 сравнения, сдвигающий регистр 8, счетчик 25 9, блок 10 подготовки данных, третий 1 и десятый 12 выходы РИб, первый 13 и второй 14 выходы РИ6, четвертый 15, пятый 16, шестой 17, се,дьмой 18, восьмой 19 и девятый 20 выходы РИб, ЗО выход 21 останова процесса контроля устройства, информационный выход 22 устройства, установочный вход 23 уст-; .ройства.

Распределитель 6 импульсов (фиг. 2) 5 содержит тестой 24, второй 25 и седьмой 26 элементы И соответственно, пятый элемент ИЖ 27, второй счетный триггер 28, четвертый элемент И 29, второй элемент ИЛИ 30, первый элемент И 31, первый 33, третий 34 и четвер- тьй 34 элементы ИЛИ, третий 35 и пер- вьй 36 счетные триггеры соответственно, третий элемент И 37, счетчик 38, дешифратор 39, восьмой элемент И 40, шестой элемент ИЛИ 41, второй триггер 42, десятый 43, одиннадцатый 44, двенадцатый 45 и девятьй 46 элементы И соответственно, первый триггер 47 и пятый элемент И 48,50

Влек 7 сравнения (фиг, 3) содержит регистр 49 и схему 50 равенства,

Блок 10 подготовки данных (фиг. 4) содержит первый регистр 51, схему 52 сравнения, первьш элемент И 53, 53 первый элемент ИЛИ 54„ счетчик 55 ошибок, второй коммутатор 56, дешифратор 57, первый коммутатор 58, п ре:го

40

45

10

15

25 ЗО ;

5 50

53 2315052

гистроБ 59, селектор-мультиплексор

60, второй 61 и третий 62 элементы И и второй элемент ИЛИ 63,

Вход тестовой последовательности и информационный выход устройства представляют собой п-разрядный код в соответствии с разрядностью выбранной ЦВМ,

Вход и выход объекта 5 контроля представляет собой код с числом разрядов меньше или равно п.

Выход счетчика 9 представляет собой k-разрядный код.

Коммутатор 4 может быть построен на 2п двухвходовых схемах И (по две cxeNtb И на один разряд информационно го выхода ЦВМ), При этом сигнал на первом (ВЫХ,1) и втором (ВЫХ,2) выходах коммутатора 4 соответственно :го сост авляет: ВЫХ1-ИНФ1 ТГ2; ВЫХ2«ИНФ1 ТГ2, где ШФ1 - сигнал логического О или 1 i-ro ного выхода ЦВМ;

40

45

разряда информацион- ТГ2, ТГ2 - соответственно прямой и инверсный выходные сигналы триггера 2.

Устройство работает следующим об- разом.

Перед началом работы сигналом, подаваемым по линии 23 связи, триггер 2, тактовьй генератор 3, РИб и блок 1 о подготовки данных устанавли- ваются в исходное (нулевое)состоя- ние, На к,алодом наборе тестовой последовательности устройство последовательно выполняет три цикла,Временная диаграмма работы устройства для одного набора тестовой последовательности приведена на фиг, 5,

При выполнении первого цикла ЦВМ1 выдает в объект 5 контроля по информационному каналу очередной набор тестовой последовательности. Выходной код контролируемого устройства 5 как реакция на поданньй входной код записывается в регистр 49 блока 7 срав- 1ения,

Первьш цикл начинается по сигналу запуска с управляющего выхода ЦВМ, устанавливающего триггер 2 в 1 и запускающего тактовьй генератор 3, Выходной сигнал триггера 2 является управляющим для коммутатора 4. С информационного выхода ЦВМ1 на вход коммутатора 4 поступает очередной набор тестовой последовательности, Сигнсшом 1 с выхода триггера 2 разрешается прохождение набора тестовой последовательности на вход объекта 5j

3 .. контроля. Выходной код контролируемого устройства 5 поступает на регистр 49 блока 7 сравнения.

Последовательность сигналов такто вого генератора 3 через элемент ИЗ 1 запускает счетчик 38, Сигнал с первого выхода дешифратора 39 участвует в формировании сигнала в линии 1I связи, управляющего записью выходного кода контролируемого устройства 5 после окончания в нем переходных процессов в регистр 49, а также обнуляющего счетчик 38 и останавливающег тактовый генератор 3. На этом заканчивается первый цикл.

При выполнении второго цикла сравнивается эталонный код, выдаваемый ЦВМ1, и выходной код контролируемого устройства 5. По результату сравнения формируется код, единица в любом из разрядов которого говорит о несрав- йении для данного разряда кода объекта контроля и эталонного кода,.Последовательно для каждого разряда со значением I, начиная с младшего, формируется код адреса этого разряда и записывается в блок подготовки данных. После окончания формирования блока данных для ЦВМ в нее выдается сигнал прерывания.

Второй цикл также начинается сигналом запуска с управляющего выхода ЦВМ1, отстоящего по времени от первого сигнала запуска на время не менее 4т, где Т - период повторения частоты тактового генератора 3. Через время меньше или равно Т после окончания

.сигнала запуска ЦВМ1 выдает с информационного выхода на коммутатор 4

.эталонный код. Сигналом запуска уста|навливается в О триггер 2 и запус;кается тактовый генератор 3.

При значении О выходного сигнала триггера 2 эталонный код через коммутатор поступает на схему 50 равенства и сравнивается с выходным кодом контролируемого устройства 5,

.поступающим на схему 50 равенства с

выхода регистра 49.

Тактовый генератор 3 вырабатывает последовательность сигналов, запускающих счетчик 38, в результате чего дешифратор 39 выдает сигнал поочередно на каждом из своих выходов, Сигнал с первого выхода дешифратора 39 уча- ствует в формировании сигнала в линии 13 связи, по которому код с выхода схемы 50 равенства переписывается

5 О15

20 , 25 30

,-

0 5

40

5

15054

в сдвигающий регистр 8. Сигналом со второго выхода дешифратора 39 устанавливается в 1 триггер 42, разрешая формирование на выходе элементов И43, 45, 44 сдвинутых одна относительно другой последовательностей п сигналов. где п - число разрядов выходного кода объекта 5 контроля.

Каждым сигналом в линии 17 связи с выхода элемента И45 при условии единичного выхода сдвигающего регис.т- ра 8 увеличивается на единицу состояние счетчика 55, и на соответствующем выходе дешифратора 57 появляется единичный сигнал, управляющий выбором комера регистра 59 для записи Б него выходного кода счетчика 9, являющегося кодом адреса неисправного разряда. Момент записи кода в регистр 59 определяется сигналом в .линии 16 связи с выхода элемента И 44, проходящего через элемент И 62 при условии единичного выхода сдвигающего регистра 8.

Каждый из- п регистров 59 содержит по К разрядов, где К для предельного случая, когда все выходы объекта : контроля не совпадают с эталонным кодом, выбирается из условия

,n,

где К - число разрядов кода , выдаваемого по информационному каналу ЦВМ. Поскольку случай полного несовпаде- ЛИЯ разрядов маловероятен, на практике число регистров 59 может быть уменьшено на 40-50% относительно числа п,

Сигнал с второго выхода дешифратора 39 имеет длительность, равную одному периоду повторения сигналов тактового генератора 3.

Сигнал с третьего выхода дешифратора 39 устанавливает в триггер 47, блокирующий запуск счетчика 38

-через элемент И 31 на время выдачи , последовательности п сигналов элементами И 43, 45, 44. После завершения выдачи п сигналов с выхода счетчика 9 на элемент И 46 поступает К-разрядный единичный код. При этом сигналом 1 с выхода элемента И 46 устанавливается в триггер 36. Сигналом с его выхода устанавливаются в О триггеры 42, 47. При этом прекращается выдача сигналов с выхода элементов И 43, 45, 44 и снимается блокировка запуска счетчика 38. Очередным запускающим сигналом с выхода тактового генерато5

pa 3 снимается сигнал с третьего выхода дешифратора 39, При этом в счетчик 55 записано число всех разрядов вых одного кода блока 7 сравнения, имеющих значение ,

Сигналом с четвертого выхода де- пшфратора 39 через элементы ИШ 41 , 63 -состояние счетчика 55 увеличивается на единицу.

Сигналом с пятого выхода дешифратора 39 код счетчика 55 переписывается в регистр 51 и в ЦВМ1 выдается сигнал прерывания.

Сигналом с шестого выхода дешифра1

второй выход распр еделителя и сов - с входом сдвига сдвигающе стра и со счетным входом счетчи запуска устройства соединен с 5 запуска тактового генератора, которого соединен с тактовым в распределителя импульсов, перв формацоинный вход блока сравне подключен к информационному вы 10 контролируемого устройства, тр выход распределителя импульсов нен с управляющим входом блока нения , выход которого соединен информационным входом сдвигающ

тора 39 счётчик 55 через элемент ИШ. fS гистра, отличающеес 54 устанавливается в О. На этом заканчивается второй цикл.

При выполнении третьего цикла сформированные данные в виде набора кода адресов неисправных разрядов по 20 информационному каналу вьщаются в ЦВМ, затем в систему прерывания ЦВМ выдается сигнал останова процестем,, что, с целью повьппения бы действия устройства, в него вв Т-триггер, коммутатор и блок п товки данных, причем вход запу устройства соединен со счетным дом Т-триггера, установочный в устройства соединен с входом с Т-триггера, установочным входо тового генератора и с первыми ново чными входами распределите пульсов и блока подготовки дан выход 1 -триггера соединен с ра щим входом распределителя импу и с управляющим входом коммута информационный вход которого я ся входом тестовой последоват ти устройства, первый и второй мационные выходы коммутатора с ны соответственно с информацио входом контролируемого устройс вторым информационным входом б сравнения., третий выход распре теля импульсов соединен с перв дом останова тактового генерат четвертый выход распределителя пульсов - с входом сброса счет выход которого соединен с вход да адреса неисправного разряда подготовки данных и с входом е ного кода распределителя импул пятый, шестой, седьмой, восьмо вятьй выходы распределителя им сов соединены соответственно вым разрешающим, вторым разреш счетным, вторым установочным и тьим разрешающим входами блок готовки данньпс, выход сдвигающ регистра соединен с входом оши разрядах блока подготовки дан ход останова блока подготовки соединен с вторым установочным распред€шителя импульсов, втор дом останова тактового генера является выходом останова проц

са, свидетельствукнций об окончании обмена с ЦВМ по данному текущему набору тестовой последовательности. После этого ЦВМ1 или анализирует результаты или переходит к следующему набору тестовой последовательности.

Третий цикл начинается сигналом с седьмого выхода дешифратора 39, Этим сигналом блокируется запуск счетчика 38 и разрешается прохождение на запуск счетчика 55 сигналов тактового генератора 3 через элементы И 48, ИЛИ 41, 63. В соответствии с кодом счетчика 55 селектор-мультиплексор пропускает в линию 22 связи код одного из регистров 59. При совпадении кодов счетчика 55 и регистра 51 срабатывает схема 52 сравнения и сигналом с выхода элемента И 53 обнуляется через элемент ИЛИ 54 счетчик 55, обнуляются- тактовый генератор 3 и ; РИ6, а на второй вход прерывания : ЦВМ1 выдается СИГНАЛ об окончании процесса.

Формула изобретения

1. Устройство для контроля элект- ронных устройств, содержащее тактовый генератор, распределитель импульсов, блок сравнения, сдвигающий ре- гистр, счетчик, причем первый выход распределителя импульсов соединен с входом приема сдвигающего регистра,

31505«

второй выход распр еделителя импульсов - с входом сдвига сдвигающего регистра и со счетным входом счетчика,вход запуска устройства соединен с входом 5 запуска тактового генератора, выход которого соединен с тактовым входом распределителя импульсов, первый ин- формацоинный вход блока сравнения подключен к информационному выходу 10 контролируемого устройства, третий выход распределителя импульсов соединен с управляющим входом блока сравнения , выход которого соединен с информационным входом сдвигающего реfS гистра, отличающеес я

гистра, отличающеес

тем,, что, с целью повьппения быстродействия устройства, в него введены Т-триггер, коммутатор и блок подготовки данных, причем вход запуска устройства соединен со счетным входом Т-триггера, установочный вход устройства соединен с входом сброса Т-триггера, установочным входом тактового генератора и с первыми уста- ново чными входами распределителя импульсов и блока подготовки данных, выход 1 -триггера соединен с разрешающим входом распределителя импульсов и с управляющим входом коммутатора, информационный вход которого является входом тестовой последовательности устройства, первый и второй информационные выходы коммутатора соединены соответственно с информационным входом контролируемого устройства и вторым информационным входом блока сравнения., третий выход распределителя импульсов соединен с первым входом останова тактового генератора, четвертый выход распределителя импульсов - с входом сброса счетчика, выход которого соединен с входом кода адреса неисправного разряда блока подготовки данных и с входом единичного кода распределителя импульсов, пятый, шестой, седьмой, восьмой и де- вятьй выходы распределителя импульсов соединены соответственно с первым разрешающим, вторым разрешающим, счетным, вторым установочным и третьим разрешающим входами блока готовки данньпс, выход сдвигающего регистра соединен с входом ошибки в разрядах блока подготовки данных, выход останова блока подготовки данных соединен с вторым установочным входом распред€шителя импульсов, вторым входом останова тактового генератора и является выходом останова процесса

контроля устройства, информационный выход блока подготовки данных является информационным выходом устройства десятый выход распределителя и; -пульсов соединен с четвертым разг ;11ающим входом блока подготовки данных и с выходом сигнала прерывания устройства, причем блок подготовки данных содержит схему сравнения, счетчик ошибок, дешифратор, два коммутатора, селектор-мультиплексор, п+1 регистров, где п-разрядность кода тестовой последовательности, три элемента И и два элемента ИЛИ, причем вход приема первого регистра является четвер- тым разрешающим входом блока подготовки данных, выход первого регистра соединен с первым входом схемы сравнения, выход которой соединен с первым входом первого элемента И, выход которого соединен с первым входом йерного элемента ЛЛИ и является выходом останова блока подготовки данных, второй и третий входы первого элемента ИЛИ являются соответственно первым и вторым установочными входами блока подготовки данныхJ выход первого элемента ИЛИ соединен с входом сброса счетчика ошибок, счетный вход которого соединен с выходом второго элемен- та ИЛИ, первый вход которого является счетным входом блока подготовки данных, а второй вход соединен с выходом второго элемента И, первый вход которого является вторым разрешающим входом блока подготовки данных, вход ошибки в разрядах блока подготовки данных подключен к второму входу второго элемента И и к первому входу третьего элемента И, второй вход ко- торого является первым разрешающим входом блока подготовки данных, выход третьего элемента И соединен с управляющим входом первого коммутатора, выход счетчика ошибок соединен с ин- формационным входом первого регистра,с вторым входом схемы сравнения, с информационными входами второго коммутатора и дешифратора, п выходов дешифратора соединены с группой ин- формационных входов первого коммутатора, третий разрешающий вход блока подготовки данных подключен к управляющему входу второго коммутатора и к второму входу первого элемента И, выход второго коммутатора -соединен с управляющим входом селектора-мультиплексора, группа информационнхы входов которого соединена с выходами второго - (п+1)-го регистров, первый - п-й выходы первого коммутатора соединены соответственно с входами приема второго - (п+1)-го регистров, информационные входы которых образуют вход кода адреса неисправного разряда блока подготовки данных, выход селектора-мультиплексора является ин .формациокным выходом блока подготовк

данных.

2. Устройство по п. I, отличающееся тем, что распределитель импульсов содержит счетчик, дешифратор, три Т-триггера, два триггера , шесть элементов ИЛИ и двенадцать элементов И, причем первый и второй входы первого элемента ИЛИ являются соответственно первым и вторы установочными входами распределителя импульсов, выход первого элемента ШШ соединен с первым входом второго элемента ШШ, установочными входами первого, второго и третьего Т-триггеров первыми входами третьего и четвертого элементов ШШ и является четвертым выходом распределителя импульсов, тактовый вход распределителя импульсов подключен к прямому входу первого элемента И, к первому прямому входу второго элемента И и к первым входам третьего, четвертого и пятого элементов И, выход четвертого элемента И является третьим выходом распределителя импульсов и соединен с первым входом пятого элемента ШШ, вторым входом второго элемента ИЛИ и первым инверсным входом первого элемента И, выход которого соединен со счетным входом счетчика, вход сброса которого соединен с выходом второго элемента ИЛИ, а группа выходов счетчика соединена с группой входов дешифратора, первый выход которого соединен с первым входом шестого элемента И и с вторым прямым входом второго элемента И, второй, третий и четвертый выходы дешифратора соединены соответственно с первым входом седьмого элемента И, с прямым входом восьмого элемента И и с первым входом шестого элемента ИЛИ, пятый и шестой выходы дешифратора являются соответственно десятым и восьмым выходами распределителя импульсов, седьмой выход дешифратора соединен с вторым инверсным входом первого элемента И, вторым входом пятого элемен

9

та И и является девятым выходом распределителя импудьсов, выход пятого элемента И соединен с вторым входом шестого элемента ИЛИ, выход которого является седьмым выходом распределителя импульсов, первый вход девятого элемента И является входом единичного кода распределителя импульсов, выход девятого элемента И соединен со счетным кходом первого Т-триггера, выход которого соединен с вторыми входами третьего и четвертого элементов ИЛИ и инверсным входом восьмого

элемента И, выход которого соединен с S-входом первого триггера, R-вход которого соединен с выходом четвертого элемента ИЛИ, а выход первого триггера соединен с третьим инверсны входом первого элемента И, вход разрешения распределителя импульсов подключен к второму входу шестого элемента И и к инверсньтм входам второго и седьмого элементов И, выход шесто- го элемента И соединен с вторым вхо дом пятого элемента ИЛИ, выход которого соединен со счетньи входом второго Т-триггера, выход которого

0

1505

10

соединен с вторым входом четвертого элемента И, выход второго элемента И является первым выходом распределителя импульсов, выход седьмого элемента И соединен с S-входом второго триггера, Н--вход которого соединен с выходом третьего элемента ИЛИ, выход второго триггера соединен с прямым входом десятого элемента И и с вторым входом третьего элемента И, выход которого соединен с первым инверсным входом десятого элемента И, первым входом одиннадцатого элемента И, прямым входом двенадцатого элемента 5 И и счетным входом третьего Т-триггера, выход которого соединен с вторым инверсным входом десятого элемента И, BTopbws входом одиннадцатого элемента И и инверсным входом двенадцатого элемента И, выходы десятого, одиннадцатого и двенадцатого элементов И являются соответственно вторым пятым и шестым выходами распределителя импульсов, выход одиннад-. цатого элемента И соединен с вто- рьт входом девятого злемен - та И,

0

5

(p.Vff. /

tfae.t

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для контроля электронных устройств | 1978 |

|

SU978151A2 |

| Система для контроля электронных устройств | 1988 |

|

SU1667074A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для ввода информации | 1986 |

|

SU1383330A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Устройство для контроля ЦВМ | 1987 |

|

SU1509908A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

Изобретение относится к вычислительной технике и автоматике и может :быть использовано в системах автоматического контроля интегральных микросхем, а также блоков и устройств дискретного действия при их производстве и эксплуатации. Целью изобретения является повышение быстродействия устройства. Устройство позволяет на каящом наборе тестовой последовательности сократить число прерываний в : ЦВМ и затрат мшпинного времени на организацию процесса прерывания. Уст- . ройство для контроля электронных устройств содержит триггер со счетным входом, тактовьй генератор, коммутатор, распределитель импульсов, блок сравнения, сдвигающий регистр, счетчик и блок подготовки данных. 1 з.п. ф-лы, 5 ил. § (Л сд о ел

11

/

2ц

э

Фив: 5

| Гуляев В.А., Макаров С.М., Новиков B.C | |||

| Диагностика вычислительных машин | |||

| Киев: Техника, 1981, с | |||

| Способ получения продукта конденсации бетанафтола с формальдегидом | 1923 |

|

SU131A1 |

| Система для контроля электронных устройств | 1977 |

|

SU696464A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1984-09-05—Подача