Устройство для преобразования перемещения в код относится к преобразователям неэлектрических величин в дискретный электрический сигнал и может найти применение в многоканальных системах сбора информации, в устройствах цифровой индикации положения элементов управляемого объекта., в замкнутых системах числового програмного управления (ЧПУ) станками для управления положением подвижных элементов станка.

Известно счетно-решающее устройство, содержащее два цифроаналоговых положительных устройства, на входы которых поступают аналоговые выходт ные сигналы синусно-косинусного датчика (индуктосин, сельсин, вращающийся трансформатор) и компенсационные сигналы, представленные в двоичном коде и выбираемые из двух постоянных запоминаюиуих устройстзв.

Разностное устройство вырабатывает сигнал ошибки, который анализируется схемой управления счетчиком, JlBVM уровням мплитуды сигна га ошкбки соответствуют два фиксированных значенияГдискретности, которые обуславливают состояние реверсивного счетчика. Выход счетчика является адресом вы борки компенсационных сигналов, записанных в постоянных запоминающих устройствах. Работа устройства .осуществляется до обеспечения равенства нулю сигнала ошибки, при этом на выходе счетчика устанавливается электрический эквивалент механического перемещения подвижных частей датчика друг относительно друга, выраженный в дво10ичном коде Ц.

Недостатком устройства является его сравнительно низкое быстродействие, обусловленное тем, что данное устройство является аналого-цифровым

15 преобразователем следящего типа и предполагает невысокие скорости и ускорения измеряемых величин перемещений 2 .

Известно устройство аналого-цифро20вого преобразователя тригонометрических функций, содержащее два цифроаналоговых множительных устройства, выходы которых соединены со входами аналого-цифрового интегрирующего устройства, выход которого через преобразователь цифровых сигналов соединен со входами цифроаналоговых множительных устройств ГЗ .

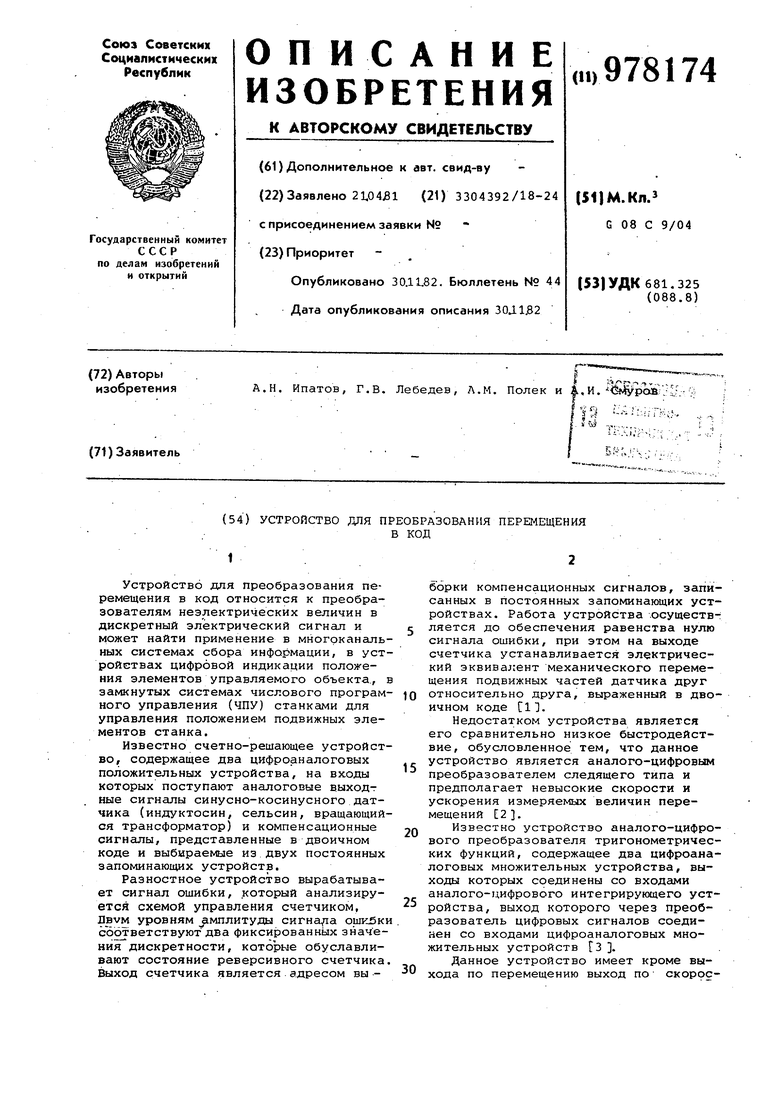

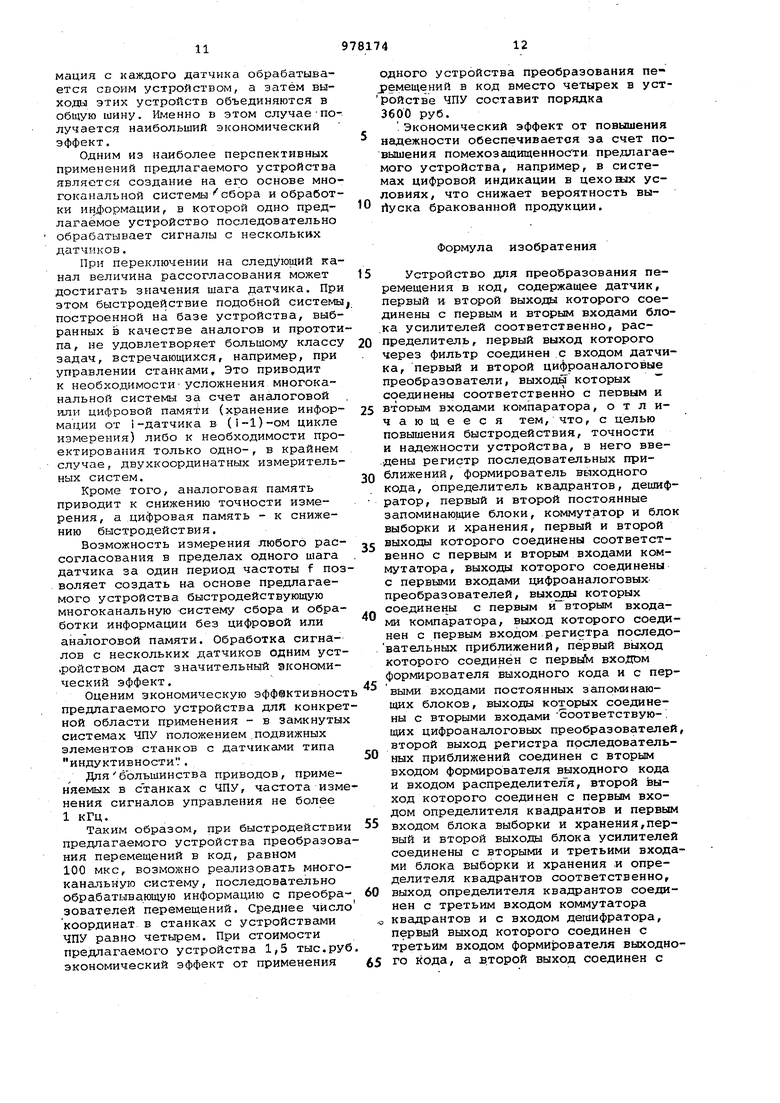

Данное устройство имеет кроме вы30хода по перемещению выход по скорости, однако быстродействие устройства ограничено, так как его можно отнести к аналого-цифровым преобразова телям с двойным интегрированием Г2. Кроме того. Преобразования по опре- . делению измеряемой величины осуществ ляются не реверсивными счетчиками,ка в устройстве 13, а последовательннчми регистрами сдвига. Наиболее близким по техническому решению к предлагаемому является уст ройство для преобразования перемещений в код, содержащее датчик, выходы которого через блок усилителей соединены с первыми входа1ми цифроаналоговых преобразователей, выходы которых соединены соответственно с первы и вторым входами блокё1ми выбора знака, распределитель сигналов, первый выход которого через фильтр соединен со входом датчика, второй,выход - с первым входом анализатора рассогласования (компаратора), выход которого соединен со вторым входом блока выбора дискретности, третий выход распределителя сигналов соединен с первым входом блока выбора дискретности, выход которого соединен со входом реверсивного счетчика и первым, входом синусно-косинусного цифро вого преобразователя, четвертый выход распределителя импульсов соединен со вторым входом синусно-косинус ного преобразователя, первый и второй входы которого соединены со вторыми входами соответствующих цифроаналоговых преобразователей, а трети выход соединен; с третьим входом блок выбора знака ( коммутатора квадрантов ), выход которого соединен с первым входом анализатора рассогласования 4 . По сравнению с устройствами следя щего типа и устройствами, работающими по принципу двойного интегрирования, быстродействие известного устройства выше за счет реализуемой в устройстве динамическойпрограммы. Однако это увеличение быстродействия достигается за счет снижения точности измерения из-за увеличения дискретности. Поэтому необходимость изме рения с высокой точностью накладывает существенные ограничения на допус тимые скорости и ускорения измеряеNBdx перемещений. Кроме того, для всех вышеперечисленных устройств, имеющих в канале отработки рассогласования реверсивный счетчик или регистр сдвига, характерна относительно низкая помехозащищенность и, следовательно, низкая надежность, особенно для систем циф,)овой индикации в цеховых условиях. Цель изобретения - повышение быстродействия, точности и надежности устройства для преобразования перемещений в код. Поставленная цель достигается тем, что в устройство для преобразования перемещения в код, содержащее датчик, первый и второй выходы которого соединены с первым rt вторым входами блока усилителей соответственно, распределитель, первый выход которого через фильтр соединен с входом датчика, первый и второй цифроаналоговые преобразователи, выходы которых соединены соответственно с первым и вторым входами компаратора, введены регистр последовательных приближений, формирователь выходного кода, определитель квадрантов, дешифратор, первый и второй постоянные запоминающие блоки, коммутатор и блок выборки и хранения, первый и второй выходы которого соединены соответственно с первым и вторым входами коммутатора, выходы которого соедине.ны с первыми входами цифроаналоговых преобразователей; выходы которых соединены с первым и вторым входами компаратора, выход которого соединен с первым входом регистра последовательных приближений, первый выход которого сое.динен с первым входом формирователя выходного кода и с первыми входами постоянных запоминающих блоков, выходы которых соединены с вторыми входами соответствующих цифроаналоговых преобразователей, второй выход регистра последовательных приближений соединен с вторым входом формирователя выходного кода и входом распределителя, второй выход которого соединен с первым входом определителя квадрантов и первым входом блока выборки и хранения, первый и второй выход блока усилителей соединен со вторыми и третьими входами блока выборки и хранения и определителя квадрантов соответственно, выход определителя квадрантов соединен с третьим входом коммутатора квадрантов и с входом детиифратора, первый выход которого соединен с третьим входом формирователя выходного кода, а второй выход соединен с вторыми входами постоянных запоминакяцих блоков, третий и четвертый выходы распределителя соединены со вторым и третьим входами регистра последовательных приближений соответственно. На фиг. 1 изображена структурная схема устройства; на фиг. 2 - диаграмма работы распределителя; на фиг. 3 - определитель квадрантов; на фиг. 4 - коммутатор квадрантов; на фиг. 5 - диаграммы, поясняющие принцип адресации постоянных запоминающих устройств. Предлагаемое устройство содержит распределитель 1, фильтр 2, датчик 3, блок 4 усилителей, блок 5 выборки

и хранения, коммутатор 6 квадрантов, определитель 7 квадрантов, дешифратор 8, цифроаналоговые преобразователи (UAnj 9 и 10, постоянные запоминающие блоки (ПЗБ) 11 и 12, компаратор 13, регистр 14 последовательных приближений (РПП), формирователь . 15 выходного кода.

Выходы датчика 3 соединены со входами блока 4 усилителей, первый выход которого соединен с первыми входами блока 5 выборки и хранения и определителя 7 квадрантов, второй выход блока 4 усилителей соединен со. вторыми входами блока 5 выборки и хранения и определителя квадрантов 7, выход которого соединен с третьим входом коммутатора 6 квадрантов и со входом дешифратора 8. Первый выход дешифратора В соединен с третьим входом преобразователя 15 выходного кода, а второй выход соединен со вторыми входами ПЗУ 11 и ПЗУ 12. Первый и второй входы коммутатора б квадрантов соединены ,с соответствующими выходами блока 5 выборки хранения, а первый и второй выходы соединены со. ответственно с первыми входами ЦАП 9 и 10, выходы которых соединены с первым и вторым входами компаратора 13. Выход компаратора соединен с первым входом РПП 14, первый выход которого соединен с первым входом выходного формирователя 15 кода, а также с первыми входами ПЗБ 11 и 12, выходы которых соединены соответственно со вторыми входами ЦАП 9 и 10. Второй выход РПП 14 соединен со вторым входом формирователя 15 выходного кода и входом распределителя 1, первый выход распределителя через фильтр 2 соединен со входом датчика 3, второй выход распределителя 1 соединен с первым входом определителя 7 квадрантов и первым входом блока 5 выборки и хранения,, третий и четвёртый выходы распределителя 1 соединены соответственно со вторым и третьим входами РПП 14.

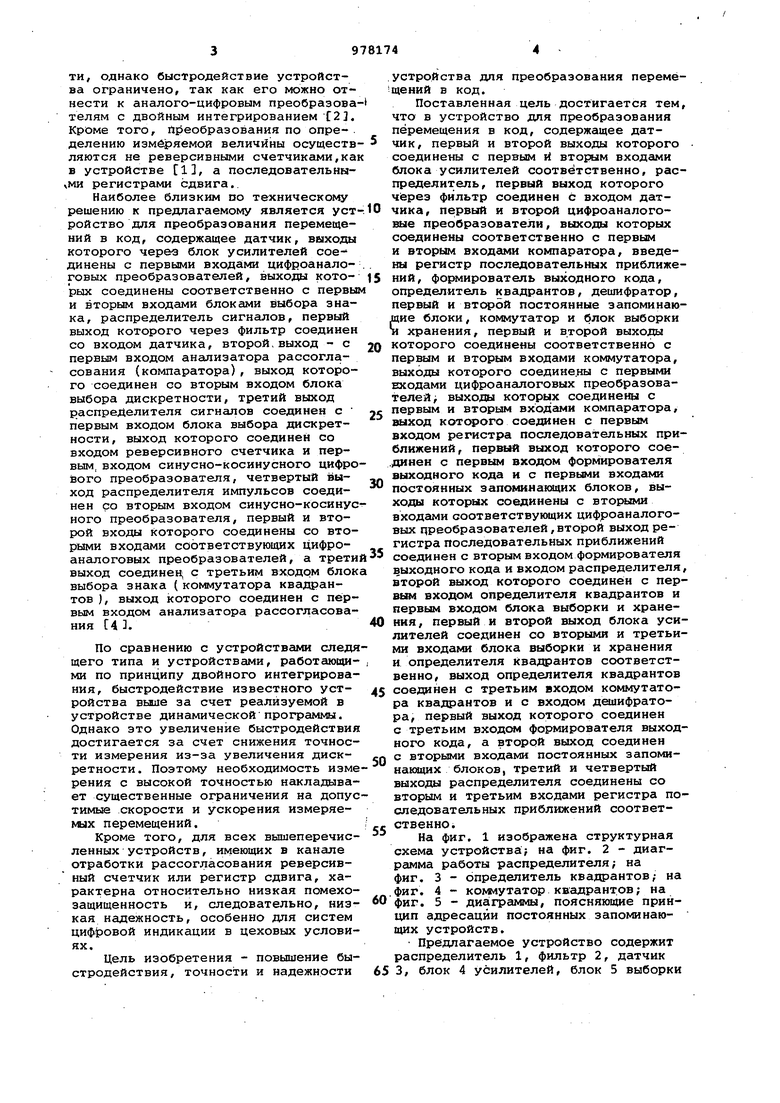

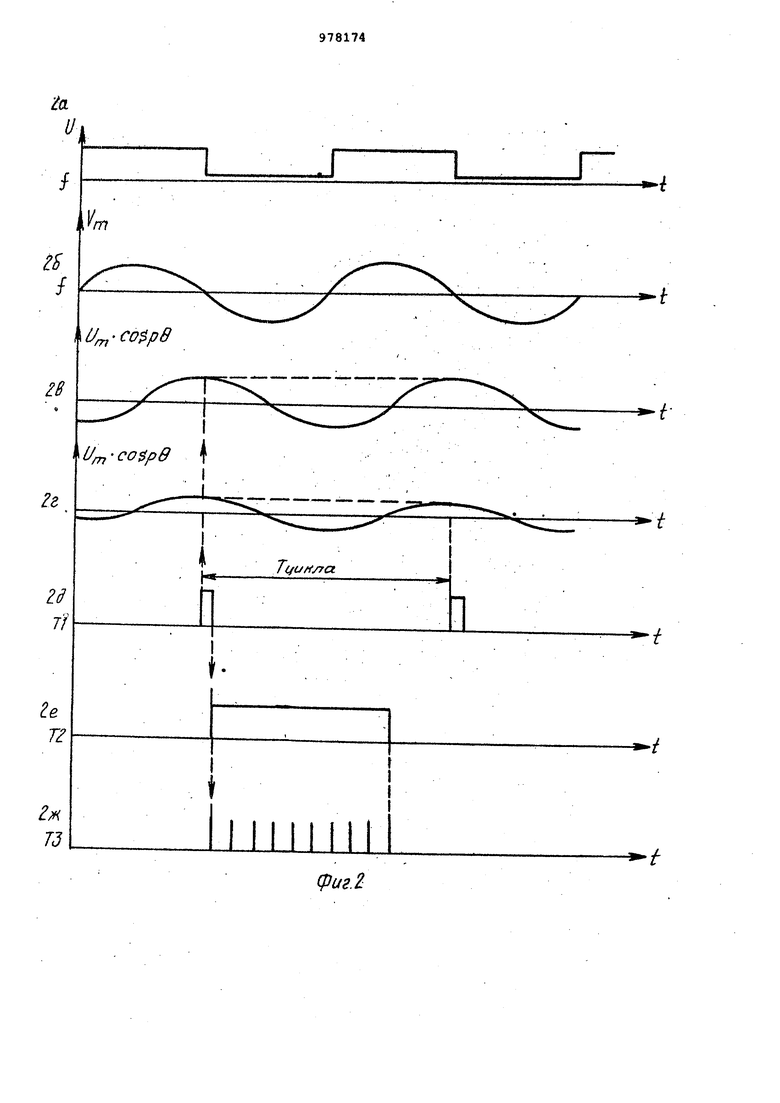

Определитель 7 квадрантов (фиг.З) состоит из двух компараторов 16 и 17 Коммутатор 6 квадрантов (фиг. 4) содержит операционные усилители 18, 19 и ключи 20, 21.

Устройство работает следующим образом.

Рассмотрим работу устройства на примере работы с датчиком типа кругювой.индуктосин (фиг. 2).

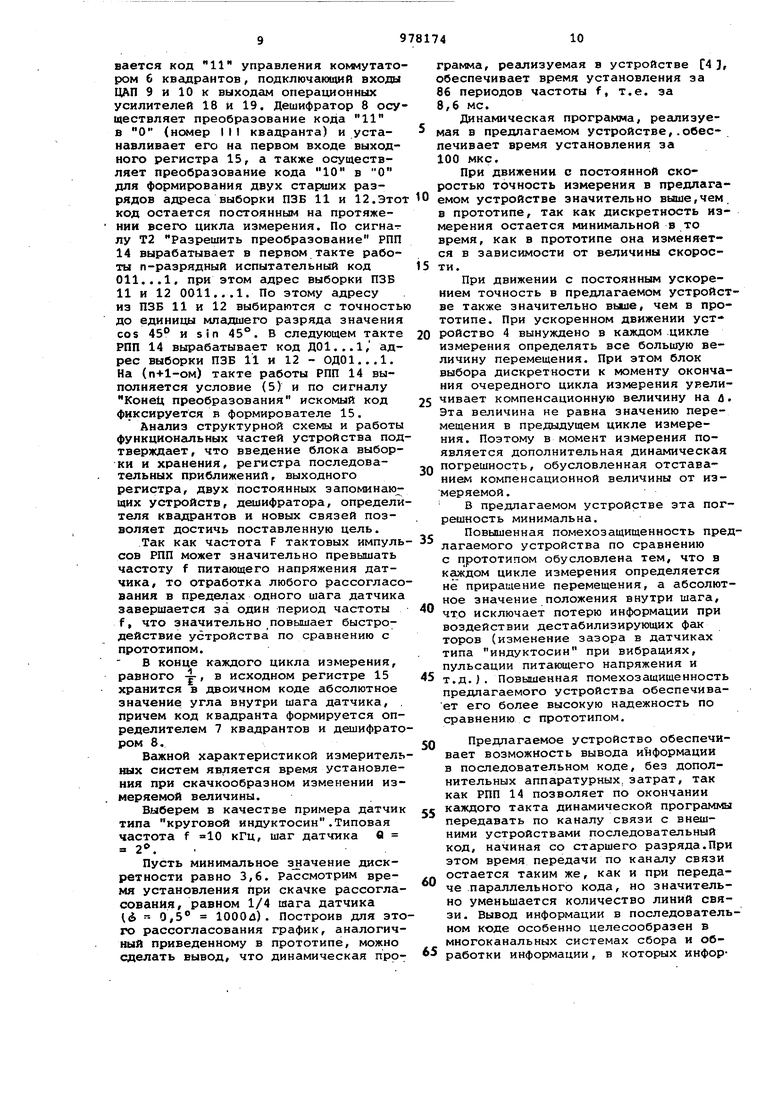

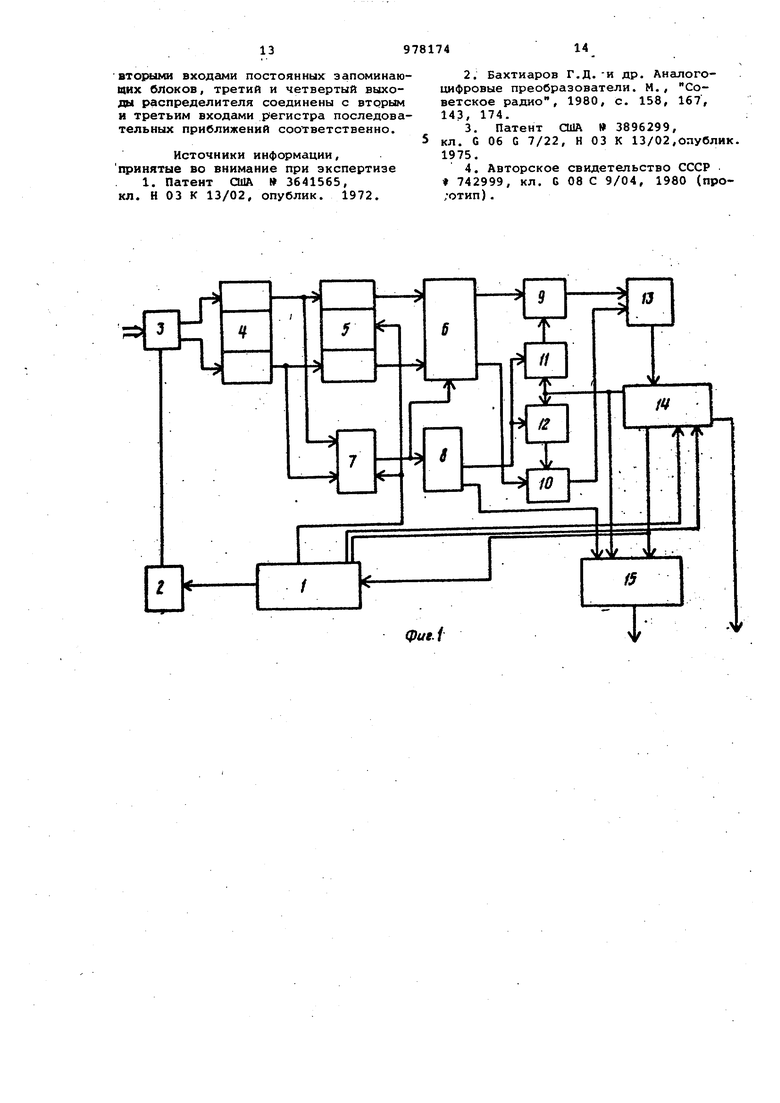

Импульсный сигнал частоты распределителя 1 (фиг. 2а) фильтром 2 преобразуется в синусоидальный сигнгш. (фиг. 2б). Этим сигналом запитывается роторная обмотка датчика 3. Со статорных обмоток датчика снимаются информационные сигнгшы U ebK t и , (фиг. 2в и 2г), промодулированные по амплитуде по законам синуса и косинуса в функции от угла поворота

Ujb,,. Urn sinpe-srn(2Jft-90° (1) UebW2 и„, cospe.sin(2 ft-90), (2)

где p - число пар полюсов обмотки

ротора или коэффициент электрической редукции; 9 - механический угол поворота

ротора относительно статора. В частности,для кругового индуктосина р 180, и шаг датчика равен 2. Для датчика типа индуктосин сигналы статорных обмоток сдвинуты по фазе на 90° относительно сигнала обмотки ротора. Эти сигналы через блок 4 усилителей поступают в блок 5 выборки и хранения и определитель 7 квадрантов. В блоке 5 выборки и хранения, состоящем из двух типовых схем выборки и хранения, запоминаются мгновенные значения амплитуд сигналов (1) и (2) в моменты времени

t -т- + 2к 5 (к 0,1) по сигналу Т1 от распределителя 1 (фиг.2д).

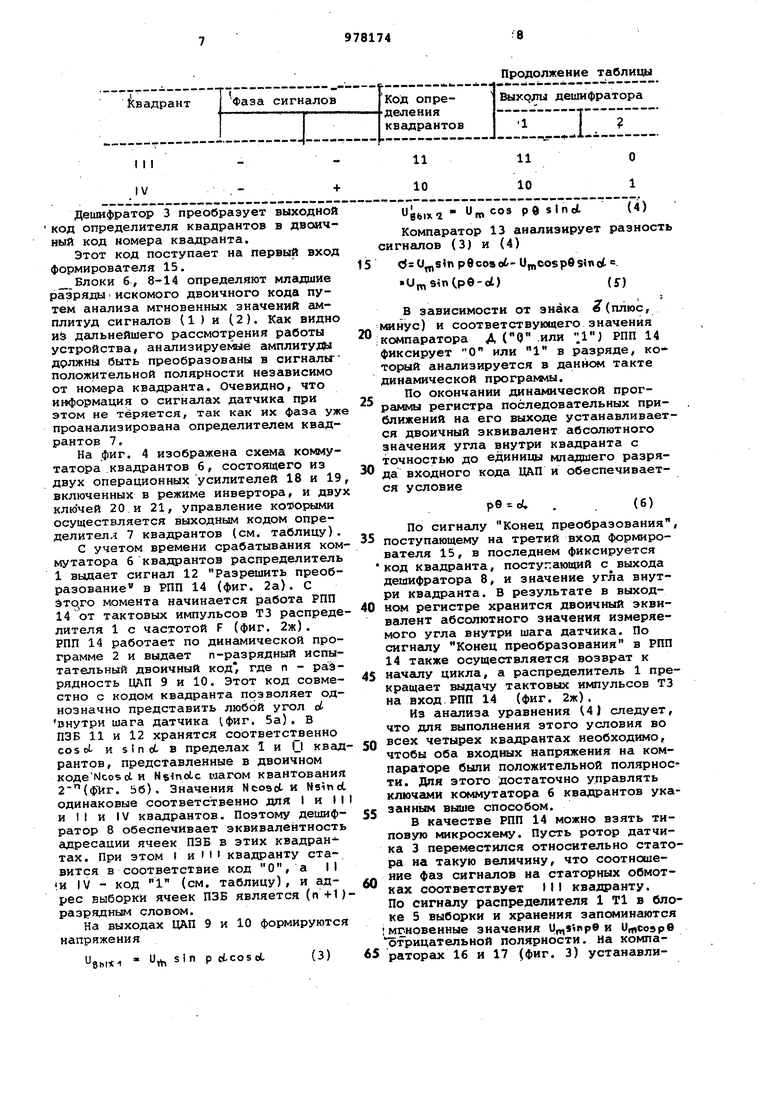

Целью преобразования выходных сигналов датчика является определение oL-электрического эквивалента угла р и представление его в двоичном коде. Два старших разряда искового кода указывают на Hcwep четверти шага датчика (номер квадранта), в котором расположен измеряемый угол р®..

Определитель 7 квадрантов (фиг.З) совместно с дешифратором 3 служит

45 для определения номера квадранта.Определитель 7 квадрантов состоит иэ двух компараторов 16 и 17, стробируемых с71гналом распределителя 1, и фактически является анализатором фазы

50 выходных сигналов датчика Ue(,ni7 Первому квадранту соответствует выходной код определителя квадрантов 7 00, второму - код 01. третьему - код 11 и четвертому - код

55 10 (в старшем разряде анализируется фаза сигнала Cl, в младшем фаза сигнала 2 согласно таблицы)1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синусно-косинусного цифроаналогового преобразования | 1983 |

|

SU1278897A1 |

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

| Измерительный преобразователь | 1988 |

|

SU1553843A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Скважинный инклинометр | 1990 |

|

SU1721225A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1280698A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478332A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1119050A1 |

| Двухотсчетный преобразователь угол-код | 1986 |

|

SU1403372A1 |

01

01

код определителя квадрантов в двоичный код номера квадранта.

Этот код поступает на первый вход формирователя 15.

Блоки 6, 8-14 определяют младшие

разряды искомого двоичного кода путем анализа мгновенных значений амплитуд сигналов (1 ) и (2). Как видно и дальнейшего рассмотрения работы устройства, анализируемые амплитуды дрлжны быть преобразованы в сигналы положительной полярности независимо от номера квадранта. Очевидно г что информация о сигналах датчика при этом не теряется, так как их фаза уж проанализирована определителем квадрантов 7.

На фиг. 4 изображена схема коммутатора квадрантов 6, состоящего из двух операционных усилителей 18 и 19 включенных в режиме инвертора, и дву ключей 20 и 21, управление которыми осуществляется выходным кодом определителл 7 квадрантов (см. таблицу).

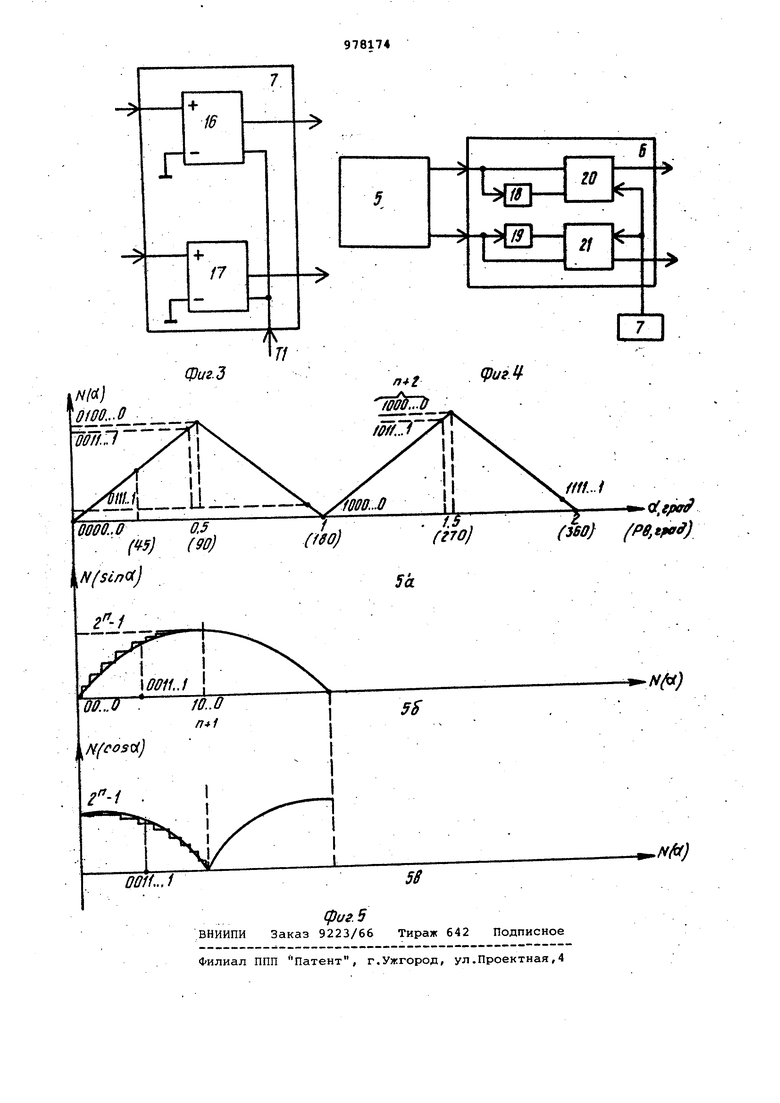

С учетом времени срабатывания коммутатора б квадрантов распределитель 1 выдает сигнал 12 Разрешить преобразование в РПП 14 (фиг. 2а). С йто.,го момента начинается работа РПП 14 от тактовых импульсов ТЗ распределителя 1 с частотой F (фиг. 2ж). РПП 14 работает по динамической программе 2 и выдает п-разрядный испытательный двоичный код где п - ра1эрядность ЦАП 9 и 10. Этот код совместно с кодом квадранта позволяет однозначно представить любой угол ( внутри шага датчика 1фиг. 5а). В ПЗБ 11 и 12 хранятся соответственно со sot и sinoL в пределах 1 и П квадрантов, представленные в двоичном кодеМсовd и шагом квантования 2(ф11г. 5б). Значения NcosoL и Msind одинаковые соответственно для I и II и II и IV квадрантов. Поэтому дешифратор 8 обеспечивает эквивалентность адресации ячеек ПЗБ в этих квадрантах. При этом I и м I квадранту ставится в соответствие код О, а II И IV - код 1 (см. таблицу), и адрес выборки ячеек ПЗБ является (п +1)разрядным словом.

На выходах ЦАП 9 и 10 формируются напряжения

(3)

- Uyf, sin р dcos oL

и

вЫ«1

Продолжение таблицы

Компаратор 13 анализирует разность сигналов (3) и (4)

iS pecosot-и,„со8рв5 по(., (pe-ot)(5-)

В зависимости от знака (плюс, минус) и соответствующего значения компаратора Д (9 .или 1) РПП 14 фиксирует О или 1 в разряде, которшй анализируется в данном такте динамической программы.

По окончании динамической програколы регистра последовательных приближений на его выходе устанавливается двоичный эквивалент абсолютного значения угла внутри квадранта с точностью до единицы младшего разряда входного кода ЦАП и обеспечивается условие

(. . (б)

По сигналу Конец преобразования,

5 поступающему на третий вход формирователя 15, в последнем фиксируется код квадранта, поступающий с выхода дешифратора 8, и значение угла внутри квадранта. В результате в выходном регистре хранится двоичный эквивалент абсолютного значения измеряемого угла внутри шага датчика. По сигналу Конец преобразования в РПП 14 также осуществляется возврат к

5 началу цикла, а распределитель 1 прекращает выдачу тактовых импульсов ТЗ на вход РПП 14 (фиг. 2ж).

Из анализа уравнения И) следует, что для выполнения этого условия во

Q всех четырех квадрантах необходимо, чтобы оба входных напряжения на компараторе бьши положительной полярноети. Для этого достаточно управлять ключами коммутатора б квсшрантов укас занным выше способом.

В качестве РПП 14 можно взять типовую микросхему. Пусть ротор датчика 3 переместился относительно статора на такую величину, что соотнсшение фаз сигналов на статорных обмоткак соответствует III квадранту. По сигналу распределителя 1 Т1 в блоке 5 выборки и хранения запоминаются мгновенные значения U sinpO и U icospe ртрицательной полярности, на компа 5 раторах 16 и 17 (фиг. 3) устанавливается код 11 управления коммутатором б квадрантов, подключающий входы ЦАП 9 и 10 к выходам операционных усилителей 18 и 19. Дешифратор 8 осуществляет преобразование кода 11 в О (нсмер II1 квадранта) и устанавливает его на первом входе выходного регистра 15, а также осуществляет преобразование кода 10 в О для формирования двух старших разрядов адреса выборки ПЗБ 11 и 12.Это код остается постоянным на протяжении всего цикла измерения. По сигна-г лу Т2 Разрешить преобразование РПП 14 вырабатывает в первом такте работы п-разрядный испытательный код 011...1, при этом адрес выборки ПЗБ 11 и 12 0011...1. По этому адресу из ПЗБ 11 и 12 выбираются с точность до единицы младшего разряда значения cos 45° и sin 45°. В следующем такте РПП 14 вырабатывает код Д01...1, адрес выборки ПЗВ 11 и 12 - ОД01...1. На (п+1-ом) такте работы РПП 14 выполняется условие (5) и по сигналу KoHet; преобразования искомый код фиксируется в формирователе 15.

Анализ структурной схемы и работы функциональных частей устройства подтверждает , что введение блока выборки и хранения, регистра последовательных приближений г выходного регистра, двух постоянных запоминающих устройств, дешифратора, определителя квадрантов и новых связей позволяет достичь поставленную цель.

.Так как частота F тактовых импульсов РПП может значительно превышать частоту f питающего напряжения датчика, то отработка любого рассогласования в пределах одного шага датчика завершается за один период частоты f, что значительно повышает быстродействие устройства по сравнению с прототипом.

В конце каждого цикла измерения, равного -J-, в исходном регистре 15 хранится в двоичном коде абсолютное значение угла внутри шага датчика, . причем код квадранта формируется определителем 7 квадрантов и дешифратором 8.

Важной характеристикой измерительных систем является время установления при скачкообразном изменении измеряемой величины.

Выберем в качестве примера датчик типа круговой индуктосин.Типовая частота f 10 кГц, шаг датчика в 2. .

Пусть минимальное 3jia4eHHe дискретности равно 3,6. Рассмотрим время установления при скачке рассогласования, равном 1/4 шага датчика {& - 0,5 1000л). Построив для этого рассогласования график, аналогичный приведенному в прототипе, можно сделать вывод, что динамическая программа, реализуемая в устройстве С4, обеспечивает время установления за 86 периодов частоты f, т.е. за 8,6 мс.

Динамическая программа, реализуемая в предлагаемом устройстве,.обеспечивает время установления за 100 МКС.

При движении с постоянной скоростью точность измерения в предлагаемом устройстве значительно выше,чем в прототипе, так как дискретность измерения остается минимальной в то время, как в прототипе она изменяется в зависимости от величины скорости.

При движении с постоянным ускорением точность в предлагаемом устройстве также значительно вьше, чем в прототипе. При ускоренном движении устройство 4 вынуждено в каждом цикле измерения определять все большую величину перемещения. При этом блок выбора дискретности к моменту окончания очередного цикла измерения уреличивает компенсационную величину на и, Эта величина не равна значению перемещения в предыдущем цикле измерения. Поэтому в момент измерения появляется дополнительная динамическая

погрешность, обусловленная отставанием компенсационной величины от измеряемой .

В предлагаемом устройстве эта погрешность минимальна.

Повышенная помехозащищенность предлагаемого устройства по сравнению с прототипом обусловлена тем, что в каждом цикле измерения определяется не приращение перемещения, а абсолютное значение положения внутри шага,

что исключает потерю информации при воздействии дестабилизирующих фак торов (изменение зазора в датчиках типа индуктосин при вибрациях, пульсации питающего напряжения и

т.д.). Повышенная помехозащищенность предлагаемого устройства обеспечйвает его более высокую надежность по сравнению с прототипом.

Предлагаемое устройство обеспечивает возможность вывода и11формации в последовательном коде, без дополнительных аппаратурных, затрат, так как РПП 14 позволяет по окончании

каждого такта динамической программы передавать по каналу связи с внешними устройствами последовательный код, начиная со старшего разряда.При этом время передачи по каналу связи

остается таким же, как и при передаче параллельного кода, но значительно уменьшается количество линий связи. Вывод информации в последовательном коде особенно целесообразен в многоканальных системах сбора и обработки информации, в которых информация с каждого датчика обрабатывается своим устройством, а затем выходы этих устройств объединяются в общую шину. liMeHHo в этом случае-получается наибольший экономический эффект.

Одним из наиболее перспективных применений предлагаемого устройства является создание на его основе многоканальной системысбора и обработки инДюрмации, в которой одно предлагаемое устройство последовательно обрабатывает сигналы с нескольких датчиков.

При переключении на следующий канал величина рассогласования может достигать значения шага датчика. При этом быстродействие подобной системы построенной на базе устройства, выбранных в качестве аналогов и прототипа , не удовлетворяет большому классу задач, встречающихся, например, при управлении станками. Это приводит к необходимости-усложнения многоканальной системы за счет аналоговой или цифровой памя- и (хранение информации от i-датчика в (1-1)-ом цикле измерения) либо к необходимости проектирования только одно-, в крайнем случае, двухкоординатных измерительных систем.

Кроме того, аналоговая память приводит к снижению точности измерения, а цифровая память - к снижению быстродействия.

Возможность измерения любого рассогласования в пределах одного шага датчика за один период частоты f позволяет создать на основе предлагаемого устройства быстродействующую многоканальную систему сбора и обработки информации без цифровой или аналоговой памяти. Обработка сигналов с нескольких датчиков одним уст.ройством даст значительный экономический эффект.

Оценим экономическую эффективност предлагаемого устройства для конкретной области применения - в замкнутых системах ЧПУ положением .подвижных элементов станков с датчикги«1и типа индуктивности ..

Длябольшинства приводов, применяемых в станках с ЧПУ, частота изменения сигналов управления не более 1 кГц.

Таким образом, при быстродействии предлагаемого устройства преобразования перемещений в код, равном 100 МКС, возмонсно реализовать многоканальную систему, последовательно обрабатывающую информацию с преобразователей перемещений. Среднее число координат в станках с устройствами ЧПУ равно четырем. При стоимости предлагаемого устройства 1,5 тыс.руб экономический эффект от применения

одного устройства преобразования пе земещений в код вместо четырех в устройстве ЧПУ составит порядка 3600 руб.

. Экономический эффект от повышения

надежности обеспечивается за счет повышения помехозащищенности предлагаемого устройства, например, в системах цифровой индикации в цехонлх условиях, что снижает вероятность выrtycKa бракованной продукции.

Формула изобратения

5 Устройство для преобразования перемещения в код, содержащее датчик, первый и второй выходы которого соединены с первым и вторым входами блока усилителей соответственно, распределитель, первый выход которого через фильтр соединен с входом датчика, первый и второй цифроаналоговые преобразователи, выходы которых соединены соответственно с первым и 5 ВТОРЫМ входами компаратора, отличающееся тем, что, с целью повышения быстродействия, точности и надежности устройства, в него вве.дены регистр последовательных приQ ближений, формирователь выходного

кода, определитель квадрантов, дешифратор, первый и второй постоянные запоминающие блоки, коммутатор и блок выборки и хранения, первый и второй c выходы которого соединены соответственно с первым и вторым входами коммутатора, выходы которого соединены с первыми входами 1у1фроаналоговых преобразователей, выходы которых соединены с первым и вторым входами компаратора, выход которого соединен с первым входом регистра последовательных приближений, первый выход которого соединён с первьЛл входом формирователя выходного кода и с первыми входами постоянных запоминающих блоков, выходы которых соединены с вторыми входами соответствую-. щих цифроаналоговых преобразователей, второй выход регистра прследователь0 ных приближений соединен с вторым входом формирователя выходного кода и входом распределителя, второй выход которого соединен с первым входом определителя квадрантов и первым 5 входом блока выборки и хранения,первый и второй выходы блока усилителей соединены с вторыми и третьими входами блока выборки и хранения и определителя квадрантов соответственно, 0 выход определителя квадрантов соединен с третьим входом коммутатора ,а квадрантов и с входом дешифратора, первый выход которого соединен с третьим входом формирователя выходного кода, а второй выход соединен с вторыми входами постоянных запоминающих блоков, третий и четвертый выходы распределителя соединены с вторым и третьим входами регистра последовательных приближений соответственно. Источники информации, принятые во внимание при экспертизе 1. Патент США 3641565, кл. Н 03 К 13/02, опублик. 1972 9 4 2.Бахтиаров Г,Д.-и др. Аналогоцифровые преобразователи. М., Советское радио, 1980, с. 158, 167, 143 / 174. 3.Патент США 3896299, 1975 ° ° ° 13/02,опублик. 4.Авторское свидетельство СССР . 742999, кл. G 08 С 9/04, 1980 (про;отип).

i

s

Ufrj-со рв

TifUH a

гд

7/

T-J

(риг.2:

1

t

Авторы

Даты

1982-11-30—Публикация

1981-04-21—Подача