(54) УСТРОЙСТЕЗО ДЛЯ ВВОДА ИНФОРМАИИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения задач в вычислительной системе | 1988 |

|

SU1508226A1 |

| Устройство для ввода информации | 1984 |

|

SU1291988A1 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Многоканальное устройство для распределения заданий процессорам | 1988 |

|

SU1619287A1 |

| Устройство переменного приоритета | 1986 |

|

SU1417000A2 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1988 |

|

SU1589283A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1545219A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

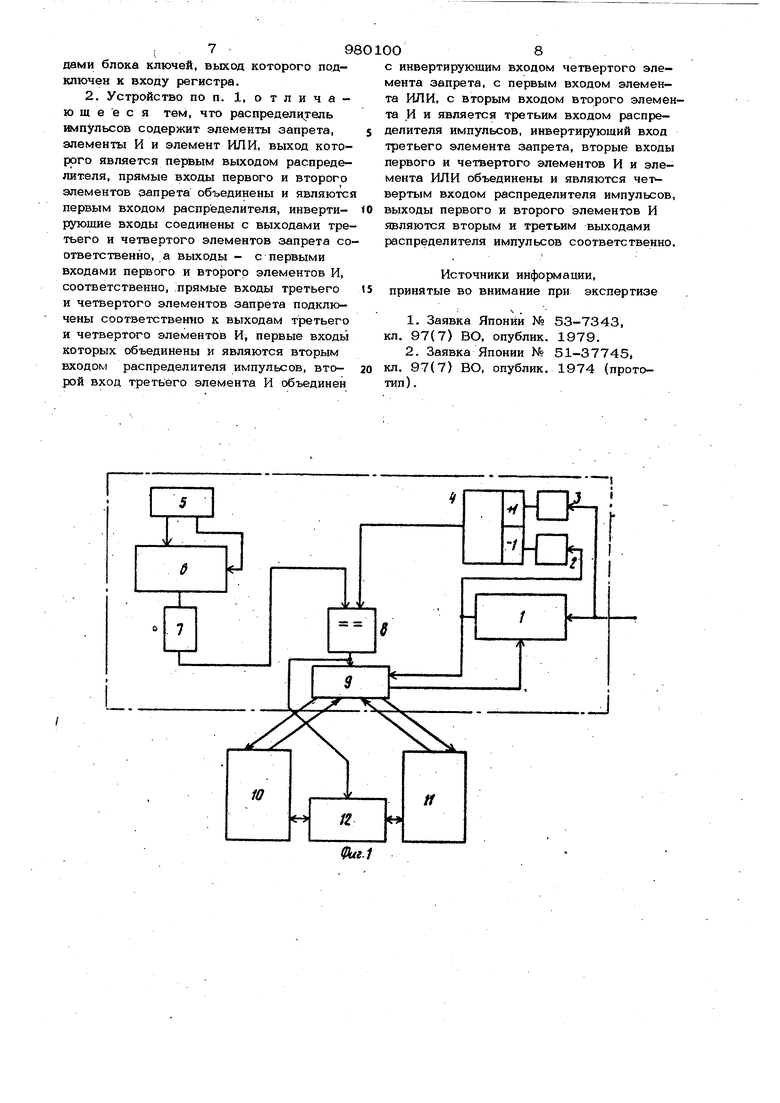

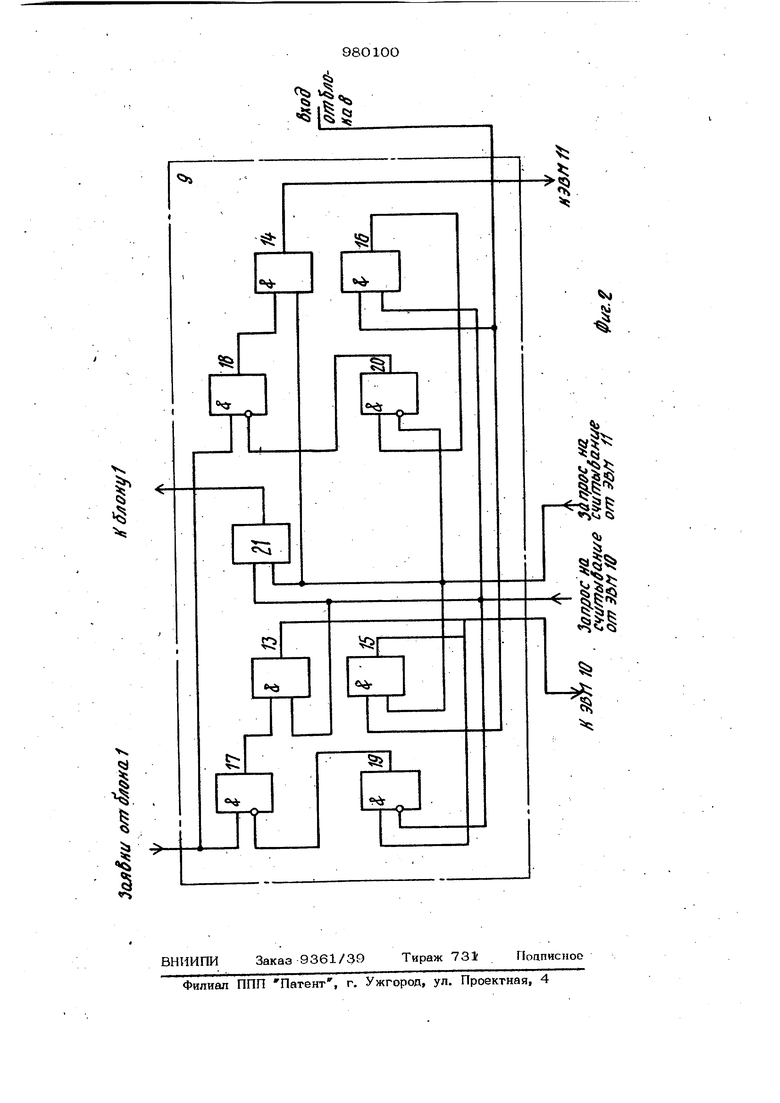

Изобретение относится к вычислительной технике и может быть использовано для ввода информации в вычислительные системы, содержа1дие несколько ЭВМ.. Известно устройство для ввода информации, осуществляющее переключение с однопроцессорного на двухпроцессорный режим работы. В каждом процессоре имеются; устройство для формирования коман ды пуска другого процессора, генератор сигналов индикации главного и дополни.тельного процессора и генератор сигнало ш дикаиии режима работы. По поступающей из работающего процессора команде второй процессор запускается, если он используется в качестве дополнительного процессора и если из второго процессора поступает сигнал о соответствующем режиме работы riT . Это устройство имеет тот недостаток, что его пропускная способность постоянна при любом числе входных заявок. Наиболее близким по технической сущности к предлагаемому является устрой- ство для ввода информации, содержащее буферный регистр, обший для всех вычислительных машин и хранящий : входную информацию, аппаратуру переда- и информации с регистра в вычислительные машины, аппаратуру, которая при запросе из вычислительных машин на считывание информации запрещает ввод информации в буферный регистр и запоминает ее, а при окончании считывания информации всеми вычислительными мащинами с буферного регистра возобновляет передачу.информации в буферный регистр, что обеспечивает все вычислительные мащины одинаковой информаииией 2 . Это устройство имеет ограниченное быстродействие. . Цель изобретения - повышение быстродействия устройства. Указанная цель достигается тем, что в устройство для ввода информации, содержащее блок переключения режимов обработки информации и регистр, введены задатчик кода, блок ключей, блок сравнения, накопитель, первый и второй дешифра торы, счетчик и распределитель импульсов, первый вход которого объединен с входом первого дешифратора и подключен к выходу накопителя, второй вход соединен с выходом блока сравнения и с входом блока переключения режимов обработки -информации, первый выход распределителя соединен с первым входом накопителя, третий и. четвертый входы и второй и третий выходы являются соответствующими входами и выходами устройства, второй вход накопителя и вход второго дешифратора объединены и являются информационным входом устройства, выходы дешифраторов подключены к соответствующим входам счетчика, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к выходу регистра, выходы эадатчика кода соединены с соответствующими входами блока ключей, выход которого подключен к входу регистра. Кроме того, распределитель импульсов содержит элементы запрета, элементы И и элемент ИЛИ, выход которого является первым выходом распределителя импульсов, прямые входы первого и второго эле ментов запрета объединены и являются первым входом распределителя импульсов инвертирующие входы соединены с выходами третьего и четвертого элементов запрета соответственно, а выходы - с первыми входами первого и второго элементов И соответственно, прямые входы третьего и четвертого элементов запрета подключены соответственно к выходамтретьего и четвертого элементов И, первые входы которых объединены и являюtся вторым входом распределителя импуль сов, второй вход третьего элемента И объединен с инвертирующим входом четвертого элемента запрета, с первым входом элемента ИЛИ, с вторым входом вто рого элемента И и является третьим входом распределителя импульсов, инвертирующий вход третьего элемента запрета, вторые входы первого и четвертого элементов И и элемента ИЛИ объединены и являются четверть1М входом распределителя импульсов, выходы первого и второго элементов И являются вторым и третьим выходами распределителя имщ льсов соответственно. На фиг. 1 изображена схема устройства ; на фиг. 2 - схема распределителя ИМПуЛЬзСОВ. Устройство включает накопитель 1, первый и второй дешифраторы 2 и 3, счетчик 4, задатчик 5 кода, блок 6 ключей, регистр 7, блок 8 сравнения, распределитель: 9 импульсов, первую и вторую ЭВМ 10 и 11, блок 12 переключения режимов, обработки информации, первый, второй, третий и четвертый элементы И 13 - 16, первый, второй, третий и четвертый элементы запрета 17 - 2О, элемент ИЛИ 21. Устройство работает следующим образом . С задатчика 5 через блок 6 вводится в регистр 7 число, определяющее критический уровень загрузки накопителя 1. Это число поступает на один из входов блока 8. Предназначенные для обработки заявки поступают в накопитель 1 и на вход дещифратора 3. Дешифратор 3 преобразует служебный признак начала заявок в управляющий сигнал, который поступает в реверсивный счетчик 4 через суммирующий вход, увеличивая тем самым содержащееся в нем число на единицу. Это число, определяющее текущий уровень загрузки накопителя 1, поступает на второй вход блока 8, где сравнивается с числом выставленным регистром 7. Если число, выставленное счетчиком 4 и определяющее текущий уровень загрузки накопителя 1 меньше числа выставленного регистром 7, которое определяет критический уровень загрузки, то блок 8 выдает блоку 12 нулевой управляющий сигнал на параллельную обработку информации двумя ЭВМ и распределителю 9 импульсов на параллельное распределение одних и тех же заявок в обе ЭВМ 10 и 11. ЭВМ 10 и 11 через распределитель 9 импульсов выставляют накопителю 1 требование на считывание, и считывание очередной заявки из накопителя 1 через распределитель 9 импульсов происходит в обе ЭВМ 10 и 11. При считывании заявки дешифратор 2 преобразует служебный признак начала заявки на выходенакопителя 1 в управляющий сигцал, который через вычитающий вход уменьшает содержимое реверсивного счетчика 4 на единицу. Обе ЭВМ 1О и 11 ведут параллельную обработку информации в режиме дублирования, что повышает степень надежности функционирования вычислительного комплекса и досто- верность результатов обработки заявок, поскольку отказ одной ЭВМ не вызывает отказа комплекса в -целом - вторая ЭВМ продолжает нормально функционировать. Режим дублирования имеет место до тех пор, пока количество заявок, хранящихся в блоке накопления заявок, на одну не превысит критического уровня загрузки. Если значение текущего уровня загруз ки (содержимое реверсивного счетчика 4) превышает значение критического уровня загрузки накопителя 1 (содержимое регистра 7), блок 8 снимает с блока 12 и распределителя 9 импульсов сигнал парал лельной обработки информа1ши, в результате чего ЭВМ переходят на авторо(ный режим обработки заявок. Распределитель 9импульсов распределяет заявки, считываемые из накопителя 1, в канщую ЭВМ по мере поступления запросов на автоном ную одномащинную обработку. Каждая ЭВМ обрабатывает свою заявку. Автономный режим работы комплекса имеет место до тех пор, пока текущий уровень загрузки, определяемый количест вом хранящихся в накопителе 1 числа заявок, не станет меньще критического, после чего комплекс опять переходит в режим дублирования. Распределитель 9 импульсов работает следующим образом. При нулевом сигнале на управляющем входе от блока 8 запросы на считывание заявок из накопителя поступают от ЭВМ 10и через элемент ИЛИ 21 в-накопитель 1 и на входы элементов И 13 и 14 Считывание заявок из накопителя 1 проис- ходит через открытые элементы 17 и 18 и элементы И 13 и 14 одновременно. Таким образом, одна и та же заявка поступает на вход ЭВМ 10 и 11, которые работают в этом случае в режиме дублирования. При единичном сигнале на управляюще входе этот сигнал поступает на входы элементов И 15 и 16. Пусть какая-либо из ЭВМ, например 10, выставит запрос на считывание, который через элемент ИЛИ 21 пойдет к блоку накопления заявок. Этот же сигнал запроса через элемент И 16 и элемент 20 поступает на управляющий вход элемента 18, блокируя считывание заявки по запросу от ЭВМ 11 и одновременно поступает на вход элемен та И 13 и элемента 19, разрешая ЭВМ 10 считывание информации из накопителя 1 через открытый элемент 17 и элемент И 13. Во время считывания информации в ЭВМ 1О запрос от ЭВМ 11 блокируется от возможных воздействий на элемент 17 элементом 19. После считывания информации в ЭВМ 10 запрос снимается, следовательно, снимается блокировка с эле ментов запрета 18 и 19 и блок готов к удовлетворению следующего запроса от любой из ЭВМ. Точно так же удовлетворяется запрос ЭВМ 11. В этом случае блокируется вход на ЭВМ 10. Таким образом, происходит распределение заявок между ЭВМ в автономном режиме, когда машины работают независимо друг от друга. Предлагаемое устройство обеспечивает гибкое изменение режима работы вычислительного комплекса при изменении потока входньрс заявок: при малой загрузке ЭВМ работают параллельно, в режиме дублирования, обрабатывая одновременно одни и те же заявки,. что обеспечивает высокую надежность функционирования вычислительного комплекса,. при увеличении загрузки выше критического значения. ЭВМ работают в автономном режиме, обрабатывая каждая свою заявку и не дублируя одна другую, что увеличивает быстродействие устройства при увеличении интенсивности поступления заявок. Фор м у л а изобретения Устройство для ввода информации, содержащее блок переключения релшмов обработки информации и регистр, о т л и чающее ся тем, что, с целью повышения быстродействия устройства, в него введены задатчик кода, блок ключей, блок сравнения, накопитель, первый и второй дешифраторы, счетчик и распределитель импульсов, первый вход которого объединен с входом первого дешифратора и подключен к выходу накопителя, второй вход соединен с выходом блока сравнения и с входом блока переключения режимов обработки информации, первый выход распределителя импульсов соединен с первым Ьходом накопителя, третий и четвертый входы и второй и третий выходы являются соответствующими входами и выходами устройства, второй вход накопителя и вход второго дешифратора объединены и являются информационным входом устройства, выходы дешифраторов подключены к соответствующим входам счетчика, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к выходу регистра, выходы задатчика кода соединены с соответствующими входами блока ключей, выход которого подключен к входу регистра.

с инвертирующим входом четвертого элемента запрета, с первым входом элемента ИЛИ, с вторым входом второго элемента И и является третьим входом распределителя импульсов, инвертирующий вход третьего элемента запрета, вторые входы первого и четвертого элементов И и элемента ИЛИ объединены и являются четвертым входом распределителя импульсов, выходы первого и второго элементов И являются вторым и третьим выходами распределителя импульсов соответственно.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-12-07—Публикация

1981-06-11—Подача