Изобретение относится к вычислительной технике и может быть использовано для построения многомашинных вычислительных систем.

Целью изобретения является повышение достоверности информации, передаваемой по общей магистрали и принимаемой одним из устройств системы, за счет обеспечения автоматической обратной передачи принятого устройством-приемником пакета данных устройству-передатчику .

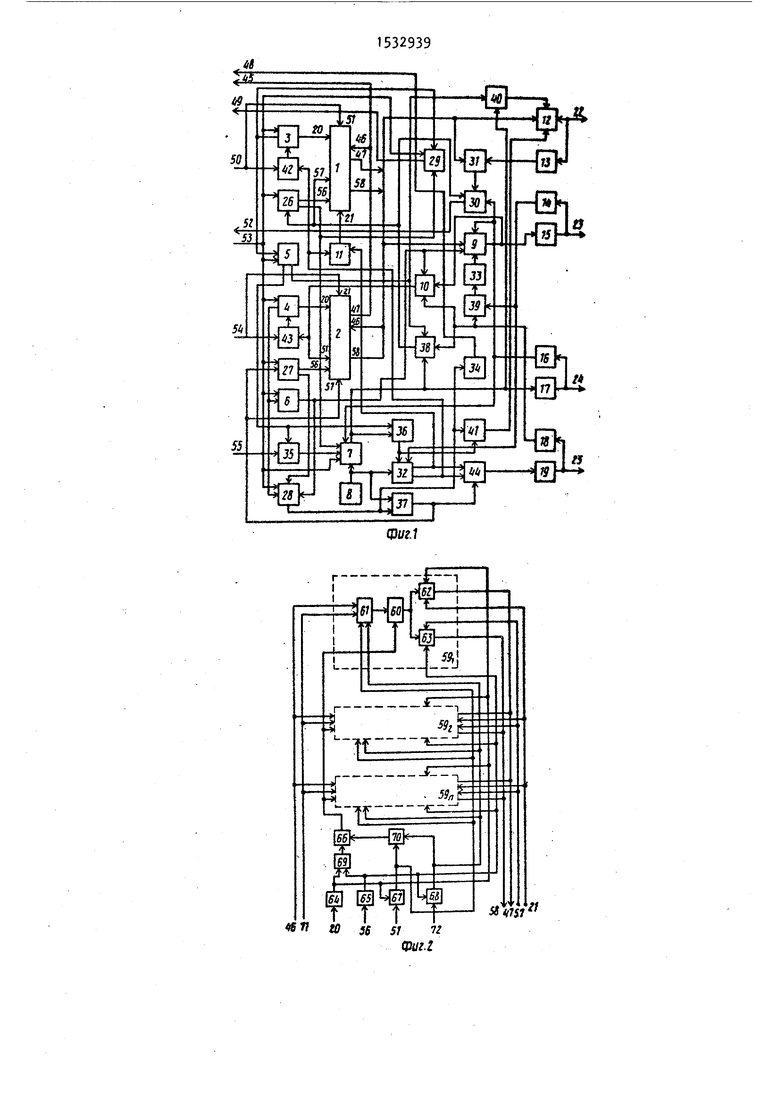

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - пример реализации блоков буферной памяти; на фиг.З - структура узла захвата магистрали; на фиг.4 - структурная схема дешифратора адреса; на фиг.5 - схема объединения ЭВМ в многомашинную систему с использованием данного устройства.

Устройство (фиг.1) содержит блоки

1и 2 буферной памяти, счетчики 3 и 4, триггеры 5 и 6, узел 7 захвата магистрали, генератор 8 импульсов, дешифратор 9 адреса, элемент И 10, элемент ИЛИ 11, магистральные усилители 12-19, адресные входы 20 блоков 1 и

2буферной памяти, входы 21 чтения блоков 1 и 2 буферной памяти, шину

22 информации, шину 23 подтверждения, шину 24 занятости, шину 25 синхронизации, счетчики 26 и 27, триггеры 28- 30, блок 31 сравнения, распределитель 32 импульсов, одновибраторы 33 и 34, элементы И 35-40, элементы ИЛИ 41-44, линию 45 данных, входы 46 и выходы 47 блоков 1 и 2 буферной памяти, линию 48 прерывания, линию 49 требования Записи, линию 50 записи, входы 51 записи блоков 1 и 2 буферной памяти, линию 52 прерывания, линию 53

i -

СО

начальной установки, линию 5 чтения, линию 55 требования передачи, адресные входы 56 блоков 1 и 2 буферной памяти, входы 57 чтения блоков 1 и 2 буферной памяти, выходы 58 блоков 1 и 2 буферной памяти.

Блоки 1 и 2 буферной памяти (фиг,2) содержат узлы 59 памяти, каждый из которых включает регистр 60, мультиплексор 61 и группы элементов И 62 и 63 и схему управления, состоящую из дешифраторов и 65, группы элементов И 66-68 и группы элементов ИЛИ 69 и 70, входы 71 и 72. Узел 7 захвата магистрали (фиг.З) содержит счетчик 73 регистр 74 и триггер 75. Дешифратор 9 адреса (фиг.4) содержит узел 76 сравнения, регистр 77, триг

10

15

са на линию 53. По этому импульсу счетчики 3, 4, 26 и 27 триггеры 5 6, 28 и 29 сбрасывают в ноль, на ходе узла 7 магистрали захвата по ляется нулевой потенциал, который инициирует появление нулевого уро на выходах триггеров 30 и дешифра ров 9 всех устройств 80 системы. линии 49 появляется потенциал лог ческой единицы.

В устройствах 80 блоки 1 буфер памяти доступны с линии 45 только записи, а блоки 2 буферной памяти только по чтению. Запись данных в блок 1 сопровождается сигналом на нии 50, а чтение из блока 2 - сиг лом на линии . Наличие единицы линии 49 означает, что блок 2

78 и элемент И 79. На фиг.5 изоб- 2Q свободен. При записи информации в

80 сопряжения и

30

35

гер

ражены устройства

ЭВМ 81.

Устройство работает следующим образом.

Обмен информацией между парой ЭВМ 25 81i (i 1-n) и 8lj (j 1-n) системы с помощью устройств 801 и 80j (фиг.5) осуществляется через общую магистраль, состоящую из следующих шин: шины 22 информации; шины 23 подтверждения; шины 2k занятости; шины 25 синхронизации.

Обмен включает в себя следующие j этапы:проверка ЭВМ 81i инициатором обмена занятости своего устройства 801 и при необходимости ожидание его освобождения; занесе ме пакета информации по линии 45 из ОЗУ ЭВМ 81 в блок 1 буферной памяти устройства 801; захват устройством 801 общей магистрали; проверка занятости блока 2 буферной памяти устройства 80j и в случае необходимости ожидание его освобождения; передача пакета информации из блока 1 буферной памяти устройства 801 в блок 2 буферной памяти устройства 80j; обратная передача пакета из блока 2 буферной памяти устройства %80j через общую магистраль и срав- .нение передаваемого с содержимым блока 1 буферной памяти устройства 801; в случае несовпадения данных перевод ЭВМ 81i в режим прерывания по ошибке в передаче; чтение информации из блока 2 буферной памяти устройства 80j в ОЗУ ЭВМ 8lj no прерыванию. 55 . Начало работы системы осуществляется с инициализации устройств 80, которая производится подачейимпуль40

45

50

блок 1 по заднему фронту импульса на линии 50 значение счетчика 3 у личивается на единицу. Значение на выходах этого счетчика определяет рес информационного слова, записы мого в блок 1„

i

После переполнения счетчика 3 его выходе переполнения появляется импульс, по фронту которого счетн триггер 5 и триггер 29 устанавлива ся в единицу, в результате чего н линиии 49 появляется нулевой уров свидетельствующий о том, что блок устройства 801 занят, на входах эл ментов И 38 и 40 появляются нулевы потенциалы. ЭВМ 81is записав паке в блок 1, устанавливает требовани передачи единичным уровнем на лин 55, тем самым единичный потенциал выхода элемента И 35 подается на вход запроса узла 7. После разреш ния всевозможных конфликтов на вых узла 7 появляется единичный потен свидетельствующий о захвате устрой вом 801 общей магистрали. Этот пот циал поступает на шину 24 занятост а в устройстве 801 - на входы элем тов И 36, 38, 40. На выходе элеме И 36 появляется потенциал логическ единицы, который разрешает прохожд ние синхроимпульсов с генератора 8 на первый выход распределителя 32 пульсов. Синхроимпульсы с выхода р пределителя 32 поступают на вход 2 чтения блока 1 и на шину 25 синхр зации. По этим импульсам происходи чтение первого слова из блока 1 в устройстве 801. Содержимое этого с ва определяет адрес устройства 80j

са на линию 53. По этому импульсу счетчики 3, 4, 26 и 27 триггеры 5, 6, 28 и 29 сбрасывают в ноль, на выходе узла 7 магистрали захвата появляется нулевой потенциал, который . инициирует появление нулевого уровня на выходах триггеров 30 и дешифраторов 9 всех устройств 80 системы. На линии 49 появляется потенциал логической единицы.

В устройствах 80 блоки 1 буферной памяти доступны с линии 45 только по записи, а блоки 2 буферной памяти - только по чтению. Запись данных в . блок 1 сопровождается сигналом на линии 50, а чтение из блока 2 - сигналом на линии . Наличие единицы на линии 49 означает, что блок 2

Q свободен. При записи информации в

0

5

5

5

0

5

0

блок 1 по заднему фронту импульса на линии 50 значение счетчика 3 увеличивается на единицу. Значение на выходах этого счетчика определяет адрес информационного слова, записываемого в блок 1„

i

После переполнения счетчика 3 на его выходе переполнения появляется импульс, по фронту которого счетный триггер 5 и триггер 29 устанавливаются в единицу, в результате чего на линиии 49 появляется нулевой уровень, свидетельствующий о том, что блок 1 устройства 801 занят, на входах элементов И 38 и 40 появляются нулевые потенциалы. ЭВМ 81is записав пакет в блок 1, устанавливает требование передачи единичным уровнем на линию 55, тем самым единичный потенциал с выхода элемента И 35 подается на вход запроса узла 7. После разрешения всевозможных конфликтов на выходе узла 7 появляется единичный потенциал, свидетельствующий о захвате устройством 801 общей магистрали. Этот потенциал поступает на шину 24 занятости, а в устройстве 801 - на входы элементов И 36, 38, 40. На выходе элемента И 36 появляется потенциал логической единицы, который разрешает прохождение синхроимпульсов с генератора 8 на первый выход распределителя 32 импульсов. Синхроимпульсы с выхода распределителя 32 поступают на вход 21 чтения блока 1 и на шину 25 синхронизации. По этим импульсам происходит чтение первого слова из блока 1 в , устройстве 801. Содержимое этого слова определяет адрес устройства 80j

на общей магистрали. Адресное слово поступает на шину 22 через магист - ральный усилитель 12, открытый на передачу уровнем единицы на выходе элемента ИЛИ 41.

В устройстве 80j адресное слово че через магистральный усилитель 12 по- | ступает на входы дешифратора 9 адре- са. Синхронизация работы дешифратора осуществляется импульсами, поступающими на его вход синхронизации с шины 25. Если блок 2 в устройстве 80j свободен (о чем свидетельствует наличие логической единицы на нулевом выходе триггера 6),на выходе дешифратора 9 появляется потенциал единицы, который поступает на шину 23 и в устройство 801,.переключает прохождение импульсов с входа распределителя 32 импульсов на его второй выход. Синхроимпульсы, поступающие с второго выхода распределителя 32,инициируют чтение всего пакета из блока 1. Чтение слова сопровождается импульсом на входе 21 блока 1 по адресу, задаваемому на его входе 20. По заданному фронту импульса происходит увеличение содержимого счетчика 3 на единицу. Информация с выходов 47 блока 1 устройства 801 через усилитель 12 поступает на шину 22. После переполнения счетчика 3. на его выходе переполнения появляется импульс, который обнуляет триггер 5, тем самым инициируя появление уровня логического нуля на выходах элементов И 35 и 36, Уровень нуля на выходе элемента И 36 закрывает прохождение синхроимпульсов через распределитель 32. Одновременно с этим уровнем логической единицы с нулевого выхода триггера 5 происходит появление единичного уровня на выходе элемента И 40, который в устройстве 801 закрывает усилитель 12 для передачи в оба направления.

В устройстве 80j информация с шины 22 поступает через усилитель 12 на входы 46 блока 2. Синхронизация осуществляется импульсами на шине 25, которые через усилитель 18 и элемент И 10 (элемент И 39 закрыт уровнем нуля на выходе магистрального усилителя 14) поступают на вход 51 записи блока 2 и через элемент ИЛИ 43 на счетный вход счетчика 4. По заднему фронту импульсов происходит наращивание счетчика 4, значение которого задает адрес записываемой информации на

о

5

0

5

0

5

0

5

входах адреса 20 блока 2 устройства 80j. После переполнения счетчика 4 на выходе его переполнения появляется импульс, который устанавливает в единицу триггеры 6 и 28. Уровень нуля на нулевом выходе триггера 6 закрывает элемент И 10, а уровень еди ницы на выходе триггера 28 разрешает прохождение импульсов в устройстве 80j с генератора 8 через элемент И 37. Этим же уровнем усилитель 12 переключается на передачу. Синхросигналы с выхода элемента И 37 поступают на вход 57 чтения блока 2 и на синхровход счетчика 27.

По заднему фронту импульса происходит увеличение его значения, которое определяет адрес информации в блоке 2. Таким образом происходит выдача информации из блока 58 на шину 22. После выдачи всего пакета на выходе переполнения счетчика 27 появляется импульс, по которому обнуляется триггер 28, тем самым закрывая элемент И 37. По перепаду в ноль на выходе 28 на выходе одновибратора 34 появляется импульс прерывания, который передается по линии 48 и переводит ЭВМ 81j в режим чтения пакета. Импульсы чтения поступают на вход 21 чтения блока 2 устройства 80j. По заднему фронту импульса увеличивается на единицу значение счетчика 4. Данные из блока 2 устройства 80j поступают в ЭВМ 8lj через линию 45. После чтения всего пакета на выходе переполнения счетчика 4 появляется импульс, по которому обнуляется счетный триггер 6. Значение триггера 28 не изменяется ввиду присутствия на его D-входе уровня логического нуля.

В устройстве 801 информация поступает с шины 22 через магистральный усилитель 13 на входы блока 31 сравнения. Импульсы синхронизации с шины 25 через элемент И 38 поступают на синхровход счетчика 26 и вход 57 чтения блока 1. По импульсу происходит чтение слова из блока 1 на выходы 58. По заднему фронту импульса увеличивается на единицу значение счетчика 26, определяющего адрес считваемой информации, которая поступает на другие информационные входы блока 31 сравнения. При первом несовпадении информации, передаваемой по шине 22 и считы- , ваемой из блока 1, на выходе блока 31 сравнения появляется единичный потенциал. По заднему фронту импульса синхронизации триггер 30 переключается в единицу, выдавая в ЗВМ 81i сигнал прерывания по линии 52, свидетельствующий об ошибке в передаче После переполнения счетчика 26 на его выходе переполнения появляется импульс, который обнуляет триггер 29 и сбрасывает узел 7, в результате чего на линии kS появляется единичный потенциал, на шинах 23 и 2k появляется потенциал логического нуля, триггер 30 сбрасывается в ноль. ЭВМ 81i, получив прерывание по линии 52, может повторить передачу пакета, проделав заново описанный цикл.

Блоки 1 и 2 буферной памяти (фиг.2) работают следующим образом.

Емкость блоков 1 и 2 задается количеством узлов 59, а разрядность - разрядностью регистров 60.Адресация узлов осуществляется со входов 20 и 156. После выставления адреса на соот- 25 ветствующем выходе дешифратора 6k или 65 появляется потенциал логической единицы, который через группу элементов ИЛИ 69 поступает на соответствуюЗапросы на захват общей магистрали поступают с входа запроса на D-вход триггера 75. Если на ширине 2k находится потенциал логического нуля, то при поступлении импульсов на вход синхронизации узла 7 происходит последовательное наращивание значения счетчика 73. Начальное значение счетчика 73 задается значением на выходах регистра 7k, представляющего соответствующий приоритету устройства 801 набор логических нулей и единиц. Чем выше приоритет устройства, тем большее двоичное значение находится на выходах регистра 7k, Как только возникает переполнение счетчика 73, на его выходе переполнения возникает импульс, поступающий на С-вход триггера 75, переводя его в единичное состояние. Триггер 75 выставляет на выход узла 7 единичный уровень, который через шину 2k поступает на входы запрета всех узлов 7 устройств 80 системы, тем

самым производя начальную установку счетчиков 73 и блокируя их работу. Сброс триггера 75 производится подачей сигнала на входы установки или освобождения. Таким образом, такая

вход группы элементов И 66. После 30 реализация узла 7 позволяет осущестщии

прихода импульса записи на вхоц 51 или 72 на соответствующем выходе (в зависимости от адреса) группы элемен- JTOB ИЛИ 70 появляется импульс, который поступает через соответствующий элемент группы элементов И 66 на вход синхронизации регис а 60 одного из каналов 59 в соответствии с адресаци- ей. Причем.при поступлении импульса записи на вход 51 запись осуществляется со входов 6 по адресу, задаваемому на входах 20, а при поступлении импульса записи на вход 72 запись ин формации происходит с входов 71 по адресу, задаваемому на входах 56. Чтение информации осуществляется подачей импульса чтения на вход 21 или 57. При этом при поступлении импульса чтения на вход 21 информация поступает на выходы k7 через группу .. элементов И 62 соответствующего адресации с входов 20 узла 59, а при поступлении импульса чтения на вход 57 информация поступает на выходы 58 через группу элементов И 63 соответствующего адресации с входов 56 узла 59.

Узел 7,(фиг.З) работает следующим образом,

влять захват общей магистрали только одному устройству 801.

Дешифратор 9 адреса (фигЛ) обеспечивает, адресацию устройств 80 с

35 общей магистрали. Код адреса устройства 80j задается регистром 77, представляющим набор нулей и единиц в зависимости от адреса устройства 80j. Работа узла 76 сравнения синхронизи40 руется импульсами, поступающими со входа синхронизации дешифратора 9 При совпадении адреса устройства 80j, задаваемого регистром 77, с информацией на входах дешифратора 9 на вы45 ходе узла 76 сравнения появляются импульсы, которые поступают на вход ч элемента И 79. Если блок 2 адресуемого устройства 80j свободен, то импульсы с выхода элемента И 79 посту50 лают на С-вход триггера 78(D-вход в состоянии- логической единицы), переключая его в единичное состояние. Потенциал с выхода дешифратора адреса поступает на шину 23 подтаержде-5 ния. С)брос триггера 78 осуществляется подачей уровня логического нуля на вход запрета дешифратора адреса, который соединен с входом сброса триггера 78,

в

)

10

- 25 и 532939.8

Запросы на захват общей магистрали поступают с входа запроса на D-вход триггера 75. Если на ширине 2k находится потенциал логического нуля, то при поступлении импульсов на вход синхронизации узла 7 происходит последовательное наращивание значения счетчика 73. Начальное значение счетчика 73 задается значением на выходах регистра 7k, представляющего соответствующий приоритету устройства 801 набор логических нулей и единиц. Чем выше приоритет устройства, тем большее двоичное значение находится на выходах регистра 7k, Как только возникает переполнение счетчика 73, на его выходе переполнения возникает импульс, поступающий на С-вход триггера 75, переводя его в единичное состояние. Триггер 75 выставляет на выход узла 7 единичный уровень, который через шину 2k поступает на входы запрета всех узлов 7 устройств 80 системы, тем

самым производя начальную установку счетчиков 73 и блокируя их работу. Сброс триггера 75 производится подачей сигнала на входы установки или освобождения. Таким образом, такая

20

реализация узла 7 позволяет осуществлять захват общей магистрали только одному устройству 801.

Дешифратор 9 адреса (фигЛ) обеспечивает, адресацию устройств 80 с

общей магистрали. Код адреса устройства 80j задается регистром 77, представляющим набор нулей и единиц в зависимости от адреса устройства 80j. Работа узла 76 сравнения синхронизируется импульсами, поступающими со входа синхронизации дешифратора 9 При совпадении адреса устройства 80j, задаваемого регистром 77, с информацией на входах дешифратора 9 на выходе узла 76 сравнения появляются импульсы, которые поступают на вход ч элемента И 79. Если блок 2 адресуемого устройства 80j свободен, то импульсы с выхода элемента И 79 постулают на С-вход триггера 78(D-вход в состоянии- логической единицы), переключая его в единичное состояние. Потенциал с выхода дешифратора адреса поступает на шину 23 подтаерждения. С)брос триггера 78 осуществляется подачей уровня логического нуля на вход запрета дешифратора адреса, который соединен с входом сброса триггера 78,

Формула изобретения

1. Устройство для сопряжения ЭВМ с общей магистралью, содержащее два блока буферной памяти, два счетчика, три триггера, узел захвата магистрали, генератор импульсов, дешифратор адреса, восемь магистральных усилителей, первый элемент И, первый элемент ИЛИ, два одновибратора, причем первый информационный вход-выход первого магистрального усилителя соединен с информационным входом второго магистрального усилителя и является входом-выходом устройства для подключения к информационной шине общей магистрали, информационный вход/ третьего магистрального усилителя соединен с информационным выходом четвертого магистрального усилителя и является входом-выходом устройства для подключения к шине подтверждения общей магистрали, информационный вход пятого магистрального усилителя соединен с информационным выходом шестого магистрального усилителя и является входом-выходом устройства для подключения к шине занятости общей магистрали, информацион-

ный вход седьмого магистрального усилителя соединен с информационным выходом восьмого магистрального усилителя и является входом-выходом устройства для подключения к шине синхронизации общей магистрали, при этом первые адресные входы первого и второго блоков буферной памяти соединены с выходами соответственно первого и второго счетчиков, выходы переполнения которых соединены со счетными входами соответственно первого и

второго триггеров, выход второго триггера соединен суправляющим входом дешифратора адреса и с первым входом первого элемента И, второй вход которого i

соединен с выходами дешифратора адреса

и с информационным входом четвертого магистрального усилителя, выход генератора импульсов соединен с синхро-. входом узла захвата магистрали, отличающееся тем, что, с целью повышения достоверности передаваемой информации за счет обеспечения автоматической обратной передачи принятого устройством-передатчиком пакета данных устройству-передатчику, в устройство введены два счетчика,

0

.5

0

5

0

5

0

5

0

два триггера, четыре элемента ИЛИ, шесть элементов И, блок сравнения, распределитель импульсов, причем выходы первого одновибратора и третьего триггера являются выходами устройства для подключения соответственно к первому и второму входам прерывания ЭВМ, информационный вход первого блока буферной памяти соединен с первым информационным выходом второго блока буферной памяти и является входом-выходом устройства для подключения к информационному входу-выходу ЭВМ, выход четвертого триггера и первый вход второго элемента И являются, ся выходом и входом устройства для подключения соответственно к входу требования записи и к выходу требования передачи ЭВМ, вход записи первого блока буферной памяти соединен с первым входом первого элемента ИЛИ /и является входом устройства для подключения к выходу записи ЭВМ, первый вход чтения второго блока буферной памяти соединен с первым входом второго элемента ИЛИ и является входом устройства для подключения к выходу чтения ЭВМ, установочный вход первого счетчика соединен с установочными входами второго, третьего, четвертого счетчиков, узла захвата магистрали, с нулевыми входами первого, второго триггеров, с первыми нулевыми входами четвертого, пятого триггеров и является входом устройства для подключения к установочному выходу ЭВМ, при этом выход генератора импульсов соединен с синхровходом распределителя импульсов и с первым входом третьего элемента И, второй вход которого соединен с входом запуска первого одновибратора, с первым входом третьего элемента ИЛИ, и с выходом пятого триггера, второй нулевой вход которого соединен с выходом) переполнения четвертого счетчика, выход которого соединен с вторым адресным входом второго блока буферной памяти, вход записи которого соединен с выходом первого элемента И и с вторым входом второго элемента ИЛИ, выход которого соединен со счетным входом второго счетчика,счетный вход первого счетчика соединен с выходом первого элемента ИЛИ, второй вход которого соединен с первыми входами четвертого и пятого элементов ИЛИ и с первым синхровыходом распределите1

ля импульсов, второй синхровыход ко- , торого соединен с вторыми входами четвертого и пятого элементов ИЛИ, .выходы которых соединены соответственно с первым входом чтения первого блока буферной памяти и с информационным входом восьмого магистрального усилителя, второй информационный .вход-выход первого магистрально- го усилителя, соединен с первым, вторым информационными выходами первого блока буферной памяти, с вторым информационным выходом и информационным входом второго блока буферной памяти, с информационным входом дешифратора адреса, с первым информационным входом блока сравнения, втЈ рой информационный вход и выход которого соединены соответственно с информационным выходом второго магистрального усилителя и с информационны входом третьего триггера, выход / третьего счетчика соединен с вторым адресным входом первого блока буферной памяти, второй вход чтения которого соединен со счетным входом третьего счетчика, с выходом четвертого элемента И и с синхровходом третьего триггера, нулевой вход кото рого соединен с разрешающим входом дешифратора адреса, с информационным выходом пятого магистрального усилителя и с входом запрета узла захвата магистрали, выход которого соединен с первыми входами пятого, шестого элементов И-, с информационным входом шестого магистрального усилителя и с первым входом четвертого элемента И, второй вход которого соединен с

третьим входом первого элемента И, с информационным выходом седьмого магистрального усилителя и с первым входом седьмого элемента И, выход которого соединен с входами запуска -, второго одновибратора, выход которого соединен с синхровходом дешифратора адреса, информационный выход третьего .магистрального усилителя соединен с

зд

293912

вторым входом седьмого элемента И,

5

0

5

5

0

5

управляющим входом распределителя импульсов, разрешающий вход которого соединен с выходом пятого элемента И, и с вторым входом, третьего элемента ИЛИ, выход которого соединён с входом режима работы первого магистрального усилителя, разрешающий вход которого соединен с выходом шестого элемента И, второй вход которого соединен с третьим входом четвертого элемента И и с нулевым выходом первого триггера, единичный выход которого соединен с вторым входом пятого элемента И и с вторым входом второго элемента И, выход которого соединен с входом запроса.узла захвата магистрали, вход освобождения которого соединен с выходом переполнения третьего счетчика и с вторым4 нулевым входом четвертого триггера, счетный вход которого соединен с выходом переполнения первого счетчика, выход третьего элемента И соединён с третьим входом пятого элемента ИЛИ, со счетным входом четвертого счетчика и с вторым входом чтения второго блока буферной памяти, выход второго триггера соединен с информационным входом пятого триггера, синхровход которого соединен с выходом переполнения второго счетчика.

2, Устройство по п.1, о т л и - чающееся тем, что узел захвата магистрали содержит регистр, счетчик и триггер, причем счетный вход счетчика является синхровходом узла, установочный вход счетчика, первый , второй нулевые входы, информационный вход и выход триггера являются соответственно входом запрета, входом освобождения, установочным входом, входом запроса и выходом узла, при этом в узле захвата магистра - ли выход регистра соединен с информационным входом счетчика, выход переполнения которого соединен с синхровходом триггера.

//

1гпф

2L IS 3S Ot U

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

| Устройство для сопряжения ЭВМ | 1987 |

|

SU1460724A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с магистралью | 1984 |

|

SU1246107A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1986 |

|

SU1354199A1 |

| Устройство для сопряжения электронных вычислительных машин | 1987 |

|

SU1443001A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1987 |

|

SU1439612A1 |

| Устройство для управления обменом информацией | 1987 |

|

SU1513460A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения многомашинных вычислительных систем. Целью изобретения является повышение достоверности информации, передаваемой по общей магистрали и принимаемой одним из устройств системы, за счет обеспечения автоматической обратной передачи принятого устройством-приемником пакета данных устройству-передатчику. Устройство содержит два блока буферной памяти, восемь магистральных усилителей, узел захвата магистрали, генератор импульсов, распределитель импульсов, дешифратор адреса, пять триггеров, четыре счетчика, семь элементов И, пять элементов ИЛИ, два одновибратора, блок сравнения. 1 з.п. ф-лы, 5 ил.

.„iUr

°K

П.

-rrtit n

6Ј62«l

t

Фиг. 5

Редактор Т.Парфенова

Составитель С.Пестмал Техред М.Ходанич

Заказ 8101/54

Тираж 668

ВШИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственнотиэдательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Т

Фм.З

Фив. Ч

Корректор О.Ципле

Подписное

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

| Насос | 1917 |

|

SU13A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1989-12-30—Публикация

1988-02-18—Подача