Изобретение относится к вычислительной технике и может быть использовано для построения многомашинных вычислительных систем.

Целью изобретения является повышение быстродействия.

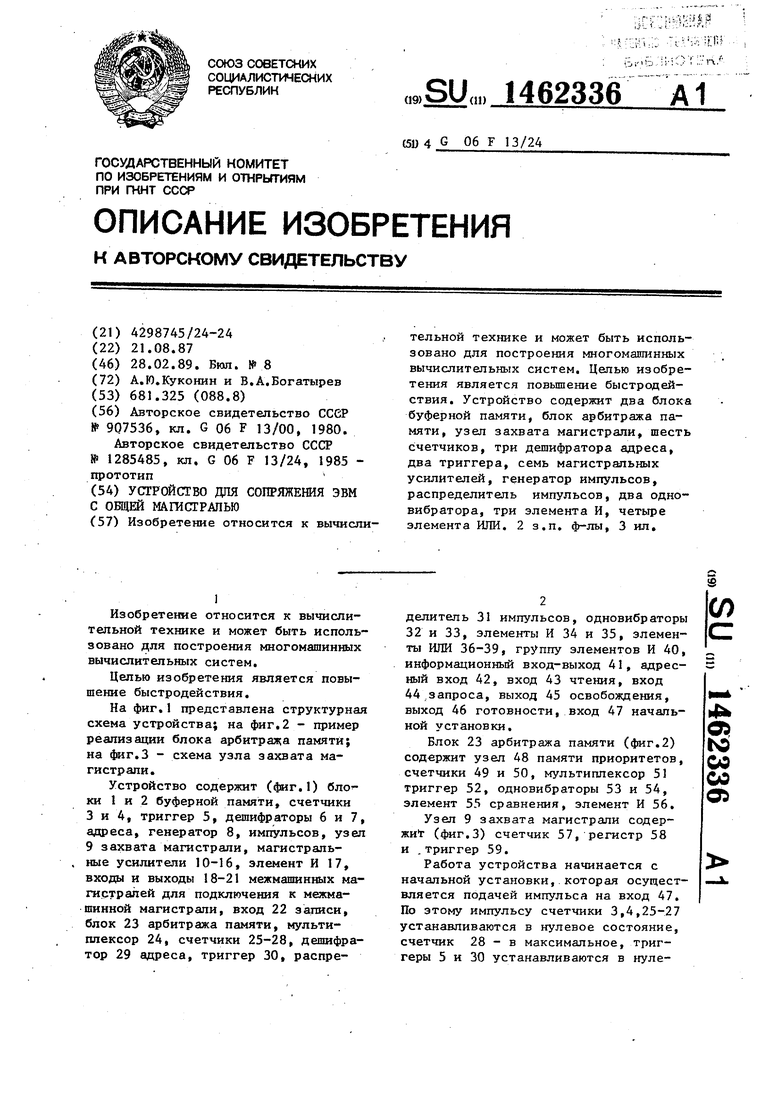

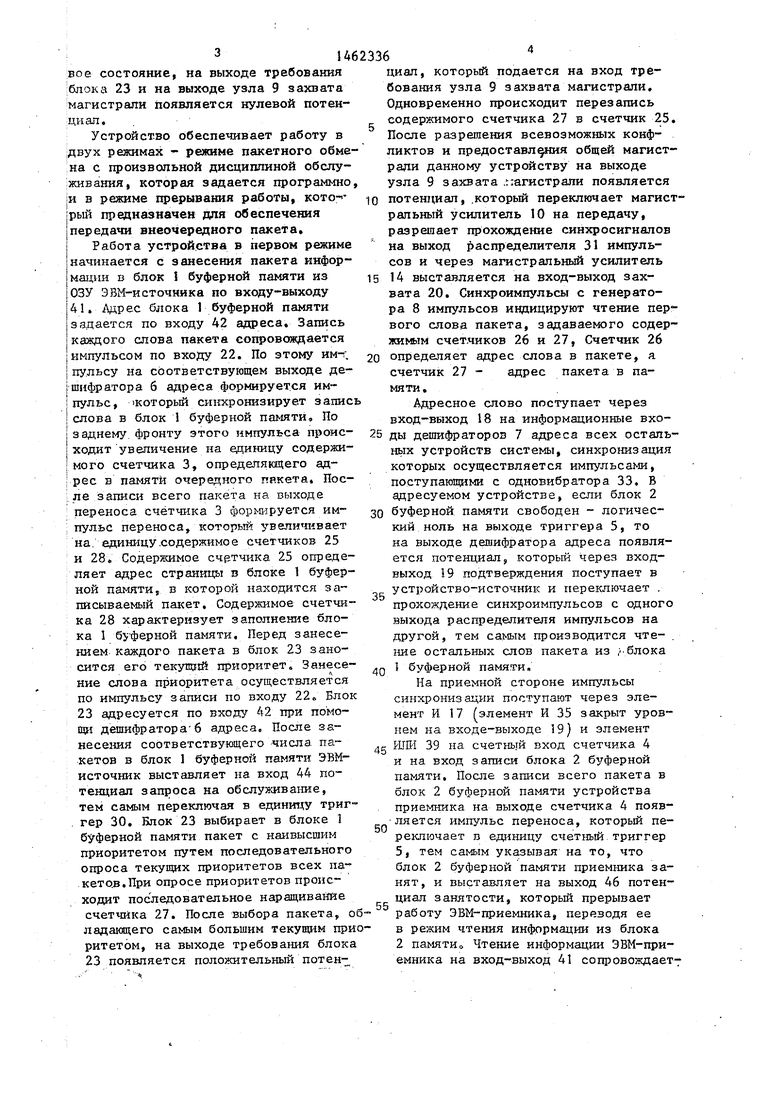

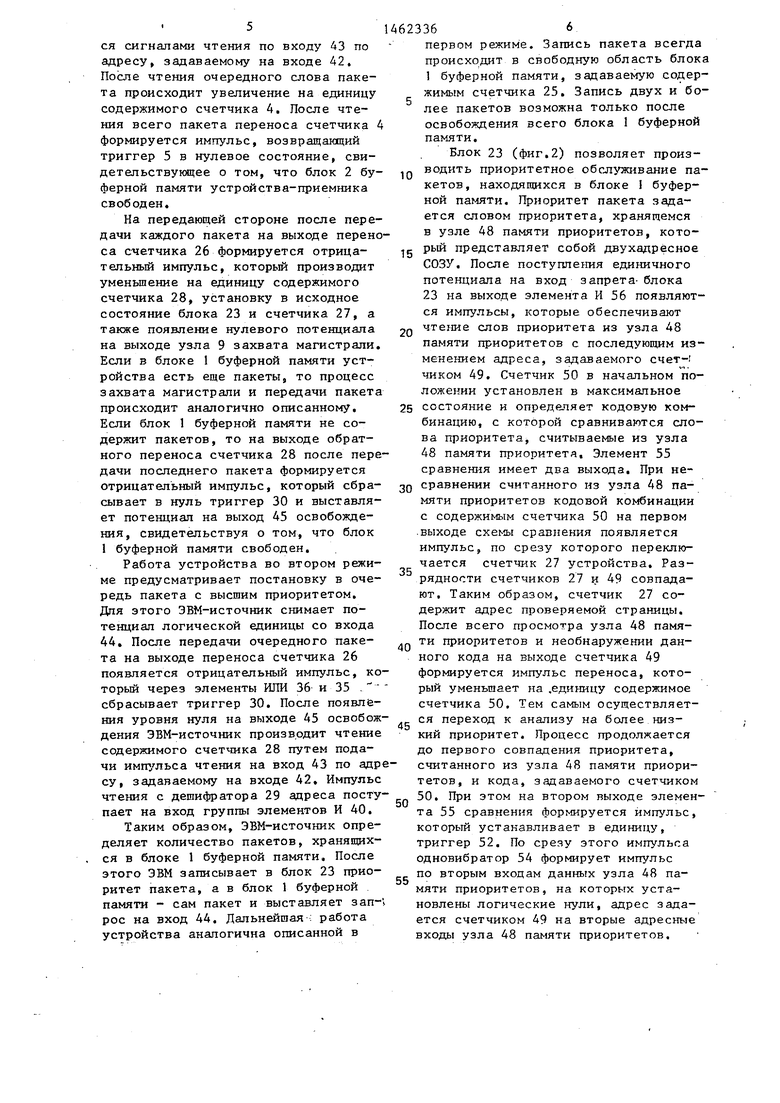

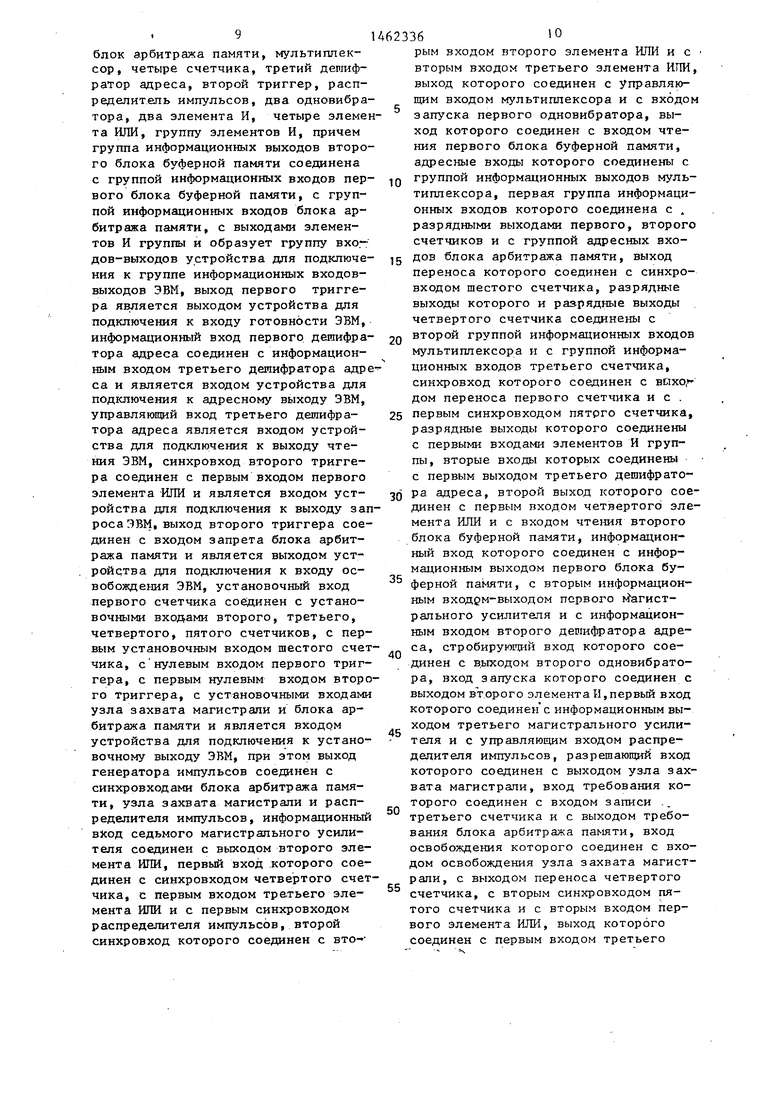

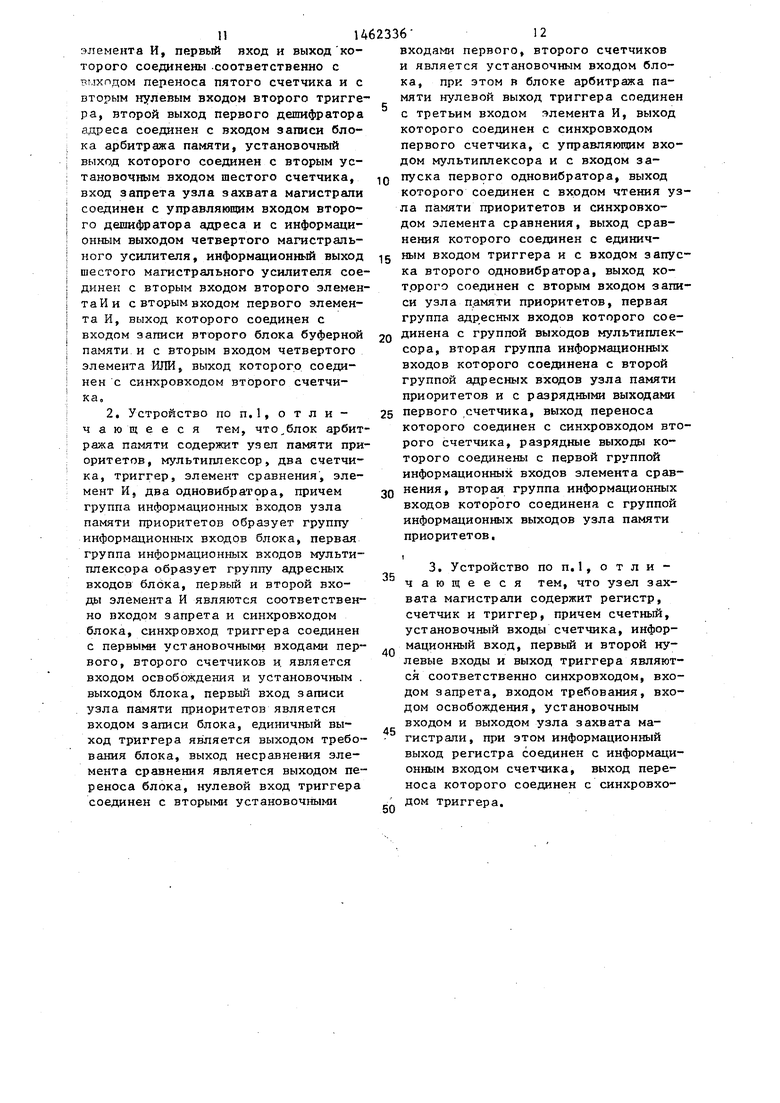

На фиг.1 представлена структурная схема устройства; на фиг.2 - пример реализации блока арбитража памяти; на 4иг.З - схема узла захвата магистрали.

Устройство содержит (4иг.1) бло ки 1 и 2 буферной памяти, счетчики 3 и 4, триггер 5, дешифраторы 6 и 7, адреса, генератор 8, импульсов, узел 9 захвата магистрали, магистральные усилители 10-16, элемент И 17, входы и выходы 18-21 межмашинных магистралей для подключения к межмашинной магистрали, вход 22 записи, блок 23 арбитража памяти, мультиплексор 24, счетчики 25-28, дешифратор 29 адреса, триггер 30, распределитель 31 импульсов, одновибраторы 32 и 33, элементы И 34 и 35, элементы ШШ 36-39, группу элементов И 40, информационньй вход-выход 41, адресный вход 42, вход 43 чтения, вход 44 .запроса, выход 45 освобождения, выход 46 готовности, вход 47 начальной уст анов ки.

Блок 23 арбитража памяти (фиг.2) содержит узел 48 памяти приоритетов, счетчики 49 и 50, мультиплексор 51 триггер 52, одновибраторы 53 и 54, элемент 55 сравнения, элемент И 56. Узел 9 захвата магистрали содержи (фиг.З) счетчик 57, регистр 58 и .триггер 59.

Работа устройства начинается с начальной установки,.которая осуществляется подачей импульса на вход 47. По этому импульсу счетчики 3,4,25-27 устанавливаются в нулевое состояние, счетчик 28 - в максимальное, триггеры 5 и 30 устанавливаются в 1гуле(Л

ф tc

со со

СП

вое состояние, на выходе требования блока 23 и на выходе узла 9 захвата магистрали появляется нулевой потен:Циап,

Устройство обеспечивает работу в ;двух режимах - режиме пакетного обмена с произвольной дисциплиной обслу- :живания, которая задается программно |и в режиме прерывания работы, кото--- |рый предназначен для обеспечения (передачи внеочередного пакета, 1 Работа устройства в первом режиме (начинается с занесения пакета инфор- в блок 1 буферной памяти из ОЗУ ЭВМ-источника по входу-выходу 41. Адрес блока 1 буферной памяти задается по входу 42 адреса. Запись каждого слова пакета сопровождается Импульсом по входу 22. По этому I пульсу на соответствующем выходе де- iшифратора б адреса формируется Им- j пульс, 1который си1 хронизирует запис I слова в блок 1 буферной памяти. По iзаднему, фронту этого нмпульса проис- ходит увеличение на единицу содержи- 1 мого счетчика 3, определяюцего ад- рее в памяти очередного пакета. Посыле записи всего пакета на выходе : переноса счётчика 3 формируется им- ; пульс переноса, которьй увеличивает на. единицу .содержимое счетчиков 25 и 28. Содержимое счртчика 25 определяет адрес страницы в блоке 1 буферной памяти, в которой находится записываемый пакет. Содержимое счетчика 28 характеризует заполнение блока 1 буферной памяти. Перед занесением каждого пакета в блок 23 заносится его текущий приоритет. Занесение слова приоритета осуществляется по импульсу записи по входу 22 Блок 23 адресуется по входу 42 при помощи дешифратора 6 адреса. После занесения соответствующего числа пакетов в блок 1 буферной памяти ЭВМ- источник выставляет на вход 44 потенциал запроса на обслуживание, тем самым переключая в единицу триггер 30. Блок 23 выбирает в блоке 1 буферной памяти пакет с наивысшим приоритетом путем последовательного опроса текущих приоритетов всех пакетов.При опросе приоритетов происходит последовательное наращивание счетчИка 27. После выбора пакета, о ладакядего самым большим текувщм приритетом, на выходе требования блока 23 появляется положительный потенциал, который подается на вход требования узла 9 захвата магистрали. Одновременно происходит перезапись содержимого счетчика 27 в счетчик 25. После разрешения всевозможных конфликтов и предоставления общей магист ради данному устройству на выходе узла 9 захвата .::агистрали появляется

потенциал, .который переключает магистральный усилитель 10 на передачу, разрешает прохождение синхросигналов на выход распределителя 31 импульсов и через магистральный усилитель

5 14 выставляется на вход-выход захвата 20. Синхроимпульсы с генератора 8 импульсов индицируют чтение первого слова пакета, задаваемого содержимым счетчиков 26 и 27, Счетчик 26

0 определяет адрес слова в пакете, я счетчик 27 - адрес пакета в памяти.

Адресное слово поступает через вход-выход 18 на информационнь1е вхо5 ды дешифраторов 7 адреса всех осталь- нь1х устройств системы, синхронизация которых осуществляется импyльca ш, поступающими с одновибратора 33. В адресуемом устройстве, если блок 2

0 буферной памяти свободен - логический ноль на выходе триггера 5, то на выходе дешифратора адреса появляется потенциал, которьш через вход- выход 19 подтверждения поступает в устройство-источник и переключает . прохождение синхроимпульсов с одного выхода распределителя импульсов на другой, тем самым производится чте- . гше остальных слов пакета из /.блока

1буферной памяти.

На приемной стороне импульсы синхронизации поступают через элемент И 17 (элемент И 35 закрыт уровнем на входе-выходе 19) и злемент ШШ 39 на счетиьтй вход счетчика 4 и на вход записи блока 2 буферной памяти. После записи всего пакета в блок 2 буферной памяти устройства приемника на выходе счетчика 4 появляется импульс переноса, которьй переключает в единицу счетньй триггер 5, тем самым указывая на то, что блок 2 буферной памяти приемника занят, и выставляет на выход 46 потенциал занятости, которьй прерывает работу ЭВМ-приемника, переводя ее в режим чтения информации из блока

2памяти Чтение информации ЭВМ-приемника на вход-выход 41 сопровождает7

5

40

45

50

55

5

ся сигналами чтения по входу 43 по адресу, задаваемому на входе 42. После чтения очередного слова пакета происходит увеличение на единицу содержимого счетчика 4. После чтения всего пакета переноса счетчика 4 формируется импульс, возвращающий триггер 5 в нулевое состояние, сви- детельствукяцее о том, что блок 2 буферной памяти устройства-приемника свободен.

На передающей стороне после передачи каждого пакета на выходе переноса счетчика 26 формируется отрицательный импульс, который производит уменьшение на единицу содержимого счетчика 28, установку в исходное состояние блока 23 и счетчика 27, а также появление нулевого потенциала на выходе узла 9 захвата магистрали. Если в блоке 1 буферной памяти устройства есть еще пакеты, то процесс захвата магистрали и передачи пакета происходит аналогично описанному. Если блок 1 буферной памяти не содержит пакетов, то на выходе обратного переноса счетчика 28 после передачи последнего пакета формируется отрицательный импульс, который сбрасывает в нуль триггер 30 и выставляет потенциал на выход 45 освобождения, свидетельствуя о том, что блок 1 буферной памяти свободен.

Работа устройства во втором режиме предусматривает постановку в очередь пакета с высшим приоритетом. Дпя этого ЭВМ-источник снимает потенциал логической единицы со входа 44. После передачи очередного пакета на выходе переноса счетчика 26 появляется отрицательный импульс, который через элементы ИЛИ 36 и 35 . сбрасывает триггер 30. После появления уровня нуля на выходе 45 освобождения ЭВМ-источник производит чтение содержимого счетчика 28 путем подачи импг льса чтения на вход 43 по адр су, задаваемому на входе 42. Импульс чтения с дешифратора 29 адреса поступает на вход группы элементов И 40.

Таким образом, ЭВМ-источник определяет количество пакетов, хранящихся в блоке 1 буферной памяти. После этого ЭВМ записывает в блок 23 приоритет пакета, а в блок 1 буферной памяти - сам пакет и выставляет sanрос на вход 44. Дальнейшая : работа устройства аналогична описанной в

623366

первом режиме. Запись пакета всегда происходит в свободную область блока 1 буферной памяти, задаваемую содержимым счетчика 25. Запись двух и более пакетов возможна только после освобождения всего блока I буферной памяти.

Блок 23 (фиг.2) позволяет произ- . водить приоритетное обслуживание пакетов, находящихся в блоке 1 буферной памяти. Приоритет пакета задается словом приоритета, хранящемся в узле 48 памяти приоритетов, кото- g рый представляет собой двухадресное СОЗУ. После поступления единичного потенциала на вход запрета-блока 23 на выходе элемента И 56 появляются импульсы, которые обеспечивают 2Q чтение слов приоритета из узла 48 памяти приоритетов с последующим изменением адреса, задаваемого счет-i чиком 49. Счетчик 50 в начальном положении установлен в максимальное 25 состояние и определяет кодовую комбинацию, с которой сравниваются слова приоритета, считываемые из узла 48 памяти приоритета. Элемент 55 сравнения имеет два выхода. При не- 3Q сравнении считанного из узла 48 памяти приоритетов кодовой комбинации с содержимым счетчика 50 на первом .выходе схемы сравнения появляется импульс, по срезу которого переключается счетчик 27 устройства. Разрядности счетчиков 27 и 49 совпадают. Таким образом, счетчик 27 содержит адрес проверяемой страницы. После всего просмотра узла 48 памяти приоритетов и необнаружении данного кода на выходе счетчика 49 формируется импульс переноса, который уменьшает на .единицу содержимое счетчика 50. Тем самым осуществляется переход к анализу на более низкий приоритет. Процесс продолжается до первого совпадения приоритета, считанного из узла 48 памяти приоритетов, и кода, задаваемого счетчиком 50. При этом на втором выходе элемента 55 сравнения формируется импульс, который устанавливает в единицу, триггер 52. По срезу этого импульса одновибратор 54 формирует импульс по вторым входам данных узла 48 памяти приоритетов, на которых установлены логические нули, адрес задается счетчиком 49 на вторые адресные входы узла 48 памяти приоритетов.

35

40

45

0

5

Тем самым происходит обнуление пос- Т ледией считанной-ячейки. Триггер 52, усгановлега1ый в единицу, вьщает потенциал на выход требования и одновременно закрывает прохождение синхроимпульсов через элемент И 56. После передачи всего пакета на входе освобождения появляется импульс, который устанавливает в исходное сос- i тояние счетчики 49 и 50. По срезу этого импульса происходит обнуление i триггера 52, Таким образом, блок 23 возвращен в исходное состояние, и, если есть уровень единицы на вхо- I де запрета, повторяет цикл выделения старшего приоритета. При нахождении в узле А8 памяти, приоритетов двух одинаковых комбинаций обслуживание : пакетов происходит в порядке их оп- : роса„ Нулевая комбинация приоритета . является запрещенной.

Узел 9 захвата магистрали (фиг.З) позволяет производить приоритетное, обслуживание запросов на захват запросов общей магистрали. Запросы на захват поступают с входа требоваш1Я на 0 входы триггера 59. Если па входе-выходе 20 находится логический нуль, то импульсы синхронизации поступают на вход синхронизации счетчика 57, производя последовательное наращивание его значения. Начальпое значение счетчика 57 задается значением регистра 58, представляющего соответствующий приоритету устройства набор нулей и единиц Чем выше приоритет устройства, тем большее значе1ше находится на выходе регистра 58. Как только возникает переполнение счетчика 57, на его выхде формируется импульс переноса, по заднему фронту которого триггер 59 переключается в единичное состояние. Потенциал с выхода узла 9 захвата магистрали через вход-выход 20 производит начальную установку счетчиков 57 всех устройств системЬ:, тем самым блокируя у них режим счета,, Дальнейшая .работа узла 9 захвата магистрали возможна после освобождения общей магистрали, которое осуществляется после передачи пакета импульсом, поступающим на вход освобождения узла 9 захвата магистрали или ее начальной установки, т.е. сброса в нуль триггера 59. Таким образом, общая магистраль может быть

предоставлена только одному устройству.

Формула

зобретенйя

5

0

5

5

0

50

1. Устройство для сопряжения ЭВМ с общей магистралью, содержащее два блока буферной памяти, два счетчика, первый триггер, два дешифратора адреса, генератор импульсов, узел захвата магистрали, семь магистральных усилителей, первый элемент И, при этом первый информационный вход- выход первого магистрального усилителя является входом-выходом устройства для подключения к информационной шине общей магистрали, информационный выход второго магистрального усилителя и информационный вход третьего магистрального усилителя являются выходом и входом устройства для подключения к шине подтверждения захвата общей магистрали, информационный вход четвертого магистрального усилителя и информационный выход пятого магистрального усилителя являются входом и выходом устройства для подключения к шине захвата об- 0 щей магистрали, информационный вход шестого магистрального усилителя и информа}1ионный выход седьмого магистрального усилителя являются входом и выходом устройства для подключения к шине синхронизации общей магистрали, управляющий вход первого дешифратора адреса является входом устройства для подключения к выходу записи ЭВМ, при зтом управляющий вход первого магистрального усилителя соединен с информационным входом пятого магистрального усилителя и с выходом узла захвата магистрали, первый выход первого дешифратора адреса соединен с синхровходом первого счетчика и с входом записи первого блока буферной памяти, разрядные выходы второго счетчика соединены с адресными входами второго блока буферной памяти , выход переноса второго счетчика соединен с сиихровходом первого триггера, выход которого соединен с раз- решаюЕщм входом второго дешифратора адреса, выход которого соединен с информационным входом второго магистрального усилителя и с первым входом первого элемента И, отличающееся тем, что, с целью повьш1е- ния быстродействия, в него введены

45

55

9

блок арбитража памяти, мультиплексор, четыре счетчика, третий дешифратор адреса, второй триггер, распределитель импульсов, два одновибра- тора, два элемента И, четыре элемента ИЛИ, группу элементов И, причем группа информационных выходов второго блока буферной памяти соединена с группой информационных входов первого блока буферной памяти, с группой информационных входов блока арбитража памяти, с выходами элементов И группы и образует группу вхо-г дов-выходов устройства дпя подключения к группе информационных входов- выходов ЭВМ, выход первого триггера является выходом устройства дпя подключения к входу готовности ЭВМ, информационный вход первого дешифратора адреса соединен с информационным входом третьего дешифратора адреса и является входом устройства для подключения к адресному выходу ЭВМ, управляющий вход третьего дешифратора адреса является входом устройства для подключения к выходу чтения ЭВМ, синхровход второго триггера соединен с первым входом первого элемента ИЛИ и является входом устройства для подключения к выходу запроса ЭВМ, выход второго триггера соединен с входом запрета блока арбитража памяти и является выходом устройства дпя подключения к входу освобождения ЭВМ, установочный вход первого счетчика соединен с установочными входами второго, третьего, четвертого, пятого счетчиков, с первым установочным входом шестого счетчика, с нулевым входом первого триггера, с первым нулевым входом второго триггера, с установочными входами узла захвата магистрали и блока арбитража памяти и является входом устройства для подключения к установочному выходу ЭВМ, при этом выход генератора импульсов соединен с синхровходами блока арбитража памяти, узла захвата магистрали и распределителя импульсов, информационный вход седьмого магистрального усилителя соединен с выходом второго элемента ИЛИ, первый вход .которого соединен с синхровходом четве того счетчика, с первым входом третьего элемента ИЛИ и с первым синхровходом распределителя импульсов, второй синхровход которого соединен с вто-6233610

рым входом второго элемента ИЛИ и с вторым входом третьего элемента ИЛИ, выход которого соединен с управляющим входом мультиплексора и с входом запуска первого одновибратора, выход которого соединен с входом чтения первого блока буферной памяти, адресные входы которого соединены с

Q группой информационных выходов муль- типпексора, первая группа информационных входов которого соединена с разрядными выходами первого, второго счетчиков и с группой адресных вхо15 дов блока арбитража памяти, выход переноса которого соединен с синхровходом шестого счетчика, разрядные выходы которого и разрядные выходы четвертого счетчика соединеИ) с

2Q второй группой информационных входов

мультиплексора и с группой информа- ционных входов третьего счетчика,

синхровход которого соединен с выхо, дом переноса первого счетчика и с .

25 первым синхровходом пятрго счетчика, разрядные выходы которого соединены с первыми входами элементов И группы, вторые входы которых соединены с первым выходом третьего дешифратоJQ ра адреса, второй выход которого соединен с первым входом четвертого элемента ИЛИ и с входом чтения второго блока буферной памяти, информационный вход которого соединен с информационным выходом первого блока бу ферной памяти, с вторым информационным входсм-выходом первого aгиcт- рального усилителя и с информационным входом второго дешифратора адреса, стробирующий вход которого соединен с выходом второго одновибратора, вход запуска которого соединен с выходом второго элемента И,первый вход которого соединен с информационным выходом третьего магистрального усилителя и с управляющим входом распределителя импульсов, разрешающий вход которого соединен с выходом узла захвата магистрали, вход требования которого соединен с входом записи ., третьего счетчика и с выходом требования блока арбитража памяти, вход освобождения которого соединен с входом освобождения узла захвата магистрали, с выходом переноса четвертого счетчика, с вторым синхровходом пятого счетчика и с вторым входом первого элемента ИЛИ, выход которого соединен с первым входом третьего

40

45

50

55

элемента И, первый вход и выход которого соединены соответственно с выходом переноса пятого счетчика и с вторым нулевым входом второго триггера, второй выход первого дешифратора адреса соединен с входом записи блока арбитража памяти, установочный выход которого соединен с вторым установочным входом шестого счетчика, вход запрета узла захвата магистрали соединен с управляющим входом второго дешифратора адреса и с информационным выходом четвертого магистрального усилителя, информационный выход шестого магистрального усилителя соединен с вторым входом второго элемен- таИи с вторым входом первого элемента И, выход которого соединен с входом записи второго блока буферной памяти и с вторым входом четвертого элемента ИЛИ, выход которого соединен с синхровкодом второго счетчика,

2, Устройство по п.1, о т л и - чающееся тем, арбитража памяти содержит узел памяти приоритетов, мультиплексор, два счетчика, триггер, элемент сравнения, элемент И, два одновибратора, причем группа информационных входов узла памяти приоритетов образует группу информационных входов блока, первая группа информационных входов мультиплексора образует группу адресных входов блока, первый и второй входы элемента И являются соответственно входом запрета и синхровходом блока, синхровход триггера соединен с первы «1 установочными входами первого, второго счетчиков и. является входом освобождения и установочным . выходом блока, первый вход записи узла памяти приоритетов является входом записи блока, единичный выход триггера является выходом требования блока, выход несравне1шя элемента сравнения является выходом переноса блока, нулевой вход триггера соединен с вторыми установочными

входами первого, второго счетчиков и является установочным входом блока, при этом в блоке арбитража памяти нулевой выход триггера соединен с третьим входом элемента И, выход которого соединен с синхровходом первого счетчика, с управляющим входом мультиплексора и с входом запуска первого одновибратора, выход которого соединен с входом чтения узла памяти приоритетов и синхровходом элемента сравнения, выход сравнения которого соединен с единичным входом триггера и с входом запуска второго одновибратора, выход ко- т.орого соединен с вторым входом записи узла памяти приоритетов, первая группа адресных входов которого соединена с группой выходов мультиплексора, вторая группа информационных входов которого соединена с второй группой адресных входов узла памяти приоритетов и с разрядными выходами

первого счетчика, выход переноса

которого соединен с синхровходом второго счетчика, разрядные выходы которого соединены с первой группой информационных входов элемента сравнения, вторая группа информационных входов которого соединена с группой информационных выходов узла памяти приоритетов.

3. Устройство по п.1, о т л и - чающееся тем, что узел захвата магистрали содержит регистр, счетчик и триггер, причем счетный, установочный входы счетчика, информационный вход, первый и второй нулевые входы и выход триггера являются соответственно синхровходом, входом запрета, входом требования, входом освобождения, установочным входом и выходом узла захвата магистрали, при этом информационный выход регистра соединен с информационным входом счетчика, выход переноса которого соединен с синхровходом триггера,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для сопряжения электронных вычислительных машин | 1987 |

|

SU1443001A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1987 |

|

SU1439612A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1986 |

|

SU1354199A1 |

| Устройство для сопряжения ЭВМ | 1987 |

|

SU1460724A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1988 |

|

SU1571603A1 |

| Устройство для подключения источников информации к общей магистрали | 1986 |

|

SU1381531A1 |

| Устройство для сопряжения электронной вычислительной машины с общей магистралью | 1987 |

|

SU1411765A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения многомашинных вычислительных систем. Целью изобретения является повьшение быстродействия. Устройство содержит два блока буферной памяти, блок арбитража памяти, узел захвата магистрали, шесть Счетчиков, три дешифратора адреса, два триггера, семь магистральных усилителей, генератор импульсов, распределитель импульсов, два одно- вибратора, три элемента И, четьфе элемента ИЛИ. 2 з.п. ф-лы, 3 ил.

фиг. 2

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-08-21—Подача