(54) СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по длительности | 1980 |

|

SU902240A1 |

| Селектор информационного сигнала | 1989 |

|

SU1737738A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1403356A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Цифровой измеритель длительности одиночных импульсов | 1983 |

|

SU1171444A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Селектор импульсов по длительности | 1981 |

|

SU978335A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2267221C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

1

Иэофетр ние относится к импульсной и может быть использовано для сепшшни импульсов заданной длительности.

Известен селектор импульсов по длительности, содержащий два сдвиговых регистра, счетчик импульсов, входной логический блок, импульсный выходной каскДд решакяций блок, каскад стробирования и три элемента сброса 1 .

Недостатком данного устройствами ЛЯ0ТСЯ низкая надежность, определяемая большнм количеством используемого {з дования, и невозможность формирования выходных импульсов с наперед заданной длительностью.

Известен селектор импульсов по длительности, содержащий генератор тактовых импульсов, счетчик импульсов, по два {ешифратора и триггера, инвертор, элемент задержки и три элемента СОЕП пения, С 2 3 .

Недостатком этого устройства является сложность и возможность формиров ния выходного импульса длительностью, равной только длительности импульса генератора тактоьых импульсов.

Наиболее близким по техничесвюй сущности и досшгаемому результату к предлагаемому, является селектор импульсов по длительности, содержащий два регистра

сдвига, элемент ИЛИ, соединен)Ш1й с установочным входом регистра, три элемен|Та И, соединенные входами с выходом регистра, и инвертор, вход которого со динен с инфopмiauиoннoй шиной и с инфор мационнымвходом регистра сдвига С 3 .

Недостапсом этого устройства являет ся его слозкность, определяемая большим , количеством используемого оборудования, что, в конечном счете, сяфеделяет и невысокую надежность устройства.

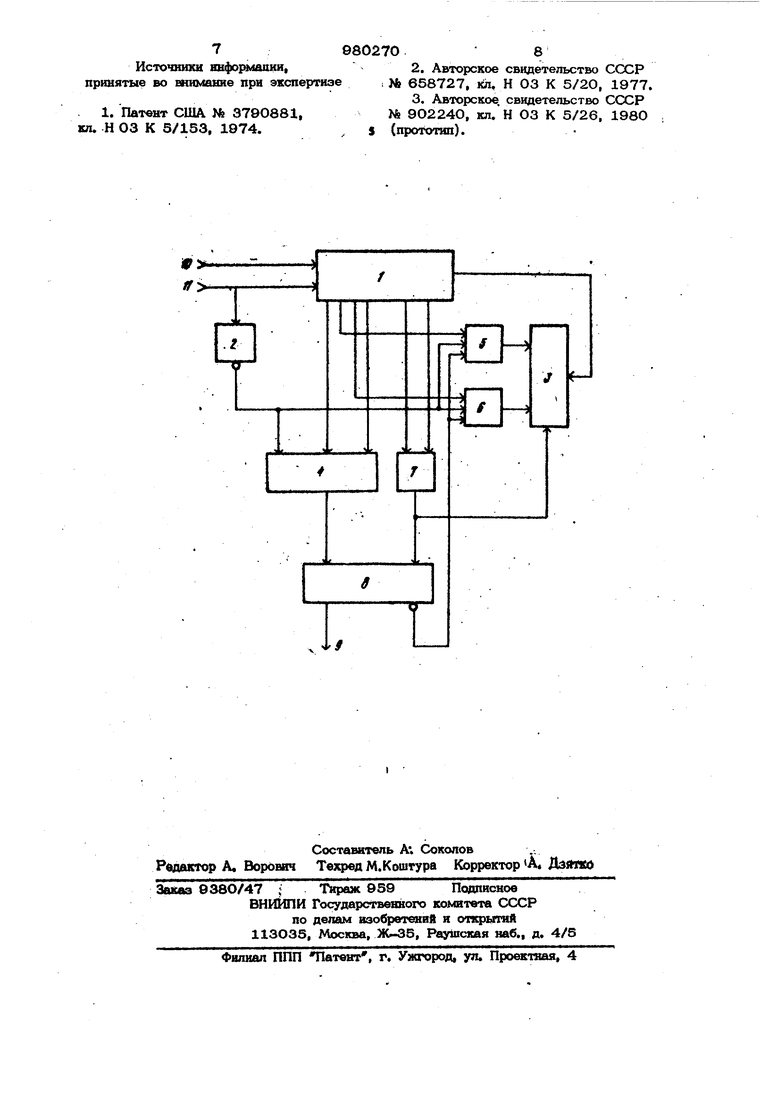

Цель изо(етения - упрощение устройства. Поставленная цель, достигается тем, что в селектор импульсов по длительности, содержащий регистр сдвига, элемент ИЛИ, три элемента И и инвертор, вход которого соединен с информационной шиной и с информационным входом регистра сдвига, выход - с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с первым, вторым и третьим выходами регистра сдвига, четвертътй выход которого соединен с третьим входом первого элемента И, а выходы вто рого и третьего элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, вьжод которого соединен с установочным входом регистра сдвига, вход синхронизации которого соединен с шиной синхронизации, введены триггер и четвертый элемент И, первый и второй входы которого соединены соответственно с пятым и шестым вь ходами регистра сдвига, а выход соединен с третьим входом элемента ИЛИ не обнуляющим входом триггера, вход записи которого соединен с выходом первого элемента И, инверсный выход - с третьими входами второго и третьего элементов И, а прямой выход - с выходной шиной устройства. На чертеже приведена структу|)ная cx ма устройства. Селек-вор импульсов по длительности содержит п -разрядный регистр 1 сдвига, информационный вход которого соединен со входом инвертора 2, а установочный вход - с выходом элемента 3 ИЛ Выход инвертора 2 соед1Шен с первыми входами элементов 4-6 И, вторые вхо- ды которых соединены соответственно с первым, вторым и третьим ыходамирегистра 1. Четвертый выход регистра 1 соединен с третьим входом элемента 4, а пятый к шестой выходы регистра 1 соедине Ш1 соответственно с первым и вторым входами элемента 7 И. Выходы элементов 5-7 соединены соответственно с первым, вторым и третьим входами элемента 3, третий вход которого соединен, кроме того, с обнуляющим вхо дом триггера 8, вход записи которого соединен с выходом элемента 4. Инверс ный выход триггера 8 соединен с треть ими входами элементов 5 и 6, а прямой выход - с выходной шиной 9 устройства Вход синхронизации регистра 1 соединен с шиной 10 синхронизации, по которой поступают импульсы сдвига (высокой астоты), информационный вход регистра 1 соединен о информационной шиной 11, о которой поступают селектируемые кмпульсьи Первьй и второй выходы регистра 1 являются соответственно прямым и инверсным выходами i -го разряда регистра 1. Наличие единицы в i -м разряде регистра 1 означает, что длительность входного селектируемого импульса соответст вует нижнему пределу селекции. Третей и четвертый выходы регистра 1 являются соответствеэшо прямым и инверсньпл выходами j -го разряда регистра 1 (п j i ). Наличие единицы в j -м разряде регистра 1 означает, что длительность входного селектируемого импульса « превьппает верхний предел селекшш. Пятый и шестой выходы регистра 1 являются соответственно инверсным выходом . ( | -1)-го разряда и прямым выходом -го разряда регистра 1 ( 1с может принимать любое значение от 2 до п ) и определяют длительность выходного импульса, вырабатываемого предлагаемым селекторюм импульсов по длительности Б ответ на входные импульсы, длительность которых соответствует пределам селекции. Селектор импульсов по длительности работает следутошим образом. В исходном состоянии, когда входные . импульсы не поступают на информационную шину 11, регистр 1 и триггер 8 находятся в обнуленном состоянии. При поступлении на вход регистра 1 входного импульса с информационной шины в разр5щы регистра 1 последовательно, начиная с первого, записывается логическая единица, так как на вход синхронизации регистра 1 посюяшю поступают синхронизирующие импульсы, обеспечивающие сдвиг логической единицы из предьздуи1его разряда в последующий. Количество рваряцоъ регистра 1, в которые .будет записана логическая единица, зависит от длительности входного импульса. Если длительность входного импульса меньше нижнего предела селекции, то i -и и все последующие разрзады регистра 1 будут находиться в нулевом состоянии, т.е. на первом и третьем выходах регистра 1 будут уровни логическохх нуля, а на втором и четвертом выходах - уровни логической единицы. После овончания входного импульса на выходе инвертора 2 формируется уровень логичес- кой едтшцы, воадействуклаей на первые входы элементов 4-6. Элемент 4 не сра батьгаает, так как на его второй вход поступает логический нуль, триггер 8 не переключается и на выходе устройства нет отклика на данный входной импульс, Уровень логической единицы юшерсного выхода триггера 8 воздействует 1Ш третьи входы элементов 5 и 6. Так как все три входа элемента 5 находятся в состо нии логической единицы, он срабатьшает и через элемент 3 обнуляет регистр 1, Устройство готово к приему следующего входного импульса. Если длительность входного импульса больще верхнего предела селектирования, то j -и разр1Зд регистра 1 находится в единичном состоянии, т.е. на первом и третьем выходах регистра 1 - уровни ло гической единицы, а на втором и четвертом выходах - уровни логического нуля. После окончания входного импульса на выходе инвертора 2 формируется уровень логической единицы. Элемент 4 не ера- батывает, так как его третий вход находится в состоянии логического нуля, триггер 8 не переключается и на выходе устройства нет отклика на данный входно импульс. Уровень логической единицы инверсного выхода триггера 8 воздейст- вует на третьи входы элементов 5 и 6. Так как все три входа элемента 6 находятся в состоянии логической единицы, он срабатывает и через элемент 3 обнуляет регистр 1. лг «, Устройство готово к приему следующего входного импульса. Если длительность входного импульса соответствует пределам селекции, то i -и разряд регистра 1 находится в единич- ном состоянии,, а j -и разряд - в нулевом состоянии. После окончания входного . импульса уровень логической единицы с выхода инвертора 2 воздействует на первые входы элементов 4-6; на второй и третий входы элемента 4 поступают в данном случае уровни логической единицы соответственно с первого и с четве1 того выходов регистра 1. Элемент 4 срабатьшает и устанавливает триггер 8 в единичное состояние, на прямом выходе которого, связанном с выходной шиной 9, появляется импульс логической единицы. При этом уровень логического нуля с инверсного выхода триггера 8 воздействует на третьи входы элементов 5 и 6 и блокирует обнуление регистра 1 через эти элементы на все время формвровгшия выходного импульса. После окончания входного импульса логичесвая единица, записанная в регистре 1, продолжает сдвигаться вправо, н регистр 1 с первого разр1зда начинает заполняться логическим нулем. Как тольло (tc -1}-й разряд регистра 1 переходит в нулевое состояние (при этом 1с -и разряд находится в единичном состоянии), пятый и шестой выходы регистра 1 находятся в единичном ростоянии, 7 срабатьшает и обнуляет триггер 8 « через элемент 3 - регистр 1. Устройство готово к при му следующего входного импульса. Пределы селекции и длитетшкость выходньпс импульсов устройства можно легко изменять, подключая выходы регистра 1 к соответствующим разрядам. Таким образом, введение триггера и элемента И позволяет упростить устрой- ство, исключив из него второй регистр и элемент сброса. Формула изобретения Селектор импульсов по длительности, содержащий регистр сдвига, элемент ИЛИ, три элемента И и инвертор, вход которого соединен с информационной щиной и с информационным входом регистра сдвига, выход - с первыми входами пер вого, второго и третьего элементов И, вторые входы которых соединены соответственно с первым, вторым и третьим выходами регистра сдвига, четвертый выход которого соединен с третьим входом первого эле 1ента И, а выходы второго и третьего элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен ,с установочным входом регистра сдвига, вход синхронизации которого соедини с щиной синхронизации, отличающийся тем, что, с целью упрощения устройства, в него введены григгер и четвертый элемент И, первый н второй входы которого соединены со- ; тветственно с пятым и шестым выходами регистра сдвига, а выход соединен с третьим входом элемента ИЛИ и с обнуляххцим входом триггера, вход записи которого соединен с выходом цервого шемехта И, инверсный выход - с треть|ми входамн второго и третьего элемен тов И, а прямой выход - с выходной щиной устройства.

Источники внформашш, принятые во внимание при экспертизе

,

.1

: № 658727, кл, Н 03 К 5/20, 1977.

S (прототип).

Авторы

Даты

1982-12-07—Публикация

1981-06-18—Подача