соединен с инверсным выходом первого 1К-триггера и с его информационными I- и К-входами, а выход подключен к первому выходу блока синхронизации, инверсный выход D-триггера соединен с третьим выходом блока синхронизации и входом установки в О второго

1К-триггера и с вторым входом второго элемента И, третий вход которого соединен с инверсным выходом второго, 1К-триггера и с его информационными I- и К-входами, а выход второго элемента И соединен с вторым выходом блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Устройство для предварительной обработки изображений | 1989 |

|

SU1654849A1 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1990 |

|

SU1755360A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для обработки и регистрации сигналов | 1987 |

|

SU1458845A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Генератор псевдослучайных последовательностей | 1987 |

|

SU1443141A1 |

| Устройство для выделения экстремумов | 1983 |

|

SU1111174A1 |

1. ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ДЛИТЕЛЬНОСТИ ОДИНОЧНЫХ ИМПУЛЬСОВ, содержащий блок задержки с п отводами, генератор счетных импульсов, основной и уточняющий счетчики, отличающийся тем, что, с целью повышения точности измерений, в него введены блок синхронизации, первый и второй элементы ИЛИ, регистр сдвига, инвертор, D-триггер,- элемент И-НЕ, элемент 2И-ШТИ-НЕ, элемент задержки, причем выход генератора счетных импульсов подключен ко входу синхронизации блока синхронизации, первый выход которого соединен с первым входом первого элемента -ИЖ, второй вход которого подключен к второму выходу блока синхронизации, а выход соединен с V-входом регистра сдвига непосредственно и через инвертор с С-входом регистра сдвига, выход которого подключен к D-входу D-триггера, выход которого соединен с первым входом элемента И-НЕ, выход которого подключен к счетному входу уточняющего счетчика, выход которого соединен с первым входом элемента 2И-ИЛИ-НЕ, второй вход которого подключен к третьему выходу блока синхронизации, четвертый выход которого соединен с третьим входом элемента 2И-ИЛИ-НЕ, четвертый вход которого подключен ко второму входу элемента И-НЕ, входу синхронизации D-триггера, выходу генератора счетных рз пульсов и входу синхронизации регистра сдвига, разрядные входы которого соединены с выходами блока задержки с п отводами, вход которого через элемент задержки подключен к информа(О ционному входу блока синхронизации, сл первьм выход которого соединен с первым входом второго элемента ИПИ, выход которого подключен к входам обнуления уточняющего и основного счетчиков, счетный вход последнего соединен с выходом элемента ,. 2. Измеритель по п.1, о т л и .чающийся тем, что, блок 4 4 синхронизации содержит первый и второй 1К-триггеры, первый и второй элементы И и D-триггер, первый вход которого соединен с первыми входами первого и второго 1К-триггеров, с. первыми входами первого и второго элементов И и входом синхронизации блока синхронизации, информационный вход D-триггера подключен к информационному входу блока синхронизации, а прямой выход которого соединен с четвертым выходом блока синхронизации, с входом установки в О первого1К-триггера и с вторым входом парно го элемента И, третий вход которого

1

Изобретение относится к измерительной -технике и может быть использойано при измерении длительности одиночных импульсов.

Известен многоканальный преобразователь длительности импульсов в цифровой код, состоящий из секционированной линии задержки, элементов совпадения и счетчиков, определяемых числом выводов секционированной лини задержки, и сумматора 1 J.

Недостатком устройства является аппаратурная сложность.

Наиболее близким техническим решением к изобретению является уст.ройство для измерения одиночных временных интервалов, содержащее генератор счетных импульсов, временной селектор, первый блок задержки на длительность периода счетных импульсов с п отводами, п вспомогательных временных селекторов, п-входовой второй блок задержки с задержкой на период счетных импульсов между соседними входами, уточняющий и основной счетчики, схема управления реверсом и блок управления, выход которого соединен со вторыми входами вспомогательных временных селекторов, первые входы которых соединены соответственно с отводами первого блока задержки, а выходы-- с входами второго блока задержки, выход которого соединен со счетным входом уточняющего счетчика, выход которого соеди- ней с первым счетным входом основного счетчика, а вход выбора режиг а с входом выбора режима основного счетчика и с выходом схемы управления реверсом, вход которой соединен с входом устройства, с первым выходом временного селектора, с входом первого блока задержки, с сигнальным

входом блока управления, синхровход которого соединен с выходом генератора счетных импульсов и с вторым входом временного селектора, выход которого соединен со вторым счетным входом основного счетчика 2 J.

Недостатком известного устройства является невысокая точность, зависящая от минимально допустимой длительности расщепленного уточняющего импульса на отводе первого блока задержки, и сложность.

Целью изобретения является повышение точности измерения.

Поставленная цель достигается тем, что в цифровой.измеритель длительности одиночных импульсов, содержапщй блок задержки, с п отводами, генератор счетных импульсов, основой и уточняющий счетчик, дополнительно введены блок синхронизации первьм и второй элементы ИЛИ, регистр сдвига, инвертор, D-триггер, элемент И-НЕ, элемент 2И-И1И-НЕ и элемент задержки, причем генератор счетных импульсов подключен ко входу синхронизации блока синхронизации, первый выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен ко второму выходу блока синхронизации, а выход соединен с V-входом регистра сдвига непосредственно и через инвертор с С-входом регистра сдвига, выход которого подключен к D-входу D-триггера, выход которого соединен с первым входом элемента И-НЕ, выход которого подключён к счетному входу уточняющего счетчика, выход которого соединен с первым входом элемента 2И-ИЛИ-НЕ, второй вход которого подключен к третьему выходу блока синхронизации, четвертый выход которого соединен с третьим входом элемента 2И-ИЛИ-НЕ, четвертый вход которого подключен ко второму входу элемента И-НЕ, входу синхронизации D-триггера, выходу генератора счетных импульсов и входу синхронизации регистра сдвига, разрядные входы которого соединены с выходами блока задержки с п отводами, вход которого через элемент задержки подключен к информационному входу блока синхронизации, первый выход которого соединен с.первым входом второго, элемента ИЛИ, выход которого подключен к входам обнуления уточняющего и основного счетчиков, счетный вход последнего соединен с выходом элемента 2И-ИЛИ-НЕ.

Кроме того, блок синхронизации содержит первый и второй 1К-триггеры первый и второй элементы И и D-триггер, первый вход которого соединен с первыми входами первого и второго ХК-триггеров, с первыми входами первого и второго элементов И и со входом синхронизации блока синхронизации, информационный вход D-триггера подключен к информационному входу блока синхронизации, а прямой выход которого соединен с четвертым выходом блока синхронизации, с входом установки в О первого 1К-триггера и со вторым входом первого элемента И, третий вход которого соединен с инверсным выходом первого IK-триггера и с его информационными I- и К-вхдами, а выход подключен к первому выходу блока синхронизации, инверсный выход D-триггера соединен с третьим выходом блока синхронизации, с входом установки в О второго IK-триггера, со вторым входом второго элемента И, третий вход i oToporo соединен с инверсным выходом второго 1К-триггера и с его информационными I- и К-входами, а выход второго элемента И соединен со вторым выходом блока синхронизации.

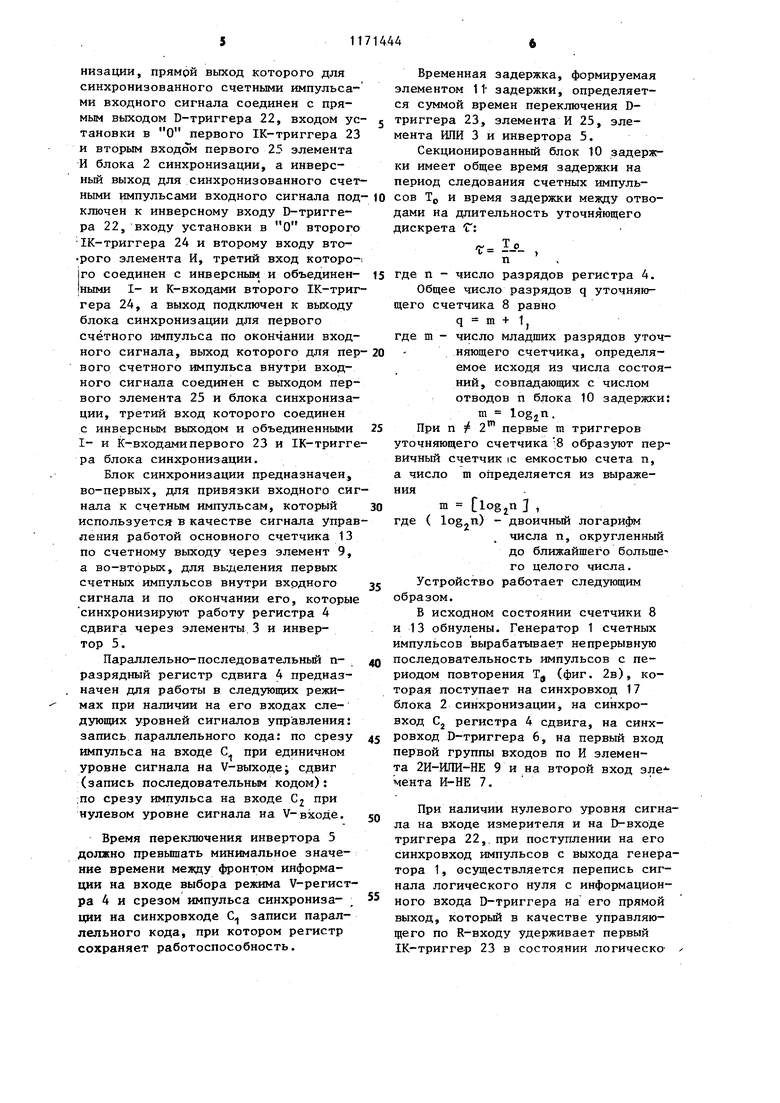

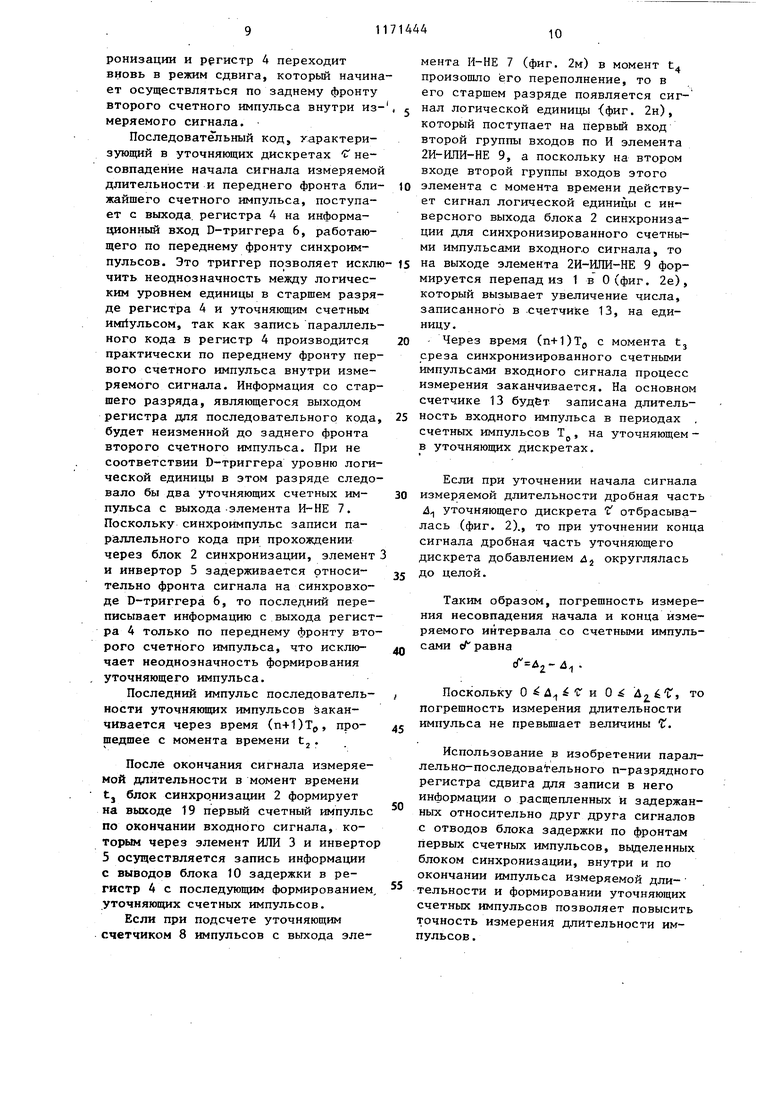

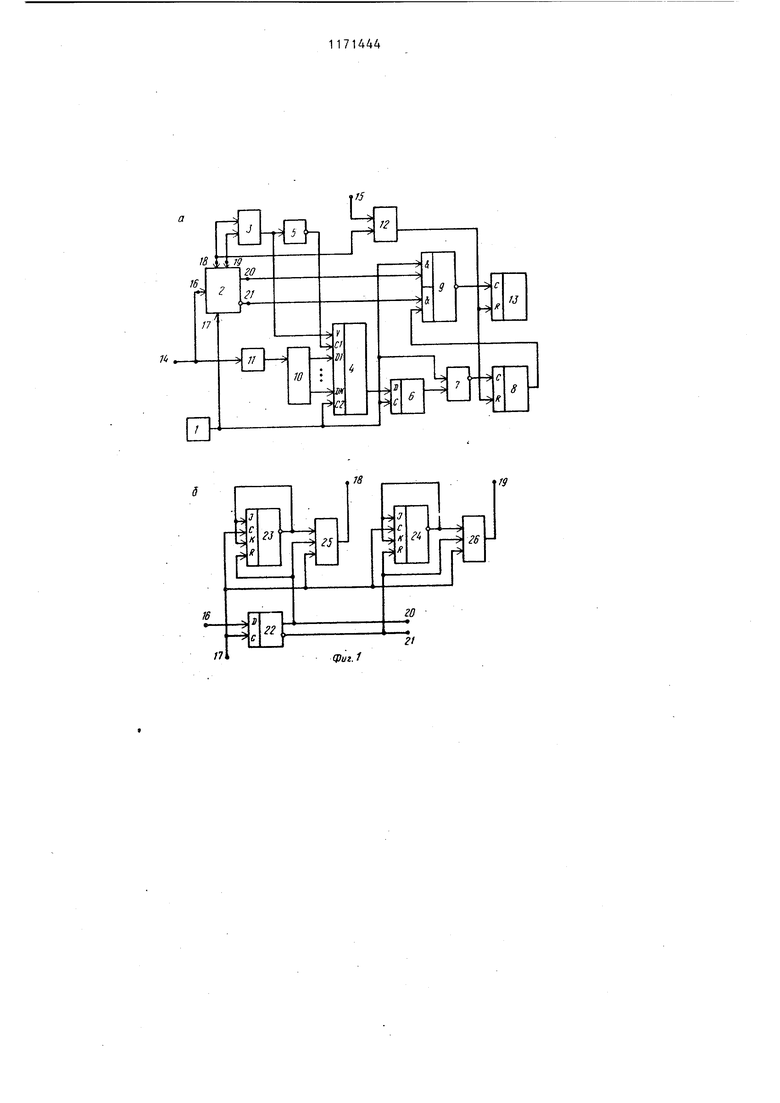

На фиг . 1 показан предлагаемый измеритель (а - функциональная схема б - блок синхронизации); на фиг. 2 временные диаграммы.

Измеритель длительности импульсо содержит генератор 1 счетных импульсов, подключенный своим входом ко входу синхронизации блока 2 синхронизации, выход которого для первого

счетного импульса внутри входного сигнала соединен с первым входом первого элемента ИЛИ 3, второй вход которого подключен к еыходу блока синхронизации для первого счетного импульса по окончании входного сигнала, а выход соединен с входом V выбора режима работы регистра 4 сдвига напрямую, а через инвертор 5 - с входом синхронизации записи параллельного кода регистра 4, выход которого подключен к D-входу D-триггера 6, выход которого соединен с первым входом элемента И-НЕ 7, выход которого подключен к счетному входу уточняющего счетчика 8, выход которого соединен с первым входом.второго элемента И элемента 2И-Р1ПИ-НЕ 9, второй вход которого подключен к инверсному выходу блока 2 синхронизации, прямой выход которого соединен со вторым входом первого элемента И элемента 2И-ИЛИ-НЕ 9, первый вход которого подключен ко второму входу элемента И-НЕ 7, входу синхронизации D-триггера 6, выходу генератора 3 и входу синхронизации регистра 4, входы параллельного ввода информации соединены с выходами секционированного блока 10 задержки, вход которого через элемент 11 задержки подключен к информационному входу блока 2 синхронизации, выход которого для первого счетного импульса внутри входного сигнала соединен с первым входом элемента ИЛИ 12, выход которого подключен к входам установки в О уточняющего 8 и основного 13 счетчиков, счетный вход последнего соединен с выходом элемента 2И-Ш1И-НЕ 9, а выход совместно с выходом уточняющего счетчика 8 является вьпсодом устройства, информационный вход 14 которого подключен к информационному входу блока 4 синхронизации, а вход. 15 установки в исходное состояние соединен со вторым входом второго элемента ИЛИ 12. Блок .2 синхронизации имеет входы 16 у 17 и выходы 18-21.

Блок 2 синхронизации содержит D-триггер 22, вход синхронизации которого соединен с входами синхронизации блока 2 синхронизации, первого 23 и второго 24 1К-триггеров и первыми входами первого 25 т второго 26 элементов И блока 2 синхронизации, а D-B7KiA триггера 22 подключен к информационному входу блока 2 синхронизации, прямрй выход которого для синхронизованного счетными импульсами входного сигнала соединен с прямым выходом D-триггера 22, входом установки в О первого 1К-триггера 23 и вторым входом первого 25 элемента И блока 2 синхронизации, а инверсный выход для синхронизованного счетными импульсами входного сигнала подключей к инверсному входу D-триггера 22, входу установки в О второго 1К-триггера 24 и второму входу второго элемента И, третий вход которо-i го соединен с инверсным и объединенными I- и К-входами второго 1К-триггера 24, а выход подключен к выходу блока синхронизации для первого счётного импульса по окончании входного сигнала, выход которого для первого счетного импульса внутри входного сигнала соединен с выходом первого элемента 25 и блока синхронизации, третий вход которого соединен с инверсным выходом и объединенными I- и К-входами первого 23 и IK-триггера блока синхронизации.

Блок синхронизации предназначен, во-первых, для привязки входного сигнала к счетным импульсам, который используется в качестве сигнала управления работой основного счетчика 13 по счетному выходу через элемент 9, а во-вторых, для вьзделения первых счетных импульсов внутри входного сигнала и по окончании его, которые синхронизируют работу регистра 4 сдвига через элементы.3 и инвертор 5.

Параллельно-последовательный празрядный регистр сдвига 4 предназначен для работы в следующих режимах при наличии на его входах следующих уровней сигналов управления: запись параллельного кода: по срезу импульса на входе С. при единичном уровне сигнала на V-выходе; сдвиг (запись последовательным кодом): ;по срезу импульса на входе С-, при нулевом уровне сигнала на V-входе.

Время переключения инвертора 5 должно превышать минимальное значение времени между фронтом информации на входе выбора режима V-регистра 4 и срезом импульса синхрониза- , ции на синхровходе С записи параллельного кода, при котором регистр сохраняет работоспособность.

Временная задержка, формируемая элементом 11- задержки, определяется суммой времен переключения Dтриггера 23, элемента И 25, элемента ИЛИ 3 и инвертора 5,

Секционированный блок 10 задержки имеет общее время задержки на период следования счетных импульсов TO и время задержки между отводами на длительность уточняющего дискрета С:

-- , п

где п - число разрядов регистра 4. Общее число разрядов q уточняющего счетчика 8 равно

q m + 1

где m - число младших разрядов уточняющего счетчика, определяемое исходя из числа состояний, совпадающих с числом отводов п блока 10 задержки

m ,

При п Ф 2 первые та триггеров уточняющего счетчика .8 образуют первичный счетчик 1C емкостью счета п, а число m определяется из выражения

m logjn , где ( log п) - двоичный логарифм

числа п, округленный до ближайшего большего целого числа. Устройство работает следующим образом.

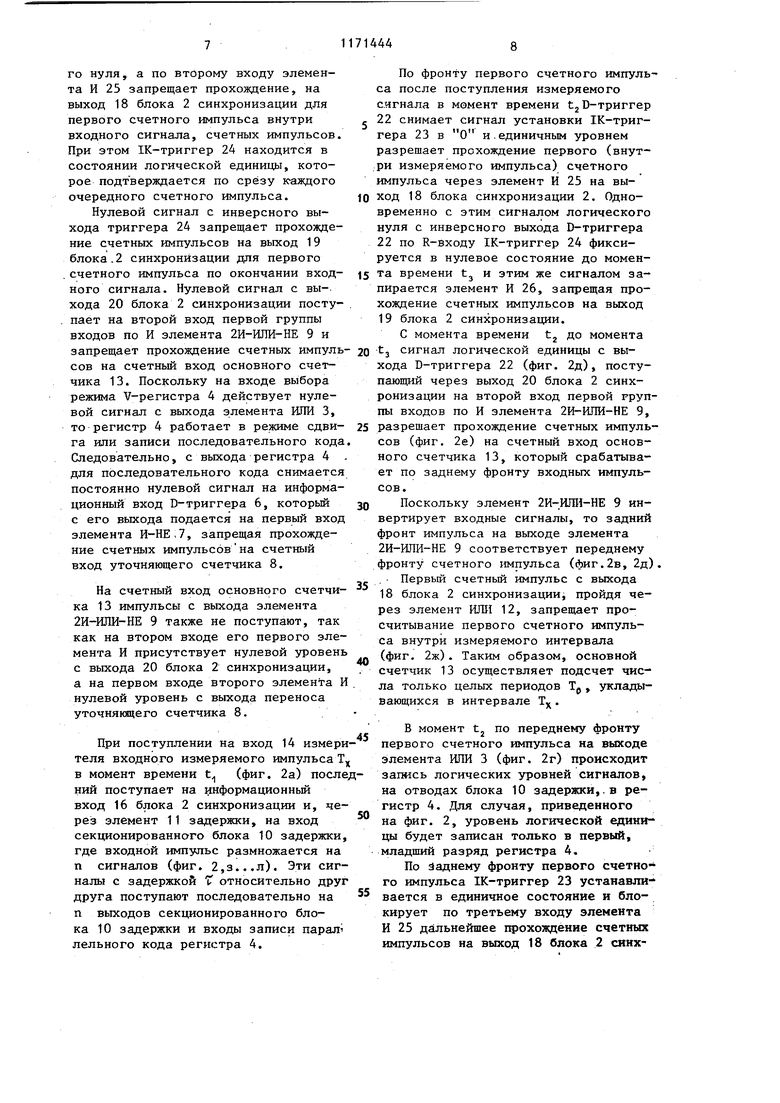

В исходном состоянии счетчики 8 и 13 обнулены. Генератор 1 счетных импульсов вырабатывает непрерывную последовательность импульсов с периодом повторения Тд (фиг. 2в), которая поступает на синхровход 17 блока 2 синхронизации, на синхровход Cj регистра 4 сдвига, на синхровход D-триггера 6, на первый вход первой группы входов по И элемента 2И-ШШ-НЕ 9 и на второй вход эле мента И-НЕ 1.

При наличии нулевого уровня сигнала на входе измерителя и на D-входе триггера 22,. при поступлении на его синхровход импульсов с выхода генератора 1, осуществляется перепись сигнала логического нуля с информационного входа D-триггера на его прямой выход, который в качестве управляющего по R-входу удерживает первый 1К-триггер 23 в состоянии логическо го нуля, а по второму входу элемента И 25 запрещает прохождение, на выход 18 блока 2 синхронизации для первого счетного импульса внутри входного сигнала, счетных импульсов При этом 1К-триггер 24 находится в состоянии логической единицы, которое подтверждается по срезу юаждого очередного счетного импульса. Нулевой сигнал с инверсного выхода триггера 24 запрещает прохождение счетных импульсов на выход 19 блока.2 синхронизации для первого .счетного импульса по окончании входного сигнала. Нулевой сигнал с выхода 20 блока 2 синхронизации поступает на второй вход первой группы входов по И элемента 2И-ИЛИ-НЕ 9 и запрещает прохождение счетных импуль сов на счетный вход основного счетчика 13. Поскольку на входе выбора режима V-регистра 4 действует нулевой сигнал с выхода элемента ИЛИ 3, то регистр 4 работает в режиме сдвига или записи последовательного кода Следовательно, с выхода регистра 4 для последовательного кода снимается постоянно нулевой сигнал на информационный вход D-триггера 6, который с его выхода подается на первый вход элемента И-НЕ,7, запрещая прохождение счетных импульсовна счетный вход уточняющего счетчика 8. На счетный вход основного счетчи ка 13 импульсы с вькода элемента 2И-ИЛИ-НЕ 9 также не поступают, так как на втором входе его первого эле мента И присутствует нулевой уровен с выхода 20 блока 2 синхронизации, а на первом входе второго элемента нулевой уровень с выхода переноса уточнякщего счетчика 8. При поступлении на вход 14 измер теля входного измеряемого импульса Т в момент времени t (фиг. 2а) посл ний поступает на информационньй вход 16 блока 2 синхронизации и, че рез элемент 11 задержки, на вход секционированного блока 10 задержки где входной импульс размножается на п сигналов (фиг. 2,з...л). Эти сиг налы с задержкой Т относительно дру друга поступают последовательно на п выходов секционированного блока 10 задержки и входы записи парал лельного кода регистра 4. По фронту первого счетного импульса после поступления измеряемого сигнала в момент времени t2D-тpиггep 22 снимает сигнал установки 1К-триггера 23 в О и.единичным уровнем разрешает прохождение первого (внутри измеряемого импульса) счетного импульса через элемент И 25 на выход 18 блока синхронизации 2. Одновременно с этим сигналом логического нуля с инверсного выхода D-триггера 22 по R-входу 1К-триггер 24 фиксируется в нулевое состояние до момента времени t и этим же сигналом запирается элемент И 26, запрещая прохождение счетных импульсов на ВЕЛХОД 19 блока 2 синхронизации. С момента времени t до момента tj сигнал логической единицы с выхода D-триггера 22 (фиг. 2д), поступающий через выход 20 блока 2 синхронизации на второй вход первой группы входов по И элемента 2И-Ш1И-НЕ 9, разрешает прохождение счетных импульсов (фиг. 2е) на счетный вход основного счетчика 13, который срабатывает по заднему фронту входных импульсов. Поскольку элемент 2И-,ИШ1-НЕ 9 инвертирует входные сигналы, то задний фронт импульса на выходе элемента 2И-Ш1И-НЕ 9 соответствует переднему фронту счетного импульса (фиг.2в, 2д). Первый счетный импульс с выхода 18 блока 2 синхронизации, пройдя через элемент ИЛИ 12, запрещает просчитывание первого счетного импульса внутри измеряемого интервала (фиг. 2ж). Таким образом, основной счетчик 13 осуществляет подсчет числа только целых периодов Тр, укладывающихся в интервале Т. В момент tj по переднему фронту первого счетного импульса на выходе элемента ИЛИ 3 (фиг. 2г) происходит запись логических уровней сигналов, на отводах блока 10 задержки,, в регистр 4. Для случая, приведенного на фиг. 2, уровень логической единицы будет записан только в первый, младший разряд регистра 4. По заднему фронту первого счетного импульса 1К-триггер 23 устанавливается в единичное состояние и блокирует по третьему входу элемента И 25 дальнейшее прохождение счетных импульсов на выход 18 блока 2 синхронизации и регистр 4 переходит вновь в режим сдвига, который начин ет осуществляться по заднему фронту второго счетного импульса внутри из меряемого сигнала. Последовательный код, характеризующий в уточняющих дискретах С несовпадение начала сигнала измеряемо длительности и переднего фронта бли жайщего счетного импульса, поступает с выхода, регистра 4 на информационный вход D-триггера 6, работающего по переднему фронту синхроимпульсов. Это триггер позволяет искл чить неоднозначность между логическим уровнем единицы в старшем разря де регистра 4 и уточняющим счетным имйульсом, так как запись параллель ного кода в регистр 4 производится практически по переднему фронту пер вого счетного импульса внутри измеряемого сигнала. Информация со стар шего разряда, являющегося выходом регистра для последовательного кода будет неизменной до заднего фронта второго счетного импульса. При не соответствии D-триггера уровню логи ческой единицы в этом разряде следо вало бы два уточняющих счетных импульса с выхода-злемента И-НЕ 7. Поскольку синхроимпульс записи параллельного кода при прохождении через блок 2 синхронизации, элемент и инвертор 5 задерживается относительно фронта сигнала на синхровходе D-триггера 6, то последний переписывает информацию с выхода регист ра 4 только по переднему фронту вто рого счетного импульса, что исключает неоднозначность формирования уточняющего импульса. Последний импульс последовательности уточняющих импульсов заканчивается через время (п+1)Тр, прошедшее с момента времени tj. После окончания сигнала измеряемой длительности в момент времени tj блок синхррнизации 2 формирует на выходе 19 первый счетный импульс по окончании входного сигнала, которым через элемент ИЛИ 3 и инверто 5 осуществляется запись информации с выводов блока 10 задержки в регистр 4 с последующим формированием уточняющих счетных импульсов. Если при подсчете уточняющим счетчиком 8 импульсов с выхода элемента И-НЕ 7 (фиг. 2м) в момент t произошло его переполнение, то в его старшем разряде появляется сигнал логической единицы -(фиг. 2н), который поступает на первьй вход второй группы входов по И элемента 2И-ИЛИ-НЕ 9, а поскольку на втором входе второй группы входов этого элемента с момента времени действует сигнал логической единицы с инверсного выхода блока 2 синхронизации для синхронизированного счетными импульсами входного сигнала, то на выходе элемента 2И-ИЛИ-НЕ 9 формируется перепад из 1 в О (фиг. 2е), который вызывает увеличение числа, записанного в счетчике 13, на единицу. - Через время (п+ОТ с момента tj среза синхронизированного счетными импульсами входного сигнала процесс измерения заканчивается. На основном счетчике 13 будет записана длительность входного импульса в периодах , счетных импульсов Т, на уточняющем в уточняющих дискретах. Если при уточнении начала сигнала измеряемой длительности дробная часть Л уточняющего дискрета t отбрасывалась (фиг. 2)., то при уточнении конца сигнала дробная часть уточняющего дискрета добавлением л округлялась до целой. Таким образом, погрешность измерения несовпадения начала и конца измеряемого интервала со счетными импульсами с равна 0 2-41Поскольку о Д С и О , то погрешность измерения длительности импульса не превьш1ает величины t. Использование в изобретении параллельно-последовагельного п-разрядного регистра сдвига для записи в него информации о расщепленных и задержанных относительно друг друга сигналов с отводов блока задержки по фронтам первых счетных импульсов, вьщеленных блоком синхронизации, внутри и по окончании импульса измеряемой дли- тельности и формировании уточняющих счетных импульсов позволяет повысить точность измерения длительности импульсов .

.

г.

-«ь

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автоматическая аппаратура контроля радиоэлектронного оборудования | |||

| Под ред | |||

| Н.Н, Пономарева, М., Советское радио, 1975, с, | |||

| Аппарат для электрической передачи изображений без проводов | 1920 |

|

SU144A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ измерения одиночных временных интервалов | 1971 |

|

SU474783A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| . | |||

Авторы

Даты

1985-08-07—Публикация

1983-04-15—Подача